FPGA的时钟频率同步原理研究与设计实现

FPGA分频与倍频的简单总结(涉及自己设计,调用时钟IP核,调用MMCM原语模块)

FPGA分频与倍频的简单总结(涉及⾃⼰设计,调⽤时钟IP核,调⽤MMCM原语模块)原理介绍1、分频FPGA设计中时钟分频是重要的基础知识,对于分频通常是利⽤计数器来实现想要的时钟频率,由此可知分频后的频率周期更⼤。

⼀般⽽⾔实现偶数系数的分频在程序设计上较为容易,⽽奇数分频则相对复杂⼀些,⼩数分频则更难⼀些。

1)偶分频系数=时钟输⼊频率/时钟输出频率=50MHz/5MHz=10,则计数器在输⼊时钟的上升沿或者下降沿从0~(10-1)计数,⽽输出时钟在计数到4和9时翻转。

2)奇分频系数=50MHz/10MHz=5,则两个计数器分别在输⼊时钟的上升沿和下降沿从0~ (5-1)计数,⽽相应的上升沿和下降沿触发的输出时钟在计数到1和4时翻转,最后将两个输出时钟进⾏或运算从⽽得到占空⽐为50%的5分频输出时钟。

下图所⽰为50MHz输⼊时钟进⾏10分频和5分频的仿真波形2、倍频两种思路:PLL(锁相环)或者利⽤门延时来搭建注意:此仿真是利⽤FPGA内部电路延迟来实现的倍频需要在后仿真下才能看到波形,在⾏为仿真下⽆法得到输出波形。

⼀、时钟IP的分频倍频相关参数说明输⼊时钟:clk_in1(125MHz)输出时钟:clk_out1(50MHz),clk_out2(74.25MHz)则VCO Freq=1262.5MHz=clk_in1*CLKFBOUT_MULT_F/DIVCLK_DIVIDE=125*50.5/5clk_out1(50MHz)=VCO_Freq/Divide=1265.5/25.250clk_out2(74.25MHz)=VCO_Freq/Divide=1265.5/17⼆、MMCME4_ADVMMCME4是⼀种混合信号块,⽤于⽀持频率合成、时钟⽹络设计和减少抖动。

基于相同的VCO频率,时钟输出可以有单独的分频、相移和占空⽐。

此外,MMCME4还⽀持动态移相和分数除法(1)Verilog 初始化模板MMCME4_ADV #(.BANDWIDTH("OPTIMIZED"), // Jitter programming.CLKFBOUT_MULT_F(5.0), // Multiply value for all CLKOUT.CLKFBOUT_PHASE(0.0), // Phase offset in degrees of CLKFB.CLKFBOUT_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKIN1_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKIN2_PERIOD(0.0), // Input clock period in ns to ps resolution (i.e. 33.333 is 30 MHz)..CLKOUT0_DIVIDE_F(1.0), // Divide amount for CLKOUT0.CLKOUT0_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT0.CLKOUT0_PHASE(0.0), // Phase offset for CLKOUT0.CLKOUT0_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT1_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT1_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT1_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT1_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT2_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT2_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT2_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT2_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT3_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT3_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT3_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT3_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT4_CASCADE("FALSE"), // Divide amount for CLKOUT (1-128).CLKOUT4_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT4_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT4_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT4_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT5_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT5_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT5_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT5_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).CLKOUT6_DIVIDE(1), // Divide amount for CLKOUT (1-128).CLKOUT6_DUTY_CYCLE(0.5), // Duty cycle for CLKOUT outputs (0.001-0.999)..CLKOUT6_PHASE(0.0), // Phase offset for CLKOUT outputs (-360.000-360.000)..CLKOUT6_USE_FINE_PS("FALSE"), // Fine phase shift enable (TRUE/FALSE).COMPENSATION("AUTO"), // Clock input compensation.DIVCLK_DIVIDE(1), // Master division value.IS_CLKFBIN_INVERTED(1'b0), // Optional inversion for CLKFBIN.IS_CLKIN1_INVERTED(1'b0), // Optional inversion for CLKIN1.IS_CLKIN2_INVERTED(1'b0), // Optional inversion for CLKIN2.IS_CLKINSEL_INVERTED(1'b0), // Optional inversion for CLKINSEL.IS_PSEN_INVERTED(1'b0), // Optional inversion for PSEN.IS_PSINCDEC_INVERTED(1'b0), // Optional inversion for PSINCDEC.IS_PWRDWN_INVERTED(1'b0), // Optional inversion for PWRDWN.IS_RST_INVERTED(1'b0), // Optional inversion for RST.REF_JITTER1(0.0), // Reference input jitter in UI (0.000-0.999)..REF_JITTER2(0.0), // Reference input jitter in UI (0.000-0.999)..SS_EN("FALSE"), // Enables spread spectrum.SS_MODE("CENTER_HIGH"), // Spread spectrum frequency deviation and the spread type .SS_MOD_PERIOD(10000), // Spread spectrum modulation period (ns).STARTUP_WAIT("FALSE") // Delays DONE until MMCM is locked)MMCME4_ADV_inst (.CDDCDONE(CDDCDONE), // 1-bit output: Clock dynamic divide done.CLKFBOUT(CLKFBOUT), // 1-bit output: Feedback clock.CLKFBOUTB(CLKFBOUTB), // 1-bit output: Inverted CLKFBOUT.CLKFBSTOPPED(CLKFBSTOPPED), // 1-bit output: Feedback clock stopped.CLKINSTOPPED(CLKINSTOPPED), // 1-bit output: Input clock stopped.CLKOUT0(CLKOUT0), // 1-bit output: CLKOUT0.CLKOUT0B(CLKOUT0B), // 1-bit output: Inverted CLKOUT0.CLKOUT1(CLKOUT1), // 1-bit output: CLKOUT1.CLKOUT1B(CLKOUT1B), // 1-bit output: Inverted CLKOUT1.CLKOUT2(CLKOUT2), // 1-bit output: CLKOUT2.CLKOUT2B(CLKOUT2B), // 1-bit output: Inverted CLKOUT2.CLKOUT3(CLKOUT3), // 1-bit output: CLKOUT3.CLKOUT3B(CLKOUT3B), // 1-bit output: Inverted CLKOUT3.CLKOUT4(CLKOUT4), // 1-bit output: CLKOUT4.CLKOUT5(CLKOUT5), // 1-bit output: CLKOUT5.CLKOUT6(CLKOUT6), // 1-bit output: CLKOUT6.DO(DO), // 16-bit output: DRP data output.DRDY(DRDY), // 1-bit output: DRP ready.LOCKED(LOCKED), // 1-bit output: LOCK.PSDONE(PSDONE), // 1-bit output: Phase shift done.CDDCREQ(CDDCREQ), // 1-bit input: Request to dynamic divide clock.CLKFBIN(CLKFBIN), // 1-bit input: Feedback clock.CLKIN1(CLKIN1), // 1-bit input: Primary clock.CLKIN2(CLKIN2), // 1-bit input: Secondary clock.CLKINSEL(CLKINSEL), // 1-bit input: Clock select, High=CLKIN1 Low=CLKIN2.DADDR(DADDR), // 7-bit input: DRP address.DCLK(DCLK), // 1-bit input: DRP clock.DEN(DEN), // 1-bit input: DRP enable.DI(DI), // 16-bit input: DRP data input.DWE(DWE), // 1-bit input: DRP write enable.PSCLK(PSCLK), // 1-bit input: Phase shift clock.PSEN(PSEN), // 1-bit input: Phase shift enable.PSINCDEC(PSINCDEC), // 1-bit input: Phase shift increment/decrement.PWRDWN(PWRDWN), // 1-bit input: Power-down.RST(RST) // 1-bit input: Reset);(2)本实验仿真所⽤参数配置说明及部分端⼝调⽤1、参数配置说明本实验通过输⼊时钟CLKIN1(150MHz),实现输出反馈时钟CLKFBOUT(150MHz)、输出时钟CLKOUT0(74.25MHz)、输出时钟CLKOUT1(74.25MHz)、输出时钟CLKOUT2(59.4MHz)、输出时钟CLKOUT3(49.5MHz)。

基于FPGA的高频时钟电路设计

G A的编程可以实现不 同频率输 出。图 2 所示 为它 的部分逻辑单元 。 它 的输 出时钟频 率 f r 小 主要决 定 于 外 o 大 u 部输入的参考时钟 f F R 的频率 以及 内部的 P L E L

(h aeL ce o p 分频 因 子 P、 和 N. P rs- ok dL o ) M 用 公式表达如下 :

响 AD 的动态 性 能 , 了将 这 种 影 响最 小 化 , C 为

输 出我们所需 要频率的时钟信号. 由时钟 芯片 输出的是一对差分 的 L P C V E L电平信号 , 所用

的扇出芯片 N 6 1 S是一个可 以将一对差分 BN 4

的 L P C 电 平 信 号 转 化 为 四对 差 分 的 vEL L D V S电平信号输 出的转换器。图 l 所示 为设

第 2 8卷

20 年 08

第 4期

7 月

核 电子学 与探 测 技 术

Nu la lcr nc cerE e to i s& D tcin Teh oo y eet c n lg o

Vo 8 N0 4 k2 .

J1 20 u. 0 8

基 于 F GA 的 高 频 时 钟 电路 设 计 P

理意义 的参数—— 中微子 混合角 e 。实验利 。

用 电子反中微子在大型液体闪烁体探测器中的 反B 衰变反应来测量反应堆 中微子 。比较远近 探 测 器 测得 的 中微 子 Leabharlann 量 和 能 谱 , 可 以知 道 就

编程实现对时钟芯片 MP 94 2的控制 , C 23 并根

据需要输出高达 1 G赫兹 的高频 时钟. 设计 中 的难点 主要 是 在 时钟 信 号 高达 1 GHz 印制版 时

高速NRZ码同步时钟提取设计及FPGA实现

高速NRZ码同步时钟提取设计及FPGA实现徐泽琨,黄明,汪弈舟,李国诚,黄炎(北方工业大学,北京 100041)摘 要:为精准提取高速NRZ码元的时钟,设计了过零检测微分型数字锁相环,采用增加/扣除脉冲法进行动态相位调整,用以实现对高速NRZ码元接收序列进行位时钟同步;分析了最大锁定范围和最大锁定频率与本地时钟频率的关系;使用Verilog HDL语言进行代码编写,基于FPGA进行了验证。

应用误码仪实测表明:在发送波特率为1 Mbps的PN17伪随机序列时,时钟同步后误码率小于10-7;最高时钟恢复速率可达50 Mbps。

实际应用中具有很好的适用性和抗干扰性。

关键词: 增加/扣除脉冲法;位时钟同步;时钟恢复;FPGA;高速NRZ码中图分类号:TP311文献标识码:A文章编号:2095-8412 (2019)05-028-06工业技术创新 URL: http: // DOI: 10.14103/j.issn.2095-8412.2019.05.005引言在现代通信系统中,位时钟同步技术即在通信码元中提取时钟信息,是精准判断通信数据的基础。

例如在光通信发送端和接收端之间,时钟不会单独传送,只能从信号中提取(恢复),如果时钟有偏差,就会直接导致误码率的增大。

在接收端进行位同步处理,对时钟纠偏,恢复同步时钟;据此作为最佳采样脉冲,对接收信号进行提取操作,能够准确地恢复原始发送数据。

同步性能的好坏直接影响通信系统的性能。

出现同步误差或失去同步,就会导致通信系统性能下降或通信中断[1]。

本文基于增加/扣除脉冲法,应用过零检测微分型数字锁相环,对高速N R Z(N o n R e t u r n Zero)码进行时钟同步提取,通过了FPGA仿真测试和系统信号实测。

此算法的优势在于它可在500 MHz主频下实现高达50 Mbps数据速率的时钟同步。

算法结构简单、易于实现,非常节省FPGA内部设计资源。

1 基本原理1.1 NRZ编码原理N R Z编码也称为不归零编码,是最常用于传输高速同步数据的一种编码。

关于FPGA设计中多时钟域和异步信号处理有关的问题

有一个有趣的现象,众多数字设计特别是与FPGA设计相关的教科书都特别强调整个设计最好采用唯一的时钟域。

换句话说,只有一个独立的网络可以驱动一个设计中所有触发器的时钟端口。

虽然这样可以简化时序分析以及减少很多与多时钟域有关的问题,但是由于FPGA外各种系统限制,只使用一个时钟常常又不现实。

FPGA时常需要在两个不同时钟频率系统之间交换数据,在系统之间通过多I/O接口接收和发送数据,处理异步信号,以及为带门控时钟的低功耗ASIC进行原型验证。

本章讨论一下在FPGA设计中多时钟域和异步信号处理有关的问题和解决方案,并提供实践指导。

这里以及后面章节提到的时钟域,是指一组逻辑,这组逻辑中的所有同步单元(触发器、同步RAM块以及流水乘法器等)都使用同一个网络作为时钟。

假如设计中所有的触发器都使用一个全局网络,比如FPGA的主时钟输入,那么我们说这个设计只有一个时钟域。

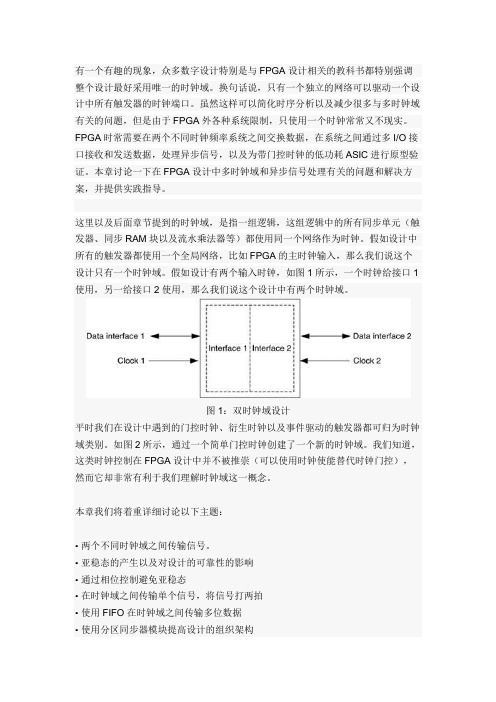

假如设计有两个输入时钟,如图1所示,一个时钟给接口1使用,另一给接口2使用,那么我们说这个设计中有两个时钟域。

图1:双时钟域设计平时我们在设计中遇到的门控时钟、衍生时钟以及事件驱动的触发器都可归为时钟域类别。

如图2所示,通过一个简单门控时钟创建了一个新的时钟域。

我们知道,这类时钟控制在FPGA设计中并不被推崇(可以使用时钟使能替代时钟门控),然而它却非常有利于我们理解时钟域这一概念。

本章我们将着重详细讨论以下主题:•两个不同时钟域之间传输信号。

•亚稳态的产生以及对设计的可靠性的影响•通过相位控制避免亚稳态•在时钟域之间传输单个信号,将信号打两拍•使用FIFO在时钟域之间传输多位数据•使用分区同步器模块提高设计的组织架构•处理ASIC验证原型里的门控时钟•建立一个单时钟模块•自动门控移除图2:通过门控时钟创建的时钟域一、跨时钟域设计中包含多时钟域,首先要解决的是在不同时钟域之间传输信号的问题。

信号跨时钟域传输将会是一个大问题,原因如下:1、信号跨时钟域传输产生的故障总是不太容易复现。

基于FPGA的数字钟设计

数字钟的设计一、 设计要求设计一个数字钟,要求用数码管分别显示时、分、秒的计数,同时可以进行时间设置,并且要求在整点的时候能够实现报时功能。

二、 设计原理计数器在正常工作下是对1Hz的频率计数,在调整时间状态下是对调整的时间模块进行计数;控制按键来选择是正常计数还是调整时间,并决定是调整时还是分;时间显示的LED数码管采用动态扫描实现;在整点到达时,还具有整点报时功能。

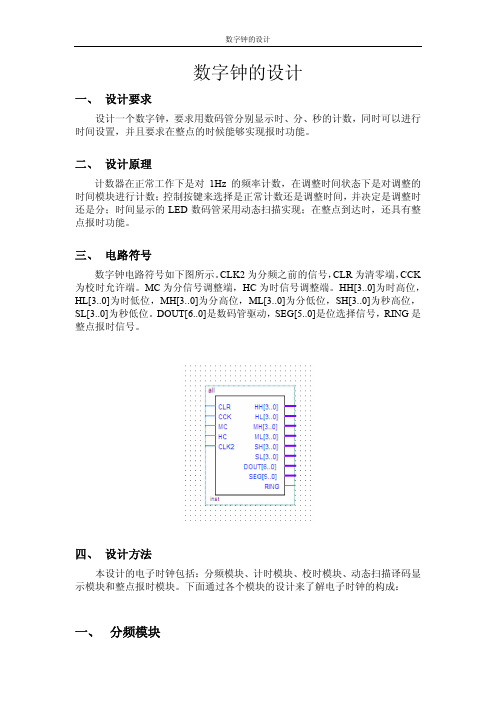

三、 电路符号数字钟电路符号如下图所示。

CLK2为分频之前的信号,CLR为清零端,CCK 为校时允许端。

MC为分信号调整端,HC为时信号调整端。

HH[3..0]为时高位,HL[3..0]为时低位,MH[3..0]为分高位,ML[3..0]为分低位,SH[3..0]为秒高位,SL[3..0]为秒低位。

DOUT[6..0]是数码管驱动,SEG[5..0]是位选择信号,RING是整点报时信号。

四、 设计方法本设计的电子时钟包括:分频模块、计时模块、校时模块、动态扫描译码显示模块和整点报时模块。

下面通过各个模块的设计来了解电子时钟的构成:一、 分频模块程序附录:module clk2clk1s(clk,clk1s); input clk;output clk1s;reg clk1s;reg [3:0] cnt;always@(posedge clk)if(cnt==4'b1111)beginclk1s<=~clk1s;cnt<=0;endelsecnt<=cnt+1; endmodule波形仿真:二、 计时模块六十进制计数器六十进制计数器程序附录:六十进制计数器模块:module m60(clk,clr,qh,ql,cao);input clk,clr;output cao;output[3:0] qh,ql;reg [3:0] qh,ql;reg cao;always @(posedge clk or negedge clr) beginif(clr==0)beginqh<=4'h0;ql<=4'h0;cao<=0;endelse if(ql==9)beginql<=0;if(qh==5)beginqh<=0;cao<=1;endelse qh=qh+1;endelsebeginql<=ql+1;cao<=0;endendendmodule二十四进制计数器模块:module m24(clk,clr,qh,ql);input clk,clr;output[3:0] qh,ql;reg [3:0] qh,ql;always @(posedge clk or negedge clr) beginif(clr==0)beginqh<=4'h0;ql<=4'h0;endelse if(qh==2)beginql<=ql+1;if(ql==3)beginqh<=0;ql<=0;endendelse if(ql==9)beginqh<=qh+1;ql<=0;endelseql<=ql+1; end endmodule波形仿真:清零清零正常计时三、 校时模块四、 动态译码显示模块CCK 为0不支持校时,有进位信号时产生分(时)脉冲程序附录:1、位扫描信号(HH,HL,MH,ML,SH,SL逐位扫描,并输出)module sel(clk,hh,hl,mh,ml,sh,sl,out);input clk;input [3:0] hh,hl,mh,ml,sh,sl;output [3:0] out;reg [3:0] out;reg [3:0] ss=0;always @(posedge clk)beginif(ss<4'b0101)ss<=ss+1;elsess<=0;endalways @(posedge clk)begincase(ss)4'd0:out<=sl;4'd1:out<=sh;4'd2:out<=ml;4'd3:out<=mh;4'd4:out<=hl;4'd5:out<=hh;endendmodule仿真图:2、段扫描信号(选择数码管点亮哪一位)module seg(clk,seg);input clk;output [5:0] seg;reg [5:0] seg;reg [3:0] ss=0;always @(posedge clk)beginif(ss<4'b0101)ss<=ss+1;elsess<=0;endalways @(posedge clk)begincase(ss)4'd0:seg<=6'b111110;4'd1:seg<=6'b111101;4'd2:seg<=6'b111011;4'd3:seg<=6'b110111;4'd4:seg<=6'b101111;4'd5:seg<=6'b011111;default:seg<=6'b111111;endcaseend3、4—7译码module decode4_7(decodeout,indec); output[6:0] decodeout;input[3:0] indec;reg[6:0] decodeout;always @(indec)begincase(indec)4'd0:decodeout=7'b1111110;4'd1:decodeout=7'b0110000;4'd2:decodeout=7'b1101101;4'd3:decodeout=7'b1111001;4'd4:decodeout=7'b0110011;4'd5:decodeout=7'b1011011;4'd6:decodeout=7'b1011111;4'd7:decodeout=7'b1110000;4'd8:decodeout=7'b1111111;4'd9:decodeout=7'b1111011;default: decodeout=7'b0000000;endcaseendendmodule五、 整点报时模块六、 数字钟仿真图数字钟的设计注:动态扫描的时钟频率尽量要快。

(完整版)基于FPGA的等精度频率计的设计与实现毕业设计

第一章课题研究概述1.1课题研究的目的和意义在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。

测量频率的方法有多种,其中电子计数器测量频率具有精度高、使用方便、测量迅速,以及便于实现测量过程自动化等优点,是频率测量的重要手段之一。

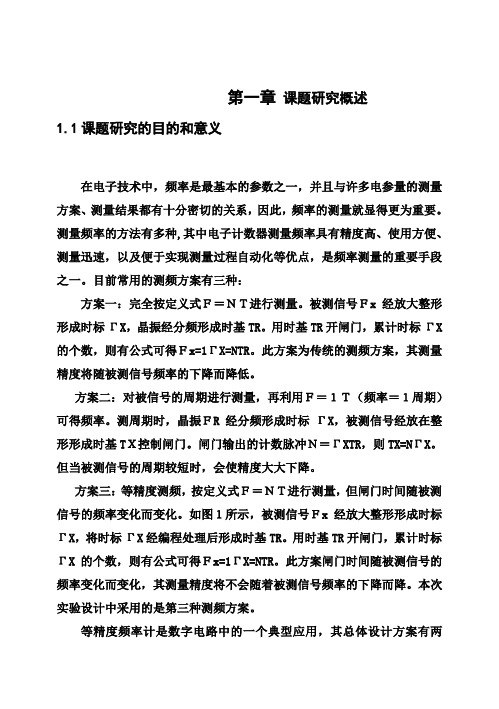

目前常用的测频方案有三种:方案一:完全按定义式F=NT进行测量。

被测信号Fx经放大整形形成时标ГX,晶振经分频形成时基TR。

用时基TR开闸门,累计时标ГX 的个数,则有公式可得Fx=1ГX=NTR。

此方案为传统的测频方案,其测量精度将随被测信号频率的下降而降低。

方案二:对被信号的周期进行测量,再利用F=1T(频率=1周期)可得频率。

测周期时,晶振FR经分频形成时标ГX,被测信号经放在整形形成时基TX控制闸门。

闸门输出的计数脉冲N=ГXTR,则TX=NГX。

但当被测信号的周期较短时,会使精度大大下降。

方案三:等精度测频,按定义式F=NT进行测量,但闸门时间随被测信号的频率变化而变化。

如图1所示,被测信号Fx经放大整形形成时标ГX,将时标ГX经编程处理后形成时基TR。

用时基TR开闸门,累计时标ГX的个数,则有公式可得Fx=1ГX=NTR。

此方案闸门时间随被测信号的频率变化而变化,其测量精度将不会随着被测信号频率的下降而降。

本次实验设计中采用的是第三种测频方案。

等精度频率计是数字电路中的一个典型应用,其总体设计方案有两种:方案一:采用数字逻辑电路制作,用IC拼凑焊接实现。

其特点是直接用现成的IC组合而成,简单方便,但由于使用的器件较多,连线复杂,体积大,功耗大,焊点和线路较多将使成品稳定度与精确度大打折扣,而且会产生比较大的延时,造成测量误差、可靠性差。

方案二:采用可编程逻辑器件(CPLD)制作。

随着现场可编程门阵列FPGA的广泛应用,以EDA工具作为开发手段,运用VHDL等硬件描述语言语言,将使整个系统大大简化,提高了系统的整体性能和可靠性。

基于FPGA位同步时钟提取方案的设计

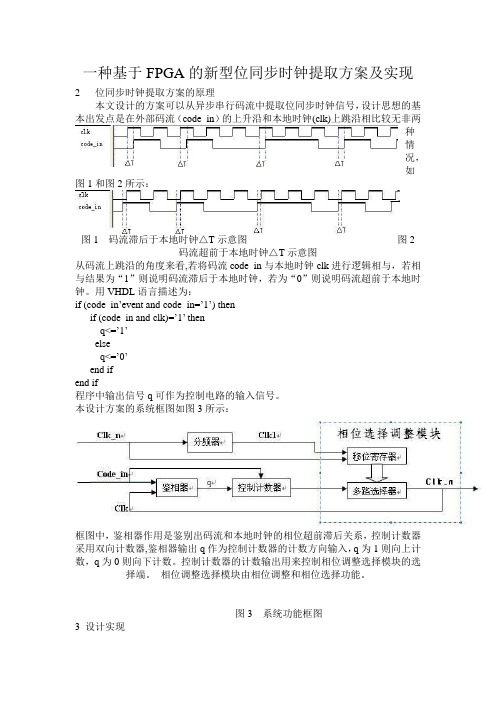

一种基于FPGA的新型位同步时钟提取方案及实现2 位同步时钟提取方案的原理本文设计的方案可以从异步串行码流中提取位同步时钟信号,设计思想的基本出发点是在外部码流(code_in)的上升沿和本地时钟(clk)上跳沿相比较无非两种情况,如图1和图2所示:图1 码流滞后于本地时钟△T示意图图2码流超前于本地时钟△T示意图从码流上跳沿的角度来看,若将码流code_in与本地时钟clk进行逻辑相与,若相与结果为“1”则说明码流滞后于本地时钟,若为“0”则说明码流超前于本地时钟。

用VHDL语言描述为:if (code_in’event and code_in=’1’) thenif (code_in and clk)=’1’ thenq<=’1’elseq<=’0’end ifend if程序中输出信号q可作为控制电路的输入信号。

本设计方案的系统框图如图3所示:框图中,鉴相器作用是鉴别出码流和本地时钟的相位超前滞后关系,控制计数器采用双向计数器,鉴相器输出q作为控制计数器的计数方向输入,q为1则向上计数,q为0则向下计数。

控制计数器的计数输出用来控制相位调整选择模块的选择端。

相位调整选择模块由相位调整和相位选择功能。

图3 系统功能框图3 设计实现依据图3系统功能框图,利用Altera 公司的Quartus II 设计软件,采用自顶向下的模块化设计方法,用VHDL 语言和电路原理图混合输入设计对位同步时钟提取电路的各个部件分别进行设计。

本设计方案的鉴相器原理相对简单,不需要用VHDL语言设计,仅用两个与门和一个D触发器就可以实现,如图4 所示。

图中的的第二个与门(inst23)是为了实现D触发器的时钟输入端与数据输入端同步。

控制计数器设计使用QuartusII的MegaWizard Plug_InManager工具来实现一个简单的双向数器,计数方向由鉴相器输出q控制,q为1则计数器向上计数,q为0则计数器向下计数,计数系数由Count Modulus设定,设定的数值要求等于分频器的分频系数N。

基于FPGA的数字电子时钟设计与实现.

课程设计 (论文说明书题目:基于 FPGA 的数字电子时钟设计院 (系 :信息与通信学院专学生姓名:学号:0900240115指导教师:职2012 年 12 月 25 日一、所用设备与器材1.1仪器设备使用仪器设备有 FPGA DE2-70开发板、 PC 机、信号发生器。

图 1 FPGA DE2-70开发板图二.系统方案2.1 设计思想利用数字电子技术、 EDA 设计方法、 FPGA 等技术,设计、仿真并实现一个基于 FPGA 的数字电子时钟基本功能, 其基本组成框图如图 1所示,振荡器采用ALTERA 的 DE2-70实验板的 50MHz 输出,分频器将 50MHz 的方波进行分频进而得到 1Hz 的标准秒脉冲,时、分、秒计时模块分别由二十四进制时计数器、六十进制分计数器和六十进制秒计数器完成,校时模块完成时和分的校正。

扩展功能设计为倒计时功能,从 59分 55秒至 59分 59秒,每秒亮一盏灯报时。

2.1.1课题背景20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力的推动了社会生产力的发展和社会信息化程度的提高, 同时也使现代电子产品性能更进一步, 产品更新换代的节奏也越来越快。

20世纪 80年代末,出现了 FPGA(Field Progrommable Gate Array, CAE 和 CAD 技术的应用更为广泛,它们在 PCB 设计的原理图输入,自动布局布线及 PCB 分析, 以及逻辑设计,逻辑仿真布尔综合和化简等方面担任了重要的角色,为电子设计自动化必须解决的电路建模,标准文档及仿真测试奠定了基础。

硬件描述语言是 EDA 技术的重要组成部分, VHDL 是作为电子设计主流硬件的描述语言。

本论文就是应用 VHDL 语言来实现秒表的电路设计。

VHDL 语言是标准硬件描述语言,它的特点就是能形式化抽样表示电路结构及行为,支持逻辑设计中层次领域的描述,借用了高级语言的精巧结构简化电路描述,具有电路模拟与验证及保证设计的正确性,支持电路由高层向底层的综合变换,便于文档管理,易于理解和设计重用。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

FPGA的时钟频率同步原理研究与设计实现

引言

网络化运动控制是未来运动控制的发展趋势,随着高速加工技术的发展,对网络节点间的时间同步精度提出了更高的要求。

如造纸机械,运行速度为1 500~1 800m/min,同步运行的电机之间1μs的时间同步误差将造成30 μm的运动误差。

高速加工中心中加工速度为120 m/min 时,伺服电机之间1μs的时间同步误差,将造成2 μm的加工误差,影响了加工精度的提高。

分布式网络中节点的时钟通常是采用晶振+计数器的方式来实现,由于

晶振本身的精度以及稳定性问题,造成了时间运行的误差。

时钟同步通常是选

定一个节点时钟作为主时钟,其他节点时钟作为从时钟。

主节点周期性地通过

报文将主时钟时间发送给从节点,从节点接收到报文后,以主时钟为基准进行

延迟补偿,然后将计算出的新时钟值赋给从时钟。

这种同步方法造成了从时钟

计数值的不连续,即会出现重复(从时钟晶振频率快于主时钟)或跳跃(从时钟晶

振频率慢于主时钟),而且这种方法并没有从根本上解决时钟频率的不同步问题,因此要进一步提高同步精度很困难。

本文研究了一种可对频率进行动态调整的

时钟,通过对时钟频率的动态修正,实现主从时钟频率的同步,进而实现时间

同步。

1 时钟同步原理

要实现两个时钟的同步,一是时钟的计数值要相同,二是计数增长速率

要相同。

如图1 所示,设主时钟的频率为f,从时钟频率在Nn-1 到Nn 时间段

为fn-1,在Nn 到Nn+1 为fn,SyncDelay 为同步报文从主站到从站的延迟时间,可以通过延时测量帧采用往返法测量得到,从时钟要在Nn+1 时刻达到与主时

钟相等,那么有:。