8路数据选择器、16位奇偶检验器的设计

数字ic课程设计_8路选择器

目录1课程设计名称 (1)2课程设计内容 (1)3课程设计目的 (1)4课程设计要求 (1)5使用软件 (1)6课程设计原理 (1)7课程设计网表 (4)8结果及分析 (8)9延时手工计算 (10)10总结 (11)11参考书目 (11)1.课程设计名称设计一个用两个4选1数据选择器接成8选1数据选择器。

2.课程设计内容设计一个用两个4选1数据选择器接成8选1数据选择器,要求要有超前进位,减小输出的延迟,采用0.5um工艺设计。

3.课程设计目的训练学生综合运用学过的数字集成电路的基本知识,独立设计相对复杂的数字集成电路的能力。

4.课程设计要求4.1、按设计指导书中要求的格式书写,所有的内容一律打印;4.2、报告内容包括设计过程、仿真的HSPICE网表,软件仿真的结果及分析、延时的手工计算;4.3、要有整体电路原理图,仿真的波形图;4.4、软件仿真必须要有必要的说明;要给出各个输入信号的具体波形和输出信号的测试结果。

4.5、写出对应的HSPICE设计网表,网表仿真结果符合设计要求。

把仿真图形附在报告上。

4.6、设输入端的电容为C inv,输出端的负载电容为5000C inv,从输入到输出任意找一通路,优化通路延时,手工计算确定通路中每个门对应的晶体管的尺寸。

每组三个同学选择不能为同一通路。

此部分的计算参数可采用书中第六章的参数。

4.7、各种器件的具体结构可参考阎石的《数字电子技术基础》一书。

不允许有完全一样的报告,对于报告完全相同者,记为不及格。

5.使用软件软件为HSPICE和COSMOS-SCOPE。

6.课程设计原理此题目要求用两个四选一多路选择器搭成一个八选一多路选择器,由此可知有八位输入信号,则选择用三位控制信号实现该功能。

由真值表可得两个四选一多路选择器的逻辑表达式分别为:设sel,s1,s2为控制信号,c1-c8为选择输入信号,out1,out2为选择器输出。

Out1=nsel*ns1*ns2*c1+nsel*ns2*c2+ nsel*s1*ns2*c3+ nsel*s1*s2*c4 out2=sel*ns1*ns2*c5+sel*ns1*s2*c6+sel* ns1*s2*c7+sel* ns1*s2*c8做出真值表根据逻辑表达式做出电路图sel S1 S2 C1 0 0 0 C2 0 0 1 C3 0 1 0 C4 0 1 1 C5 1 0 0 C6 1 0 1 C7 1 1 0 C81114输入与非门反相器2输入或非门7.课程设计网表*select8_1.lib"e:\lib\h05hvcddtt09v01.lib" tt.subckt inv in outmp1 out in vdd vdd nvp w=2u l=1umn1 out in gnd gnd nvn w=1u l=1u.ends.subckt nand4 a b c d zmp1 z a vdd vdd nvp l=1u w=2ump2 z b vdd vdd nvp l=1u w=2ump3 z c vdd vdd nvp l=1u w=2ump4 z d vdd vdd nvp l=1u w=2umn1 z a 1 gnd nvn l=1u w=4umn2 1 b 2 gnd nvn l=1u w=4umn3 2 c 3 gnd nvn l=1u w=4umn4 3 d gnd gnd nvn l=1u w=4u.ends.subckt select4 sell s11 s22 a b c d selectxnd1 nsell ns11 ns22 a out1 nand4xnd2 nsell ns11 s22 b out2 nand4xnd3 nsell s11 ns22 c out3 nand4xnd4 nsell s11 s22 d out4 nand4xnd5 out1 out2 out3 out4 select nand4xinv1 s11 ns11 invxinv2 s22 ns22 invxinv3 sell nsell inv.ends.subckt nor2 a b outmp1 x a vdd vdd nvp w=4u l=1ump2 out b x vdd nvp w=4u l=1umn1 out a gnd gnd nvn w=1u l=1umn2 out b gnd gnd nvn w=1u l=1u.ends.global vdd gndxselect1 sel s1 s2 c1 c2 c3 c4 select1 select4 xselect2 nsel s1 s2 c5 c6 c7 c8 select2 select4xnor select1 select2 nf nor2xnot nf f invxnot1 sel nsel invvdd vdd gnd 5vsel sel gnd pulse 0 5 50ns 100ps 100ps 50ns 100ns vs1 s1 gnd 0vs2 s2 gnd 0vc1 c1 gnd pulse 5 0 10ns 100ps 100ps 20ns 30ns vc2 c2 gnd 5vc3 c3 gnd 5vc4 c4 gnd pulse 0 5 10ns 100ps 100ps 20ns 30ns vc5 c5 gnd pulse 0 5 10ns 100ps 100ps 20ns 30ns vc6 c6 gnd 5vc7 c7 gnd 5vc8 c8 gnd pulse 5 0 10ns 100ps 100ps 20ns 30ns.tran 50ps 100ns.plot tran v(f).end8.结果及分析分析:由波形知,在前50ns控制信号为sel,s1,s2=000,后50ns控制信号为sel,s1,s2=100。

verilog实现8路数据选择器

《串行数据检测器》实验报告* All right reserved*/module mux_8(addr, in1, in2, in3, in4, in5,in6,in7,in8,mout,ncs); input [2:0] addr; //输入的地址端,3位选择开关input [3:0] in1,in2,in3,in4,in5,in6,in7,in8; //8路数据端输入input ncs; //使能信号output [3:0] mout; //一路输出reg [3:0] mout; //输出声明为寄存器类型always @(addr or in1 or in2 or in3 or in4 or in5 or in6 or in7 or in8 or ncs) //8路输入或者选择开关或者使能信号发生变化则条件触发beginif(!ncs) //低电平使能case(addr)3'b000: mout = in1; //选择开关的3位对应000时,输出等于in1输入;3'b001: mout = in2; //选择开关的3位对应001时,输出等于in1输入;3'b010: mout = in3; //选择开关的3位对应010时,输出等于in1输入;3'b011: mout = in4; //选择开关的3位对应011时,输出等于in1输入;3'b100: mout = in5; //选择开关的3位对应100时,输出等于in1输入;3'b101: mout = in6; //选择开关的3位对应101时,输出等于in1输入;3'b110: mout = in7; //选择开关的3位对应110时,输出等于in1输入;3'b111: mout = in8; //选择开关的3位对应111时,输出等于in1输入;endcaseelsemout = 0; //使能信号高电平时输出一直为0;endendmodule2.编写测试模块test_mux_8.v如下/*** @File test_mux_8.v* @Synopsis 这是8路数据选择器mux_8的测试模块* @Author 陈昊, @* @Version 1* @Date 2010-11-05*//* Copyright(0) 2010-* By* All right reserved*/`timescale 1ns/1nsmodule test_mux_8;wire[3:0] mout; //声明输出为线网型,4位reg [3:0] in1,in2,in3,in4,in5,in6,in7,in8; //声明8路输入信号reg [2:0] addr; //3位的选择开关,寄存型类型reg ncs; //1位的寄存器型使能信号//-------------------------------------------------------------产生测试信号------------------------------------------------------ initialbeginncs=0; //在初始化模块里将使能信号置为0,让选择器正常工作in8={$random}%16; //使用系统任务$random产生一个0至15之间的数in1={$random}%16; //并赋予输入in2={$random}%16;in3={$random}%16;in4={$random}%16;in5={$random}%16;in6={$random}%16;in7={$random}%16;addr=3'b000; //让选择开关的3位初始对应为000.repeat(5) //重复下面的语句块5次,赋5次值 begin#10 in8={$random}%16;in1={$random}%16;in2={$random}%16;in3={$random}%16;in4={$random}%16;in5={$random}%16;in6={$random}%16;in7={$random}%16;addr=addr+1; //每执行一次后改变一次选择开关的值,加1end#10 $stop;end//-------------------------------------------------------------------2.选择Altera STRATIX器件库利用Synplify Pro综合产生的RTL级电路如下五、分析与讨论。

EDA设计8路数据选择器、16位奇偶检验器的设计

大神:枫晓惜

8路数据选择器(每位数据3位输入)

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY EIGHT_XUAN_1 IS PORT( RST: IN STD_LOGIC; A: IN STD_LOGIC_VECTOR(2 DOWNTO 0); --定义A2,A1, A0的端口为输入 D0: IN STD_LOGIC_VECTOR(2 DOWNTO 0); --定义选择端口 D1: IN STD_LOGIC_VECTOR(2 DOWNTO 0); D2: IN STD_LOGIC_VECTOR(2 DOWNTO 0); D3: IN STD_LOGIC_VECTOR(2 DOWNTO 0); D4: IN STD_LOGIC_VECTOR(2 DOWNTO 0); D5: IN STD_LOGIC_VECTOR(2 DOWNTO 0); D6: IN STD_LOGIC_VECTOR(2 DOWNTO 0); D7: IN STD_LOGIC_VECTOR(2 DOWNTO 0); Q: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); --定义Q2,Q1, Q0的端口为输出 END EIGHT_XUAN_1; ARCHITECTURE ART OF EIGHT_XUAN_1 IS SIGNAL Q1: STD_LOGIC_VECTOR(2 DOWNTO 0); --定义信号量

--当复位信号“1”有效,清零 --对信号量赋值,实现选择的功能 --当A的值是“000”是把D0的值

--当A没被列出来时,Q1执行空操作

波形仿真

16位奇偶检验器的设计

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY parity_check IS PORT ( a:IN STD_LOGIC_VECTOR (15 DOWNTO 0); --输入端口 十六位的数据 y:OUT STD_LOGIC); --将其奇 偶校验的结果输出,若为奇数个1 输出为高电平;若为偶数个1输出 为低电平 END parity_check; ARCHITECTURE arch OF parity_check IS BEGIN PROCESS(a) VARIABLE temp:STD_LOGIC; BEGIN temp:='0'; --偶校验初始值设为0,奇校 LOOP temp:=temp XOR a(i); temp END LOOP; y<=temp; END PROCESS; END arch;

实验8 8位十六进制频率计设计

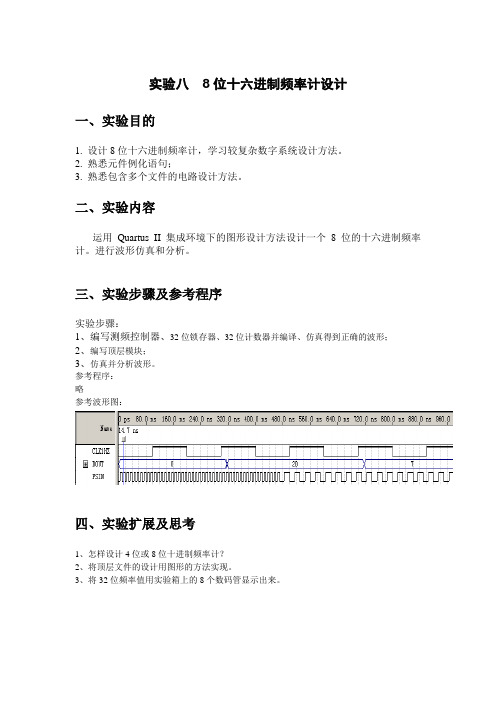

实验八8位十六进制频率计设计

一、实验目的

1. 设计8位十六进制频率计,学习较复杂数字系统设计方法。

2. 熟悉元件例化语句;

3. 熟悉包含多个文件的电路设计方法。

二、实验内容

运用Quartus II 集成环境下的图形设计方法设计一个8位的十六进制频率计。

进行波形仿真和分析。

三、实验步骤及参考程序

实验步骤:

1、编写测频控制器、32位锁存器、32位计数器并编译、仿真得到正确的波形;

2、编写顶层模块;

3、仿真并分析波形。

参考程序:

略

参考波形图:

四、实验扩展及思考

1、怎样设计4位或8位十进制频率计?

2、将顶层文件的设计用图形的方法实现。

3、将32位频率值用实验箱上的8个数码管显示出来。

16位的奇偶校验器设计

课程设计报告学生姓名学号班级电子信息工程院系信院电子系题目16位的奇偶校验器设计指导教师2012 年 5 月题目一:设计一个16位的奇偶校验器,并仿真验证其功能。

(1班1组)(要求:输入一个16位的矢量数值,统计矢量中“1”的个数;并判断16位数中1的个数的奇偶性)1、设计思路2、VHDL程序(或原理图)3、仿真波形(图片)4、程序分析1,设计思路如下:可以使用FOR_LOOP语句,语法格式如下:[LOOP标号: ] FOR 循环变量,IN 循环次数范围LOOP顺序语句END LOOP [LOOP标号];FOR后的“循环变量”是一个临时变量,属LOOP语句的局部变量,不必事先定义。

“循环次数范围”规定LOOP语句中的顺序语句被执行的次数。

循环变量从循环次数数范围的初值开始,每执行完一次顺序语句后递增1,直至达到循环次数范围指定的最大值。

其中定义输入端口十六位的数据总线为a, 输出端口y将其奇偶校验的结果输出, 输出端c统计1 的个数2,VHDL程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY parity_check ISPORT (a:IN STD_LOGIC_VECTOR (15 DOWNTO 0); y:OUT STD_LOGIC;c:out integer range 0 to 16);END parity_check;ARCHITECTURE arch OF parity_check ISBEGINPROCESS(a)V ARIABLE temp:STD_LOGIC;V ARIABLE m: INTEGER RANGE 0 TO 16; BEGINtemp:='0';m:=0; --偶校验初始值设为0,奇校验初始值设为1 FOR i IN 0 TO 15 LOOPtemp:=temp XOR a(i);IF (a(i)='1') THEN m:=m+1;END IF;END LOOP;y<=temp;c<=m;END PROCESS;END arch;原理图如下:3,仿真波形如下:程序分析实体:实体名parity_check输入端口十六位的数据总线a:IN STD_LOGIC_VECTOR (15 DOWNTO 0)输出端口y:OUT STD_LOGIC;将其奇偶校验的结果输出若为奇数个1 输出为高电平;若为偶数个1输出为低电平输出端c:out integer range 0 to 16)统计1 的个数结构体:结构体名arch在进程PROCESS(a)中定义变量V ARIABLE temp:STD_LOGIC;V ARIABLE m: INTEGER RANGE 0 TO 16; 并进行变量的赋值temp:='0';m:=0;loop循环FOR i IN 0 TO 15 LOOPtemp:=temp XOR a(i);IF (a(i)='1') THEN m:=m+1;END IF;END LOOP;Temp与a(i)异或将其结果赋给tempIf语句若a(i)为1 m加1计数将其m的计数结果赋给c c 即为a中1 的个数。

八选一数据选择器逻辑电路设计思路

八选一数据选择器逻辑电路设计思路哎呀,这道题目可真是让人头疼啊!不过,别着急,我们一起来想办法解决这个问题吧!我们来看看这个题目的要求:八选一数据选择器逻辑电路设计思路。

简单来说,就是要我们设计一个逻辑电路,它可以从8个输入信号中选择其中一个输出。

这听起来好像很简单,但是实际上还是有一些细节需要注意的。

那么,我们现在就开始着手解决这个问题吧!我们需要明确一下这个逻辑电路的基本结构。

一般来说,这种类型的逻辑电路通常由触发器和多路复用器组成。

触发器可以用来存储输入信号的状态,而多路复用器则可以用来选择不同的输入信号进行处理。

接下来,我们需要考虑一下具体的实现方法。

对于这个问题,我们可以使用两个触发器和三个多路复用器来实现。

具体来说,我们可以将第一个触发器的Q0引脚连接到第二个触发器的D引脚上,这样就可以实现第一个触发器的输出与第二个触发器的输入相同。

然后,我们将第一个触发器的Q1引脚连接到第三个多路复用器的A引脚上,将第一个触发器的Q2引脚连接到第四个多路复用器的A引脚上,将第一个触发器的Q3引脚连接到第五个多路复用器的A引脚上,将第一个触发器的Q4引脚连接到第六个多路复用器的A引脚上,将第一个触发器的Q5引脚连接到第七个多路复用器的A引脚上,将第一个触发器的Q6引脚连接到第八个多路复用器的A引脚上。

这样一来,当第一个触发器的输出为1时,第二个触发器的输出就会被选择出来;当第一个触发器的输出为0时,第二个触发器的输出就不会被选择出来。

同样的道理,当第一个触发器的输出为1时,第三个、第四个、第五个、第六个、第七个和第八个多路复用器的输出都会被选择出来;当第一个触发器的输出为0时,这些多路复用器的输出就不会被选择出来。

我们还需要考虑一下如何控制这个逻辑电路的工作状态。

一般来说,我们可以使用一些基本的逻辑门来实现这一点。

比如说,我们可以使用与门来控制触发器的输出是否为高电平;使用或门来控制多路复用器的选择功能是否被激活;使用非门来控制整个逻辑电路的工作状态是否被改变。

八选一数据选择器逻辑电路设计思路

八选一数据选择器逻辑电路设计思路数据选择器逻辑电路设计,让复杂变简单嘿,朋友们!今天咱们来聊一聊那个让人头疼又爱不释手的东西——数据选择器逻辑电路。

别急,让我用轻松幽默的方式,带你一起走进这个小小的“魔法世界”。

想象一下,你手里有一堆颜色各异的糖果,想要选出一种特定的颜色,比如红色。

这听起来是不是有点像我们在设计数据选择器时的挑战?没错,就是那种既需要精准又得巧妙处理的选择难题。

你得知道数据选择器是什么。

简单来说,它就像是个小魔术师,能够从一大堆数据中,挑选出你想要的那一个。

但它可不是随便选一个就行,而是要根据输入的信号来决定输出的。

这个过程就像是一场智慧与勇气的较量,既要有策略,又要有胆量。

接下来,咱们说说设计思路。

设计数据选择器的时候,你得先搞清楚你要控制的是哪一类信号。

比如,你是想控制数字信号还是模拟信号?是单端还是差分信号?这些问题就像是一座座山,只有越过它们,你才能找到通往成功的道路。

然后,你需要规划你的电路结构。

想象一下,你正在搭建一座城堡,每个元件就像是城堡里的一间房,而你的设计思路就像是城堡的蓝图。

你得确保所有的房间都按照计划建造好,这样才能保证城堡稳固、美观。

当然啦,设计过程中难免会遇到一些“小麻烦”。

比如,有时候信号可能会混在一起,让你难以分辨哪个才是你想要的。

这时候,你得学会运用各种“技巧”,比如滤波器、多路复用器等等,来帮助你解决问题。

别忘了测试和调试。

就像战士在战斗结束后要检验战利品一样,你在完成设计后也要对电路进行测试,确保它能够正常工作,没有遗漏任何细节。

数据选择器逻辑电路的设计并不是一件容易的事情,但只要你有耐心、细心,再加上一点点创意和想象力,你一定能够成为那个出色的“魔法师”。

在这个过程中,你会发现自己不仅学会了如何解决问题,还收获了成长和快乐。

所以,不要害怕挑战,勇敢地去迎接吧!。

8路数据选择器、16位奇偶检验器的设计.

课程设计报告(理工类)课程名称: EDA技术专业班级:电子科学与技术102 学生学号: 050210109 学生姓名:江杰所属院部:物电学院指导教师:顾涵20 12 ——20 13 学年第 1 学期设计项目名称:8位数据选择器与16位奇偶校验器设计同组学生姓名:张海军、贺旌、蒋宁洲实验地点:力行楼203 设计成绩:批改教师:批改时间:一、设计目的和要求1.课程设计目的本实验课程的目的,旨在通过上机实验自己进行EDA设计,使学生加深理解EDA技术的基本方法,帮助和培养学生建立利用原理图和硬件描述语言进行电路设计的基本方法和利用EDA工具软件(MAX+plusⅡ)设计简单数字电子系统的能力,为以后从事有关数字电子系统方面的设计和研究开发工作打下基础。

2.课程设计的基本要求1、通过课程设计使学生能熟练掌握一种EDA软件(MAXPLUS2)的使用方法,能熟练进行设计输入、编译、管脚分配、下载等过程。

2、通过课程设计使学生能利用EDA软件(MAXPLUS2)进行至少一个电子技术综合问题的设计(内容可由老师指定或自由选择),设计输入可采用图形输入法或AHDL硬件描述语言输入法。

3、通过课程设计使学生初步具有分析、寻找和排除电子电路中常见故障的能力。

4、通过课程设计使学生能独立写出严谨的、有理论根据的、实事求是的、文理通顺的字迹端正的课程设计报告。

3.课程设计类型EDA技术VHDL程序设计二、仪器和设备计算机,MAX+plusⅡ软件三、设计过程1.设计内容和要求a).设计一个八选一数据选择器,同时每一个输入端口又由3个二进制位组成,输出端口是从前八个端口选择一个由3个二进制位组成的端口。

b).设计一个16位奇偶校验器,对输入的信号进行统计奇数或者偶数的数量。

将其奇偶校验的结果输出,若为奇数个 1 输出为高电平;若为偶数个1输出为低电平2.设计方法和开发步骤a).方法:查阅相关资料,找到对于一个四选一数据选择器和8位奇偶校验器的介绍,运用类比的方法写出设计所需要的程序。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计报告(理工类)课程名称: EDA技术专业班级:电子科学与技术102 学生学号: ********* 学生姓名:江杰所属院部:物电学院指导教师:顾涵20 12 ——20 13 学年第 1 学期设计项目名称:8位数据选择器与16位奇偶校验器设计同组学生姓名:张海军、贺旌、蒋宁洲实验地点:力行楼203 设计成绩:批改教师:批改时间:一、设计目的和要求1.课程设计目的本实验课程的目的,旨在通过上机实验自己进行EDA设计,使学生加深理解EDA技术的基本方法,帮助和培养学生建立利用原理图和硬件描述语言进行电路设计的基本方法和利用EDA工具软件(MAX+plusⅡ)设计简单数字电子系统的能力,为以后从事有关数字电子系统方面的设计和研究开发工作打下基础。

2.课程设计的基本要求1、通过课程设计使学生能熟练掌握一种EDA软件(MAXPLUS2)的使用方法,能熟练进行设计输入、编译、管脚分配、下载等过程。

2、通过课程设计使学生能利用EDA软件(MAXPLUS2)进行至少一个电子技术综合问题的设计(内容可由老师指定或自由选择),设计输入可采用图形输入法或AHDL硬件描述语言输入法。

3、通过课程设计使学生初步具有分析、寻找和排除电子电路中常见故障的能力。

4、通过课程设计使学生能独立写出严谨的、有理论根据的、实事求是的、文理通顺的字迹端正的课程设计报告。

3.课程设计类型EDA技术VHDL程序设计二、仪器和设备计算机,MAX+plusⅡ软件三、设计过程1.设计内容和要求a).设计一个八选一数据选择器,同时每一个输入端口又由3个二进制位组成,输出端口是从前八个端口选择一个由3个二进制位组成的端口。

b).设计一个16位奇偶校验器,对输入的信号进行统计奇数或者偶数的数量。

将其奇偶校验的结果输出,若为奇数个 1 输出为高电平;若为偶数个1输出为低电平2.设计方法和开发步骤a).方法:查阅相关资料,找到对于一个四选一数据选择器和8位奇偶校验器的介绍,运用类比的方法写出设计所需要的程序。

b).步骤:Ⅰ去图书馆查找相关资料,了解基本原理;Ⅱ写出真值表,根据真值表分析程序结构;Ⅲ确定输入输出,且数据选择器使用case语句,奇偶校验器使用loop结构;Ⅳ参考四选一数据选择器,,8位奇偶校验器,写出VHDL程序;综合编译,仿真,并进一步完善。

3.设计思路a)八选一数据选择器执行对8个数据源的选择,d0,d1,d2,d3,d4,d5,d 6,d7 定义为七个数据输入端口作为数据输入端。

使用三位地址码产生8个地址信号,由a0a1a2选择信号,从而实现y的选择输出。

真值表如下:又因为我们的每个输入端口又由3个二进制位组成,输出又由某一个端口的三个二进制位组成,只要再把每一个输入端口,输出端口设成具有3个的位矢量,然后再做其余的相应修改即可。

b)可以使用FOR_LOOP语句,语法格式如下:[LOOP标号: ] FOR 循环变量,IN 循环次数范围LOOP顺序语句END LOOP [LOOP标号];FOR后的“循环变量”是一个临时变量,属LOOP语句的局部变量,不必事先定义。

“循环次数范围”规定LOOP语句中的顺序语句被执行的次数。

循环变量从循环次数数范围的初值开始,每执行完一次顺序语句后递增1,直至达到循环次数范围指定的最大值。

其中定义输入端口十六位的数据总线为a, 输出端口y将其奇偶校验的结果输出。

4.设计难点a )在设计数据选择器的时候没有理解输入输出端口还是由3个二进制位组成,理解出错,还用元件例化的方法走了不少弯路。

b )16位奇偶校验器由于对for ..loop 语句的不熟悉调试不少时间。

四、设计结果与分析1.思路问题以及测试结果失败分析a )由于八选一数据选择器比较的简单,大体的程序编写出来了,由于刚开始没理解要求,输入输出都要求是由3个二进制位组成,按着自己的错误理解进行再修改而没有成功,最后在老师的又一次讲述下听懂了要求,然后很快就出来了。

b.)16位奇偶校验器调试着几次就没什么问题了。

2.程序简要说明VHDL代码如下八选一数据选择器(每个输入输出端口都是由3个二进制位组成)LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY EIGHT_XUAN_1 ISPORT(RST: IN STD_LOGIC;A: IN STD_LOGIC_VECTOR(2 DOWNTO 0); --定义A2,A1,A0的端口为输入D0: IN STD_LOGIC_VECTOR(2 DOWNTO 0);D1: IN STD_LOGIC_VECTOR(2 DOWNTO 0);D2: IN STD_LOGIC_VECTOR(2 DOWNTO 0);D3: IN STD_LOGIC_VECTOR(2 DOWNTO 0);D4: IN STD_LOGIC_VECTOR(2 DOWNTO 0);D5: IN STD_LOGIC_VECTOR(2 DOWNTO 0);D6: IN STD_LOGIC_VECTOR(2 DOWNTO 0);D7: IN STD_LOGIC_VECTOR(2 DOWNTO 0);Q: OUT STD_LOGIC_VECTOR(2 DOWNTO 0)); --定义Q2,Q1,Q0的端口为输出END EIGHT_XUAN_1;ARCHITECTURE ART OF EIGHT_XUAN_1 ISSIGNAL Q1: STD_LOGIC_VECTOR(2 DOWNTO 0); --定义信号量BEGINPROCESS(A)BEGINIF RST='1' THEN Q1<="000"; --当复位信号“1”有效,清零ELSECASE A IS --对信号量赋值,实现选择的功能WHEN "000"=> Q1 <= D0;WHEN "001"=> Q1 <= D1;WHEN "010"=> Q1 <= D2;WHEN "011"=> Q1 <= D3;WHEN "100"=> Q1 <= D4;WHEN "101"=> Q1 <= D5;WHEN "110"=> Q1 <= D6;WHEN "111"=> Q1 <= D7;WHEN OTHERS => NULL; --当A没被列出来时,Q1执行空操作END CASE;END IF;END PROCESS;Q<= Q1;END ART;仿真波形如下:16位奇偶检验器设计LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY parity_check ISPORT (a:IN STD_LOGIC_VECTOR (15 DOWNTO 0); --输入端口十六位的数据y:OUT STD_LOGIC); --将其奇偶校验的结果输出,若为奇数个1 输出为高电平;若为偶数个1输出为低电平END parity_check;ARCHITECTURE arch OF parity_check ISBEGINPROCESS(a)V ARIABLE temp:STD_LOGIC;BEGINtemp:='0'; --偶校验初始值设为0,奇校验初始值设为1FOR i IN 0 TO 15 LOOPtemp:=temp XOR a(i); --Temp与a(i)异或将其结果赋给tempEND LOOP;y<=temp;END PROCESS;END arch;仿真波形如下:五、实验心得体会通过本次课程设计的学习,我深深的体会到设计课的重要性和目的性。

本次设计课不仅仅培养了我们实际操作能力,也培养了我们灵活运用课本知识,理论联系实际,独立自主的进行设计的能力。

它不仅仅是一个学习新知识新方法的好机会,同时也是对我所学知识的一次综合的检验和复习,使我明白了自己的缺陷所在,从而查漏补缺。

希望学校以后多安排一些类似的实践环节,让同学们学以致用。

虽然软件的仿真功能很强大,但是还是需要操作人员仔细的进行观察及调试的,否则也容易出现仿真错误。

在设计中要求我要有耐心和毅力,还要细心,稍有不慎,一个小小的错误就会导致结果的不正确,而对错误的检查要求我要有足够的耐心,通过这次设计和设计中遇到的问题,也积累了一定的经验,对以后从事集成电路设计工作会有一定的帮助。

在应用VHDL的过程中让我真正领会到了其并行运行与其他软件顺序执行的差别及其在电路设计上的优越性。

用VHDL硬件描述语言的形式来进行数字系统的设计方便灵活,利用EDA软件进行编译优化仿真极大地减少了电路设计时间和可能发生的错误,降低了开发成本,这种设计方法必将在未来的数字系统设计中发挥越来越重要的作用。

六、参考文献1.刘江海等.EDA技术.华中科技大学出版社,2009.2. 李国洪等. 可编程器件EDA设计与实践.机械工业出版社,2004.3. 康华光等。

电子技术基础.高等教育出版社,2005.。