JFET_OpAmp_characteristics

高速相机皮秒级可编程延迟单元电路设计

Cj

I

刘 春 平 ,龚 向东 ,黄 虹 宾 。 景 镇 李

( 圳 市微 纳 光 子信 息 技 术 重 点 实 验 室 ,深 圳 5 8 6 ) 深 1 0 0

摘 要 :纳 秒 ( s 和 亚 纳 秒 高速 相 机 各 部 件 之 间 需 要 精 密 的 可 编 程 时 间 延 迟 来 保 证 同 步 。本 文 提 出一 种 基 于 EP D 和 n) L AS C, 字 和模 拟 时 间 延 迟 相 结合 的 解 决 方 案 , 时 长 度 可 编 程 , 时 分 辨 率 可 达 皮 秒 ( s 级 。 该 系统 体 积 小 , 本 低 , I 数 延 延 p) 成 可 实现 参 数 设 置 、 示和 控 制 等 功 能 。 显 关 键 词 :精 密 时 间 延 迟 ;可 编 程 器件 ;专 用 集成 电路 ;高速 相 机

i p ogr m m a e a he r s l ton i o pio s c nd l v 1 Thes s e ss alv u e a d lw o t nd c n beus d f a a e e s r a bl nd t e o u i sup t c e o e e . y t m ha m l ol m n o c s ,a a e orp r m t r s ti e tng,dipl y a d c nto1 s a n o r . Ke o d y w r s: p e ietm ede a r cs i l y; p o a m ab ede ie;A SI ; h gh s e d c m e a r gr m l vc C i p e a r

延 迟 通 常 是 让 信 号 沿 导 体 传播 , 过 控 制 导 体 的 长 短 来 控 通 制 时 延 。如 果 选 择 电信 号 或 光 信 号 , 于 传 播 速 度 快 , 由 可 以获 得 很 高 的延 时 精 度 , 电缆 或 光 纤 会 比较 长 , 迟 单 但 延

IP113CLF原厂资料

10 /100Base-Tx/Fx Media ConverterFeaturesA 10/100BASE-TX/ 100BASE-FX converter Built in a 10/100BASE-TX transceiverBuilt in a PHY for 100BASE-FXBuilt in a 2-port switch– Pass all packets without address andCRC check (optional)– Supports modified cut-through frameforwarding for low latency– Supports pure converter mode dataforwarding for extreme low latency – Supports flow control for full and halfduplex operation– Bandwidth control– Forward 1600 bytes packet formanagement– Optional forward fragmentsBuilt in 128Kb RAM for data bufferSupports auto MDI-MDIX functionSupports link fault pass through functionSupports far end fault functionLED display for link/activity, full/half, 10/100 Built in a watchdog timer to monitor internal switch errorSupports EEPROM Configuration0.25u CMOS technologySingle 2.5V power supply48-pin LQFP packageSupport Lead Free package (Please refer to the Order Information) General DescriptionIP113C LF can be a 10/100BASE-TX to 100BASE-FX converter. It consists of a 2-port switch controller, a fast Ethernet transceiver and a PHY for 100BASE-FX. The transceivers in IP113C LF are designed in DSP approach with advance 0.25-um technology; this results in high noise immunity and robust performance.IP113C LF not only supports store and forward mode, it also supports modified cut through mode and pure converter mode for low latency data forwarding. IP113C LF can transmit packet(s) up to 1600 bytes to meet requirement of extra long packets.IP113C LF supports IEEE802.3x, collision base backpressure, and various LED functions, etc. These functions can be configured to fit the different requirements by feeding operation parameters via EEPROM interface or pull up/down resistors on specified pins.Block DiagramRevision HistoryRevision # Change DescriptionIP113C LF-DS-R01 Initial release.IP113C LF-DS-R02 Remove Operation Junction Temperature.IP113C LF-DS-R03 TP port should be linked at 100M full duplex when working at this mode.IP113C LF-DS-R04 Add the order information for lead free package.IP113C LF-DS-R05 Revise the diagram.IP113C LF-DS-R06 TP_FORCE (Pin24) &X_EN(Pin29)It is an input pin during reset period. The default value is latched at the end of reset. IP113C LF-DS-R07 Remove internal pull-high resistance & pull-low resistance on page 5.Modify the IPL : pull-low and IPH : pull-highIP113C LF-DS-R08 Add Power Pin description on Page10Application DiagramApplicationsUn-managed converter10B A S E_T/100B A S E-TX100B A S E-F XPIN DiagramN CF A S T _F W DG N D R X IP L F PG N D A 1A V C C G N D T X O M A V C C R X IM F X R D M D I R E C T _W I R E V C C F X S D F X T D P F X T D M N CT S M R E S E T B T S E X _E N L E D _F X _F E F _D E T / D U P L E X _M O D E L E D _T P _F D X L E D _T P _L IN KL E D _F X _L IN K / F X _F U L L L E D _F X _S D / S P E E D _M O D EV C C X 2G N D V C C O S C I S D A S C L / A 0N C V C C B G R E SV C C _IO G N D _IO G N DL E D _F X _F D X / A 2T X O P F X R D P A V C C N CT P _F O R C EL E D _T P _S P D1. PIN DescriptionType DescriptionpinI InputpinO OutputIPL Input pin with internal pull-low resistor.IPH Input pin with internal pull-high resistor.Pin no. Label Type DescriptionTransceiver5, 6 RXIP, RXIM I TP receive8, 9 TXOP, TXOM O TP transmit2 BGRES OBand gap resistorIt is connected to GND through a 6.19k (1%) resistor inapplication circuit.18 FXSD I100Base-FX signal detectFiber signal detect. It is an input signal from fiber MAU.Fiber signal detect is active if the voltage on FXSD is higherthan the threshold voltage, which is 1.35v ±5% when VCCis equal to 2.5v.13, 14 FXRDP, FXRDM I Fiber receiver data pairCommon-mode voltage of FXRDP and FXRDM aresuggested to near 0.5x AVCC.When voltage peak-to-peak>0.1V,FXRX could beworkable.16, 17 FXTDP, FXTDM O Fiber transmitter data pairFXTX with the external 100Ωresistor.Common-mode voltage of FXTDP and FXTDM aresuggested to near 0.5x AVCC.Swing of Voltage ≧ 0.8V.1. PIN Description (continued)Pin no. Label Type DescriptionLED pins31 LED_TP_LINK OTP port link LEDOn: link ok, Off: link fail, Flash: link ok & activity(Flash: on for 20ms and off for 80ms)33 LED_TP_SPD OTP port speed LEDOn: 100M, Off: 10M32 LED_TP_FDX OTP port full duplex LEDOn: full, Off: half,Flash: half & collision happens(Flash: on for 20ms and off for 80ms)36 LED_FX_LINK OFiber port link LEDOn: link ok, Off: link fail, Flash: link ok & activity(Flash: on for 20ms and off for 80ms)37 LED_FX_FDX OFiber port full duplex LEDOn: full, Off: half, Flash: half & collision happens(Flash: on for 20ms and off for 80ms)38 LED_FX_SD Fiber port signal detectOn: fiber signal detected, Off: fiber unplugged30 LED_FX_FEF_DETOFar end fault pattern receivedFor End Fault Patterns ReceiveLED On: 80ms, LED Off: 20msFor End Fault Pattern not ReceiveLED always OffNote: The output of LED pin is logic low when the LED is on.1. PIN Description (continued)Pin no. Label Type DescriptionMC operation mode29 X_EN O/IPH IEEE 802.3X enable on TP port and fiber port1: enable (default),0: disableIt is an input pin during reset period. The default value islatched at the end of reset.After reset, it becomes an output pin for testing.It should be connected to GND through a 1k ohm resisterto set 0.24 TP_FORCE O/IPL Local TP port auto negotiation enable1: TP port supports auto-negotiation with limited capabilitydefined in SPEED_MODE and DUPLEX_MODE.0: TP port supports auto-negotiation with 10M/100M, full/half capability (default)The default value may be updated by either programmingEEPROM register 3.5 or MII register 20.13.It is an input pin during reset period. The default value islatched at the end of reset.After reset, it becomes an output pin for testing.It should be connected to VCC through a 1k ohm resisterto set 1.38 SPEED_MODE IPHLocal TP port speed1: TP port has the 100Mb speed ability0: TP port has the 10Mb speed ability onlyIt is valid only if TP_FORCE is enabled.IPH30 DUPLEX_MODELocal TP port duplex1: TP port has the Full duplex ability0: TP port has the Half duplex ability onlyIt is valid only if TP_FORCE is enabled.36 FX_FULL IPHSet the duplex of fiber port1: full duplex (default)0: half duplex1. PIN Description (continued)Pin no. Label Type Description MC operation mode1. PIN Description (continued)Pin no. Label Type DescriptionMC operation mode21 LFP IPLLink fault pass through (LFP)1: enableLink status of one port is forwarded to the other port.0: disable (default)22, 23 DIRECT_WIRE,FAST_FWDIPL DIRECT_WIREFAST_FWD Function0 0 Store and forward switch mode(default)0 1 Modified cut-through switchmode1 0 Converter mode1 1 Converter mode withauto-change-forward functionStore and forward switch mode:IP113C LF will begin to transmit a frame right after thecompletion of receiving a frame.Modified cut-through switch mode:IP113C LF will begin to forward a frame after the first 64bytes data received. TP port should be forced at 100M atthis mode.Converter mode:Incoming frames are not buffered in IP113C LF to achievethe min latency. Both TP port and fiber port of IP113C LFshould work at 100M full duplex in this mode. If TP port islinked at half duplex, the total length of UTP cable and fibershould be less than 60 meters to meet the requirement ofCSMACD in IEEE802.3.Converter mode with auto-change-forward function:IP113C LF will change to forward mode if it detects thespeed is different in TP port and FX port.In converter mode, IP113C LF forwards IEEE802.3x pauseframe directly. In the other modes, IP113C LF doesn’tforward IEEE802.3x pause frame directly, it sends outpause frame when its internal buffer is full.1. PIN Description (continued)Pin no. Label Type DescriptionEEPROM interface45, 46 SDA, SCL IPH, O EEPROM interface37, 12, 46A[2:0] IPLPHY addressIP113C LF uses A[2:0] as EEPROM address to readEPROM.Pin no. Label Type DescriptionMisc.28 RESETB IResetIt is low active.41, 40 OSCI, X2 I, O Crystal pinsOSCI and X2 are connected to a 25Mhz crystal.If a 25MHz oscillator is used, OSCI is connected to theoscillator’s output and X2 should be left open.26, 27 TSM, TSE IPL Scan pinsThese two pins should be left open or connected to groundfor normal operation.Pin no. Label Type DescriptionPower1,7,11 AVCC 2.5VAnalogPower19,39,44 VCC 2.5V Digital Power34 VCC_IO 3.3V or 2.5V Digital Power35 GND_IO I/OGround4,10,20, 42,43 GNDGround2. Functional DescriptionData forwardingIP113C LF supports three types of data forwarding mode, store & forward mode, modified cut-through mode and pure converter mode. It can forward a frame despite of its address and CRC error. IP113C LF begins to forward the received data only after it receives the frame completely. The latency depends on the packet length.Modified cut-through modeIP113C LF begins to forward the received data when it receives the first 64 bytes of the frame. The latency is about 512 bits time width. The maximum packet length can be up to1600 bytes in this mode. Please refer to the pin description of FAST_FWD for configuration information.Pure converter modeIP113C LF operates with the minimum latency in this mode. The transmission flow does not wait until entire frame is ready, but instead it forwards the received data immediately after the data being received. Both transceivers are interconnected via internal MII signals, therefore the internal switch engine and data buffer are not used. Both TP port and fiber port of IP113C LF should work at 100M full duplex in this mode. If TP port is linked at half duplex, the total length of UTP cable and fiber should be less than 60 meters to meet the requirement of CSMACD in IEEE802.3.The packet length is not limited at this mode. Please see pin description of DIRECT_WIRE for configuration information.Fragment forwardingIP113C LF forwards CRC error packets but it will filter fragments when it works in modified cut-through mode. IP113C LF forwards fragments if user turns on bit 3 of EEPROM register 2.TP port force modeThe TP port of IP113C LF can work at auto mode or force mode. The following table shows all of the combination of its TP port.Link partner’s capabilityAN on AN off{TP_FORCE,IP113C LF’s link result100F100H10F10H100F 100H 10F10H SPEED_MODE,DUPLEX_MODE} IP113C LF’s capability011 100/10M, Full/Half, AN on 100F100H10F10H100H 100H 10H10H 010 100/10M, Half, AN on X 100H X 10H100H 100H 10H10H 001 10M, Full/Half, AN on X X 10F10H100H 100H 10H10H 000 10M, Half, AN on X X X 10H100H 100H 10H10H 111 100M, Full, AN on 100F X X X 100F 100F X X 110 100M, Half, AN on X 100H X X 100H 100H X X 101 10M, Full, AN on X X 10F X X X 10F10F 100 10M, Half, AN on X X X 10H X X 10H10H Note:AN on: with auto-negotiation capabilityAN off: without auto-negotiation capability100F: 100M full duplex100H: 100M half duplex10F: 10M full duplex10H: 10M half duplexLink fault pass throughWhen link fault pass through function is enabled, link status on TX port will inform the FX port of the same device and vice versa. From the link fault pass through procedure illustrates in the figure below, if link fail happens on IP113C LF’s TX port (1), the local FX port sends non-idle pattern to notice the remote FX port (2). The remote FX port then forces its TX port to link failed after receiving the non-idle pattern (4). In other words, this mechanism will alert the link fault status of local TX port to the remote converter’s TX port, and the link status of the remote TX port will become off. Link status LED will also be off for both IP113C LF and its link partner.(1) TP port link failedThe procedure of link fault pass through(3) fiber port gets remote link fault information (4) TP link fail(5) remote TPlink is offnon-idle patternNormal caseLED SW1LED_TP_LINK1LED_FX_LINK1LEDSW2localremote LED_FX_LINK2LED_TP_LINK2Link LED onSW1LED_TP_LINK1 LED_FX_LINK1LED_FX_LINK2LED_TP_LINK2Link LED onSW2ON ON ON ON ON ONRemote TP port disconnectedIP113C LF IP113C LFFiberSwitch1Switch2 LED SW1LED SW2local remote LED_TP_LINK1LED_FX_LINK1LED_FX_LINK2LED_TP_LINK2UTPUTPdisconnectLink LED onSW1 LED_TP_LINK1 LED_FX_LINK1LED_FX_LINK2LED_TP_LINK2Link LED onSW2Off Off Off Off Off OffFX port disconnectedIP113CLF IP113CLFUTP UTFiber P Switch1 Switch2LEDSW1LED_TP_LINK1LED_FX_LINK1LEDSW2localremoteLED_FX_LINK2LED_TP_LINK2Link LED onSW1 LED_TP_LINK1 LED_FX_LINK1LED_FX_LINK2LED_TP_LINK2Link LED onSW2Off Off Off Off Off OffLED diagnostic functions for fault indicationLED_TP_LINK LED_FX_LINK LED_FX_SD LED_FX_FEF_DET Status On On On Off Linkok Flash Flash On Off Link ok & activityOff Off On Off Remote TP link offOff Off Off Off Fiber RX off, Fiber TX/ RX offOff Off On Flash FiberTXoff NoteFlash: flash, period 100 msLink fault pass through is enabled.EEPROM – store the initial valueIP113C LF supports two ways to load initial value of MII registers. The procedure is illustrated as below.1. IP113C LF reads the default setting of MII register from pins2. IP113C LF updates the default setting of MII by reading EEPROM. If there exists an EEPROM3. After reading EEPROM, IP113C LF is virtually isolated from the EEPROM. Micro-controller can program both MII register and EEPROM.4. IP113C LF reloads the content of EEPROM to recover the value in MII registers programmed by Micro-controller after power on reset.Auto MDI_MDIXIP113C LF supports auto MDI-MDIX. It is always enabled. The following is its application circuit for auto MDI-MDIX.GND GNDIP113C LF's application circuit (auto MDI-MDIX on)EEPROM registersType Description Type Description R/W Read/Write RC Read and ClearSC Self-Clearing LL LatchingLow RO Read Only LH Latching HighPin(1) The default value is “1” and it dependson the setting of its corresponding pin.Pin(0) The default value is “0” and it dependson the setting of its corresponding pin.ROM NAME R/W DESCRIPTION DEFAULT EEPROM enable register 00[7:0] --EEPROM enable register 0This register should be filled with 55. IP113C LFwill examine the specified pattern to confirm ifthere is a valid EEPROM.55hROM NAME R/W DESCRIPTION DEFAULT EEPROM enable register 11[7:0] --EEPROM enable register 1This register should be filled with AA. IP113C LFwill examine the specified pattern to confirm ifthere is a valid EEPROM. The initial setting isupdated with the content of EEPROM only if thespecified pattern 55AA is found.AAhEEPROM registers (continued)ROM NAME R/W DESCRIPTION DEFAULT Switch configuration register 12.0 reserved -- The default value must be adopted for normaloperation.2.1 direct_wire -- Please see pin description of DIRECT_WIRE formore detail information.Pin (0)2.2 fast_fwd -- Please see pin description of FAST_FWD for moredetail information.Pin (0)2.3 mg_pass_fragment_en -- Pass fragment packet (>7B and <64B)1: pass fragment0: not pass fragment2.4 mg_col16_drop_en -- Collision 16 times drop enable1: drop0: not drop2.5 mg_col_backoff_en -- Collision back-off enable1: back after collision0: not back off after collision12.6 reserved --Thedefaultvalue must be adopted for normaloperation.2.7 p01_mg_backpress_en -- TP port backpressure control enable for halfduplex1: backpressure enable0: backpressure disable1 3.0 reserved --Thedefaultvalue must be adopted for normaloperation.0 3.1 reserved --Thedefaultvalue must be adopted for normaloperation.3.2 reserved -- The default value must be adopted for normaloperation.1 3.3 reserved --Thedefaultvalue must be adopted for normaloperation.1 3.4 mg_em_bist_en --SSRAM BIST enable (R/W by EEPROM only)1: BIST enable0: bypass BIST13.5 tp_force -- This pin overwrites the setting on pin 26TP_FORCE.Pin (0)3.6 mg_receive_en -- TP receive enable1: TP port can receive packet0: TP port drop all received packet1 3.7 reserved --Thedefaultvalue must be adopted for normaloperation.ROM NAME R/W DESCRIPTION DEFAULT Switch configuration register 2port allocated memory pages120d 4[7:0] p01_mg_port_page_no -- TPThe default is 120 pages with 64 bytes per page.120dport allocated memory pages5[7:0] p02_mg_port_page_no -- FXThe default is 120 pages with 64 bytes per page.Note: p01_mg_port_page_no adds p02_mg_port_page_no must be equal to 240.EEPROM registers (continued)ROM NAME R/W DESCRIPTION DEFAULT Local MC extended registervalue must be adopted for normaldefault6.0 reserved --Theoperation.value must be adopted for normaldefaultThe6.1 reserved --operation.6.2 p01_mg_auto_neg_en -- TP port auto-negotiation enable11: TP auto-negotiation enable0: TP auto-negotiation disable16.3 p01_mg_speed_mode -- TP port speed selection1: 100M, 0:10M6.4 p01_mg_duplex_mode -- TP port duplex mode selection11: full duplex, 0:half duplex16.5 p01_mg_flow_ctrl_en -- TP port flow control selection1: on, 0:offdefaultvalue must be adopted for normalThe6.6 reserved --operation.flow control/backpressure enablePin (1)port6.7 p02_mg_flow_ctrl_en -- Fiber1: enable, 0: disable17.0 p02_mg_duplex_mode -- Fiber port duplex mode (FX_FULL)1: full duplex, 0:half duplex7.1 reserved -- The default value must be adopted for normal1operation.7.2 reserved -- The default value must be adopted for normaloperation.7[4:3] p01_mg_throttle_confg -- TP port input Rate Control002'b00: full speed2'b01: 1/4 speed2'b10: 2/4 speed2'b11: 3/4 speed7[6:5] p01_mg_throttle_confg -- TP port output Rate Control002'b00: full speed2'b01: 1/4 speed2'b10: 2/4 speed2'b11: 3/4 speed17.7 mg_link_pass_en -- Link Fault Pass through enable (LFP)1: enable, 0: disable3. Signal RequirementsAbsolute Maximum RatingStresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. Functional performance and device reliability are not guaranteed under these conditions. All voltages are specified with respect to GND.Supply Voltage –0.3V to Vcc+0.3VInput Voltage –0.3V to Vcc+0.3VOutput Voltage –0.3V to Vcc+0.3VStorage Temperature -55°C to 125°CAmbient Operating Temperature (Ta) 0°C to 70°CDC CharacteristicOperating ConditionsParameter Sym. Min. Typ. Max. Unit Conditions Supply Voltage VCC 2.375 2.5 2.625VPower Consumption 0.475 WVCC=2.5v Input ClockParameter Sym. Min. Typ. Max. Unit Conditions Frequency 25 MHzFrequencyTolerance -100 +100PPMI/O Electrical CharacteristicsParameter Sym. Min. Typ. Max. Unit Conditions Input Low Voltage VIL 0.8 VInput High Voltage VIH 2.0 VOutput Low Voltage VOL 0.4 V IOH=4mAOutput High Voltage VOH VCC_IO-0.4VIOL=4mA4. Order InformationPart No. Package NoticeIP113C48-PIN LQFP -IP113C LF 48-PIN LQFP Lead free5. Package Detail132425363748Notes:1. DIMENSION D & E DO NOT INCLUDE MOLD FLASH OR PROTRUSION.2. DIMENSION b DOES NOT INCLUDE DAMBAR PROTRUSION / INTRUSION.3. MAX. END FLASH IS 0.15MM.4. MAX. DAMBAR PROTRUSION IS 0.13MM.GENERAL APPEARANCE SPEC SHOULD BE BASED ON FINAL VISUAL INSPECTION SPEC.IC Plus Corp.ACTION DYNAMIC TECH(HK) TRADING COMPANYadd:Room1139-1142,Guoli Building,ZhenzhongRoad,Futian District,Shenzhen,China Tel:86-755-82539044 82539193Faxÿ86-755-82539160E-mail:DNSJ@。

MB90F546GSPF中文资料

2

MB90540/540G/545/545G Series

(Continued) • UART 1 With full-duplex double buffer (8-bit length) Clock asynchronized or clock synchronized serial (extended I/O serial) can be used. • External interrupt circuit (8 channels) A module for starting an extended intelligent I/O service (EI2OS) and generating an external interrupt which is triggered by an external input. • Delayed interrupt generation module Generates an interrupt request for switching tasks. • 8/10-bit A/D converter (8 channels) 8/10-bit resolution can be selectively used. Starting by an external trigger input. Conversion time : 26.3 µs • FULL-CAN interfaces MB90540 series : 2 channel MB90545 series : 1 channel Conforming to Version 2.0 Part A and Part B Flexible message buffering (mailbox and FIFO buffering can be mixed) • External bus interface : Maximum address space 16 Mbytes • Package: QFP-100, LQFP-100

噪声信号调理

www.analog.eetchina .com(Part 2)传感器电路的低噪声信号调理作者:Reza Moghimi reza.moghimi@ADI 公司随着模数转换器和数模转换器分辨率的提高以及电源电压的降低,最低有效位(LSB )变得更小,这使得信号调理任务变得更加困难。

由于信号大小更接近于本底噪声,因此,必须对外部和内部噪声源(包括Johnson 、散粒、宽带、闪烁和EMI )进行处理。

不相关的噪声源采用和的平方根(RSS )的形式进行叠加:另一方面,其它相关噪声源,如输入偏置电流消除等,必须采用带有相关因子的RSS 形式进行叠加。

图1所示的是典型信号调理电路中的噪声源,以及可用于反相、同相、差分及其它通用配置的通用公式。

图1:噪声源包含运算放大器的输入电压噪声和输入电流噪声,以及外部电阻的Johnson噪声。

GainNoise Noise V Noise f BW R R Gain Noise RTI out BWloop closed _*_@_57.11___12==+=221122212122322122132][4]*[][44R R R KTR R R R R In R In R R R KTR KTRVn BW NoiseRTI++++++++=−+ 正确的设计方法从传感器及其特征噪声、阻抗、响应和信号幅度入手,实现最低的折合到输入端(RTI)噪声将能够优化信噪比(SNR)。

与先解决增益和功耗需求、然后再努力应对噪声问题的方法相比,围绕着低噪声来解决问题将更加有效。

这是一个重复的过程,首先考虑放大器的工作区:宽带或1/f。

接着,挑选合适的有源器件,设计最佳的噪声特性。

在放大器周围放置无源器件,并限制带宽。

然后分析非噪声需求,如输入阻抗、电源电流和开环增益。

如果没有达到噪声指标,则重复这一过程,直到获得可以接受的解决方案为止。

运算放大器的选择在一些情况下,宽带噪声为22 nV/rt-Hz的运算放大器可能优于宽带噪声为10 nV/rt-Hz的器件。

FPGA pin Loc

IOP100

IOP91 ION91 IOP111 ION111

IO_1x5转换板管脚 J2.17 J5.30 J5.32 J2.14 J2.16

IOP95 ION109 ION100 IOP108 ION102 IOP102 ION107

J5.46 J2.8 J2.19 J2.2 J2.27 J2.25 J2.47

IOP101 ION108 ION101 IOP106 ION118 ION81 IOP97 IOP109 ION97

J2.21 J2.4 J2.23 J2.41 J2.44 J5.392.17 JA41.30 JA41.32 JA42.14 JA42.16

R16 R13 B10 P13 G11 H11 J10

JA42.21 JA42.4 JA42.23 JA42.41 JA42.44 JA41.39 JA42.5 JA42.6 JA42.7

ETH_RXCK ETH_RXDV ETH_RXER ETH_CRS ETH_COL ETH_PHY_MDIO ETH_PHY_MDC ETH_PHY_INT ETH_PHY_RESET

D9 N13 C9 J9 K12 L14 T12 T13 R12

发送时钟 发送数据线 发送数据线 发送数据线 发送数据线 发送数据线 发送数据线 发送数据线 发送数据线 发送时钟 发送错误 发送使能 接收数据线 接收数据线 接收数据线 接收数据线 接收数据线 接收数据线 接收数据线 接收数据线 接收时钟 接收数据有效 接收错误 检验信号 冲突信号 管理接口数据信号 管理接口时钟 中断信号,有效的极性可编程 硬件复位,低有效

USB子板管脚

USB子板信号

IO_P2 IO_1x5转换板信号

88 84 82 80 78 76 74 72 70 68 90 86 100 102 104 106 108 110 112 114 96 98 94 116 118 33 64 92 62

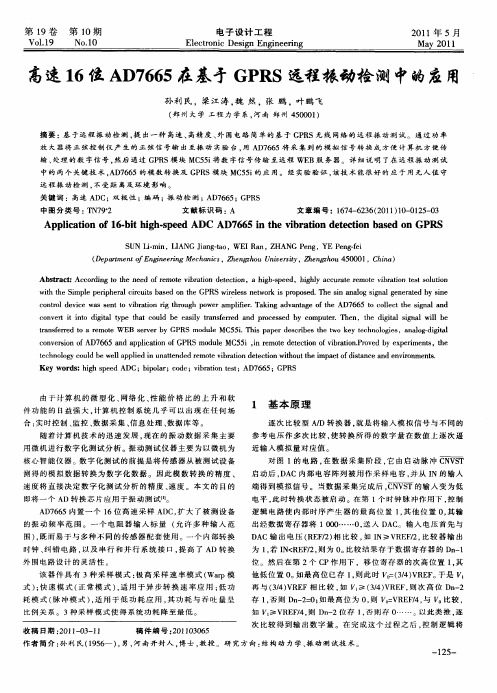

高速16位AD7665在基于GPRS远程振动检测中的应用

作 者 简 介 : 利 民 ( 9 6 ) 男 , 南 开 封人 , 士 , 授 。 研 究 方 向 : 构 动 力 学 、 动 测 试 技 术 。 孙 15 一 , 河 博 教 结 振

— .

1 - 25

《 电子设计 工程) 0 1 第 l 21 年 0期

产 生 AD 转 换 代 码 的 输 出至 并 口( 口) 并 将 BU Y线 的输 串 , S 出置 为 低 电 平[3 z1 -。

c n et i i t ii l tp h t c u d b a i r n f re n r c se y c mp tr h n,t e d gt lsg a i e o v r t n o d g t y e t a o l e e sl ta se r d a d p o e s d b o u e .T e a y h ii in l w l b a l t n fre o a r moe W EB s r e y GP S mo u e MC 5 . h sp p rd s r e h w e e h o o is n l gd gt l r s r d t e t a e e v rb R d l 5 i T i a e e c i st e t o k y t c n l ge ,a a o - ii b a

放 大 器 将 正 弦 控 制 仪 产 生 的 正 弦 信 号 输 出 至 振 动 实 验 台 . AD7 6 用 6 5将 采 集 到 的 模 拟 信 号 转 换 成 方 便 计 算 机 方 便 传

输、 处理 的数 字信 号 , 然后 通过 GP RS模 块 MC 5 将 数 字信 号 传 输 至 远 程 WEB服 务 器 。 详 细 说 明 了在 远 程振 动 测 试 5i 中的 两 个 关键 技 术 , AD7 6 6 5的模 数 转 换 及 G RS模 块 MC 5 P 5 i的应 用 。 经 实验 验 证 , 技 术 能很 好 的 应 于 用 无 人值 守 该

LF356中文资料

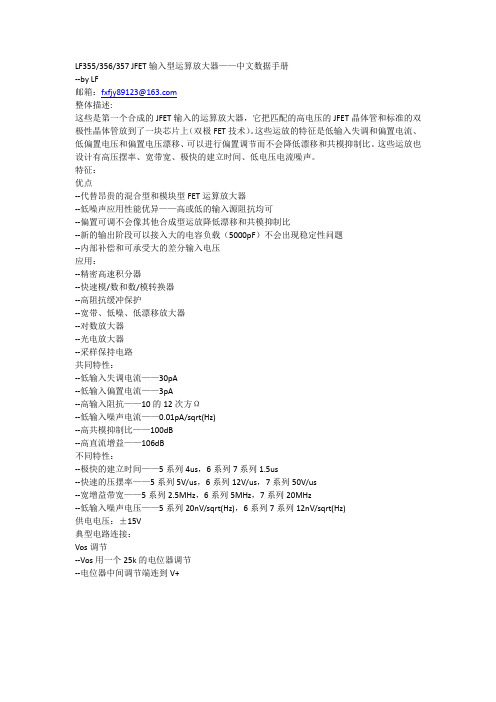

LF355/356/357 JFET输入型运算放大器——中文数据手册--by LF邮箱:fxfjy89123@整体描述:这些是第一个合成的JFET输入的运算放大器,它把匹配的高电压的JFET晶体管和标准的双极性晶体管放到了一块芯片上(双极FET技术)。

这些运放的特征是低输入失调和偏置电流、低偏置电压和偏置电压漂移、可以进行偏置调节而不会降低漂移和共模抑制比。

这些运放也设计有高压摆率、宽带宽、极快的建立时间、低电压电流噪声。

特征:优点--代替昂贵的混合型和模块型FET运算放大器--低噪声应用性能优异——高或低的输入源阻抗均可--偏置可调不会像其他合成型运放降低漂移和共模抑制比--新的输出阶段可以接入大的电容负载(5000pF)不会出现稳定性问题--内部补偿和可承受大的差分输入电压应用:--精密高速积分器--快速模/数和数/模转换器--高阻抗缓冲保护--宽带、低噪、低漂移放大器--对数放大器--光电放大器--采样保持电路共同特性:--低输入失调电流——30pA--低输入偏置电流——3pA--高输入阻抗——10的12次方Ω--低输入噪声电流——0.01pA/sqrt(Hz)--高共模抑制比——100dB--高直流增益——106dB不同特性:--极快的建立时间——5系列4us,6系列7系列1.5us--快速的压摆率——5系列5V/us,6系列12V/us,7系列50V/us--宽增益带宽——5系列2.5MHz,6系列5MHz,7系列20MHz--低输入噪声电压——5系列20nV/sqrt(Hz),6系列7系列12nV/sqrt(Hz)供电电压:±15V典型电路连接:Vos调节--Vos用一个25k的电位器调节--电位器中间调节端连到V+驱动容性负载--对于LF155/6 R=5k--对于LF357 R=1.25k--由于独特的输出平台设计,这些放大器能够驱动大的容性负载并且能保持稳定性。

Cl(MAX)≈0.01uF--建立时间(Ts)≈5us大功率带宽放大器--小于等于1%的失真度,20V峰峰值的输出抖动,功率带宽为500kHz建立时间测试电路--LF155/6连接成单位增益变频器来测试建立时间,LF357连接使得Av=-5--FET用来隔离探头的电容--输出10V步进--对于LF357来说Av = -5宽带低噪低漂移放大器--寄生输入电容C1≈(LF355是3pF,LF356和LF357要加上额外的布局电容)和反馈因素相互作用产生高频极点。

JFET输入音频运算放大器

三个 版本的供 电电流 则更小 ,数据 传输 过MAX4 5 B 9 2 传输的 同时能够有效防止 作 室 设 备 、模 拟 与 数 字 混 合 控 制 台 、音 速率 最高可 达2 M / 。每种 接收 器还 系 统 响 应 噪 声 。 0 bs 具有 ±2 0 0 mA的低输 入电流 ,只有RS

制器 、编码 器 、工厂 自动化和过程 控制 网络理想的设计选 择。

双通道S / A A AS S T 转接驱动器

U C0DE 2 L系列能拒 绝对其EPC G i /

M 9 2 是 双 通道 缓冲 器 ,用 TI A X4 5 B D内存 中的产 品信息进行一般访 问 ,

超 高频R I 解决方案 FD

线应用 中灵敏 度达到一1 d 8 Bm,与之 前

幅 可 预 留 更 多 的 性 能空 间 ;静 态 电流 为

UC E 2L ̄G i+芯片的单 天 每 通 道 1 8 OD G iSI2L F .mA。

可热插拔的l 隔离器 c

的 UC ODE 备 相 比 , 它 只需 一 半 的RF 设

45 线单位负载的 l4 8总 / ,使 总 线 最 多 可 容 纳 18 接 收 器 。 2个

It r l n e si

视频 接收机等 多通道专业音频应 用的需 求 。特性 :噪 声为5 可 ,失真在 nV/ 1 时为0 0 0 5 kHz .0 0 %,即便在高 增益情

况 下 也 可 确 保 出 色 的 信噪  ̄( NR) . tS ;2 5

I 3 1 7 是高数据 速率接收 器 ,最高 的输 入信号被判 断为关 闭,不会通过 器 SL 2 7 E 速 率可达 8 M / ,最大 传播延迟 斜率 件输 出 ;S 0 bs ATA模式下 ,OOB 检测 电路 为 8 ,可确保 器件之 间的 良好 匹配 。 nS

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. Pyroelectric Detectors with JFET source follower or integrated CMOS-OpAmp- A ComparisonJFET on hybridChip ofboardFig.2: Frequency response of signal voltage U S and voltage responsivity R V of a pyroelectric detector with 2mmx2mm active sensing elementIn voltage mode the pyroelectric current, created in the single crystalline LiTaO3 chip, charges the electric capacity. The resulting voltage is displayed by a simple Source follower (JFET, gate resistor and external source resistor).In current mode the generated pyroelectric current is transformed by a Current-Voltage-Converter (OpAmp with feedback components, also named Trans-Impedance-Amplifier TIA). The frequency dependent conversion factor I/U is determined by the complex feedback components and is typically in the range of 10 ... 200 pA/V. While the thermal time constant τT (typically 150ms) as a measure of the thermal coupling of the pyroelectric element to its surrounding is effective in both operation modes, the electric time constant τE is determined by different components. In voltage mode τE is calculated as a product of pyroelectric chip capacity C P and gate resistor R G (typically 1.5s). In current mode τE is only determined by the feedback components R fb and C fb (typically 16ms).Main differences between pyroelectric detectors with JFET and CMOS-OpAmp•At common modulation frequencies between 1Hz and 10Hz in gas analysis and flame detection the detector will operate above the thermal and electrical time constant (1/f behavior of signal). The maximal responsivity is located beyond the normal modulation frequency range. Low-frequency disturbances up to some Millihertz will be transmitted. Detectors need settling times up to some 10 seconds.•Detectors in current mode are mostly operated between both time constants and resultant cut-on and cut-off frequency. Here the signal voltage is on its highest level and stable over a broad frequency range, possibly over some hundred Hz. Low-frequency disturbances are one magnitude away from the cut-on frequency and will therefore by suppressed 10 times more compared to the voltage mode. Themeasuring signals are already stable after a few seconds.•Due to the virtual short circuit of the pyroelectric element in current mode, an antiparallel connected compensation element does not lead to a reduction of signal and detectivity. Furthermore an incomplete illuminated pyroelectric element in current mode does not cause a loss of both signal and detectivity in contrast to the voltage mode.Why we are using CMOS-Operational amplifiers?CMOS technology combines technological and customer demands for a low supply voltage, low power consumption, Rail-to-Rail performance at output and low chip costs. Additionally the completely isolating gate (SiO2) in the operational amplifier shows a better performance during operation at high temperatures as opposed to the JFET design. The current mode which earlier was only possible to apply in combination with very expensive OpAmps like OPA128 or AD549, can now be applied in applications for gas analysis and flame detection which were previously dominated both technologically and price wise by the JFET. Comparison of the modulated output signal for detectors with JFET and OpAmpThe electrical time constant defines the form of the output signal in current and voltage mode. Identical time constants lead to the same signal form in both modes. In current mode we can work with a nearly arbitrary electrical time constant, which is an essential advantage. Therefore short time constants are preferred due to the resulting short settling time.Figures 3 to 6 show typical signal characteristics in order with decreasing electrical time constant.Fig. 3: LME-302 Voltage mode at 1Hz, 5Hz and 20Hz, thermal time constant 150ms, electrical time constant 5sFig. 4: LME-335 Current mode at 1Hz, 5Hz and 20Hz, thermal time constant 150ms, electrical time constant 20msFig. 5: LME-341 Current mode at 1Hz, 5Hz and 20Hz, thermal time constant 150ms, electrical time constant 5msFig. 6: LME-351 Current mode at 1Hz, 5Hz and 20Hz, thermal time constant 150ms, electrical time constant 1msFeedback Resistor Influence to Responsivity (signal), Detectivity (signal-to-noise ratio) and Stability of the operating point for a detector with integrated OpAmpIn accordance with voltage mode detectors the Ohm rating of the integrated resistor leads to opposite detector properties:• A large resistor results in a high signal and an increased detectivity since the noise only increasesthe square root of the resistor value. In contrast an amplifier stage after the detector would increase signal and noise by the same ratio.• A small resistor increases the stability of the DC operating point, therefore a thermal compensation isoften not necessary for R<10Gohm.11010010000,1110100Frequency [Hz]R e s p o n s i v i t y [k V /W ]1,0E+071,0E+081,0E+090,1110100Frequency [Hz]S p e c . D e t e c t i v i t y [c m H z 1/2/W ]Fig 7: Frequency response of responsivity (signal) and detectivity (signal-to-noise ratio) as a function of the feedbackresistor; LME-335 (100GOhm), LME-345 (24Gohm), LME-351 (5GOhm)Power supply for InfraTec CMOS OpAmp detectorsWe use mainly a split power supply ±2.2V ... ±8V for our detectors. Principally a single supply (4.5V ... 16V) is also possible, for this version the TO39-housing of our single detectors is located on Reference potential (mostly U/2).For customized detectors we can also integrate different operational amplifiers, which can be operated either with a very small supply voltage (single supply +2.2V) and isolated detector housing or with very supply high voltages and a high dynamic range (split supply ±13V).InfraTec can assure the availability of detectors with JFET source follower and CMOS-OpAmp for many years to come. The technical advantages will however accelerate the trend to use the current mode OpAmp detectors.。