快速实现ARM和DSP的通信和协同工作(精)

基于双核ARM和DSP的通信接口驱动设计与实现研究

基于双核ARM和DSP的通信接口驱动设计与实现研究摘要:随着市场对监控终端产品的需求越来越大,越来越多的人开始关注这个新兴产业,基于此,介绍了一种自行研究开发的基于ARM 和DSP双处理器芯片为硬件平台,在ARM处理器上采用了源代码公开的嵌入式Linux作为操作系统嵌入视频监控终端,详细分析该系统中两个处理器芯片DSP与ARM之间HPI数据传输模式和驱动接口,并结合实际出现的传输性能的问题进行了详细的分析和研究。

关键词:嵌入式ARM DSP 双核心HPI随着视频处理、计算机、通信、自动化控制等相关技术的不断发展,也随着社会环境的不断变化,出现了以数字化、智能化、网络化为主要特征的监控系统。

监控系统可以用于校园安全监控,考试监控,城市交通监控等方面,能够给人们带来良好的生活环境。

嵌入式视频监控系统主要是由采集部分,编码部分,传输部分,显示部分和控制部分组成[1]。

而基于ARM处理器的嵌入式系统以其自身资源丰富、功耗低、价格低廉、支持厂商众多的缘故,越来越多地应用在各种需要复杂控制和通信功能的嵌入式系统中。

作为数字处理专用电路,DSP的数字信号处理能力十分强大,但对诸如任务管理、通信、人机交互等功能的实现较为困难。

如果将这两者结合起来,即由DSP结合采样电路采集并处理信号,由ARM处理器作为平台,将经过DSP运算的结果发送给用户程序进行进一步处理,然后提供图形化友好的人机交互环境完成数据分析和网络传输等功能,就会最大限度的发挥两者所长[2]。

本文介绍了一种我们自行研究开发的基于双核ARM和DSP的嵌入式视频监控系统。

该系统ARM处理器采用的是Cirrus Logic公司的EP9315,DSP采用的是TI公司的TM320DM642。

这样既可以充分利用DSP强大的数据处理能力,又能发挥ARM处理器在控制方面的优势。

1 TMS320DM642的HPI接口在传统的单片机与主机进行接口时,需要外扩必要的硬件电路。

DSP与单片机的一种高速通信实现方案

DSP与单片机的一种高速通信实现方案摘要:介绍了一种利用双口RAM实现DSP与单片机高速数据通信的方法,给出了它们之间的接口电路以及软件实现方案。

关键词:DSP;双口RAM;接口电路;数据通信1 引言数字信号处理器(DSP)是一种适合于实现各种数字信号处理运算的微处理器,具有下列主要结构特点:(1)采用改进型哈佛(Harvard)结构,具有独立的程序总线和数据总线,可同时访问指令和数据空间,允许实际在程序存储器和数据存储器之间进行传输;(2)支持流水线处理,处理器对每条指令的操作分为取指、译码、执行等几个阶段,在某一时刻同时对若干条指令进行不同阶段的处理;(3)片内含有专门的硬件乘法器,使乘法可以在单周期内完成;(4)特殊的指令结构和寻址方式,满足数字信号处理FFT、卷积等运算要求;(5)快速的指令周期,能够在每秒钟内处理数以千万次乃至数亿次定点或浮点运算;(6)大多设置了单独的DMA总线及其控制器,可以在基本不影响数字信号处理速度的情况下进行高速的并行数据传送。

由一片DSP加上存储器、模/数转换单元和外设接口就可以构成一个完整的控制系统,但这种方案要达到高速实时控制是不可行的。

因为一个实时控制系统一般需要完成数据采集、模/数转换、分析计算、数/模转换、实时过程控制以及显示等任务,单靠一片DSP来完成这些工作势必会大大延长系统对控制对象的控制周期,从而影响整个系统的性能。

所以我们添加一个CPU,负责数据采集、模/数转换、过程控制以及人机接口等任务,使DSP专注于系统控制算法的实现,充分利用它的高速数据处理能力。

从性能价格比的角度出发,这个CPU采用8位的51系列单片机。

这时,两个CPU 之间的数据共享就成了一个重要的问题。

采用双口RAM(简称DRAM)是解决CPU之间的数据共享的有效办法。

与串行通信相比,采用双口RAM不仅数据传输速度高,而且抗干扰性能好。

在笔者实验室研制的电力有源滤波器中,选用了TI公司的第三代DSP芯片TMS320C32和51系列单片机89C52作为控制系统的CPU。

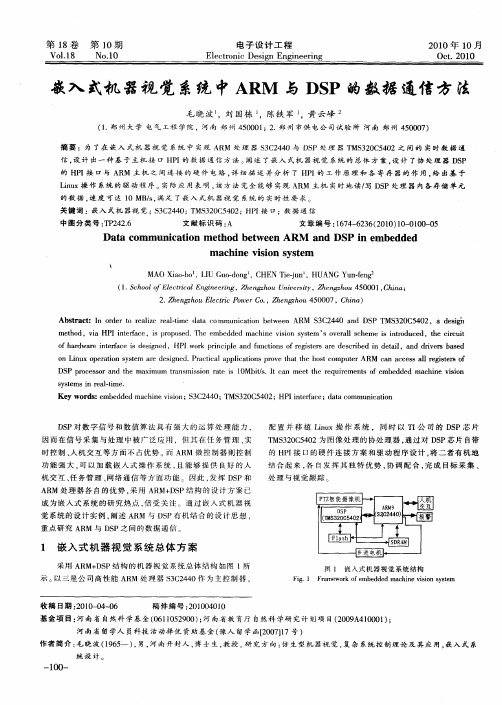

嵌入式机器视觉系统中ARM与DSP的数据通信方法

( .郑 州 大 学 电气 工 程 学 院 ,河 南 郑 州 4 0 0 ;2 郑 州 市供 电公 司试 验 所 河 南 郑 州 4 0 0 ) 1 50 1 . 5 0 7

摘 要 :为 了在 嵌 入 式 机 器 视 觉 系统 中 实现 A M 处 理 器 ¥ C 4 0与 D P处 理 器 T S 2 C 4 2之 间 的 实 时 数 据 通 R 3 24 S M 30 5 0

e

, h nzo 5 0 1 C ia Z eghu4 0 0 , hn ;

2 Z e g h u E e t c P w rC . h n z o 5 0 7,C ia) . h n z o lc r o e o ,Z e g h u 4 0 0 i hn

Ab t a t n o d r t e l e r a— me d t O sr c :I r e o r ai e lt a a C z i mmu i ai n b t e n ARM ¥ C 4 0 a d DS M¥ 2 C 4 2,a d s n c t ew e o 3 2 4 n P T 3 0 5 0 ei me h d,va HP ne fc to i Ii tra e,i p o o e . h mb d e c i e vso y t m ’ o e a l c e s i t d c d。t e c r ut s rp s d T e e e d d ma h n iin s se S v r l s ห้องสมุดไป่ตู้ me i n r u e o h i i c o ad a e i tra e i d sg e fh r w r n e c s e in d,HP o k p i cp e a d f n t n fr gse sa e d s rb d i e al n r e sb s d f 1w r r i l n u c i so e i r r e c i e n d t i,a d d i r a e n o t v O i u p r t n s se a ed s n d P a t a a p i ain r v h tt eh s c mp t r n L n x o e a o y tm r e i e . r ci l p l t sp o e t a h o t o u e i g c c o ARM a c e salr gse so c n a c s l e itr f D P p o e s ra d t e ma i m r n miso a e i 1 Mb t .I c n me tt e r q i me t o mb d e c ie vso S r c s o n h xmu t s s in r t S a 0 i s t a e h e ur / e ns fe e d d ma h n iin

ARM加DSP嵌入式双架构系统的设计与实现

兰

州

交

通

大

学

学

报

Vo 1 No 3 L3 .

Jun l f az o ioo gUnvri o r a o n h uJ tn iest L a y

J n 0 2 u e2 1

文章编号 :0 14 7 (0 2 0 —1 80 10 —3 3 2 1 )30 3—4

式多媒体应用程序平台 ( MA , pnMut ei O P O e lm d i a A pi t n l f m) T 公司推 出的专 门为支 plaos a o 是 I c i P tr 持第 3 (G 无线终端应用而设计的应用处理器 代 3) 体系结构 , 但这类芯片价格昂贵, 不适合完成某些特

定专 业领 域 的处理 . 了适 合 用户 自己的应用 需求 , 为

研究 基 于 AR 加 DS M P双 处理 器 的 架构 , 充 分 的 能

公司的高性能产 品. 系统设计采用 T 的高性 能数 I 字信 号处理 器 T 30 6 1T。芯 片 , 的核 心 主 MS 2C 4 6 [ ] 它 频能达到 1G , HZ 并且具有 丰富的片上 资源, 能够

ARM 加 D P嵌 入式 双 架构 系统 的设计 与 实现 S

赵 晶 , 王新 楼

70 7 ) 3 0 0

( 兰州交通大学 电子与信 息工程学 院, 甘肃 兰州

摘

要 : ¥C 40 在 3 2 4 A与 ¥ 2 C 4 6 30 6 1T芯 片为处理核心的基础上 , 出了一种基 于 AR 加 DS 提 M P双 架构 系统的软硬

件解决方案 , 为嵌 入 式信 号 处理 提 供 了新 的 设 计 理 念 和 实现 方 法 , 于 此 系统 可 以扩 展 开 发 出其 他 各 种 复 杂 的 信 基

ARM+DSP结构设计与实现

ARM+DSP结构设计与实现关键词:ARM处理器,嵌入式系统,DSP1 引言ARM(Advanced RISC Machine)是英国ARM公司设计开发的通用32位RISC微处理器体系结构,其主要优势在于简单的设计和高效的指令集。

ARM的设计目标是微型化、低功耗、高性能的微处理器实现[1]。

ARM 已经成为嵌入式系统主控制器的首选。

DSP(Digital Signal Processor)具有运算速度高、功耗低和智能化外设等特点,在数字信号处理方面显示了强大的实力。

由于ARM与DSP所具有的微型化、低功耗、高效性等共同特点和各自的独特优势,以ARM+DSP结构为核心的嵌入式系统在PDA、STB、DVD等消费类电子产品以及GPS、航空、勘探、测量等军方产品中得到了广泛的应用。

本文设计了基于ARM S3C2410与TMS320C5510 DSP的ARM+DSP结构的接口电路,并给出了其软件实现。

ARM+DSP结构以ARM为主控制器,DSP为协处理器,方案如图1所示。

ARM完成系统的流程调度、任务处理、中断处理以及提供显示、通信、远程控制等人机接口;DSP主要完成数字滤波、编码解码、数字调制解调等功能。

ARM与DSP利用了DSP提供的HPI口的进行通信,方便、灵活,接口电路设计简单。

ARM+DSP结构把ARM处理器和DSP处理器有机地结合起来,既能满足信号数据实时性要求,又便于系统的控制操作与升级,提高了系统的整体性能。

ARM+DSP结构具有很强的通用性,几乎不修改硬件和修改少量软件代码就可以轻松实现不同系统间的移植。

3 ARM S3C2410与TMS320C5510 DSP硬件接口设计TMS320C5510 DSP提供了一个16位宽的并行端口HPI(host port interface),通过HPI口,主机可以直接访问TMS320C5510 DSP的存储器,有关TMS320C5510 DSP的HPI口详细情况请参考资料[2][3]。

DSP和ARM通信

DSP与ARM之间的通信

1.CAN总线:

CAN通信是串行通信。

这图为买来2812板子上面的CAN的模块。

CAN的控制部分已经在2812芯片内部。

SN65HVD230是一个电平转换器。

简单的说就是讲逻辑的0和1表达在CANH和CANL上。

CANH 和CANL有电压差的时候代表逻辑1.

这图是ARM上面的CAN接口。

DSP和ARM的can模块都差不多。

电路比较简单

个人看法:

简述:电路简单,编程简单。

串行口通信,实时性稍微比较差。

假如只有DSP和ARM两个芯片,就浪费了CAN这个功能了,假如后期假如了更多的芯片,CAN总线的功能能更好体现。

2.HPI通信

HIP通信是并行通信,占用的端口比较多。

下图是ARM和DSP的HIP通信。

这种方式的速度比较快,但是实验室买的2812似乎不支持HIP通信。

所以这个方法可以ban掉了。

看法:似乎不大可行

3.采用CPLD通信

在CPLD中划出一部分作为RAM缓存。

这个是并行通信,可以在2812中实现。

原理自己都想的清楚。

看法:实时性比较高。

由于从未涉及过CPLD,编程CPLD会比较麻烦。

接口比较多,辅助,这个也提高了编程难度。

4.SPI通信

SPI通信也是串行口通信。

具体的还没看完。

待定…,似乎也是一个好方法…..

参考文献

都是知网上一搜索就出的文件!待定。

嵌入式Linux下ARM处理器与DSP的数据通信

嵌入式Linux下ARM处理器与DSP的数据通信基于核心处理器的系统以其自身资源丰盛、功耗低、价格低廉、支持厂商众多的缘故,越来越多地应用在各种需要复杂控制和通信功能的嵌入式系统中。

内核源码开放的与ARM体系处理器相结合,可以发挥Linux系统支持各种协议及存在多进程调度机制的优点,从而使开发周期缩短,扩展性增加。

作为数字处理专用,的数字信号处理能力非常强大,但对诸如任务管理、通信、人机交互等功能的实现较为困难。

假如将这三者结合起来,即由DSP结合采样电路采集并处理信号,由ARM处理器作为平台,运行Linux操作系统,将经过DSP运算的结果发送给用户程序举行进一步处理,然后提供应图形化友好的人机交互环境完成数据分析和网络传输等功能,就会最大限度的发挥三者所长。

2 系统结构

该系统硬件由二部分组成,其中一部分为若干块DSP板,各自自立承接数据采集和信号处理。

另一部分为以ARM为核心处理器的CPU板。

系统硬件框图1所示(仅接口部分)。

3 接口硬件部分设计

3.1 HPI接口简介

HPI接口是TI公司新一代、高性能DSP上用以完成与主机或其他DSP 之间数据交换的接口,这里主要介绍实际电路中用法的控制引脚和时序。

HCNTL0和HCNTL1为拜访控制挑选。

用来确定主机(ARM)毕竟对TMS320C6711中的哪一个HPI寄存器举行处理。

详细功能如表1所列。

HR/W:读写挑选控制。

为“1”表示是从DSP中读,反之则为写。

HHWIL:半字节定义挑选,与H寄存器中的HWOB位举行协作可以挑选当前传输的是高半字还是低半字。

低电平是第一个半字,高电平是其

第1页共9页。

DSP与单片机的一种高速通信实现方案

DSP与单片机的一种高速通信实现方案

一种常见的高速通信实现方案是使用SPI(串行外设接口)协议。

SPI是一种同步串行数据传输协议,常用于连接微控制器和外部设备,可以实现理论上的最高速率。

在DSP和单片机之间实现高速通信,可以按照以下步骤进行:

1. 确定通信的硬件接口:DSP和单片机必须有相应的硬件接口来实现SPI通信。

通常,SPI需要使用四根线进行通信,包括主时钟(SCLK)、主输出从输入(MOSI)、主输入从输出(MISO)、片选(SS)等。

2. 配置SPI控制器:DSP和单片机的SPI控制器需要进行适当的配置,包括通信速率、数据位宽、传输模式(主从模式)、时钟极性和相位等。

3. 实现通信协议:根据通信需求,在DSP和单片机之间定义一种通信协议。

协议包括命令和数据的格式、传输顺序、通信协议等。

通常情况下,DSP作为主设备发送命令

和数据给单片机从设备。

4. 编写软件驱动:在DSP和单片机上编写软件驱动程序来控制SPI接口,实现通信协议。

DSP的驱动程序负责发送命令和数据给单片机,单片机的驱动程序负责接收和处

理命令和数据,并向DSP返回相应的响应。

5. 进行通信测试:完成以上步骤后,进行通信测试来验证通信的可靠性和稳定性,确

保数据能够正确地在DSP和单片机之间传输。

需要注意的是,通信速率和系统时钟频率之间有一定的关系,通信速率受限于系统时

钟频率和SPI控制器的能力。

因此,在设计系统时,需要选择合适的时钟频率来满足

通信要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

快速实现ARM和DSP的通信和协同工作德州仪器(TI)的第一颗达芬奇(DaVinci)芯片(处理器)DM6446已经问世快三年了。

继DM644x之后,TI又陆续推出了DM643x,DM35x,DM6467,OMAP353x等一系列ARM+DSP或ARM+视频协处理器的多媒体处理器平台。

很多有很强DSP开发经验或ARM开发经验的工程师都转到达芬奇或通用OMAP (OMAP353x)平台上开发视频监控、视频会议及便携式多媒体终端等产品。

大家都面临着同一个问题,那就是如何实现ARM和DSP或协处理器的通信和协同工作?TI的数字视频软件开发包(DVSDK)提供了Codec Engine这样一个软件模块来实现ARM和DSP或协处理器的协同工作。

有很多工程师反馈这个软件模块非常好用,节省了很多开发时间,也有工程师认为TI提供的资料太多,不知如何快速上手。

本文将从一个第一次接触Codec Engine的工程师角度出发,归纳TI提供的相关资源(文档,例程和网络资源)并介绍相关开发调试方法帮您快速入门Codec Engine。

1. Codec Engine概述如图1所示,Codec Engine是连接ARM和DSP或协处理器的桥梁,是介于应用层(ARM侧的应用程序)和信号处理层(DSP侧的算法)之间的软件模块。

ARM应用程序调用Codec Engine的VISA (Video, Image, Speech, Audio)API,如图1中VIDENC_process(a, b, c 。

Codec Engine的stub (ARM侧)会把参数a, b, c以及要调用DSP侧process这个信息打包,通过消息队列(message queue)传递到DSP。

Codec Engine的skeleton(DSP侧)会解开这个参数包,把参数a, b, c转换成DSP 侧对应的参数x, y, z(比如ARM侧传递的是虚拟地址,而DSP只能认物理地址),DSP侧的server(优先级较低,负责和ARM通信的任务)会根据process这一信息创建一个DSP侧的process(x, y, x任务最终实现VIDENC_process(a, b, c的操作。

图1 达芬奇软件结构框图通过第一部分的介绍,我们知道了TI数字视频软件开发包(DVSDK)中的Codec Engine软件模块可以帮助我们轻松地实现ARM和DSP或协处理器的协同工作,以及Codec Engine软件模块的概要情况,下面我们将告诉你如何走完Codec Engine入门的第一步和第二步。

2. Codec Engine入门第一步从Codec Engine发布说明文档(release notes)开始。

有些初学者认为Codec Engine文件包结构复杂,很难找到自己想找的文档或例子。

其实在Codec Engine文件包的根目下有一个发布说明文档,比如Codec Engine 1.20 根目录下的release_notes_codec_engine_1_20.html。

这个文档就是你了解Codec Engine的开始,里面有关于该版本Codec Engine的介绍、相关文档资料的链接、新的功能、支持哪些芯片、已知的bug、修正了哪些bug 及例子等等的具体说明。

具体如图2蓝色字体所示。

浏览该文档后,初学者至少可以知道哪里可以找到自己想要的文档或例子。

举例来说,如果想找相关的文档,点击 Documentation就可以看到这个Codec Engine文件包里的文档的链接。

图2 Codec Engine 1.20 Release Notes截图3. Codec Engine入门第二步了解Codec Engine的运行环境及依赖的软件模块和工具。

点击Codec Engine的发布说明文档(如图2)的Validation Info,我们可以知道Codec Engine 1.20需要和以下软件模块和工具配合使用:✈ Framework Components 1.20.02✈ xDAIS 5.21✈ XDC Tools 2.93.01✈ DSP/BIOS Link 1.40.05, configured for the DM6446 EVM❑C6x Code Generation Tools version 6.0.8❑DSP/BIOS 5.31.05❑MontaVista Linux v4.0❑Red Hat Enterprise Linux 3 (SMP因此,我们需要在该Codec Engine安装的DVSDK文件包下面检查上面提到的软件模块和工具是否安装,版本是否正确。

否则,可能会编译不过 Codec Engine的例子。

那么,什么是 Framework Components,什么是xDAIS,什么又是XDC Tools 呢?你可以分别到它们的根目录下浏览它们各自的发布说明文档,做一个总体的了解。

这里我们简单介绍一下,可以帮助大家尽快找到和自己相关的重点及资源。

1 Framework Components是TI提供的一个软件模块,负责DSP侧的memory和DMA资源管理。

因此,DSP算法工程师需要了解这个软件模块。

/wiki/index.php?title=Framework_Components_FAQ2 xDAIS 是一个标准,它定义了TI DSP算法接口的标准。

这样大大提高了DSP算法软件的通用性。

DSP算法工程师要写出能被ARM通过Codec Engine 调用的算法,必须保证自己的算法接口符合这个标准。

因此,DSP算法工程师也必须了解这个软件模块。

/wiki/index.php?title=Category:XDAIS3 XDC Tools和gmake类似,是一个工具。

XDC根据用户定义的一套build指令,通过调用用户指定的ARM 工具链(Tool Chain)和DSP编译器(C6x Code Generation Tools )build出ARM侧和DSP侧的可执行文件。

可以先不必细究这个工具,只需通过编Codec Engine的例子,知道如何设置build指令就可以了。

4 DSP/BIOS Link是实现ARM和DSP之间通信的底层软件,Codec Engine就是建立在这个底层软件之上。

在修改系统内存分配(缺省是256MB的DDR2)时,DSP/BIOS Link 1.38版本的用户需要修改DSP/BIOS Link的配置文件,并重新build DSP/BIOS Link。

而DSP/BIOS Link 1.40版本以后的用户就无需此操作。

/wiki/index.php?title=DSPLink_Overview/index.php?title=Changing_the_DVEVM_memory_map5 C6x Code Generation Tools是Linux环境下C6000系列DSP的编译器。

我们用CCS开发DSP时都是用的Windows环境下的DSP编译器。

6 DSP/BIOS是TI 免费提供的DSP实时操作系统。

和上面C6x Code GenerationTools一样,这里的DSP/BIOS也是Linux环境下的版本。

DSP系统工程师需要了解这个操作系统。

/wiki/index.php?title=Category:DSPBIOS4. Codec Engine入门第三步根据自己的角色参考相关的文档和例子进行开发。

开发ARM+DSP平台需要三类工程师:ARM应用程序工程师、DSP算法工程师和DSP系统工程师。

而开发ARM+协处理器平台只需要ARM应用程序工程师。

下面就让我们针对这三类工程师做分别介绍。

如果您使用的是TI或TI第三方的编解码算法,就不需要关注DSP算法工程师的部分。

如果使用ARM+协处理器平台,就只需关心ARM应用工程师的部分。

4.1. DSP算法工程师应该如何着手?这里我们不讨论如何开发DSP算法,只讨论DSP算法工程师怎样让自己的算法可以被ARM通过Codec Engine调用。

(参考/litv/pdf/sprued6c,这个文档会讲到codec package及相关的.xs和.xdc文件,Codec Engine1.20及以上版本的用户可以先不细究这些内容,后面会介绍工具帮您自动生成这些文件。

)1 熟悉xDAIS和xDM标准xDM只是xDAIS的扩展,因此,需要先了解xDAIS。

在xDAIS 软件包根目录下的发布说明文档里,可以很快找到关于xDAIS和xDM的文档链接。

/lit/ug/spruec8b/spruec8b.pdf在xDAIS安装路径下的examples/ti/xdais/dm/examples/g711有一个g711_sun_internal.c,这个算法不符合xDAIS标准。

在同一个路径下的g711dec_sun_ialg.c (decoder和g711enc_sun_ialg.c (encoder是封装成符合xDM标准之后的编解码算法。

可以通过这个例子学习和了解如何把自己算法封装成符合xDM标准的算法。

xDAIS 6.10及其以后的版本,包含了一个工具QualiTI,可以检查您的DSP算法是否满足xDAIS标准(但不会检查是否满足xDM)。

具体请参考:/wiki/index.php?title=QualiTI_XDAIS_Compliance_Tool2 熟悉Framework ComponentsFramework Components主要包括两个模块DSKT2和DMAN3,它们分别负责DSP 侧的memory 和EDMA资源管理。

DSP算法使用的memory必须是先向DSKT2提出申请并由DSKT2分配得到的。

同样DSP算法使用的EDMA通道也是向DMAN3申请并由DMAN3分配得到的。

而关于QDMA的操作,是通过ACPY3这个模块实现的。

这样的好处是很容易对DSP侧不同的算法做整合,不同的算法之间不用担心资源(Memory和EDMA)的冲突问题。

在Framework Components 软件包根目录下的发布说明文档里,可以很快找到相关文档的链接。

在Framework Components安装路径下packages\ti\sdo\fc\dman3\examples有一个Fast Copy的例子,可以帮您理解如何基于Framework Components的ACPY3模块实现QDMA的操作。

另外,有些用户DSP侧的算法比较简单,在确保不和ARM侧EDMA资源冲突的前提下在算法里直接操作EDMA不使用DMAN3也是可以的。

这样做的弊端是和其它算法做整合时会遇到资源使用冲突的问题。