Verilog秒表计时电路

Verilog秒表设计 精品

课程名称:数字系统设计一、实验目的1、进一步熟悉ISE软件的使用,熟悉FPGA开发流程;2、掌握编写Verilog代码的步骤,学会绘制ASM图;3、学会自顶向下的设计方法,使用不同的模块实现系统的设计。

二、实验设备1、装有ISE软件的PC机一台;2、Nexys3开发板一块。

三、实验内容与要求设计一个秒表它具有计时功能。

此秒表有两个按键(reset, start)按下reset键后,秒表清零。

开始默认秒表计时,按下start键后,停止计时,再次按下start键后,又开始计时,如此反复。

用FPGA开发板上的两个七段数码管显示时间(以秒为单位),计时由0 到 59 循环。

三、实验步骤1、设计系统框图,设计采取自顶向下的设计方案,整个秒表系统的原理图如下所示。

主要包括五个模块——按键消抖模块、分频模块、按键功能控制模块、计数模块、数码管驱动显示模块。

2、根据系统的原理图,画出各个模块的ASM图。

(1)利用D触发器对按键进行消抖处理,其电路图如下。

利用下面这个电路即可实现对start键和reset键的消抖。

只有连续输入三个周期的高电平时,按键才有效。

(2)分频模块的ASM图。

此ASM图将100MHz的信号分频为100Hz的信号,用于计数和数码管的扫描。

(3)start键与reset键功能控制模块的ASM图。

图中rst为复位信号,sta为计时信号。

利用状态机实现不同状态之间的转换并输出复位信号与计时信号。

默认状态是start_time,即计时状态。

(4)计数模块的ASM图。

输入100Hz的时钟用于计数,当复位信号有效时,将所有的数全部置0。

否则sta信号有效时开始计数。

最后输出秒位与十秒位。

(5)数码管驱动模块的ASM图。

使用100Hz的信号扫描数码管,并将对应的数字以十进制形式显示在数码管上。

因为只用到两个数码管,所以前两个数码管置1,即保持不亮,只点亮后两个数码管。

3、根据所绘制各个模块的ASM图和系统的原理图,编写Verilog代码。

用Verilog语言编写的多功能数字钟

这次的闹钟电路设计和多功能数字钟有一些相似的地方,不同在于整体构思和细

节上要求的差异。

构思根据要求采用的是状态机设计方法。从一个状态进入另一个状态最适合这个

设计了。细节上和数字钟也有很大的差异。中间的控制逻辑有时候需要反馈。前

后都是有联系的,并不是独立存在的。

本次设计基本上完成的所以的要求,但是由于时间紧急,一些细节并不是很完美,

分频器的作用是对 50Mhz 的系统时钟信号进行分频,得到频率为 1hz 的信号,

作为时钟的输入信号。

2

2.控制器和计数器 控制器的作用是,调整小时和分钟的值,并能实现清零功能。计数器的

作用是实现分钟和秒钟满 60 进 1,小时则由 23 跳到 00。当到达 59 分 55 秒的时 候,LED 灯会闪烁来进行报时。

end 2:

begin state<=2; s=1;

end 3:

begin s=0; if(k1==0) //时调整

7

begin

if(nz_h_l==3)

begin

nz_h_l=0;

if(nz_h_h==2)nz_h_h=0;

else nz_h_h=nz_h_h+1;

end

else nz_h_l=nz_h_l+1;

end

else if(k3==0) finish=1;

//设置完成

else if(k4==0) spker_en=1; //停止声响

end

8

4: begin s=0; if(k4==0) begin on_off<=!on_off;state=0;end end

endcase end end endmodule 3.显示器 显示器的作用是将时:分的值在数码管上依次显示出来。从分频器输出的 1Khz 的信号作为数码管的扫描信号。SEL 表示 6 个数码管选择位,它的取值表示八个 数码管,从左至右依次是 111~000。seg 表示七段数码管,它的取值决定特定位 数上显示的数字。

电子秒表设计VHDL

一、设计题目:基于VHDL语言的电子秒表设计(可调时,有闹钟、定时功能)二、设计目的:⑴掌握较复杂的逻辑设计和调试⑵学习用原理图+VHDL语言设计逻辑电路⑶学习数字电路模块层次设计⑷掌握QuartusII软件及Modelsim软件的使用方法三、设计内容:(一)设计要求1、具有以二十四小时计时、显示、整点报时、时间设置和闹钟的功能。

2、设计精度要求为1S。

(二).系统功能描述1 . 系统输入:系统状态及校时、定时转换的控制信号为k、set、ds;时钟信号clk,采用实验箱的50MHz;系统复位信号为reset。

输入信号均由按键产生。

系统输出:8位LED七段数码管显示输出,蜂鸣器声音信号输出。

多功能数字钟系统功能的具体描述如下:2. 计时:set=1,ds=1工作状态下,每日按24h计时制计时并显示,蜂鸣器无声,逢整点报时。

3. 校时:在set=0,ds=0状态下,按下“k键”,进入“小时”校准状态,之后按下“k键”则进入“分”校准状态,继续按下“k键”则进入“秒校准”状态,之后如此循环。

1)“小时”校准状态:在“小时”校准状态下,显示“小时”数码管以1Hz的频率递增计数。

2)“分”校准状态:在“分”校准状态下,显示“分”的数码管以1Hz的频率递增计数。

3)“秒”复零状态:在“秒复零”状态下,显示“分”的数码管以1Hz的频率递增计数。

4. 整点报时:蜂鸣器在“59”分钟的第50—59,以1秒为间隔分别发出1000Hz,500Hz的声音。

5. 显示:采用扫描显示方式驱动8个LED数码管显示小时、分、秒。

闹钟:闹钟定时时间到,蜂鸣器发出交替周期为1s的1000Hz、500Hz的声音,持续时间为一分钟;6. 闹钟定时设置:在set=0,ds=1状态下,按下“k”,进入闹钟的“时”设置状态,之后按下“k键”进入闹钟的“分”设置状态,继续按下“k 键”则进入“秒”设置状态, 之后如此循环。

1)闹钟“小时”设置状态:在闹钟“小时”设置状态下,显示“小时”的数码管以1Hz 的频率递增计数。

电子钟(FPGA设计verilog代码)

电子钟(FPGA设计verilog代码)//*****************************************//电子钟:24小时制时分秒////作者:yotain////clk 50M时钟 CP 1Hz输出可接LED指示灯//nCR 清零(必须接低电平异步清零)//Adj_Min (分校正低电平计时必须接)//Adj_Hour (时校正低电平计时必须接)//dataout (数码管输出)//en (数码管使能端)//(Hour Minute Second 可以不接也可以单独接数码管一位的) //修改bcd_decoder 即可修改显示////*****************************************//************ timeclock top block*************module top_clock ( Hour, Minute, Second, CP, nCR, EN, Adj_Min, Adj_Hour,clk,dataout,en) ;input clk, nCR, EN, Adj_Min, Adj_Hour;output CP;output [7:0] Hour, Minute, Second,dataout;output [3:0] en;wire [7:0] Hour, Minute, Second, dataout;supply1 Vdd;wire MinL_EN, MinH_EN, Hour_EN;//**************Hour, Minute, Second counter************counter10 U1 ( Second[3:0], nCR, EN, CP);counter6 U2 ( Second[7:4], nCR, ( Second[3:0]==4'h9), CP);assign MinL_EN = Adj_Min? Vdd : (Second==8'h59);assign MinH_EN = ( Adj_Min &&( Minute [3:0] ==4'h59))|| ( Minute[3:0]==4'h9)&& (Second == 8'h59);counter10 U3 ( Minute[3:0], nCR, MinL_EN,CP);counter6 U4 ( Minute[7:4], nCR, MinH_EN,CP);assign Hour_EN = Adj_Hour ? Vdd: ((Minute == 8'h59)&&(Second == 8'h59));counter24 U5 ( Hour[7:4], Hour[3:0], nCR, Hour_EN,CP);bcd_decoder U6 (clk,nCR,Hour[7:4],Hour[3:0],Minute[7:4],Minute[3:0],dataout,en);PULSE U7(clk,CP);endmodule//**************counter10 ( BCD 0~9 )*************module counter10 ( Q, nCR, EN, CP);input CP, nCR, EN;output [3 : 0] Q;reg [3 : 0] Q;always @ (posedge CP or negedge nCR)beginif( !nCR ) Q<=4'b0000;else if ( !EN ) Q<=Q;else if ( Q ==4'b1001) Q <= 4'b0000;else Q <= Q+1'b1;endendmodule//**************counter6 ( BCD 0~5 )************ module counter6 ( Q, nCR, EN, CP);input CP, nCR, EN;output [3:0] Q;reg [3:0] Q;always @ (posedge CP or negedge nCR ) beginif(!nCR) Q<= 4'b0000;else if (!EN) Q<=Q;else if (Q == 4'b0101) Q<=4'b0000;else Q <= Q + 1'b1;endendmodule//***************counter24 ( 0~23 )************** module counter24 ( CntH, CntL, nCR, EN, CP); input CP, nCR, EN;output[3:0] CntH,CntL;reg [3:0] CntH,CntL;reg CO;always @ (posedge CP or negedge nCR)if(!nCR) {CntH,CntL} <=8'h00;else if(!EN) {CntH,CntL} <= {CntH,CntL};else if ( (CntH>2)||(CntL>9) || ( (CntH==2)&&(CntL>=3) ) ) {CntH,CntL} <=8'h00;else if((CntH==2)&&(CntL<3))beginCntH<=CntH;CntL<=CntL+1'b1;endelse if (CntL==9)beginCntH=CntH+1'b1;CntL=4'b0000;endelse beginCntH<=CntH;CntL<=CntL+1'b1;endendendmodule//*************cnt_1Hz*****************module PULSE ( clk, clk_1Hz);input clk;output clk_1Hz;reg [24:0] cnt_1Hz;reg R_clk=0;assign clk_1Hz=R_clk;always @ (posedge clk)if (cnt_1Hz==50000000) cnt_1Hz<=0;else cnt_1Hz<=cnt_1Hz+1;endalways @ (posedge clk)beginif(cnt_1Hz<=25000000) R_clk<=1;else R_clk<=0;endendmodule//*************bcd_decoder*************module bcd_decoder (clk,nCR,A,B,C,D,dataout,en);input clk; //system clockinput nCR; //system reset,low is activeinput [3:0] A,B,C,D;output[7:0] dataout;output[3:0] en; //enable high is activereg[7:0] dataout;reg[4:0] en;reg[15:0] cnt_scan;reg[3:0] dataout_buf;always@(posedge clk or negedge nCR)beginif(!nCR) begincnt_scan<=0;endelse begincnt_scan<=cnt_scan+1; endendalways@(cnt_scan) begincase(cnt_scan[15:14]) 2'b00:en=4'b0001;2'b01:en=4'b0010;2'b10:en=4'b0100;2'b11:en=4'b1000; default:en=4'b1111; endcaseendalways@(en)begincase(en)4'b0001:dataout_buf=A;4'b0010:dataout_buf=B;4'b0100:dataout_buf=C;dataout_buf=D; default:dataout_buf=4'b0000; endcaseendalways@(dataout_buf) begincase(dataout_buf)4'b0000:dataout=8'b1111_1100; 4'b0001:dataout=8'b0110_0000; 4'b0010:dataout=8'b1101_1010; 4'b0011:dataout=8'b1111_0010; 4'b0100:dataout=8'b0110_0110; 4'b0101:dataout=8'b1011_0110; 4'b0110:dataout=8'b1011_1110; 4'b0111:dataout=8'b1110_0000; 4'b1000:dataout=8'b1111_1110; 4'b1001:dataout=8'b1110_0110;dataout=8'b1110_1110; 4'b1011:dataout=8'b0011_1110; 4'b1100:dataout=8'b1001_1100; 4'b1101:dataout=8'b0111_1010; 4'b1110:dataout=8'b1001_1110; 4'b1111:dataout=8'b1000_1110; default :dataout=8'b0000_0010; endcaseendendmodule//End of RTL code。

基于verilog语言编程的数字秒表设计

数字秒表设计系别:电子通信工程系专业:电子信息工程班级:学号:姓名:数字秒表(基于verilong语言编程)课程设计一、设计要求用verilong语言编写程序,结合实际电路,设计一个4位LED数码显示“秒表”,显示时间为99.9~00.0秒,每秒自动减一,精度为0.1。

另设计一个“开始”按键和一个“复位”按键。

再增加一个“暂停”按键。

按键说明:按“开始”按键,开始计数,数码管显示从99.9开始每秒自动减一;按“复位”按键,系统复位,数码管显示99.9;按“暂停”按键,系统暂停计数,数码管显示当时的计数。

二、设计目的1、通过本次课程设计加深对verilong语言课程的全面认识、复习和掌握,对EPM7064芯片的应用达到进一步的了解。

2、掌握定时器、外部中断的设置和编程原理。

3、通过此次课程设计能够将软硬件结合起来,对程序进行编辑,调试。

使其能够通过电脑下载到芯片,正常工作。

4、实际操作Quartus II软件,复习巩固以前所学知识。

三、总体设计本秒表系统具有复位、暂停、秒表计时等功能。

clk为系统工作时钟,采用Altera DE2上的50M时钟信号,经过分频器产生秒表计时周期为0.01s的时钟,再经过计数器,分别对秒表的百分位、十分位、秒、秒十位、分、分十位进行计数。

onoff为启动/暂停控制信号,当它为0时,启动计时,当它为1时,计时暂停。

clr为复位信号,当该信号有效时,计数器和译码清零,此时数码管显示输出为00:00:00。

在总体电路图中,根据设计要求,需要两个输入控制信号onoff和clr。

由于开发板上除了拨动开关就是瞬时的按键开关,且按键开关平时都呈高电平,按一下为低电平。

故在实际测试时采用了拨动开关SW0来控制秒表的启动/暂停,通过KEY0来控制秒表的清零。

四、设计思路描述该实验要求进行计时并在数码管上显示时间,通过相关软件Quartus II编译,利用JTAG 下载电路到核心芯片,驱动硬件工作。

简单的数字时钟(verilog设计)

设计目标与要求

设计一个简单的数字 时钟,能够显示时、 分、秒。

时钟应具有可靠性、 稳定性和可扩展性。

要求使用Verilog语 言实现,并能够在 FPGA或ASIC上实现。

设计思路及流程

• 设计思路:采用模块化设计方法,将数字时钟划分为不同的模 块,如计数器模块、显示模块等。每个模块负责实现特定的功 能,并通过接口与其他模块进行通信。

设计思路及流程

设计流程 1. 确定设计需求和目标。 2. 制定设计方案和计划。

设计思路及流程

3. 编写Verilog代码,实现各个模块的功能。 5. 根据测试结果进行调试和优化。

未来改进方向探讨

提高计时精度

通过改进算法或采用更高 性能的硬件平台,提高数

字时钟的计时精度。

降低资源占用

优化代码结构,减少不 必要的资源占用,提高 时钟系统的运行效率。

增加实用功能

拓展应用领域

考虑增加闹钟、定时器 等实用功能,使数字时 钟更加符合用户需求。

探索将数字时钟应用于 更多领域,如智能家居、

数据类型与运算符

Verilog中的数据类型包括

整型、实型、时间型、数组、结构体等。

Verilog中的运算符包括

算术运算符、关系运算符、逻辑运算符、位运算符等。

顺序语句与并行语句

Verilog中的顺序语句包括

赋值语句、条件语句、循环语句等,用于描述电路的时序行为。

Verilog中的并行语句包括

模块实例化、连续赋值语句、门级电路描述等,用于描述电路的并行行为。

verliog数字时钟计数器电路设计

Verilog数字时钟计数器电路设计一、引言Verilog是一种硬件描述语言,用于描述、设计和模拟数字电路。

数字时钟计数器电路是数字电子系统中常见的模块,用于产生时钟信号和计数功能。

本文将介绍如何使用Verilog语言设计数字时钟计数器电路。

二、电路功能数字时钟计数器电路的功能是产生一个稳定的时钟信号,并实现计数功能,用于驱动数字系统中的时序逻辑。

该电路通常包括时钟发生器和计数器两部分,时钟发生器用于产生稳定的时钟信号,而计数器用于对时钟信号进行计数。

三、Verilog语言简介Verilog是一种硬件描述语言,它可以用于描述数字电路的结构、行为和时序特性。

Verilog语言具有丰富的语法结构,包括模块、端口、信号、赋值语句、过程块等,可以描述数字电路中的各种逻辑和时序操作。

四、数字时钟计数器电路设计1. 模块定义我们需要使用Verilog语言定义数字时钟计数器的模块。

模块是Verilog语言中的最基本单元,用于描述数字电路的结构和行为。

以下是数字时钟计数器模块的定义:```verilogmodule clk_counter(input wire clk,input wire rst,output reg [3:0] count);```在上面的代码中,我们定义了一个名为`clk_counter`的模块,该模块包括一个时钟输入`clk`、一个复位输入`rst`和一个4位计数输出`count`。

2. 时钟发生器接下来,我们需要设计时钟发生器模块,用于产生稳定的时钟信号。

以下是时钟发生器模块的定义:```verilogmodule clk_generator(output reg clk);always #10 clk = ~clk;endmodule```在上面的代码中,我们定义了一个名为`clk_generator`的模块,该模块包括一个时钟输出`clk`。

通过`always`块和`#10`延时控制,我们实现了一个简单的时钟发生器,每10个时间单位翻转一次。

时钟的verilog实现

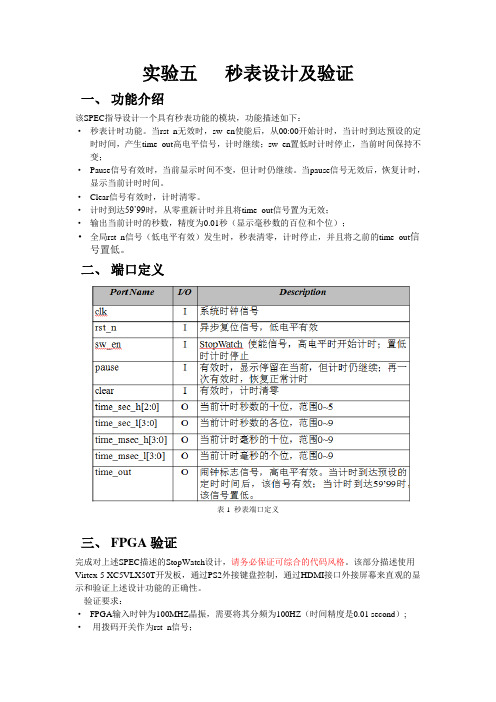

实验五秒表设计及验证一、功能介绍该SPEC指导设计一个具有秒表功能的模块,功能描述如下:·秒表计时功能。

当rst_n无效时,sw_en使能后,从00:00开始计时,当计时到达预设的定时时间,产生time_out高电平信号,计时继续;sw_en置低时计时停止,当前时间保持不变;·Pause信号有效时,当前显示时间不变,但计时仍继续。

当pause信号无效后,恢复计时,显示当前计时时间。

·Clear信号有效时,计时清零。

·计时到达59’99时,从零重新计时并且将time_out信号置为无效;·输出当前计时的秒数,精度为0.01秒(显示毫秒数的百位和个位);·全局rst_n信号(低电平有效)发生时,秒表清零,计时停止,并且将之前的time_out信号置低。

二、端口定义表1 秒表端口定义三、FPGA验证完成对上述SPEC描述的StopWatch设计,请务必保证可综合的代码风格。

该部分描述使用Virtex-5 XC5VLX50T开发板,通过PS2外接键盘控制,通过HDMI接口外接屏幕来直观的显示和验证上述设计功能的正确性。

验证要求:·FPGA输入时钟为100MHZ晶振,需要将其分频为100HZ(时间精度是0.01 second); ·用拨码开关作为rst_n信号;·使用一个按键←作为计时使能信号,模拟sw_en的功能;按一次开始计时,第二次,停止,以此类推;·使用一个按键↓作为暂停信号,模拟pause功能;计时过程中,按一次屏幕暂停计时,但stopwatch内核仍在计时,第二次,屏幕恢复计时,以此类推;·使用一个键盘键↑作为StopWatch的清零信号,按一次对计时清零;·当前计时时间显示外接屏幕上,共四个数字,前两个数显示秒数,后两个数显示毫秒数,并且显示秒数与毫秒数之间的小数点。

屏幕的显示需要一个扫描时钟,频率为25MHz,需要从100MHz的系统时钟分频得到。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

秒表计时电路

1.实验内容

1.秒表计时功能,显示分、秒、0.01秒

2.具有启动、暂停、停止和清空功能

3.增加有趣的流水灯

4.输入信号:4bit按键,50MHz时钟

5.输出信号:6位数码管

2.实验原理

(1) Verilog语言

Verilog HDL是一种硬件描述语言,以文本形式来描述数字系统硬件的结构和行为的语言,用它可以表示逻辑电路图、逻辑表达式,还可以表示数字逻辑系统所完成的逻辑功能。

本实验使用Verilog语言编写代码,通过编译,综合等实现电路设计。

其中涉及基本的语法知识,可通过查阅相关资料进行了解。

(2) quartus软件

Quartus是Altera公司的综合性PLD/FPGA开发软件,支持原理图、VHDL、VerilogHDL以及AHD等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

本实验以quartus为平台,完成代码的编辑,编译,综合及分配引脚等,最后下载。

(3) Altera DE2实验板

DE2板具有很多特性可以允许使用者实现像从单个电路到多媒体工程的广泛的电路设计。

除了一些硬件特性,DE2还有对标准IO接口的软件支持和一个可以接入多种元件的控制平台。

并且这些软件还提供一系列展现DE2板高级性能的演示。

为了向用户提供最大的灵活性,所有的连接通过Cyclone II FPGA设备。

因此用户可以配置FPGA来实现任何系统设计。

本实验用到的电路模块如右

(4) 数码管

采用共阳数码管,数码管段选方式如下

每一个数码管单独与FPGA连接

通过并行总线控制数码管显示

3.设计思路及实现方案

(1)时钟分频

clk10ms→ clk100ms → clk1s→clk10s→clk1min→clk10min→clk1h

分频单元:六分频,十分频

50MHz到100Hz分频,500000分频

(2)状态机设计

(3)设计框图

4.代码添加及说明

a)六进制分频代码

//计数器实现6分频,计数到达2和5,输出始终翻转一次,且计数达到5时计数清零module count6(rst, clk, clkout, counter);

input rst;

input clk;

output reg clkout;

output reg [3:0]counter;

always @(negedge clk or negedge rst) begin

if (~rst) begin

clkout <= 0;

counter <= 0;

end

else if (counter == 4’b0010) begin //计数满2输出反转

clkout <= ~clkout;

counter <= counter + 4'b1;

end

else if (counter == 4’b0101) begin //计数满4输出反转同时清零clkout <= ~clkout;

counter <= 0;

end

else begin

counter <= counter + 4'b1;

end

end

endmodule

b)十进制分频代码

//计数器实现10分频,计数到达4和9,输出始终翻转一次,且计数达到9时计数清零

module count10(rst, clk, clkout, counter);

input rst;

input clk;

output reg clkout;

output reg [3:0]counter;

always @(negedge clk or negedge rst) begin

if (~rst) begin counter<=0;clkout<=0; end

//计数满4输出反转

else if (counter ==4'b0100) begin clkout<=~clkout;counter<=counter+1; end //计数满9输出反转同时计数清零

else if (counter ==4'b1001) begin clkout<=~clkout;counter<=0; end

else begin counter<=counter+1; end

end

endmodule

c)时钟分频代码

always @(negedge clk or negedge rst10ms) begin

if(~rst10ms)begin clk10msreg<=0;clk10ms<=0;end

else if(clk10msreg==249999)begin clk10ms<=~clk10ms;clk10msreg<=0;end

else begin clk10msreg<=clk10msreg+1;

end

d)状态机代码

always @(negedge clk or negedge clear) begin

if (~clear) begin

state <= idlestate; rst <= 0; rst10ms <= 0;

end

else begin

case (state)

idlestate:begin if(~start)begin state<=prestate;rst<=0;rst10ms<=0;end

else begin state<=idlestate;end

end

prestate: begin state<=runstate;rst<=1;rst10ms<=1;end

holdstate:begin if(~start)begin state<=runstate;rst<=1;rst10ms<=1;end

else if(~stop)begin state<=idlestate;rst<=1;rst10ms<=0;end

else begin state<=holdstate;end

end

runstate:begin if(~stop)begin state<=idlestate;rst<=1;rst10ms<=0;end

else if(~hold)begin state<=holdstate;rst<=1;rst10ms<=0;end

else begin state<=runstate;end

end

default: state <= state;

endcase

end

end

e)各级分频代码

count6 min10counter(rst, clk10min,clk1h, timeout[7]); //10min6分频得1h

count10 min1counter (rst, clk1min, clk10min, timeout[6]);//1min 10分频得10min

count6 sec10counter(rst, clk10s, clk1min, timeout[5]);//10s 6分频得1min

count10 sec1counter (rst, clk1s, clk10s, timeout[4]);// 1s 10分频得10s

count10 ms100counter(rst, clk100ms, clk1s, timeout[3]); // 100ms10分频得1s

count10 ms10counter (rst, clk10ms, clk100ms, timeout[2]); // 10ms10分频得100ms

assign timeout[1] = 4'b1111;

assign timeout[0] = 4'b1111;

5.实验结果及分析

实验中共有四个控制按键分别测试其控制功能即启动,暂停,停止,清空。

当按下启动按键时计时器开始计时;

当按下暂停按键时计时器停止计数,再按启动又继续计时;

当按下停止按键时停止计时,再按启动从0开始;

无论何时只要按下清空按键计时器便清零。

其现象如下:

6.实验心得

1.编译时出现许可证问题;分析是软件并未破解,关闭软件重新破解。

2.编译出错;分析是代码有错,检查代码更正错误,重新编译。

3.通过本次实验对状态转移图有了更多的了解,对其应用方法有了基本的掌握。

4.进一步熟悉了硬件编程语言。