简单的除法器设计系统

电路中的除法器设计

电路中的除法器设计在电路设计中,除法器是一种十分重要的组件。

它可以将输入的数字进行除法运算,将商和余数输出。

除法器在计算机和数字信号处理器等电子设备中被广泛使用,因此其设计和优化具有重要意义。

一、除法器的基本原理除法运算是一种复杂的运算,要实现除法器的设计,首先需要了解其基本原理。

除法器的基本原理是通过移位和减法实现的。

在将被除数和除数输入除法器后,除法器将被除数和除数进行比较,并开始迭代过程。

在每一次迭代中,被除数的位数向左移动,直到其高位与除数相等或超过除数。

然后,除法器进行减法操作,将除数减去被除数,结果作为商的一位。

此后,商持续左移,被减数保持不变,重复上述过程,直到所有的商位都得出。

二、除法器的设计策略在除法器的设计中,有几种常见的策略可以考虑。

1. 组合逻辑除法器:这种类型的除法器使用组合逻辑电路实现,通过减法器、比较器和移位器等组件的组合来实现除法运算。

组合逻辑除法器的优点是速度较快,但缺点是占用较多的电路资源。

2. 串行逻辑除法器:与组合逻辑除法器相反,串行逻辑除法器使用顺序逻辑电路实现。

它通过一个时钟信号,逐位地进行计算,因此典型的串行逻辑除法器速度较慢。

但串行逻辑除法器更节省电路资源,因此在一些资源有限的场景中得到了广泛应用。

3. 重复系列除法器:这种除法器通过多个并行的子除法器实现,并行计算多个位的商。

重复系列除法器具有较高的性能,但需要更多的电路资源和功耗。

三、除法器的优化方法为了提高除法器的性能和效率,可以采用一些优化方法。

1. 位级并行思路:通过将除法器分解为多位的子除法器,并行计算多个子除法器,可以大幅提高除法器的速度。

这种方法在重复系列除法器中得到了广泛应用。

2. 乘法相关技巧:利用乘法器计算除法运算,可以加速除法器的运算速度。

通过将除数进行逆运算,转化为乘法操作,可以利用乘法器的高速性能,提升除法器的效率。

3. 进制转换思想:将数字进行二进制到十进制的转换,然后进行简单的除法运算,可以减少运算的复杂程度,提高除法器的运算速度。

Verilog除法器设计(包含单步设计和流水线设计)

Verilog除法器设计(包含单步设计和流水线设计)1.单步设计:单步设计是最简单的一种除法器设计,其原理是将被除数和除数逐位进行比较和计算,直到得到商和余数。

首先,需要定义Verilog模块的输入和输出端口。

输入包括被除数(dividend)和除数(divisor),输出包括商(quotient)和余数(remainder)。

同时,还需要定义一些辅助信号,如计数器和比较器。

```verilogmodule Dividerinput [N-1:0] dividend,input [N-1:0] divisor,output [N-1:0] quotient,output [N-1:0] remainder```在单步设计中,使用一个循环进行逐位比较和计算,直到得到商和余数。

在每一步循环中,被除数向左移动一位,并与除数进行比较。

如果被除数大于或等于除数,则商的对应位为1,否则为0。

然后,将商的对应位赋值给商,并从被除数中减去除数的相应部分。

最后,余数更新为被除数。

```verilogreg [N-1:0] temp_dividend;reg [N-1:0] temp_remainder;reg [N-1:0] temp_quotient;integer i;temp_dividend = dividend;temp_remainder = {N{1'b0}};temp_quotient = {N{1'b0}};for (i = 0; i < N; i = i+1) begintemp_remainder = temp_dividend;if (temp_remainder >= divisor) begin temp_quotient[i] = 1'b1;temp_dividend = temp_remainder - divisor; endtemp_dividend = temp_dividend << 1;endquotient = temp_quotient;remainder = temp_dividend;endendmodule```以上就是单步设计的Verilog除法器代码。

基于FPGA的4位二进制数除法器设计

基于FPGA的4位⼆进制数除法器设计1. 设计要求: 设计⼀个4位⼆进制数除法器,如下图所⽰。

其中,a[3:0]为被除数,b[3:0]为除数,s[3:0]为商,r[3:0]为余数。

2. 设计原理: 和⼗进制除法类似,以计算 27 除以 5 的过程为例:除法运算过程如下:(1) 取被除数的⾼⼏位数据,位宽和除数相同(实例中是 3bit 数据)。

(2) 将被除数⾼位数据与除数作⽐较,如果前者不⼩于后者,则可得到对应位的商为 1,两者做差得到第⼀步的余数;否则得到对应的商为0,将前者直接作为余数。

(3) 将上⼀步中的余数与被除数剩余最⾼位 1bit 数据拼接成新的数据,然后再和除数做⽐较。

可以得到新的商和余数。

(4) 重复过程 (3),直到被除数最低位数据也参与计算。

需要说明的是,商的位宽应该与被除数保持⼀致,因为除数有可能为1。

所以上述⼿动计算除法的实例中,第⼀步做⽐较时,应该取数字 27最⾼位 1 (3’b001) 与 3’b101 做⽐较。

根据此计算过程,设计位宽可配置的流⽔线式除法器,流⽔延迟周期个数与被除数位宽⼀致。

3. 设计实现module divider_4bit(input wire [3:0] a,input wire [3:0] boutput wire [3:0] s,output wire [3:0] y);wire [3:0] part_0;wire [3:0] part_1;wire [3:0] part_2;wire [3:0] part_3;assign s[3] = a[3] >= b; //最⾼位的商s[3]assign part_3 = (s[3] == 1'b1 )? a[3] - b : a[3];assign s[2] = {part_3, a[2]} >= b;assign part_2 = (s[2] == 1'b1) ? {part_3, a[2]} - b : {part_3, a[2]};assign s[1] = {part_2, a[1]} >= b;assign part_1 = (s[1] == 1'b1) ? {part_2, a[1]} - b : {part_2, a[1]};assign s[0] = {part_1, a[0]} >= b;assign part_0 = (s[0] == 1'b1) ? {part_1, a[0]} - b : {part_1, a[0]};assign y = part_0;endmodule4. 仿真验证`timescale 1ns/1psmodule divider_4bit_tb();reg [3:0] a;reg [3:0] b;wire [3:0] s;wire [3:0] y;wire [3:0] tb_s;wire [3:0] tb_y;assign tb_s = a / b;assign tb_y = a % b;divider_4bit divider_4bit_inst (.a (a),.b (b),.s (s),.y (y));initial beginrepeat(20)begina = {$random} % 16;b = {$random} % 16;# 20;endendendmodule注:0/0=⽆穷⼤,任何数除以零(⽆穷⼩)得⽆穷⼤,⽽在Veriog中,默认0/0=错误结果,s[3:0]最⼤值为15。

8位除法器版图设计

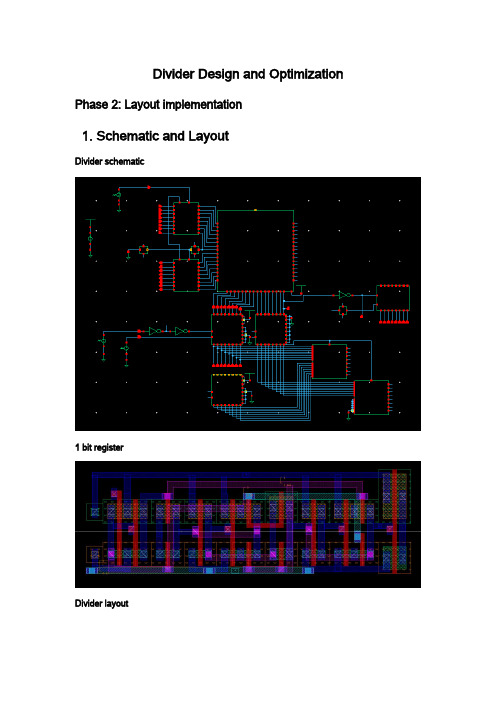

Divider Design and Optimization Phase 2: Layout implementation1.Schematic and LayoutDivider schematic1 bit registerDivider layoutAs we can see from above figure, the size of layout is about 25722um approximately. The layout include two 16 bits selector, three right shift register, three 8 bits register which can be set by parallel input when load=1. 2. The successful diagrams of DRC, LVS, PEX are shown as followDRCLVSPEX3.Simulation waveforms of quotient and remainder outputs.Quotientwe can see quotient here at the last one clock period is 0000 0011 (the picture only shows the lower four bits quotient q3q2q1q0=0011)Remainderwe can see remainder here at the last one clock period is 0000 0001 (the picture only shows the lower four bits remainder r3r2r1r0=0001)4.Future workWe consider that this design have some problem when we design it’s schematic.(1)Because we don’t use addition mode of our ALU (the original dividend is saved in a 8 bits register, we don’t need to add the negative remainder result to the divisor), we can replace the ALU by a 16 bits subtractor, the XOR in ALU can be replaced by inverter. (2)Because we don’t care all the bits result, we just care the highest bits of ALU output (this bits shows if the remainder is negative or positive), maybe the other high 7 bits output () can be throw away, so only 9 bits (the highest bit and lower 8 bits output of ALU) register is enough. After above improvement, the corresponding input of ALU can be set to 0 at all the time.(3)Maybe we don’t need to calculate all the 16 bits subtraction result, the divisor can be shift one by one bit, then all the 16 bit modules can be replace by 8 bit modules.。

(完整word版)计算器的设计

目录1。

设计要求 (2)2.设计方案与论证 (2)2.1总体设计思路 (2)2。

2总体方案 (2)3.设计原理及电路图 (4)3.1硬件设计 (4)3。

2软件设计 (11)3。

3 算术运算程序设计 (12)3。

4 显示程序设计 (13)4。

器件清单 (14)5.器件识别与检测 (15)6。

控制系统实现(软件编程与调试) (16)6。

1 硬件调试 (17)6.2 软件调试 (17)6。

3软件编程 (18)7。

设计心得 (28)8。

参考文献 (29)1。

设计要求要求计算器能实现加减乘除四种运算,具体如下:1.加法:四位整数加法,计算结果若超过四位则显示计算错误2.减法:四位整数减法,计算结果若小于零则显示计算错误3.乘法:多位整数乘法,计算结果若超过四位则显示计算错误4.除法:整数除法5.有清除功能设计要求:分别对键盘输入检测模块;LCD显示模块;算术运算模块;错误处理及提示模块进行设计,keil与protues仿真分析其设计结果。

2。

设计方案与论证2。

1总体设计思路:本计算器是以MCS-51系列8051单片机为核心构成的简易计算器系统。

该系统通过单片机控制,实现对4*4键盘扫描进行实时的按键检测,并把检测数据存储下来。

整个计算器系统的工作过程为:首先存储单元初始化,显示初始值和键盘扫描,判断按键位置,查表得出按键值,单片机则对数据进行储存与相应处理转换,之后送入数码管动态显示。

整个系统可分为三个主要功能模块:功能模块一,实时键盘扫描;功能模块二,数据转换为了数码管显示;功能模块三,数码管动态显示。

2.2总体方案:根据功能和指示要求,本系统选用以MCS—51单片机为主控机.通过扩展必要的外围接口电路,实现对计算器的设计。

具体设计如下:1、由于要设计的是简单的计算器,可以进行四则运算,为了得到教好的显示效果,采用LCD 显示数据和结果。

2、另外键盘包括数字键(0—9)、符号键(+、—、*、/)、清除键和等号键,故只需要16个按键即可,设计中采用集成的计算机键盘.3、执行程序:开机显示零,等待键入数值,当键入数字,通过LCD显示出来,当键入+、—、*、/运算符,计算器在内部执行数值转换和存储,并等待再次键入数值后将显示键入的数值,按等号就会在LCD上输出运算结果.4、错误提示:当单片机执行程序中有错误时,会在LCD上显示相应的提示,如:当输入的数值或计算器得到的结果大于计算器的显示范围时,计算器会在LCD上提示溢出;当除数为0时,计算器会在LCD上提示错误.①由于要设计的是简单的计算器,可以进行四则运算,对数字的大小范围要求不高故我们采用可以进行四位数字的运算,选用8 个LED 数码管显示数据和结果。

模拟除法器电路原理

模拟除法器电路原理一、引言除法运算是数字电路中常用的一种运算方式,而除法器电路则是实现除法运算的重要组成部分。

本文将介绍模拟除法器电路的原理和工作过程。

二、模拟除法器电路的基本原理模拟除法器电路是一种能够对两个输入数进行除法运算的电路,它能够将除数和被除数作为输入,输出商和余数。

模拟除法器电路的设计和实现需要考虑除法运算的特性和数电电路的基本原理。

三、模拟除法器电路的设计要点1. 除法器电路的输入包括除数和被除数,输出包括商和余数。

除数和被除数的位数决定了除法器电路的复杂度和精度。

2. 除法器电路通常采用串行除法算法或并行除法算法来实现除法运算。

串行除法算法需要多个时钟周期完成一次运算,而并行除法算法能够在一个时钟周期内完成运算。

3. 除法器电路中需要包含除法运算所需的基本运算单元,如加法器、减法器、比较器等。

这些基本运算单元能够完成除法算法中的各个步骤。

4. 除法器电路中需要考虑特殊情况的处理,如除数为0、被除数为0等,这些情况需要特殊的处理逻辑来确保电路的正确运行。

四、模拟除法器电路的工作过程1. 输入除数和被除数,将它们送入除法器电路。

2. 电路根据选择的算法和电路设计,进行除法运算。

3. 电路输出商和余数,可以通过显示屏、LED灯等方式显示。

五、模拟除法器电路的应用模拟除法器电路广泛应用于各种需要进行除法运算的场合,如数值计算、信号处理、通信系统等。

除法器电路能够高效地对输入数据进行除法运算,为各种应用提供了便利。

六、模拟除法器电路的优缺点1. 优点:模拟除法器电路能够高效地进行除法运算,能够满足各种应用的需求。

2. 缺点:模拟除法器电路的设计和实现比较复杂,需要考虑各种特殊情况的处理,电路的规模较大。

七、总结模拟除法器电路是一种能够对两个输入数进行除法运算的电路,它能够将除数和被除数作为输入,输出商和余数。

模拟除法器电路的设计和实现需要考虑除法运算的特性和数电电路的基本原理。

模拟除法器电路在各种应用中起到了重要的作用,能够高效地进行除法运算。

除法器设计

除法器设计摘要: 本设计要求设计一个简单的除法器,根据要求采用乘法器BG314与运算放大器3554AM以及外部电源共同实现除法器功能.乘法器用以实现乘法运算,然后通过运算放大器工作于负反馈状态实现信号的放大,并由自制电源电路供电.通过对系统各模块进行仔细的分析,了解了各器件的性能与用途后,便可将其运用到自己的设计当中去.电路设计完成后,开始对系统进行测试,方法有两种,可以通过对系统电路在Multisim软件下仿真测试,也可以做出相应的印制电路板来进行测试.在本设计中,通过仿真测试与实物测试相结合的综合测试后,发现系统基本能达到设计要求.关键字: 乘法器运算放大器电源Multisim 印制电路板Summary: This design requests to design a simple division machine, adopting the multiplication machine BG314 and the operation enlarger 3554 AMses and the exterior power supplies according to the request to carry out the division machine function together.The multiplication machine carries out the multiplication operation in order to, then pass to operate the enlarger work to carry out the signal to enlarge in the negative feedback appearance, and from the self-control power supply electric circuit power supply.Pass to carry on the careful analysis to each mold of system piece, after understanding the function and uses of each machine piece, can make use of it to own design then in the middle.The electric circuit is after design complete, starting carrying on the test to the system, the method have two kinds of, can pass to imitate the true test to the system electric circuit under the software of Multisim, can also do a homologous of print and make circuit board to carry on the test.In this design, after passing to imitate the comprehensive test that the true test and real objects test combine together, discover that the system is basic and can attain design to request.Key word: The multiplication machine operation enlarger power supply Multisim prints to make the circuit board目录1、系统方案设计与论证 (1)1.1 设计要求 (1)1.2 系统基本方案 (1)1.2.1 各模块方案选择与论证 (1)(1) 乘法器模块 (1)(2) 运算电路模块 (2)(3) 电源模块 (2)(4) 显示模块 (2)1.2.2系统各模块的最终方案 (3)2、系统的硬件设计与实现 (3)2.1 系统硬件的基本组成部分 (3)2.2 主要单元电路设计 (3)2.2.1 乘法器电路设计 (3)2.2.2 运算电路设计 (5)2.2.3 电源电路设计 (9)2.2.4 显示电路的设计 (13)3、系统测试与优化 (13)3.1 电源部分测试 (13)3.2 其他部分测试 (14)3.3 系统实现的功能 (15)4 结论 (15)4.1 评价 (15)4.2 心得 (15)5 参考文献 (16)6附录 (16)6.1 器件清单 (16)6.2 系统原理图 (16)1、系统方案设计与论证1.1 设计要求设计一个简单的除法器(Vx=0.2V V y=0.5V K=1 可用集成芯片做)1.2 系统基本方案根据题目要求,系统可以划分为集成乘法器模块、集成运算放大器模块和12V电源模块.模块框图如图1.2所示.为实现各模块的功能,分别做了几种不同的设计方案并进行了论证.图1.2 除法器基本模块方框图1.2.1 各模块方案选择与论证(1) 乘法器模块根据题目要求,模拟乘法器主要用于实现两个互不相关的模拟信号间的相乘的功能.对乘法器的选择有以下两种方案:方案一:采用集成模拟乘法器BG314. 集成模拟乘法器是实现两个模拟信号相乘的器件,它广泛用于乘法、除法、乘方和开方等模拟运算,同时也广泛用于信息传输系统作为调幅、解调、混频、鉴相和自动增益控制电路,是一种通用性很强的非线性电子器件,目前已有多种形式、多品种的单片集成电路,同时它也是现代一些专用模拟集成系统中的重要单元.该集成模拟乘法器不仅功能强大而且外部电路简单,工作原理易理解.方案二:采用分离元件组合电路.分离元件组合电路参数可自行调节,但是精度较差,在使用过程中难度较大.而且由于电路较复杂,增加了焊接的难度.根据以上论述,考虑到各方面的因素,在本设计中,采用简单、方便、可靠的集成模拟乘法器来实现.(2) 运算电路模块根据题目要求,运算电路主要用于实现信号的放大功能.对于运算放大器的选择有以下三种方案:方案一:采用单运放集成芯片3554AM.这是一款较老的芯片,在平时的电路设计当中常常要用到,主要是因为它是同类芯片当中功能相似但电路结构却相对简单的一种.方案二:采用单运放集成芯片LM741.这是曾经学到过的一种芯片,我们对它较熟悉,而且对其内部结构和功能也有所了解.它的各参数都较稳定,有较高的共模抑制比,也是需要15V的双电源供电.方案三:采用双运放集成芯片LM358.这也是一款较常用到的芯片,由于是双运放,所以功能也相应的有所加强,但是我们所用到的电路比较简单,结果可能使它的很多功能都没有得到运用,导致对资源的浪费.在本设计中,对各方案进行比较论证之后,我们采用熟悉简单而且性能优良的单运放集成芯片3554AM来实现对信号的放大.(3) 电源模块电源模块主要用于实现对各模块供电的功能.对于电源模块的选择有以下三种方案: 方案一:采用1.5V常用电池串接而成.这种方法简单易懂,但是精确度不够,稳定度也不高,当电池里面的电用光之后,便不在具有供电功能.方案二:采用直接购买电源的方法.在市场上可以直接买到相应的电源,但是考虑到经济上的原因,显然这并不合适.方案三:采用自制整流电路.这种方法简单可行,可以得到精确的电压值,而且稳定度高,可以长期使用.正好可以让自己所学的知识在实践中得到很好的运用.其方框图如图1.3所示:图1.3 整流电路方框图根据以上论述,考虑到经济、实用等方面因素,在本设计中选择方案三,采用自制整流电路来实现.(4) 显示模块根据不同的需要,显示模块可以有以下三种不同的方案可供选择:方案一:使用数码管显示时间和温度.数码管具有低功耗、低压、寿命长、耐老化、防晒、防潮、防火、防高低温等优点,对外界环境要求低,易于维护,同时其精度比较高,操作简单.另外,数码管采用BCD码显示数字,程序编译简单,资源占用较少.方案二:使用液晶显示屏显示. 液晶显示屏(LCD)具有轻薄短小,低耗电量,无辐射危险,平面直角显示以及影象稳定不闪烁,可视面积大等优势.方案三:采用数字电压表进行直接测量.数字电压表读数精确,是常用器件,使用起很方便.而且性能稳定,读数方便.根据以上论述,由于我们暂时对LCD还不是很熟悉,对其性能还不是很了解,而使用数码管会使电路变的复杂,而且还要通过编程来实现,因此我们在设计中选择直接用数字电压表进行测量显示读数.1.2.2 系统各模块的最终方案经过仔细的分析与论证,决定了系统各模块的最终方案如下:(1)乘法器模块:采用集成模拟乘法器BG314实现;(2) 运算电路模块: 采用单运放集成芯片LM741;(3) 电源模块: 采用自制整流电路实现;(4) 显示模块: 采用数字电压表进行直接测量.系统的基本框图如图1.4所示.图1.4 系统的基本框图模拟乘法器主要用于实现两个互不相关的模拟信号间的相乘的功能,而运算电路主要用于实现对信号的放大.其工作过程如下:电源加电后, 经过整流电路的整流以后可以得到运放所需要的+(-)15V电压,从乘法器输入端输入被处理电压,经过运放电路处理后便可在数字电压表上看到经过除法器处理过后的电压值了.2、系统的硬件设计与实现2.1 系统硬件的基本组成部分本题是一个除法器的综合设计,在设计中运用了模拟乘法器处理技术、电压整流技术. 2.2 主要单元电路设计2.2.1 乘法器电路设计(1) 模拟乘法器的基本特性模拟乘法器是一种完成两个模拟信号(连续变化的电压或电流)相乘作用的电子器件,通常具有两个输入端和一个输出端,电路符号如图2.1所示。

加减交替阵列除法器的设计与仿真实现

加减交替阵列除法器的设计与仿真实现一、引言随着数字电路的发展,除法器在计算机和通信系统中的应用越来越广泛。

加减交替阵列除法器是一种高效的除法器,具有运算速度快、面积小等优点。

本文将详细介绍加减交替阵列除法器的设计与仿真实现。

二、加减交替阵列除法器原理加减交替阵列除法器是一种基于移位和加减运算的快速除法器。

其主要原理如下:1. 将被除数左移n位,得到一个n+1位的数(其中最高位为0)。

2. 对于每个n+1位的数,采用加减交替的方式进行运算。

3. 在第n步时,判断商是否已经求出。

4. 如果商未求出,则返回第1步。

三、加减交替阵列除法器设计1. 系统框图加减交替阵列除法器由以下模块组成:被除数寄存器、商寄存器、余数寄存器、控制单元、计算单元和状态机。

系统框图如下所示:2. 系统模块设计(1)被除数寄存器被除数寄存器用于存储待处理的被除数。

它由一个n位的寄存器和一个移位器组成,可以将被除数左移n位。

(2)商寄存器商寄存器用于存储计算得到的商。

它由一个n位的寄存器和一个移位器组成,可以将商左移1位。

(3)余数寄存器余数寄存器用于存储计算得到的余数。

它由一个n+1位的寄存器和一个移位器组成,可以将余数左移1位。

(4)控制单元控制单元用于控制整个系统的运行。

它根据状态机的输出信号来控制各个模块之间的数据传输和运算。

(5)计算单元计算单元是加减交替阵列除法器最核心的部分,用于进行加减运算。

它由若干个加法器和减法器组成,每个加法器或减法器都能够进行一次加或减运算。

(6)状态机状态机用于控制控制单元的工作状态,并输出相应的信号。

它有以下三种状态:a. 初始化状态:在这个状态下,被除数、商、余数等变量都被初始化。

b. 运行状态:在这个状态下,加减交替阵列除法器按照原理进行运算。

c. 结束状态:在这个状态下,商已经求出,整个系统停止工作。

四、加减交替阵列除法器仿真实现1. 系统仿真为了验证加减交替阵列除法器的正确性,需要对其进行仿真。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

除法器设计摘要: 本设计要求设计一个简单的除法器,根据要求采用乘法器BG314与运算放大器3554AM以及外部电源共同实现除法器功能.乘法器用以实现乘法运算,然后通过运算放大器工作于负反馈状态实现信号的放大,并由自制电源电路供电.通过对系统各模块进行仔细的分析,了解了各器件的性能与用途后,便可将其运用到自己的设计当中去.电路设计完成后,开始对系统进行测试,方法有两种,可以通过对系统电路在Multisim软件下仿真测试,也可以做出相应的印制电路板来进行测试.在本设计中,通过仿真测试与实物测试相结合的综合测试后,发现系统基本能达到设计要求.关键字: 乘法器运算放大器电源Multisim 印制电路板Summary: This design requests to design a simple division machine, adopting the multiplication machine BG314 and the operation enlarger 3554 AMses and the exterior power supplies according to the request to carry out the division machine function together.The multiplication machine carries out the multiplication operation in order to, then pass to operate the enlarger work to carry out the signal to enlarge in the negative feedback appearance, and from the self-control power supply electric circuit power supply.Pass to carry on the careful analysis to each mold of system piece, after understanding the function and uses of each machine piece, can make use of it to own design then in the middle.The electric circuit is after design complete, starting carrying on the test to the system, the method have two kinds of, can pass to imitate the true test to the system electric circuit under the software of Multisim, can also do a homologous of print and make circuit board to carry on the test.In this design, after passing to imitate the comprehensive test that the true test and real objects test combine together, discover that the system is basic and can attain design to request.Key word: The multiplication machine operation enlarger power supply Multisim prints to make the circuit board目录1、系统方案设计与论证 (1)1.1 设计要求 (1)1.2 系统基本方案 (1)1.2.1 各模块方案选择与论证 (1)(1) 乘法器模块 (1)(2) 运算电路模块 (2)(3) 电源模块 (2)(4) 显示模块 (2)1.2.2系统各模块的最终方案 (3)2、系统的硬件设计与实现 (3)2.1 系统硬件的基本组成部分 (3)2.2 主要单元电路设计 (3)2.2.1 乘法器电路设计 (3)2.2.2 运算电路设计 (5)2.2.3 电源电路设计 (9)2.2.4 显示电路的设计 (13)3、系统测试与优化 (13)3.1 电源部分测试 (13)3.2 其他部分测试 (14)3.3 系统实现的功能 (15)4 结论 (15)4.1 评价 (15)4.2 心得 (15)5 参考文献 (16)6附录 (16)6.1 器件清单 (16)6.2 系统原理图 (16)1、系统方案设计与论证1.1 设计要求设计一个简单的除法器(Vx=0.2V Vy=0.5V K=1 可用集成芯片做)1.2 系统基本方案根据题目要求,系统可以划分为集成乘法器模块、集成运算放大器模块和12V电源模块.模块框图如图1.2所示.为实现各模块的功能,分别做了几种不同的设计方案并进行了论证.图1.2 除法器基本模块方框图1.2.1 各模块方案选择与论证(1) 乘法器模块根据题目要求,模拟乘法器主要用于实现两个互不相关的模拟信号间的相乘的功能.对乘法器的选择有以下两种方案:方案一:采用集成模拟乘法器BG314. 集成模拟乘法器是实现两个模拟信号相乘的器件,它广泛用于乘法、除法、乘方和开方等模拟运算,同时也广泛用于信息传输系统作为调幅、解调、混频、鉴相和自动增益控制电路,是一种通用性很强的非线性电子器件,目前已有多种形式、多品种的单片集成电路,同时它也是现代一些专用模拟集成系统中的重要单元.该集成模拟乘法器不仅功能强大而且外部电路简单,工作原理易理解.方案二:采用分离元件组合电路.分离元件组合电路参数可自行调节,但是精度较差,在使用过程中难度较大.而且由于电路较复杂,增加了焊接的难度.根据以上论述,考虑到各方面的因素,在本设计中,采用简单、方便、可靠的集成模拟乘法器来实现.(2) 运算电路模块根据题目要求,运算电路主要用于实现信号的放大功能.对于运算放大器的选择有以下三种方案:方案一:采用单运放集成芯片3554AM.这是一款较老的芯片,在平时的电路设计当中常常要用到,主要是因为它是同类芯片当中功能相似但电路结构却相对简单的一种.方案二:采用单运放集成芯片LM741.这是曾经学到过的一种芯片,我们对它较熟悉,而且对其内部结构和功能也有所了解.它的各参数都较稳定,有较高的共模抑制比,也是需要15V的双电源供电.方案三:采用双运放集成芯片LM358.这也是一款较常用到的芯片,由于是双运放,所以功能也相应的有所加强,但是我们所用到的电路比较简单,结果可能使它的很多功能都没有得到运用,导致对资源的浪费.在本设计中,对各方案进行比较论证之后,我们采用熟悉简单而且性能优良的单运放集成芯片3554AM来实现对信号的放大.(3) 电源模块电源模块主要用于实现对各模块供电的功能.对于电源模块的选择有以下三种方案: 方案一:采用1.5V常用电池串接而成.这种方法简单易懂,但是精确度不够,稳定度也不高,当电池里面的电用光之后,便不在具有供电功能.方案二:采用直接购买电源的方法.在市场上可以直接买到相应的电源,但是考虑到经济上的原因,显然这并不合适.方案三:采用自制整流电路.这种方法简单可行,可以得到精确的电压值,而且稳定度高,可以长期使用.正好可以让自己所学的知识在实践中得到很好的运用.其方框图如图1.3所示:图1.3 整流电路方框图根据以上论述,考虑到经济、实用等方面因素,在本设计中选择方案三,采用自制整流电路来实现.(4) 显示模块根据不同的需要,显示模块可以有以下三种不同的方案可供选择:方案一:使用数码管显示时间和温度.数码管具有低功耗、低压、寿命长、耐老化、防晒、防潮、防火、防高低温等优点,对外界环境要求低,易于维护,同时其精度比较高,操作简单.另外,数码管采用BCD码显示数字,程序编译简单,资源占用较少.方案二:使用液晶显示屏显示. 液晶显示屏(LCD)具有轻薄短小,低耗电量,无辐射危险,平面直角显示以及影象稳定不闪烁,可视面积大等优势.方案三:采用数字电压表进行直接测量.数字电压表读数精确,是常用器件,使用起很方便.而且性能稳定,读数方便.根据以上论述,由于我们暂时对LCD还不是很熟悉,对其性能还不是很了解,而使用数码管会使电路变的复杂,而且还要通过编程来实现,因此我们在设计中选择直接用数字电压表进行测量显示读数.1.2.2 系统各模块的最终方案经过仔细的分析与论证,决定了系统各模块的最终方案如下:(1)乘法器模块:采用集成模拟乘法器BG314实现;(2) 运算电路模块: 采用单运放集成芯片LM741;(3) 电源模块: 采用自制整流电路实现;(4) 显示模块: 采用数字电压表进行直接测量.系统的基本框图如图1.4所示.图1.4 系统的基本框图模拟乘法器主要用于实现两个互不相关的模拟信号间的相乘的功能,而运算电路主要用于实现对信号的放大.其工作过程如下:电源加电后, 经过整流电路的整流以后可以得到运放所需要的+(-)15V电压,从乘法器输入端输入被处理电压,经过运放电路处理后便可在数字电压表上看到经过除法器处理过后的电压值了.2、系统的硬件设计与实现2.1 系统硬件的基本组成部分本题是一个除法器的综合设计,在设计中运用了模拟乘法器处理技术、电压整流技术. 2.2 主要单元电路设计2.2.1 乘法器电路设计(1) 模拟乘法器的基本特性模拟乘法器是一种完成两个模拟信号(连续变化的电压或电流)相乘作用的电子器件,通常具有两个输入端和一个输出端,电路符号如图2.1所示。

图2.1 模拟乘法器的电路符号若输入信号为x u , y u ,则输出信号o u 为:o u =k y u x u式中: k 为乘法器的增益系数或标尺因子,单位为V 1 .根据两个输入电压的不同极性,乘法输出的极性有四种组合,用图2.2所示的工作象限来说明。

图2.2 模拟乘法器的工作象限 若信号x u 、y u 均限定为某一极性的电压时才能正常工作,该乘法器称为单象限乘法器;若信号x u 、y u 中一个能适应正、负两种极性电压,而另一个只能适应单极性电压,则为二象限乘法器;若两个输入信号能适应四种极性组合,称为四象限乘法器。

(2) BG314内部结构如图2.3所示,外部电路如图2.4所示:图2.3 BG314内部电路图2.4 BG314 外部电路(3) BG314主要技术参数 表1 BG314技术参数(4) BG314 内部结构分析输出电压o u =k x u y u式中 k=yx ox c R R I R 2为乘法器的增益系数。