基于FPGA和双DSP的高速视频图像处理系统设计(精)

基于FPGA_DSP的高清视频图像系统设计与实现_高杨

测试系统与模块化组件 电 子 测 量 技 术 ELEC TRON IC M EAS UREM EN T TECH NO LOGY 第34卷第1期2011年1月 基于FPGA+DSP的高清视频图像系统设计与实现高 杨 刘荣科 胡 伟(北京航空航天大学电子信息工程学院北京100191)摘 要:无人机在侦察、测绘等领域对图像分辨率的要求不断提高,随之带来了数据量的显著增大,其次,视频图像系统与传统遥控遥测系统的融合也是设计中需要考虑的。

针对以上问题,设计并实现了一种基于F PGA+DSP的机载高清视频图像系统,包括机载设备端和地面站端两部分,最高支持分辨率为1280×720,每秒25帧的M PEG-4实时视频编解码,平均码速率在5M bps以下。

图像分辨率和视频码率可通过上行遥控指令动态切换。

视频数据与遥测数据实现了组帧传输。

设备体积小、功耗低、可靠性高,成功完成了挂飞实验。

关键词:M PEG-4;高清视频;遥控;遥测;FPG A;DSP中图分类号:V243.5 文献标识码:ADesign and implementation of high definition videoimage system based on FPGA+DSPG ao Y ang L iu Rong ke H u Wei(Beijing University of Aeronautics and A stronau tics Electronic and Information Engineering Ins tiiu te,Beijing100191)A bstract:T he requirements o f video imag e reso lution is eve r increa sing in the UA V reco nnaissance,mapping and other fields,w hich bring a significant amount of data increa se.In additio n,the integ ratio n of video imaging sy stem and traditio nal telecontr ol and telemetering sy stem is r equired in sy stem design consider atio n.T o solve the pr oblems abo ve, w e de sig n and implement an air bo rne hig h definitio n video image system based on F PG A+DSP,including tw o pa rts: airbo rne equipment end and g round statio n end,it suppor ted the maximum re so lutio n o f1280×720,25fr ame s per second in M PEG-4real-time video encoding and deco ding w ith the ave rage code ra te below5M bps.Imag e re so lutio n a nd video code ra te can be switched up by teleco mma nd dy namically.T he video data and telemetry data are transmitted in the same f rame.T he equipment w ith sma ll size,low pow er consumptio n,hig h re liability,successfully co mpleted flight e xperiments.Keywords:M PEG-4;hig h definition video;telecontro l;telemetering;FPG A;DSP0 引 言无人机广泛应用于军事侦察以及民用测绘等领域,其中的机载视频图像系统是机载电子系统中的重要环节之一。

基于FPGA+DSP的高清视频图像系统的硬件构建

基于FPGA+DSP的高清视频图像系统的硬件构建本文围绕基于FPGA+DSP的高清视频图像系统的硬件系统展开分析,从不同的层面展开对其架构和功能的探讨。

关键字:FPGA;DSP;视频;图像系统在实际的应用环境中,高效的视频编解码技术有着广泛的应用,尤其是当前无人机对于各类工作的广泛深入,更加使得民用测绘以及军用侦测等领域,都对视频图像处理技术提出了更为迫切的要求。

无论何种应用场景,都要求能够将无人机在高空中拍摄的地面图像发送回地面,并且进一步展开处理。

相对于民用系统而言,军用的要求明显更为严格。

从高空中获取到的图像数据,其数据帧内的目标像素都比较小并且目标数量大,这就要求尽可能大的提升图像分辨率,以获取到关于地面的更多情况。

但是与此同时,随着分辨率增加的是需要传输的数据总量,这无疑与当前相对而言比较有限的无线带宽资源形成矛盾。

在这样的背景之下,不仅仅需要发展出更为有效的无线数据传输方式,高效的视频编解码技术更是成为核心重点,直接关系到解析图像本身的效果。

对于需要多路视频传输,并且整体数据率固定的情况下,可以考虑降低单路视频分辨率或者提升单路压缩比来展开工作。

想要实现这种工作方式,系统应当能够实现对于分辨率和压缩比的动态调整和切换,在提升灵活性的同时面向实际需求展开服务。

除此以外,无人机与地面的通信过程中,还需要接收地面传送向无人机的指令并且加以落实,这些数据同样要求比较高的实时性特征。

如果将这些数据与视频数据放在两个独立信道,则传输工作的整体效率就会有所降低。

因此如何构建一个包括传统遥测数据和视频数据的广义遥测系统成为必需。

一、基于FPGA+DSP的高清视频图像系统框架建设在FPGA+DSP两项技术的共同支持之下,整个高清视频图像系统架构可以参见图1。

具体而言,就是大体划分为两个部分,即机载设备端的系统和地面设备端的系统,二者之间通过无线通信网络进行数据的传输和交换。

从图1中可以看到,对于机载设备端而言,经由影像传感器获取到的视频模拟信号数据,将交由AD进行处理,并且转化成为数字信号传递给FPGA,在经过FPGA的预处理之后,生成原始数字视频数据送达DSP进行视频编码。

基于DSP+FPGA技术的视频图像采集系统的设计

2 系统结构及基本原理

一个完整的图像处理系统不但要具备图像信号的 采集功能, 还要求能对图 像进行实时显

示, 且要求完成图 像信号的 及处 分析 理算法( 像压缩匆 。 这些算法的 如图 通常 运算量大, 时 同 又要满足实时显示的 要求, 因此采用高速D P S 芯片作为数据核心处理单元。 另外, 要求系统

采集, 集部分向 存储区 像数据; 块用于 采 该 写图 另一 外部对图 读取, S 像的 DP可以 该存 读取 储区中的图像数据。 双缓存结构的一个重要特点在于 D P对存储区的数据操作是随着双口 S R M存储地址来回 A 切换的。 / 当AD转换数据写满R M 1 FG A - 时, P A会向D P S 发出一 断 个中 信号, 此时, S 读取R M 1 DP A - 中的数据,同时, / AD转换数据写人R M 2 A -,当R M 中 A- 2 的数据写满时, P A会向D P FG S 发出一个中 断信号, 此时, S 读取R M 2 DP A - 中的数据,同 时, / AD转换数据写人R M 如此交替, A -, 1 实现数据的 写人与 读取同时进行。 于D P 由 S 读取 双口R M中 A 数据的 速度远远大于A〕 A 转换写人数据的速度, 为允许采集与外部访问的同时

进行, 故采用两块存储区 操作的乒乓式切换, 满足数据的实时交换的 要求。 系统的工作过程

为:

( DP N D 1 S 通过E A 信号控制采 ) 集系统的 运行, N D 1 数据采 统 工作, 当E A = 时, 集系 开始 则数据通过AD不断地送人双口R M, / A 且双口R M每隔2 A K发出 一个中 通知D P 断, S 读取

和DP 法比 的 势。 PA时 率 内 延小; 部 逻 硬 完 速 S 无 拟 优 FG 钟频 高, 部时 全 控制 辑由 件 成, 度

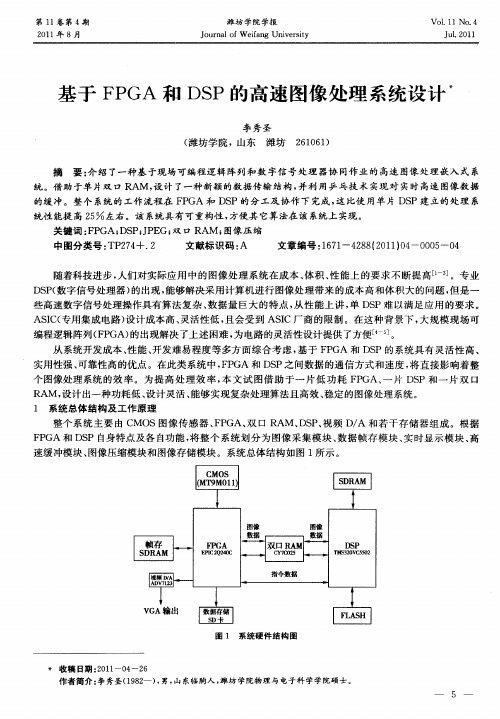

基于FPGA和DSP的高速图像处理系统设计

的缓 冲 。整 个 系统的 工作 流 程 在 F GA 和 D P的分 工 及协 作 下 完成 , 比使 用单 片 DS P S 这 P建 立 的处 理 系

统性 能提 高 2 左右 。该 系统 具 有可重 构性 , 5 方便 其 它算 法在该 系统上 实现 。

关键 词 : P F GA; S J E 双 口 RAM ; D P;P G; 图像 压 缩

第 1 卷 第 4期 1

21 0 1年 8月

潍 坊 学 院 学报

J u n l fW efn ie st o r a ia g Unv r i o y

V0 . 1N0 4 11 .

J 12 1 u. 0 1

基 于 F GA 和 DS P P的 高 速 图 像 处 理 系 统设 计

确 的配置之后 , 就可 以输 出 1 的图像数据 和一些 同步信 号 。在本系统 中采用 I O位 z C实现 传感 器配 置 ,P F— G 管脚通 过模拟 IC时序 , A 。 完成 对 C MOS 感器 的初始 化配置 , 中要 配置 的寄存 器如表 1 传 其 所示 。

表 1 MT M0 9 1寄存 器 设 置

编程逻 辑 阵列 ( P F GA) 出现解 决 了上 述 困难 , 电路 的灵活 性设 计提 供 了方便 [ 。 的 为 4 ]

从 系 统开发 成本 、 能 、 性 开发难 易程 度等 多方 面综 合考 虑 , 基于 F G 和 D P的系 统具 有 灵 活性 高 、 P A S 实用性 强 、 可靠性 高 的优 点 。在此类 系 统 中 ,P F GA和 DS P之 间 数据 的通 信 方式 和速 度 , 直 接影 响着 整 将 个 图像 处理 系统 的效 率 。为 提 高 处 理 效 率 , 文 试 图 借 助 于 一 片 低 功耗 F GA、 片 D P和 一 片 双 口 本 P 一 S

基于FPGA和DSP的高速图像处理系统设计

基于FPGA和DSP的高速图像处理系统设计李秀圣【摘要】A high-efficient image processing embedded system which is based on the field programmable gate array and high-speed digital signal processor was designed in this paper.With a dual-port RAM,a novel data transmission structure was designed,and ping-pong te%介绍了一种基于现场可编程逻辑阵列和数字信号处理器协同作业的高速图像处理嵌入式系统。

借助于单片双口RAM,设计了一种新颖的数据传输结构,并利用乒乓技术实现对实时高速图像数据的缓冲。

整个系统的工作流程在FPGA和DSP的分工及协作下完成,这比使用单片DSP建立的处理系统性能提高25%左右。

该系统具有可重构性,方便其它算法在该系统上实现。

【期刊名称】《潍坊学院学报》【年(卷),期】2011(011)004【总页数】4页(P5-8)【关键词】FPGA;DSP;JPEG;双口RAM;图像压缩【作者】李秀圣【作者单位】潍坊学院,山东潍坊261061【正文语种】中文【中图分类】TP274.2随着科技进步,人们对实际应用中的图像处理系统在成本、体积、性能上的要求不断提高[1-3]。

专业DSP(数字信号处理器)的出现,能够解决采用计算机进行图像处理带来的成本高和体积大的问题,但是一些高速数字信号处理操作具有算法复杂、数据量巨大的特点,从性能上讲,单DSP难以满足应用的要求。

ASIC(专用集成电路)设计成本高、灵活性低,且会受到ASIC厂商的限制。

在这种背景下,大规模现场可编程逻辑阵列(FPGA)的出现解决了上述困难,为电路的灵活性设计提供了方便[4-5]。

基于DSP+FPGA技术的视频图像采集系统的设计

图2

FPGA采集控制部分逻辑原理框图

4.3

DSP中断控制取数部分

数字信号处理是DSP应用的主要方面。DSP所提供的数学运算能力和运算速度远远高于

单片机,具有更为丰富的指令和更大的内存空间,可以实现较为复杂的处理算法。视频信号 经过A/D转换后,形成量化后的数字图像信号,其数据由8位并行接口输出双口RAM,然后 由DSP的中断取数功能在RAM中取数,处理后供主控计算机使用。其工作过程如下:

3.3

DSP核心处理模块 DSP是整个图像处理系统的核心,对采集到的信号进行处理、压缩等过程都由DSP编程

实现。系统由DSP通过芯片上的HPI接口与主机进行通信,接受主机控制命令并向主机传输 采样数据。DSP可对采样所得数据进行实时处理。由于实时性的要求,我们选用,11公司的

DSP处理器TMS320C6202B。 3.4

待下一个HS到来。图2为FPGA采集控制部分逻辑原理框图。

E—

一

舢i

启

#捌

行消臆延时

f6.31Is)

ENAD---DSP发出的AID控制信号 HS--:暖同步信号

cso一组合同步信号—1

AD_CLK—外每时钟信号 AD D限一向DSP发出取敦中断脉冲 ENCA—控喇AD转换信号

l I

ENCA

广

一

■DADL[旺OH]

由于在硬件设计时对实际应用的要求并不能完全了解,设计方案有一定的局限性,因此

・837・

需要使系统具有足够的冗余和灵活性。使用FPGA可以达到这—要求,通过将可能需要的各

种控制和状态信号引入FPGA,利用FPGA的大容量和现场可编程的特性就可根据不同的要求 进行现场修改,增大系统设计的成功率和灵活性。

基于FPGA+SoPC的视频图像处理系统设计

基于FPGA+SoPC的视频图像处理系统设计唐婷婷【摘要】随着信息科技技术的深入研究与应用,在很多行业领域都应用到视频图像。

该文对视频图像处理系统设计分析与研究关键通过SoPC及FPGA两大处理技术。

系统采用视频转换芯片SAA7113完成视频图像采集模块的设计,采用CY7C1049 SRAM完成图像数据的存储,设计VGA显示输出控制关联模块,同时重新修改了显示芯片具体运作形式的配置信息,相结合产生VGA具有控制能力的信号;参考VGA显示器的运行原则,实现了VGA帧一致性信号与接口水平的提升。

%With the further research and application of information technology,video images are applied in many fields. The video image processing system based on two processing technologies of SoPC and FPGA was designed and analyzed. The vid-eo conversion chip SAA7113 was adopted in the design of video image acquisition module. CY7C1049 SRAM was used to com-plete image data storage. VGA display and output control module was designed. The configuration information of the operation mode of the display chip was modified,with which VGA work control signal was generated. According to the industrial standard of VGA display,the improvement of the VGA interface level and frame synchronization signal was realized.【期刊名称】《现代电子技术》【年(卷),期】2014(000)010【总页数】5页(P59-63)【关键词】视频图像;图像处理;FPGA;SoPC【作者】唐婷婷【作者单位】复旦大学附属华东医院,上海 200040【正文语种】中文【中图分类】TN919-34;TP271对视频图像进行处理的过程中,通常图像数据信息具有庞大的运算量与吞吐量,因此需要功能强大的视频图像处理系统。

基于DSP和FPGA的实时视频图像处理系统设计

基于DSP和FPGA的实时视频图像处理系统设计

徐胜

【期刊名称】《自动化信息》

【年(卷),期】2013(000)003

【摘要】随着DSP的不断发展,视频图像处理技术也不断提高并得到了广泛的应用[1】。

其中主要应用之一是对被测物体进行高速实时采集。

由此本文介绍了一种实时视频图像处理系统设计,该系统以TMS320C6455为核心,结合视频解码芯片SAA711IH,与FPGA构成实时图像采集和逻辑控制单元,其中主要利用乒乓缓存操作来实现数据的采集和处理【2】。

作者详细介绍了FPGA的图像采集和逻辑控制部分,DSP数据中断响应处理结果,可以将处理好的数据发送到PC机上做进一步的处理。

该系统在工业领域图像处理方面具有较高的利用价值。

【总页数】3页(P43-44,22)

【作者】徐胜

【作者单位】西南交通大学信息科学与技术学院,四川成都610031

【正文语种】中文

【中图分类】TP391

【相关文献】

1.基于DSP+FPGA的实时视频采集系统设计 [J], 同伟锋;胡方明;杨颖飞;叶一初

2.基于DSP+FPGA线性结构的计算机图像处理系统设计研究 [J], 高菲;贾涛

3.基于DSP的Retinex实时视频图像处理系统设计 [J], 文迪;李武劲;古博;张弛;王

明辉

4.基于DSP+FPGA的实时视频信号处理系统设计 [J], 苏宛新;程灵燕;程飞燕

5.基于DSP的实时视频图像处理系统设计 [J], 江娟娟;汪梅

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第39卷,增刊 V01.39Supplement红外与激光工程Infrared and Laser Engineering2010年05月 Mav.2010基于FPGA和双DSP的高速视频图像处理系统设计苑爱博,鲁新平,李吉成,张志龙,杨卫平(国防科学技术大学电子科学与工程学院ATR重点实验室,湖南长沙410073摘要:介绍了基于XC5VSX95T和两片TMS320C6455的高速实时视频图像处理系统的设计原理.其中Ff,GA模块主要完成图像实时采集和传输的逻辑控制及图像预处理任务,双DSP模块承担特征提取、目标识别、跟踪等任务。

工程应用表明,该系统实时性和稳定性均达到了设计要求,能够实现快速傅里叶变换、边缘检测、识别,跟踪等图像处理算法。

关键词:图像处JE;DSP; FPGA中圈分类号l TP391. 文献标识码:A 文章编号:1007.2276(2010增(信息处理一0647.04Design of high speed video image processor based onFPGA and dual DSPsYUAN Ai—bo,LU Xin—ping,LI Ji—cheng,ZHANG Zhi-long,YANG Wei-ping(KeyLaboratoryforATR.CollegeofElectronic Science andEngineering.NationalUmve 体ityofDefenseTechnology,ChangSha410073,ChinaAbstract:This paper designed a high speed real・time system of video image processing based on two chips of TMS320C6455and Xilinx FPGA of XC5VSX95T.The system uses DSPs to process the image data and accomplishes logic control of data catching and transmission with FPGA.which combines merit such US rapidity,agility and currency.Application of engineering shows that hardware architecture is effective and feasible;the performance meets the requirement of real・time processing.The system can realize the algorithm of image processing such as Fast Fourier Transform(FFT,edge detection, recognizing,tracking and SO on.Key words:Image processing;DSP;FPGA0引言图像处理技术已经被广泛应用于视频图像处理的各个领域,可独立运行的高速实时数字图像处理平台己成为图像处理领域的一个发展趋势。

然而由于图像处理和自动目标识别的算法复杂,运算量巨大,图像处理系统通常包括分割、检测、标记、识别、跟踪等复杂的过程12l,处理实时性要求高,同时系统的体积也有严格的限制,因此在设计系统时必须综合考虑这些特点,合理选用芯片并保留一定的余度。

本文从硬件设计的角度出发研究高速实时图像处理系统。

以双DSP+FPGA的结构组成满足实时性要求的图像处理系统,充分发挥FPGA加通用DSP结构的灵活性及实时处理能力∞1。

1核心芯片的功能和特点主CPU采用TI公司的TMS320C6455定点DSP 芯片。

该芯片采用90am工艺,先进的VelociTlTM VLIW架构,拥有8个独立的功能单元,其中有2个收■日期・2010-04-08作■■介・苑爱博(1985..男.黑龙江卉齐哈尔人,硕士.主要从事图像佰息处理方面的研究。

竺彗兰皇兰耋三垒耋兰兰量兰量量:!童 t6位乘法器和0个算术逻辑单元,其最大峰值速度96410MIPS,最高主颇高达I 2GHz。

它有16Mbit片内集成大容最SRAM.拥有“位高性能外部存储器接口,可与多种同步或异步存储器直接相连,可接八大容量的SDRAM存储器.EMlFA的四个CE空间能接入高逃l G宁节;TMS320C6455拥有2个多通道缓冲串口(MeBSP.最高速率达75MbiUs.64个EDMA通道以及HPI、GPIO等可灵活使用的资源bl。

因此可吼很好地满足图像处理算法的复杂性、实时性承『灵活性要求。

系统使用的是Xilinx公司的Virtex5系列XCSVSX95T,Viaex5系列是H前最新、功能最强大的Flea,Viaex-5系列采用第.代ASMBLTM(高级硅片nl台模块列式架构,除了最先进的高性能逻辑架柑,Viaex.5FFGA还包含多种硬lP系统级模块.包括强大的36Kb Block RAM/FIFO,第二代25x18DSPSlice、带订内置数拧m抗的SelectIOrH技术、ChipSyncTM源同步接口模块、系统监视器功能、带有集成DCM(数字时钟管理器和锁相环(PLL时钟发生器的增强型时钟符理模块以厘高级配置进项19]o Virtex.5SXT为县有高级串行连接功能的高性能信号处理应用的子系列。

XC5VSX95T具有14720个Viaex-5Slice 1每个Viaex.5Slice包含四个LuT和四个触发器.640个dr州I/O管脚,可满足系统逻辑连接要求。

2系统结构和工作原理基于双DSP+FPGA框架的宴时图像处理系统结构如图1所示.该系统由预处理与控制模块、高速处理器模块,视频输出模块、通信模块、电潭模块等部分组成。

各功能模块特点及技术途径如下:囊熹-:一.叠…。

、xc;=;‰t.,㈧.”.。

%i..:… …。

二‰,、目 Fig.1 实时税额雷管赶Ⅱ系统结构框图2.1FPGA噩处理噩控—曩块FPGA芯片是整个目标信息处理机预处理和控制的核心,所有的数据都经过FPGA控制.并且FFGA 还直接承担着图像处理底层的大量的卷积和乘加运算。

所虬该芯片的设计直接决定若整个系统的运算速度。

在FPGA内部构建基于FIFO方式的EMIF接口模式.片使能信号CE和异步输出使能信号AOE用十产,上FIFO的读、写使能信号。

同时,Xilinx Virtex系列FFGA内部塑成BlockRAM.可以配置成两个端12完全独立的真正的双口RAM。

双端口Block RAM的一侧被用来实现与上位机的通信,另一侧用于实现与 FPGA内部逻辑电路与通信”J。

在接个图像处理的过程札前端的红外圈像预处理主要任务是对图像进行滤波提高图像信噪比或进行边界提取和阈值分割。

本设计采用基于Nevafia-Babu算子的方法进行边缘检测”■该方法使用6个5x5的滤渡模块(如图2所小在旷,30。

,60。

.坩,120。

. 150等方向对图像边缘进{r检测。

….一_R_』.。

:_L。

,上,.上。

L —』。

上a【—iI’i.j_i— L—_i_上—i_Li上叭上。

.,L 广山氘k扯可k_山‘-J},一, . .一, L。

1上=:=上i上i上if圈2方彤窗定义肛磋件实现渣程圈R92ql鲥叫c“耐呻^耐Hw0~flowd叫为了使5行5刊共”个像素能够在一个时刻同时输出.便于之后的核心算法模块进行流水线处理, 在5x5方形宙的硬件设计中,文采用了四个FIFO存储器。

其中FIFO地址宽度为WOe为图像宽度,这增刊苑爱博等:基于FPGA和双DSP的高速视频图像处理系统设计 649样每个FIFO正好可以存储一行共W个图像数据,使得5x5方形窗生成模块的输出W11.W55正好构成5x5模板所对应的5行5列共25个图像数据值。

经过寄存器R和FIFO的作用后,在每一个时钟周期时,.1∞ .1∞ O.1∞ .I∞0.1∞ .I∞0.1∞ .1∞0.1∞ .100000l∞ I∞ l∞ 100 00 .1∞ .I∞ .1∞ .1∞l∞ l∞l∞ l∞O O.1∞ .1∞.1∞ .1∞90..1∞ 匏.1∞ .讨.1∞ .I∞.1∞ .I∞.1∞ .I∞5x5窗函数生成模块同时输出WI 1.W55共25个待处理图像的像素数据,构成了5x5方形窗,输出数据与模板进行卷积运算,计算梯度并找}l{最大值,并与预置的阈值进行比较,判断是否为边界像素。

l∞ l∞l∞ l∞l∞ l∞讨l∞.芤l∞.蛇.100l,o.图3Nevatia.Babu算子梯度计算模板Fig.3Templates for detection of image gradients with Nevada-Babu2.2双DSP高速处理器模块高速处理器模块主要是进行图像的高层算法,其任务是对经过预处理的数字图像进行目标检测、识别和跟踪等算法。

DSPI主要承担目标特征提取及目标识别任务,DSP2完成图像跟踪功能。

系统采用两片TI公司的TMS320C6455为核心处理器,最大峰值速率为 19200MIPS,DSPI的64bit EMIFA连接FPGA与两片 FLASH存储器。

用于加载DSP的启动信息、FPGA的初始化配置和预加载基准图。

DSP通过EMIF接口总线连接到FPGA,EMIFA口的数据线、地址线、片选信号等与FPGA 的I/O连接。

将FPGA内部存储器映射到 DSP地址空间。

实现高速数据交换13J。

两片C6455之间通过全双工串行多通道缓冲串口McBSP进行控制信号的传送,通过两片C6455的EMIFA口连接至FPGA的 EMIF总线接口,可达到800MB/s的数据传输速率。

2.3视频输出模块该模块的功能是将DSP处理后的图像数据进行数模转换,并与字符信号合成后形成VGA格式的视频信号。

这里选用的数模转换芯片为ADV7123JSTl40。

这是ADI公司生产的一款三通道(每通道10位视频数模转换器,其最大数据吐率330MSPS,输}}{信号兼容 RS.343觚S.170。

由FPGA接收待显示的图像数据, 放入存储容量为128K*18的双端口显示帧缓存 (IDT70V631S中,RGA中的显示图像逻辑电路以基准频率产生复合同步、复合消隐信号。

由FPGA产生的数字视频信号分别进入到ADV7123的三个数据通道,经数模转换后输flj模拟视频信号并与原来的同步信号、消隐信号叠加后便可以在显示器上显示处理后的结果。

2.4串行通信模块模块要求实现2个422串口:传输速率为115.2Kbps、230.4Kbps。