《ITEEC架构介绍》

笔记本电脑系统架构

笔记本电脑系统架构熟悉典型主机系统架构图当前笔记本电脑虽然品牌众多,且产品外观、功能特色各有千秋。

但是除了苹果公司(Apple)部分机型外,它们的基本系统架构和原理还是一样的,都是基于IBM PC/AT的架构。

此外,值得一提的是,虽然桌面电脑和笔记本电脑外形差别很大,但其基本的系统架构和原理还是一样的,也是兼容于IBM PC/AT架构的。

我们在第一章内容里已经给读者朋友介绍了桌面与笔记本电脑的一些主要的特性差别芯片组(Chipset)是电脑主板系统架构的核心组成部分,如果说中央处理器(CPU)是整个电脑系统的大脑,那么芯片组将是整个身体的躯干。

芯片组作为直接和CPU打交道的部件,是发挥CPU性能的基础平台。

在电脑界通常称设计芯片组的厂家为Core Logic,Core的中文意思就是核心,单从字面上就足以看出芯片组在电脑主机中的分量。

对于电脑主板而言,芯片组性能的优劣,决定了主板性能的好坏与级别的高低,进而也影响到整个电脑系统性能的发挥。

提到全球个人电脑CPU及主板芯片组制造商,就不得不提到大名鼎鼎的Intel公司,其自个人电脑诞生以来,一直以领头羊的身份带领着PC技术的向前发展。

Intel每一款芯片组产品的推出,都影响着全球千千万万电脑使用者对电脑产品的性能和感官体验。

不过话也说回来,当今的AMD公司自从率先推出双核消费型CPU及并购著名显卡芯片商ATI后,其在PC集成芯片领域也占据一方,这是也普通电脑消费者所乐见的。

只有竞争的越激烈,我们才能用上性能更好、价格更便宜的电脑产品。

因为Intel公司的处理器、芯片组同出系门,在采用整套Intel芯片产品应用方案电脑机型上,也因此具有更好的兼容性与稳定性,几乎不存在配合上的问题。

电脑主板硬件开发工程师。

通常只需要严格地按照芯片规格书(Data Sheet)的定义去做相应的信号连接即可,从而大大降低了产品的研发周期与风险。

本章主要内容也将是基于Intel芯片组系统架构的机型为例,为读者朋友分不同层次、方面的内容逐一展开讲解。

ITE 智慧控制SoC介绍 2016_Jul 简体中文

电饭锅 洗衣机 微波炉

床头音响

咖啡机 门禁管理机 IT9852 SoC’s SDK Platform

洗碗机

按摩椅控制器 跑步机 21

冰箱

ITE (联阳半导体)

智慧控制 SoC 开发工具

22

ITE 智慧控制 SoC 之 SDK,HDK 内容

功能完善 容易上手 开发快速 Source code完整开放 客人技术完全掌握

8

ITE 智慧控制 SoC : 当主控系统

I2S

IR Receiver

SDIO

GPIO RMII UART x4 Wiegand

PHY

SPI

NOR NAND

24bit RGB /CPU

I2C for touch sensor PWM to Backlight

10/100 Ethernet USB

Mirco SD

Source Code Documents

Tools

Hardware Sets

ITE Embedded SDKs

23

ITE 智慧控制 SoC: S/W SDK 特色

整合 开发Tools

GUI 开发Tools

ITE Embedded SDK

平台化架构 平台化 项目管理

24

ITE 智慧控制 SoC: 图形控制开发工具

28

ITE 智慧控制 SoC: 完整设计数据

29

ITE Tech. Inc.

7F, No. 233-1, Baociao Rd., Sindian, Taipei 23145, Taiwan Tel: +886-2-2912-6889 Fax: +886-2-8914-5970 Mail: ITEsupport@

深信服分享PPT:超融合IT新架构

计算虚拟化

软件必须与硬件结合

资源利用率低、灵活 性受限于物理硬件

将软件和硬件解耦合

逻辑抽象出硬件资 源、可灵活调配

服务器虚拟化

优势

高 可靠性保障

高 灵活调度

高 高 资源利用 扩展性

问题

虚拟机的移动性 业务的部署限制

传统网络功能硬件

网络虚拟化 网络功能虚拟化

借鉴虚拟化的思路

网络虚拟化+NFV

构 超融合

架构层

aNET

aSV

aSAN

网络虚拟化

服务器虚拟化

存储虚拟化

云资源调度

基础 架构

通用X86服务器

通用交换机

深信服一体机

云运维管理

3 深信服超融合架构带来的价值

深信服计算虚拟化-aSV概述

虚拟机 虚拟化内核 虚拟化管理

物理服务器 FC/IP交换机

aSV(Hypervisor)

aCenter虚拟化管理平台(分布式)

4 深信服超融合计算虚拟化-aSV

深信服计算虚拟化-aSV概述

虚拟机 虚拟化内核 虚拟化管理

物理服务器 FC/IP交换机

aSV(Hypervisor)

aCenter虚拟化管理平台(分布式)

物理存储

aSV的特色技术-虚拟机HA高可用

财务

ERP

邮件

OS

OS

OS

邮件

ERP

网站

OS

OS

OS

aSV(Hypervisor)

公公司司概概况况

持续创新

第一台 创 新

全球 第1台 二合一VPN 中国 第1台 上网行为管理 中国 第1台 下一代防火墙

发明专利﹥380项

ITEEC架构介绍

ITEEC架构介绍ITE EC(Integrated Test Environment-Electric Controls)是一种集成的测试环境和电气控制技术架构,广泛应用于制造业中的自动化测试系统。

ITE EC架构的设计目标是通过集成不同测试设备和控制系统,提高测试效率、质量和灵活性。

ITEEC架构的核心理念是将测试设备、测试控制系统和测试数据管理系统集成到统一的平台上,通过统一的接口和协议实现它们之间的通信和协作。

这样做的好处是能够将不同设备的功能进行整合,提高测试的自动化程度,并减少人工操作的错误和干预。

ITEEC架构的关键组成部分包括测试设备、测试控制系统、测试数据管理系统和通信协议。

测试设备是进行实际测试的硬件设备,如传感器、执行器、控制器等。

测试控制系统是控制和管理测试设备的软件系统,通过与设备的通信接口实现对设备的控制和数据采集。

测试数据管理系统是用于管理测试过程中产生的数据,包括数据存储、分析和报告生成等功能。

通信协议则定义了设备和系统之间的通信方式和数据格式。

在ITE EC架构中,各个组成部分之间的通信是通过标准化的通信协议实现的,如CAN、Ethernet、RS-232等。

这样的设计可以保证不同设备和系统之间的互操作性,使得IT环境中的设备能够灵活地组合和替换,提高系统的可维护性和升级性。

另一个重要的特点是ITEEC架构支持分布式部署,即可以将测试设备和控制系统分布在不同的位置,通过网络连接进行远程控制和数据采集。

这样的设计使得测试系统的部署和维护更加灵活和便捷,并且能够适应不同规模和复杂度的生产环境需求。

在实施ITEEC架构时,需要考虑到系统的安全性和可靠性。

为此,需要采取一系列的安全措施,如访问控制、数据加密、故障检测和容错机制等,以保证系统的稳定运行和数据的安全性。

总之,ITEEC架构是一种集成的测试环境和电气控制技术架构,通过集成不同测试设备和控制系统,提高测试效率、质量和灵活性。

物联网各种主控芯片架构简介

物联网五种主控芯片架构简介人工智能芯片中兴事件引起了全球的轰动,大家的目光聚集在服务器、计算机、存储底层芯片技术缺乏之上。

紫光等国产芯片供应商股票应声上涨。

此次事件反应出了我国在芯片及其产业链上较为薄弱;毕竟PC时代,我们起步时间太晚。

不过在随即到来的物联网(芯片)时代,我们还是有希望实现弯道超车的。

物联网芯片作为万物互联的重要部分之一,包含安全芯片、移动支付芯片、通讯射频芯片和身份识别类芯片等芯片产业,预计2020年我国物联网规模将达1.5万亿。

接下来就随着蓝牙模块厂家云里物里一起来看下物联网主控芯片的几种架构。

国内外巨头纷纷布局物联网芯片物联网光明的市场前景和尚未定型的IoT主控芯片架构市场,引得国内外巨头纷纷发力,抢占制高点。

国外方面,英特尔早在2014年便发布基于x86的名为爱迪生(Edison)芯片,紧接着2015年推出基于x86的居里(Curie)芯片;高通自然也不甘停滞于移动领域,于2016年首发基于自己Krait300架构骁龙600E和410E物联网芯片,Krait300架构是基于ARM V7指令集的,性能介于ARM设计的A9、A15架构之间;三星也于2015年便发布Artik1、5、10三款物联网芯片,均基于ARM架构。

此外,谷歌、AMD、英伟达等巨头也纷纷研发物联网芯片。

国内市场,联发科在2015年便推出基于ARM v7架构物联网芯片MT2503,已广泛用于共享单车领域,并于今年与微软达成协议,合作推出首款AzureSphere芯片MT3620;华为海思于2016年9月推出首款正式商用物联网芯片,其Boudica120、150芯片也于2017年下半年大规模出货,均基于ARM架构;此外,中芯国际、华虹宏力、台积电、展讯、华润微、联芯科技等厂商也纷纷布局物联网芯片市场。

物联网芯片架构万物互联的前提是智能终端设备与传感器的连接,其应用场景和特性使得物联网芯片偏向低功耗和高整合度,低功耗使得开发人员能够为功耗受限设备增添功能,同时保持芯片尺寸,扩大应用可能性。

英特尔架构日和HotChip技术信息解读(下)

英特尔架构日和HotChip技术信息解读(下)作者:***来源:《微型计算机》2020年第19期CPU:Tiger Lake面世TigerLake是英特爾转入10nm后最重要的产品,它使用的是10nmSuperFin制程工艺,无论是频率还是性能表现都足以令人满意。

在架构方面,TigerLake使用的WillowCoveCPU架构和XeGPU架构都进行了大幅度改进,带来了革命性的技术和效能表现。

英特尔认为TigerLake拥有六大方面的优势:CPU部分,TigerLake换用了全新的WillowCove架构,拥有比前代产品更出色的性能;GPU部分,由于全新Xe架构的引入,TigerLake带来了“颠覆性”的集成图形核心性能;AI方面,TigerLake继承了全新的高斯网络加速器GNA2.0;集群方面,增强的内存性能和互联带宽带来了出色的集群性能;能耗比方面,借助于新的工艺和架构,英特尔宣称TigerLake拥有同等规模SoC芯片中最佳的表现;安全性能方面则是一贯地拥有英特尔整套安全技术支持。

除此之外,TigerLake还带来其他的一些重要功能,比如首次支持PCIe4.0、首次支持LPDDR5、首次支持USB4、Thunderbolt4、集成4个显示通道,支持4K/60fps10bit、8K/30fps10bit视频输出等功能。

频率逼近5GHz,架构升级和之前设计IceLake时一样,英特尔在TigerLake的设计上也面临两种选择,一种是更好的单线程性能或者IPC性能,另一种是更好的能效比。

在TigerLake上,英特尔选择了后者,这意味着TigerLake在任何给定的功率和电压下,相比前代产品频率更高;在任何给定的频率下,相比前代产品功耗更低或者电压更低。

在之前泄露的一些消息中,采用了10nmSuperFin 工艺的TigerLake处理器频率甚至能飙升至4.8GHz以上,着实令人惊讶。

在CPU核心架构方面,TigerLake引入全新的WillowCove核心架构设计。

IntelNehalem架构简析ICT技术

IntelNehalem架构简析ICT技术在最近举行的IDF大会(Intel Intel Developer Forum)上,Intel公布了下一代处理器架构Nehalem的不少技术细节。

Intel计划在明年第三季度下旬到第四季度上旬正式推出基于Nehalem架构的处理器,包括采用Beckton CPU的Stoutland多处理器平台、采用Gainestown CPU的Thurley双处理器平台、采用Bloomfield CPU 的Thurley单路处理器平台、采用Havendale/Lynfield CPU的Fowhollow单处理器平台。

图1:Intel推出Nhalem架构的时间表Gainestown/Bloomfield是四核处理器,共享8MB的L2 Cache,集成的内存控制器拥有3条DDR3 800/1066/1333通道,都是用LGA 1366插座。

即将推出的Penryn会采用SSE4.1指令集,而Gainestown/Bloomfield采用扩展后的SSE4.2指令集。

在设计热功耗(TDP)方面,Gainestown按频率高低分为130W/80W/60W三档,而Bloomfield分为130W/80W两档。

TDP的再度升高说明45nm制程到Nhalem架构将接近极限,此后Intel会将工艺提升到32nm。

图2:Intel扩展指令集的发展沿革Nhalem架构最大的改造在前端总线(FSB)上,传统的并行传输方式被彻底废弃,转而采用基于PCI Express串行点对点传输技术的通用系统接口(CSI),被Intel称为QuickPath。

QuickPath的传输速率为***Gbps,这样一条32bit的QuickPath带宽就能达到25.6GB/sec。

QuickPath的传输速率是FSB 1333MHz的5倍,前者虽然数据位宽较窄,但传输带宽仍然是后者的2.5倍。

由于分别用于双处理器和单处理平台,Gainestown有两条QuickPath,而Bloomfield仅有一条。

XilinxUltraScale架构-业界首款ASIC级AllProgrammable架构

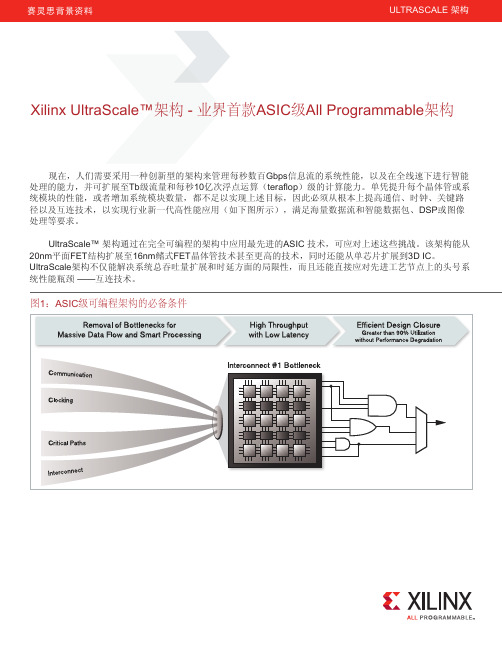

赛灵思背景资料ULTRASCALE 架构Xilinx UltraScale™架构 - 业界首款ASIC级All Programmable架构现在,人们需要采用一种创新型的架构来管理每秒数百Gbps信息流的系统性能,以及在全线速下进行智能处理的能力,并可扩展至Tb级流量和每秒10亿次浮点运算(teraflop)级的计算能力。

单凭提升每个晶体管或系统模块的性能,或者增加系统模块数量,都不足以实现上述目标,因此必须从根本上提高通信、时钟、关键路径以及互连技术,以实现行业新一代高性能应用(如下图所示),满足海量数据流和智能数据包、DSP或图像处理等要求。

UltraScale™ 架构通过在完全可编程的架构中应用最先进的ASIC 技术,可应对上述这些挑战。

该架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同时还能从单芯片扩展到3D IC。

UltraScale架构不仅能解决系统总吞吐量扩展和时延方面的局限性,而且还能直接应对先进工艺节点上的头号系统性能瓶颈 ——互连技术。

图1:ASIC级可编程架构的必备条件• Monolithic to 3D IC • Planar to FinFET • ASIC-class performance图2 :新一代高性能目标应用实图中,高速数据流(Tbps 级的汇聚速率)从左侧进入再从右侧流出。

可通过运行速度为数Gbps 的高速SerDes 收发器进行I/O 传输。

一旦以数Gbps 速度传输的串行数据流进入芯片,就必须扇出(fan out ),以便与片上资源的数据流、路由和处理能力相匹配。

新一代系统要求使用极高的数据速率,因此时钟歪斜、大量总线布置以及系统功耗管理方面的挑战会达到令人生畏的程度。

图3:为您量身定做的新一代架构UltraScale™架构具有无与伦比的高集成度、高容量和ASIC 级系统性能,可满足最严苛应用的要求。

UltraScale 架构经过精调可提供大规模布线能力并且与Vivado ®设计工具进行了协同优化,因此该架构的利用率达到了空前的高水平(超过90%),而且不会降低性能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Default:

» 0x65 – PS/2 Mouse Not Present » 0x47 – PS/2 Mouse Present

ITE 8512

Speaker: WY

整理课件

1

What’s the EC ?

Embedded Controller comes form ACPI structure

Host is communicated EC by LPC interface. The I/O port are 60/64 and 62/66

7

BIOS&EC Code Position

整理课件

8

Features

IBM AT & PS/2 8042-Compitable Host Interfaces

Support all standard Host Commands

ACPI Embedded Controller Interface ACPI System Management Bus Interface PS/2 Devices Scan Matrix Keyboard OEM Customization

Bit

Description

7

Parity Error

6

Timeout Error

5

Auxiliary Output Buffer Full

4

Inhibit Switch

3

Command/Data

2

System Flag

1

Input Buffer Full ( IBF )

0

Output Buffer Full (OBF)

整理课件

12

Features – Standard KBC Commands

Standard 64 command list Write / Read Keyboard Controller Command Byte

(60h / 20h)

The KCCB resides in 8042 RAM location 20h, Address 20h defined in the IBM 8042 programming specification.

EC integrated ps2 device, keyboard matrix, battery charger, fan control, power sequence, hot key function, backlight, CPU thermal sensor, system power consumption,etc.

Scan Matrix Keyboard

18 Scan Out (Column) 8 Scan In (Row)

Scan

HIF

ITE KBC

I2C

SMBus

PS/2

3 PS/2 Devices

3 S整M理B课u件s Devices

4

EC Feature

ITE EC

PS/2 KB/MS

MATRIX

ACPI

BIOS EEPROM

整理课件

6

Share BIOS Architecture

Max : 16M

64K~16M Byte

BIOS ROM Zone

KBC ROM Zone 64K Byte

64K KBC ROM Zone

0

Full space 16M Byte

Max :16M-64K Byte

整理课件

❖ Controller Command Byte:

▪ Bit[7] - Reserved ▪ Bit[6] - Keyboard Translate ▪ Bit[5] - Disable Auxiliary Device ▪ Bit[4] - Disable Keyboard ▪ Bit[3] - Reserved ▪ Bit[2] - System Flag ▪ Bit[1] - Enable Auxiliary Interrupt ▪ Bit[0] - Enable Keyboard Interrupt

整理课件

9

Features – Host Interface

Host Interfaces

Primary Host Interface (0x60, 0x64)

▪ HIF1 – 8042 Command Interface

Secondary Host Interface (0x62, 0x66)

▪ HIF2 – Logical HIF – ACPI Command Interface ▪ HIF3 – Logical HIF – SMI Access

Third Host Interface (0x68,0x6C)

IBM AT & PS/2 8042-Compatible

Standard KBC Commands – 0x64 port Standard KBD Commands - 0x60 port Standard AUX Commands – 0x64 port D4 command

Power management

SMBus

UART / CIR

ADC/DAC

PWM

Share BIOS

KBS Monitor

整理课件

5

EC Position

South Bridge

LPC BUS Power Management

IT8510E Or

IT8512/IT8513

IT8510E -> ISA Bus IT8512/8513 -> SPI Bus

整理课件

2

System Structure

NB

LPC

SB

EC

PS/2 KB/MS MATRIX FAN Control Charger

Flash ROM Power

Sequence….

整理课件

3

Keyboard Controller Overview

Host System

LPC/Firmware Hub

整理课件

10

Command Handler

Command handler 60/64

Is system command?

YES

Is D4 comand

NO

KBD Command

YES

Mouse Command

整理课件

11

Keyboard Controller Status Register 64h