nc后仿

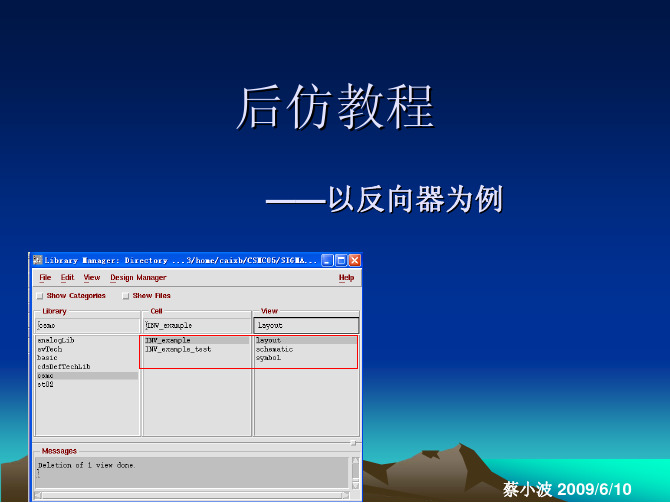

cadence后仿教程

默认第一项是 spectre,意味着 INV_example_tes t里调用的是 INV_example的 schmatic view来 进行仿真

如要进行后仿我们得 修改Switch View List, 把calibre加在spectre 前面,意味着仿真的时 候INV_example_test 调用INV_example的 calibre view来进行仿 真,这就是后仿!!!

<3>指定提取哪些节点的寄生参数: 默认是ALL Nets(提取所有节点) 也可以自定义(Specified Nets):可以提取除了指

定节点以外的所有节点(Exclude),也可以只提取指定的 节点(Include),在相应的文本框里写入节点的net名即 可,或者点击右侧的小箭头,然后在弹出的原理图里选择你 想输入的节点,按ESC键,你所选择的节点名就自动填在左 侧文本框中.

至此,我们仍未进行后仿,我们只是提取出 了寄生参数,并生成了带这些寄生参数的 calibre view,这都是为后仿做准备. 接下来介绍如何后仿.

方法一

1.打开测试平台,此 例是 INV_example_test. 2.打开ADE (仿真环 境)窗口 3.与仿真原理图不 同的是多出这一步: 点击Setup— >Environment 弹出一个配置窗口 (见下页)

6.Run PEX

弹出两个框:一个 是Calibre View配 置对话框(左 图),一个是寄生 参数文本(见下 页). 注意左边两个设 置,其他默认即 可.

6.Run PEX

第一次运行PEX会弹 出映射文件向导, 引导大家生成 MAP文件. 以后就不用设置了. 除了寄生电阻寄生电 容以外,所有器件 都用st02中的模型 来映射.

NC仿古油漆工艺流程

NC仿古油漆工艺流程一.白身的破坏处理白身的破坏处理工艺中一般有:敲打碰撞痕迹,挫刀痕,戳刀痕,蚯蚓痕,磨损痕,虫蛀痕,污染痕等等。

跟据产品或客户的要求做不同的破坏效果。

使其达到给人以久用后破旧的感觉。

要求破坏的程度要合理,协调,有一定的随意性。

(此工绪前必须将所有的钉孔和缺陷修补良好,不可遗留到后面的工绪)二.素修在白身本身木材存在色差的时候,我们人为的跟据产品面色来调配合适的修色使其基本达到一致。

便于后面的工绪顺利进行。

有的需要修红、有的需要修绿。

三.底色跟据产品面色和效果来定位底色的道数。

一般最多不会多过三道底色。

每道底色的颜色不能一样,这样做出来才会有层次感。

对于面色闪色的产品我们需要在底色里加上适量的珍珠粉。

喷手在喷底色的过程中一定要均匀喷湿,一定不能有流色的现象。

做到全面,不能有露白或喷不到位的现象。

每一道底色一定要严格参照分段色板。

第一道底色喷后稍待干后再喷第二道底色,不能有开花的现象。

四.第一道底漆此道底漆要求其浓度不能太高,一般在13秒到15秒为宜。

特别情况下做特别调整。

喷漆过程中要全面均匀喷湿即可。

对于端头或个别砂光不良的部位可适量加喷。

五.砂光第一道底漆完全待干后,用240#砂纸进行全面砂光。

砂光过程中切忌不能将底色砂穿,顺木纹进行。

基本光滑就好。

六.擦仿古漆(仿古漆)将调配好的仿古漆用毛刷刷于产品整个表面,所有的沟槽和雕花部位不可有露白再象。

然后用杂碎布擦试干净,表面只留取少许仿古漆即可。

再用毛刷排顺均匀,不要有毛刷印。

然后用纲丝绒拉出明暗效果,在做明暗效果的时候要做的协调,随意。

不要做的太有规则。

注意发黑的部位用纲丝绒清理干净。

完成后检查是否有露白的现象。

注意破坏处理的地方要做到格丽斯,不可露白。

七.第一道底漆针对做全封闭的产品一般要求底漆浓度在18秒左右,均匀喷湿于产品所有表面。

不要流油,喷涂到位,产品的主要正面需适量加喷。

针对于做开放和半开放的产品而言,底漆浓度要求在13秒到15秒为适宜,均匀喷湿产品表面一遍即可。

数字IC设计工具介绍

COMPOSER - CADENCE 逻辑图输入这个工具主要针对中小规模的ASIC以及MCU电路的逻辑设计,大的东西可能需要综合了。

虽然现在电路越设计越大,有人言必称SYNOPSYS,但只要仔细到市场上端详一下,其实相当大部分真正火暴卖钱的东西还是用CADENCE的COMPOSER加VIRTUOSO加VERILOG—XL加DRACULA流程做的。

原因很简单,客户可不买你什么流程的帐,什么便宜性能又好就买什么。

备用PC上的工具:WORKVIEW OFFICEDC - SYNOPSYS 逻辑综合这个不用说了,最经典的。

但老实说在我们现在的设计流程里用得还不多,最关键问题还是一个市场切入问题。

备用工作站上的工具:AMBIT,这个工具其实很不错,它和SE都是CADENCE出的,联合起来用的优势就很明显了。

PC上用的备用工具可以选NT版的SYNOPSYS,SYNPILIFY也不错,但主要是用做FPGA综合的。

其实最终你拿到的库有时最能说明问题,它不支持某工具,转换?急吧。

VIRTUOSO - CADENCE 版图设计这个大家比较熟了,但个人还是喜欢用PC上的TANNER。

原因是层与层之间的覆盖关系用调色的模式显示出来比直接覆盖显示就是舒服。

可惜人家老大,国产的《熊猫》也学了这个模式。

倒是以前有个COMPASS,比较好用,可惜现在不知哪去了。

SE - CADENCE 自动布局布线有了它,很多手工版图的活儿就可以不用做的,实在是一大进步。

可惜残酷市场上如果规模不大的东西人家手画的东西比你自动布的小40%,麻烦就大了。

APOLLO用的人还不是很多吧。

PC上的TANNER 据说也能做,针对线宽比较粗,规模不太大的设计。

VERILOG—XL - CADENCE 逻辑仿真VERILOG就是CADENCE的发明,我们的版本比较老,现在该工具是不是停止开发了?CADENCE 新推都叫NC-VERILOG。

SYNOPSYS的VCS是不是比NC强,反正两公司喊的挺凶,哪位对这个两个东西都比较了解,不妨对比一下。

四轴加工实例讲义

四轴加工实例教程讲义讲授教师:_____ __2011年月日一、加工任务概述利用图1-1 所示的“福”字图片,通过Mastercam 的四轴加工功能得到笔筒造型。

具体步骤如下:1)把图片中的“福”字转化成Mastercam 可读入的Autodesk 格式,或利用Mastercam9.1 自带的功能,直接可以把图片格式转换成线条。

2)经过编辑后,得到我们加工笔筒所需要的线条图形,再把图形缠绕在直径为95mm 的圆筒上3)通过Mastercam 的四轴加工功能得到笔筒造型。

图1-1 未编辑前的福字为图片格式经过图片转换,再加上修饰花边,加工后即为如图1-2 效果。

图1-2 经过图片转换经过图片转换、、修饰后的加工效果二、工艺方案笔筒的加工工艺方案如表所示。

1)工艺设计笔筒的加工工艺方案笔筒毛坯如图1-3 所示,材质为铝镁合金5050。

在实际加工中,毛坯已没有夹持余量,不可能再用三爪夹持笔筒外圆的方法加工,但可设计一阶梯芯轴,用三爪夹持心轴,找正后,把笔筒套入芯轴,并用顶尖顶牢,由于实际加工过程中,切削力很小,笔筒内孔与芯轴之间为精密配合,顶尖顶牢后,预紧力完全满足加工切削力的要求。

装夹方案设计如图1-4 所示。

图1-3 笔筒毛坯半剖视图图1-4 笔筒加工示意图2)芯轴设计经测量,笔筒的内孔直径为φ80.01mm,故芯轴直径选用φ80h5 (0+0.015),最小间隙为0.01mm,最大间隙为0.025mm,可以满足装配加工要求。

芯轴设计方案如图1-5 所示。

图1-5 芯轴设计图形三、加工模型准备1)图片转换 Mastercam9.1 版本能针对图片加工,且开发了图片直接转换成线条的程序,具体操作方法如下:步骤 1 选择需要的图片:单击“MAIN MENE”→“File”→“Converters”→“Next menu”→“Rast2vec”,选择要选的图片“福字”,如图1-6 所示。

图1-6 利用Mastercam9.1 图片加工功能选择图片步骤 2 把原图形转换为黑白图形:单击“Linear Black/White conversion”→拖动调节按钮,改变图形颜色→单击“OK”按钮,如图1-7 所示。

使用Mentor公司PCB设计工具经验

Mentor公司PCB设计工具(DxDesigner及Expedition PCB)的设计体会Expedition的设计思想大部分硬件工程师,PCB设计使用最多的恐怕就是protel,因此在使用Expedition做PCB设计时不自觉的就会把两者设计思想进行比较,从本质上来讲,两者并无什么不同,都是符号,封装,互连关系,但是在具体形式上,Expedition比起Protel要更为细致。

Protel在设计时只需要两个库:符号库及封装库,原理图设计时在元件的属性中进行两者的对应,然后生成网表文件,就可以带入到PCB中进行布局布线,如图1所示。

与此不同,Expedition中引入了中心库(Central library)的概念,符号(Symbol)与封装(Cell)的对应是在中心库中完成,形成器件(Part)。

可以说,中心库是整个设计的基础,从焊盘定义,封装制作、符号与封装的对应,都在中心库中完成。

在进行原理图设计时,可以从中心库中调符号,当然也可以自己建立本地符号库,但是在进行编译之前,要用中心库中的符号代替自己建立的符号,并在符号的属性中指定与中心库中Part的对应关系,同时指定中心库路径,这样才可以完成编译,进入下一步PCB的流程(图2)。

前端输入工具DxDesigner我购置的Mentor软件的前端管理工具是DxDesigner。

由于我们手中没有现成的中心库可用,时间又比较紧张,在设计之初,我们采用的是两个人分头进行的设计方法:一个人负责建立符号库及原理图设计,另一个人则负责作封装库,到基本完成后再整合在一起。

原理图设计工具是viewdraw,在viewdraw的环境中也可以编辑制作符号,符号(symbol)创建有导航,在编辑时比较方便,也可以用VHDL或Verilog语言作为输入源,由于现在器件公司网站上一般都会提供语言的描述,所以有时候会比较快,但是用这种方式做出来的符号往往管脚排列不规则,需要改动,有时并不比手动输入时方便多少;元器件的属性种类比较丰富,但常用的基本属性就几个,只要填写正确一般也不会出大问题;他的路径设定比较麻烦,若想把在别的机器上的设计拷过来,必须先进行归档(Archive)操作,把库、设计数据进行打包,这样的工程才能在新的机器上打开;原理图编辑功能也都大同小异,总的感觉,它的原理图输入工具没什么优势可言,输入的方便性及直观性都比较一般。

NC-verilog 仿真教程和实验实例

Cadence IC设计实验实验六 NC-Verilog Simulator实验实验目的:NC_verilog仿真器的使用,包括编译、运行和仿真。

预备工作:cp /eva01/cdsmgr/ training_IC_data/NCVlog_5_0.tarZ .tar -vxfZ NCVlog_5_0.tarZLab1。

运行一个简单的Verilog设计[1]、设置设计环境1.cd NCVlog_5_0/lab1-mux这个目录包含了用来描述一个多路选择器和其测试平台的verilog 模块。

以下是mux_test.v模块内功能模块的端口框图。

建议:如果有时间,你最好看一看各模块(module)的Verilog代码!2.创建cds.lib文件,vi cds.lib(回车)按小写”i”切换到编辑模式,在其中写入:Define lab1muxlib ./lab1-mux.lib有关vi的编辑命令,请参阅相关资料。

如”Esc”键切换到命令状态,在命令状态下,”x”是删除当前字符,”a”是在当前光标后写入,”:wq”是存盘退出,”:!q”是不保存退出。

存盘退出3.创建(库)文件夹(即目录):mkdir lab1-mux.lib (回车)4.类似步骤1,创建hdl.var文件,在其中写入:Define WORK lab1muxlib存盘退出5.查看verilog源文件。

mux.v是2选1多路选择器MUX2_1 的门级建模源文件,mux_test.v是mux.v的测试台,包含了输入激励信号和监控程序运行的任务语句。

[2]、编译源文件(ncvlog命令):当前目录应为。

/你的学号/NCVlog_5_0/lab1-mux。

1.ncvlog mux.v –messages ,这条指令是编译mux.v。

2.vi hdl.var打开hdl.var文件,在其中添加:Define NCVLOGOPTS –messages 存盘退出注:用NCVLOGOPTS变量定义常用的ncvlog命令行操作,从而避免每次都敲入同样的命令行。

nc后仿_综合后仿真

选择Annotation一项, 在子菜单中选中除第一 项的所有条目。 在delay types中选择 Maximum一项,SDF 文件中对每项延时都有 最大值,典型值,最小 值,这里选择最大值用 于仿真

在上述步骤之后,会生成一个你的设计对应的snapshot,仿真 就是针对这个Snapshot进行的。如图示,选中该文件,点击 仿真按钮

点击

进入nc_postsim文件夹

双击spi_test1,打开并加入反标命令, 退出时记得保存:File->save

准备工作介绍

在仿真已有的设计以前,必须编译和描述它。编译 过程将把源文件中的用HDL编写的单元编译成内在 的描述。描述设计将在设计的实例化,结构化信息 的基础上建立设计的层次结构,建立信号的连接, 计算所有对象的初始值。编译,描述和仿真自己的 设计要用到以下的工具: Ncvlog: 编译Verilog源文件。 ncelab 描述设计并且生成仿真的snapshot。 ncsim 对snapshot进行仿真仿真。

NC-Verilog

综合后仿真

后仿概述

后仿是在前仿的基础上加入延时信息的功能 仿真。 同时验证了设计的时序以及功能都正确,并 且确保后仿功能和前仿一致。

实验任务

掌握前仿与后仿的区别 学会用NC-verilog对设计进行后仿 在SimVision分析环境下对设计中的问题进 行调试

前仿与后仿的区别

SPI_test1为测试模块 名,ex1为例化名

将ex1,ex2,ex3全部 应用sdf文件

仿真并得到器件延时信息

谢谢!

仿真所需文件

netlist.v:DC综合生成的网表文件 .sdf:DC综合生成的标准延时文件 ,这个文 件中包含了设计的网表中单元和连线的延时 信息。 smic25.v工艺库仿真文件,包含综合目标库 中元件的仿真模型信息

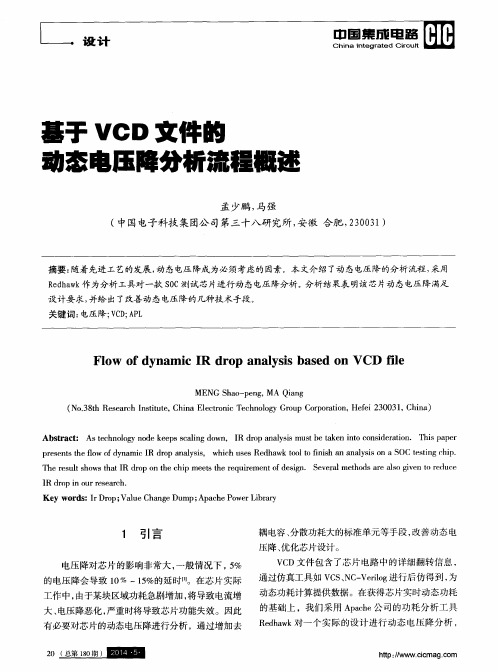

基于VCD文件的动态电压降分析流程概述

R e d h a w k 对一个实际的设计进行动态 电压降分析 ,

h¨^ . I h…

Ⅲ

, 、 ;

^

, 、Байду номын сангаас^

【 l 】 国 集 成 电 路

C hi na I nt eg r at ed Ci r cui t

Ab s t r a c t : As t e c h n o l o y g n o d e k e e p s s c a l i n g d o wn , I R d r o p a n a l y s i s mu s t b e t a k e n i n t o c o n s i d e r a t i o n .T h i s p a p e r

pr e s e nt s t h e lo f w o f dy n a mi c I R d r o p a n a l y s i s , whi c h i r s e s Re dh a wk t o o l t o f i n i s h a n a n a l y s i s o n a SOC t e s t i n g c h i p.

T h e r e s u l t s h o ws t h a t I R d r o p o n t h e c h i p me e t s t h e r e q u i r e me n t o f d e s i g n .S e v e r a l me t h o d s a r e a l s o g i v e n t o r e d u c e

并 给 出分析 结 果 。

2 分 析 流 程

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以波形的形式研究仿真的资料

在ex1模块中选择要 显示在波形窗口中的 信号。选中后点击 waveform按钮 这样就可以打开波形 窗口了。

有波形显示的波形显示窗口

后仿最大的特点就是信号翻转加入了延时信息,比如 信号spi0cn,放大波形可以看到信号相对时钟有效 边沿的延迟。

下拉波形,可以发现信 号sck_neg_dtc[0]、 nss_neg_dtc[0]为高阻 z态,这是因为综合过程 中dc可能会在优化过程 中优化掉信号,或对信 号改名,这个问题需要 在网表中解决。 打开nc_postsim文件夹 中的网表文件: spi_interface.mapped. v 按ctrl+f键,寻找信号 sck_neg_dtc[0]发现网 表中没有该信号:

但是在这之前要设置 参数,选中module后 选择toolsElaborator 进行设置。

设置参数时注意将Access Visibility按 钮选中并且它的值是All,这个选项意味 着全部存取(读,写,连接探测)来仿 真目标,这样就可以在仿真的数据库里 面探测目标和范围,调试你的设计。 由于不是所有的代码都加了时间,为防 止报错在此处加上时间。 然后点击ok即可。 与前仿不同的是,现在还要进行针 对反标延时的设置,点击选项 Advanced Options

选择creat cds.lib file,弹出第二个对 话框,save,在新对话框中点击ok, 之后在最初的对话框中点击Ok。

nclaunch的主窗口: 左边的窗口中显示了 当前目录下的所有文 件,在编译和描述后 会在右边显示设计的 库。

在在仿真你的设计以前,必须用编译器编译源文件,并且 用描述器(elaborator)把设计描述成snapshot的形式。 NCLaunch的主窗口让你可以连接你编译和描述设计所需 要的工具 VHDL 编译器(compiler) Verilog 编译器(compiler) 描述器(Elaboretor)

之后就启动了simulator,会弹出2个窗口 : 设计浏览器(Design Browser)和 控制窗口(Console window)

设计浏览器(Design Browser)

控制窗口(Console Window)

在启动的时候,控制窗口(Console Window)有两个窗口。 SimVison窗口让你可以输入SimVison的命令; 仿真器(simulator)窗口让你可以输入Tcl simulator命令。 在你运行仿真的时候,控制窗口(console window)同样会在SimVision 和simulation窗口中显示消息。

选择Annotation一项, 在子菜单中选中除第一 项的所有条目。 在delay types中选择 Maximum一项,SDF 文件中对每项延时都有 最大值,典型值,最小 值,这里选择最大值用 于仿真

在上述步骤之后,会生成一个你的设计对应的snapshot,仿真 就是针对这个Snapshot进行的。如图示,选中该文件,点击 仿真按钮

启动NClaunch

在拷贝了源文件的文件夹下面启动 nclaunch -new & 多步模式(Multiple Step)使用ncvlog和 ncelab命令来编译和描述你的设计;单步模 式(Single Step)使用ncverilog命令。选 择多步模式。

选择多步模式 Multiple step

在设计窗口中设置探测对 象:比如要观察ex1中的 信号, 点击spi_test1图 示旁边的加号,展开设计 的层次结构。 右键选中ex1不放--> 选择菜单Create Probe

针对这个探测: · 选择Include sub-scopes下拉菜 单中的all选项以包含所有设计的 子域。 · 选择Include within each scope 下拉菜单中的all选项以包含输入 ,输出和双向端口。

仿真/仿真器(Simulator)

NC浏览(NCBrowse)

波形察看窗口(Waveform Window)

选中3个.v文件, 分别是库模型 smic25.v,网 表文件以及顶层 测试文件,点击

进行编译,之后会 在右边窗口中看到 帽子图标(工作库) 很多文件。

现在要描述你的设计: 要展开库(worklib), 选择顶层单元(也就是 测试中的module), 然后选择描述按钮 (elabrate )

NC-Verilog

综合后仿真

后仿概述

后仿是在前仿的基础上加入延时信息的功能 仿真。 同时验证了设计的时序以及功能都正确,并 且确保后仿功能和前仿一致。

实验任务

掌握前仿与后仿的区别 学会用NC-verilog对设计进行后仿 在SimVision分析环境下对设计中的问题进 行调试

前仿与后仿的区别

延时反标

在spi_test1中添加并保存一下语句:

initial

begin $sdf_annotate(“spi_interface.sdf",ex1); $sdf_annotate(“spi_interface.sdf",ex2); $sdf_annotate(“spi_interface.sdf",ex3); end

继续寻找与其相关的信 号,sck_neg_dtc,可以 发现寄存器 sck_neg_dtc_reg[0]的 输出信号名为n122,通 过仔细的检验,可以发 现sck_neg_dtc [0]被改 名为n122,修改网表把 它改回来: ctrl+f,将n122改为 sck_neg_dtc[0],选择 Change All

选择yes即可

再在Console Window 点击simulationrun即可,可以发 现sck_neg_dtc信号恢复正常。

谢谢!

作用不同

前仿又称功能仿真,是指在一个设计中,在 设计实现前对所设计的逻辑进行的验证其功 能是否正确的过程 后仿又称时序仿真,是对综合后或布局布线 后并且加入了延时信息的网表文件进行的仿 真,目的是验证时序以及功能都正确

波形不同

前仿的波形输出结果相对时钟沿没有延

迟。所有信号在时钟边沿上同时到来, 没有竞争冒险情况。 后仿因为加入了时序信息,波形输出结 果相对时钟沿有一定的延迟。各个信号 延时不同, 在不同的时刻发生翻转。

前仿和后仿所使用的仿真器是相同的,

所需的流程以及激励也是相同的,不同 点主要体现在以下几个方面 :

前仿与后仿的区别

仿真ห้องสมุดไป่ตู้需文件不同

作用不同

波形不同

仿真所需文件不同

前仿是对设计.v文件以及测试.v文件进行 仿真; 后仿所需文件是综合时产生的.v网表文 件,.sdf标准延时文件,测试文件以及工艺 库.v文件。

点击

进入nc_postsim文件夹

双击spi_test1,打开并加入反标命令, 退出时记得保存:File->save

准备工作介绍

在仿真已有的设计以前,必须编译和描述它。编译 过程将把源文件中的用HDL编写的单元编译成内在 的描述。描述设计将在设计的实例化,结构化信息 的基础上建立设计的层次结构,建立信号的连接, 计算所有对象的初始值。编译,描述和仿真自己的 设计要用到以下的工具: Ncvlog: 编译Verilog源文件。 ncelab 描述设计并且生成仿真的snapshot。 ncsim 对snapshot进行仿真仿真。

实验步骤

延时反标 编译设计网表以及顶层测试文件

建立设计

仿真

调试

延时反标

后仿最重要的就是延时反标,只有将延 时信息导入设计,仿真才能验证设计的 时序 施加命令对象: 在仿真的顶层测试文件里声明反标时序 信息,在本次试验中即spi_test1.v

延时反标

反标命令: $sdf_annotate(“spi_interface.sdf",ex1); 其中,spi_interface.sdf为延时文件名, 如果延时文件没有在目前工作目录下,还需 加入具体路径名; ex1为测试模块例化设计模块时的实例名。 在本次试验中,设计模块被例化三次,分别 为ex1,ex2,ex3。

仿真所需文件

netlist.v:DC综合生成的网表文件 .sdf:DC综合生成的标准延时文件 ,这个文 件中包含了设计的网表中单元和连线的延时 信息。 smic25.v:工艺库仿真文件,包含综合目标库 中元件的仿真模型信息

后仿分类

根据仿真对象分为两类: 综合后仿真:对DC综合后的网表进行仿 真,连线延时来自于通过线载模型的估计 布局布线后仿真:对布局布线后的网表 进行仿真,连线延时来自于版图的提取

sck_neg_dtc[0],n122 都已被声明过,所以改变 后sck_neg_dtc[0]被声 明两次,删除掉原n122 处的声明(包括后面的 逗号),并保存文件。

重新选中设计

spi_interface_mapped.v

并选中

然后在Console Window 点击simulationreinvoke simulator 出现图示对话框: