EDA实验教案

eda全套课程设计

eda全套课程设计一、教学目标本课程旨在让学生掌握eda的基本概念、原理和方法,培养学生运用eda技术解决实际问题的能力。

通过本课程的学习,学生应达到以下目标:1.知识目标:了解eda的基本概念、发展历程和应用领域;掌握eda的基本原理和方法,包括电路描述、逻辑设计、仿真验证等;熟悉eda工具的使用和操作。

2.技能目标:能够运用eda工具进行电路描述和逻辑设计;具备分析和解决eda 技术问题的能力;能够进行简单的eda项目实践。

3.情感态度价值观目标:培养学生对eda技术的兴趣和好奇心,激发学生主动学习和探索的精神;培养学生团队合作意识和沟通协调能力。

二、教学内容本课程的教学内容主要包括以下几个部分:1.eda概述:介绍eda的基本概念、发展历程和应用领域。

2.eda基本原理:讲解eda的基本原理,包括电路描述、逻辑设计、仿真验证等。

3.eda工具的使用:介绍常见eda工具的使用方法和操作技巧。

4.eda项目实践:通过实际项目案例,让学生掌握eda技术的应用。

三、教学方法为了提高教学效果,本课程将采用以下教学方法:1.讲授法:讲解eda的基本概念、原理和方法。

2.案例分析法:分析实际案例,让学生了解eda技术的应用。

3.实验法:让学生动手实践,掌握eda工具的使用。

4.讨论法:鼓励学生提问、发表见解,培养团队合作意识。

四、教学资源为了支持教学内容和教学方法的实施,我们将准备以下教学资源:1.教材:选用权威、实用的eda教材作为主教材。

2.参考书:提供相关的eda参考书籍,丰富学生的知识体系。

3.多媒体资料:制作精美的课件、视频等多媒体资料,提高学生的学习兴趣。

4.实验设备:配置足够的实验设备,确保每个学生都能动手实践。

五、教学评估为了全面、客观地评价学生的学习成果,本课程将采用以下评估方式:1.平时表现:通过课堂参与、提问、讨论等方式,评估学生的学习态度和积极性。

2.作业:布置适量的作业,评估学生对课程内容的掌握程度。

eda课程设计

eda课程设计一、教学目标本课程的教学目标是使学生掌握EDA(电子设计自动化)的基本概念、原理和方法,培养学生运用EDA工具进行电子系统设计和分析的能力。

具体目标如下:1.知识目标:(1)理解EDA的定义、发展历程和应用领域;(2)掌握常见的EDA工具及其功能;(3)了解电子系统设计的基本流程;(4)熟悉硬件描述语言(如VHDL、Verilog)的基本语法和用法。

2.技能目标:(1)能够熟练使用至少一种EDA工具进行电子系统设计;(2)能够编写简单的硬件描述语言程序,实现基本的电子系统功能;(3)具备分析电子系统性能和优化设计的能力;(4)能够阅读和理解电子设计相关的技术文档。

3.情感态度价值观目标:(1)培养学生的创新意识和团队合作精神;(2)增强学生对电子技术的兴趣和热情;(3)培养学生严谨的科学态度和良好的职业道德。

二、教学内容本课程的教学内容主要包括以下几个方面:1.EDA基本概念和原理:介绍EDA的定义、发展历程、应用领域和基本原理。

2.EDA工具的使用:介绍常见的EDA工具(如Cadence、Altera、Xilinx等)的功能和操作方法。

3.硬件描述语言:介绍硬件描述语言(如VHDL、Verilog)的基本语法、结构和用法。

4.电子系统设计流程:介绍电子系统设计的整个流程,包括需求分析、电路设计、仿真验证、硬件实现等。

5.电子系统性能分析与优化:讲解如何分析电子系统的性能,并提出优化设计的策略。

6.实例分析:通过具体案例,使学生掌握EDA工具在实际工程项目中的应用。

三、教学方法本课程采用讲授法、实践教学法和小组讨论法相结合的教学方法。

1.讲授法:用于讲解EDA的基本概念、原理和工具的使用方法。

2.实践教学法:通过实际操作EDA工具,使学生熟悉电子系统设计流程,提高实际操作能力。

3.小组讨论法:分组进行案例分析,培养学生的团队协作能力和解决问题的能力。

四、教学资源1.教材:选用权威、实用的EDA教材,如《电子设计自动化原理与应用》。

EDA课程设计_2

EDA课程设计实验1多功能数字电子钟1.1 实验目的1.2 实验仪器与器材1.EDA开发软件一套2.微机一台3.实验开发系统一台4.打印机一台5.其他器件与材料若干1.3 实验说明系统输入:系统状态及校时、定时转换的控制信号为k、set;时钟信号clk,采用1024Hz;系统复位信号为reset。

输入信号均由按键产生。

系统输出:LED显示输出;蜂鸣器声音信号输出。

多功能数字钟系统功能的具体描述如下:计时:正常工作状态下,每日按24 h计时制计时并显示,蜂鸣器无声,逢整点报时。

校时:在计时显示状态下,按下“set键”,进入“小时”校准状态,之后按下“k键”则进入“分”校准状态,继续按下“k键”则进入“秒复零”状态,第三次按下“k键”又恢复到正常计时显示状态。

1.“小时”校准状态:在“小时”校准状态下,显示“小时”的数码管闪烁,并以4Hz的频率递增计数。

2.“分”校准状态:在“分”校准状态下,显示“分”的数码管闪烁,并以4Hz的频率递增计数。

3.“秒”复零状态:在“秒复零”状态下,显示“秒”的数码管闪烁并复零。

整点报时:蜂鸣器在“59”分钟的第"51”、“53”、“55"、“57”秒发频率为512Hz的低音,在“59”分钟的第“59”秒发频率为1024Hz的高音,结束时为整点。

显示:要求采用扫描显示方式驱动6个LED数码管显示小时、分、秒。

闹钟:闹钟定时时间到,蜂鸣器发出周期为1s的“滴”、“滴”声,持续时间为10s;闹钟定时显示。

闹钟定时设置:在闹钟定时显示状态下,按下“set键”,进入闹钟的“时”设置状态,之后按下“k键”进入闹钟的“分”设置状态,继续按下“k键”则进入“秒”设置状态,第三次按下“k键”又恢复到闹钟定时显示状态。

1.闹钟“小时”设置状态:在闹钟“小时”设置状态下,显示“小时”的数码管闪烁,并以4Hz的频率递增计数。

2.闹钟“分”设置状态:在闹钟“分”设置状态下,显示“分”的数码管闪烁,并以4Hz的频率递增计数。

EDA实验教案1

四、实验报告要求

根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析、硬件测试和详细实验过程;设计原程序,程序分析报告、仿真波形图及其分析报告。

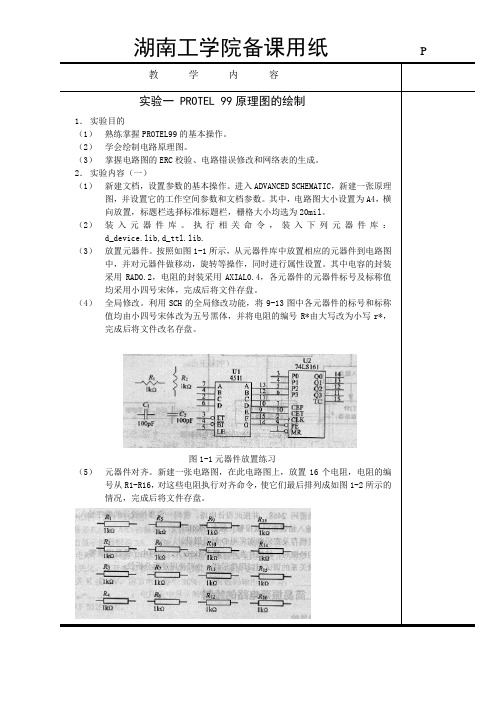

(12)给电路板图加上铺铜,铺铜与地相连,并且去除死铜,最后完成的印制电路板图如图2-7所示。

(13)将文件存盘退出.

图2-5完成自动布线图2-6连接完毕的电路

图2-7最后完成的电路板图

3.思考题

(1)简述自动布局的步骤。

(2)自动布线前,要进行哪些设置?

(3)何种类型的电路,在设计印制板时要使用铺铜?

五、实验思考和总结

1、讨论语句WHEN OTHERS=>NULL的作用。对于不同的VHDL综合器,此句是否具有相同含义和功能?

2、用VHDL例化语句(参考实验2)按图3-25的方式,以本章第一节实验三和本节实验一为底层元件,完成顶层文件设计,并重复以上实验过程。注意图3-25中的tmp是4位总线,led是7位总线。对于引脚锁定和实验,建议仍选实验电路模式6,用数码8显示译码输出,用键3作为时钟输入(每按2次键为1个时钟脉冲),或直接时钟信号clock0。

Macrofunctions项,然后选Counters项。

图3-4两位十进制计数器工作波形

向原理图编辑窗中调入宏功能元件如图3-2所示,直接在上端的Symbol Name栏中键入器件的名称,如74390等,然后点击OK键即可。如果要了解74390内部的情况,可以用鼠标在其上双击。最后根据图2-1在原理图编辑窗中完成该电路的全部绘制。绘制过程中应特别注意图形设计规则中信号标号和总线的表达方式:

EDA仿真实验教案

单管放大器的EDA仿真

一、实验目的 1、掌握EDA软件的使用方法。 2、学会用计算机仿真放大电路的整个过程和方法。

3、学会测量放大电路的静态工作点、计算电压放大倍数。 4、了解负载电阻对电压放大倍数的影响. 5、理解静态工作点对电压放大倍数和非线性失真的影响。 二、实验设备:计算机、EDA软件 三、实验电路

表1 RC 3k 3k Rb 20k 450k Ib Vb VC 静态工作点的位置

3k

1000k

(2)取输入电压Uim =5mV,f = 1kHz, Rb = 450k, RC=3k 。负载电 阻RL分别取2 k 、 3.3k 、8.2 k ,测量输出电压Uo ,计算电压 放大倍数并观察输出电压波形填入表2中。 表2

实验电路图

Rc

四、实验内容及步骤

1、进入软件工作平台

进入C盘electben5文件夹,鼠标双击WEWB32 2、选择器件及设备 (1)从主菜单的基础器件库中调出三个电阻为图中的Rb、RL、RC, 调出两个电解电容为图中的C1、C2 。 (2)从主菜单的晶体管库中调出一个NPN型三极管。 (3)从主菜单的电源库中调出一个直流电压源和接地标志。 (4)从主菜单的指示器器件库中调出三个电压表(一个为交流表), 一个电流表。 (5)从主菜单的仪器库中调出一个信号发生器和示波器。 3、电路图联接 。

EDA实验教案

EDA/VHDL实验教程实验一:熟悉Quartus II软件的基本使用方法我们将以简单的例子来介绍QuartusII的使用方法,包括设计输入,综合与适配,仿真测试,优化设计和编程下载等方法。

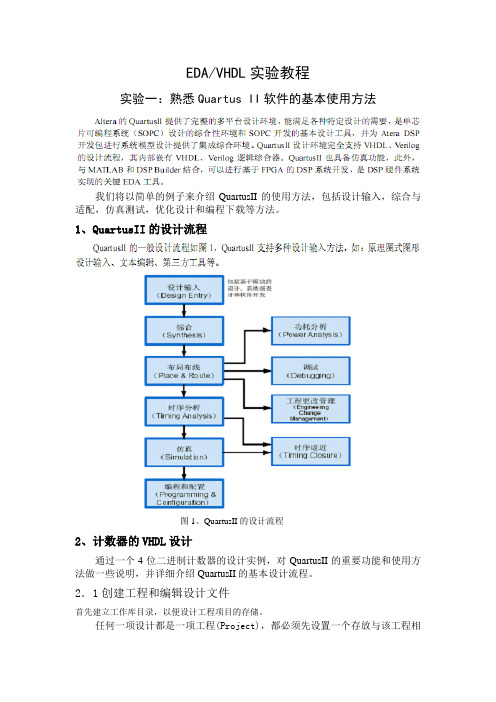

1、QuartusII的设计流程图1、QuartusII的设计流程2、计数器的VHDL设计通过一个4位二进制计数器的设计实例,对QuartusII的重要功能和使用方法做一些说明,并详细介绍QuartusII的基本设计流程。

2.1创建工程和编辑设计文件首先建立工作库目录,以便设计工程项目的存储。

任何一项设计都是一项工程(Project),都必须先设置一个存放与该工程相关的所有设计文件的文件夹。

这个文件夹被EDA软件默认为工作库(Work Library)。

不同的设计项目最好放在不同的文件夹中,同一工程的所有文件必须放在同一个文件夹中,文件夹设计不要设计在安装目录,不要将工程文件直接放在安装目录中。

图2-1、选择编辑文件的类型图2-2、编辑输入设计文件(程序见教材例3-21)图2-3、保持设计文件2.2创建工程在此利用New Project Wizard工具选项来创建设计工程,即令顶层设计cnt10.vhd为工程,并设计工程相关信息:工程名,目标器件,综合器,仿真器等。

图2-4、利用NewProjectWizard创建工程CNT4图2-5、将相关文件加入工程图2-6、选择仿真器和综合器(4)选择芯片,单击图2-6中的Next按钮,选择目标芯片。

首先在Family 栏选择MAX7000S,在Available Device栏选择EPM7128SLC84-15,可以通过右侧的封装、引脚数、速度等条件来过滤选择,选好之后按“OK”。

2.3编译前设置图2-8、选定目标芯片2.4编译图2-10、全程编译后出现的错误提示信息图2-11、编译完成后的QuartusII管理窗口界面2.5仿真图2-13、新建矢量波形文件图2-15、设置仿真时间区间图2-16、插入节点信号图2-17、选择节点图2-18、插入了信号节点的波形编辑器图2-19、设置时钟波形图2-20、仿真成功信息2.6引脚锁定和下载图2-23、编程窗口图2-24、硬件设置图2-25、增加硬件实验二:组合逻辑电路的设计实验目的:熟悉QuartusII软件下的VHDL文本设计流程,学习简单组合逻辑的设计,多层次电路的设计、仿真和综合后的电路图的查看。

eda技术实训课程设计

eda技术实训课程设计一、课程目标知识目标:1. 理解EDA技术的基本概念、原理及其在电子设计中的应用;2. 掌握EDA工具的使用方法,如原理图绘制、印制电路板(PCB)设计等;3. 学会利用EDA技术进行简单电路系统的设计、仿真与验证;4. 了解EDA技术的发展趋势及其在现代电子工程领域的地位和作用。

技能目标:1. 能够使用EDA工具完成原理图绘制、PCB布线等基本设计任务;2. 培养学生运用EDA技术解决实际电子工程问题的能力;3. 提高学生的团队协作能力和沟通能力,通过项目实训,掌握项目管理和时间规划技巧;4. 培养学生独立思考和创新能力,能够针对特定需求提出电子设计方案。

情感态度价值观目标:1. 培养学生对电子设计的兴趣,激发学习热情,树立良好的学习态度;2. 增强学生的实践操作能力,培养勇于尝试、善于克服困难的品质;3. 培养学生的创新意识和团队精神,提高职业素养,为未来从事电子工程设计奠定基础;4. 强化学生的环保意识,认识到电子设计在环保方面的重要性,培养绿色设计理念。

本课程针对高年级电子工程及相关专业学生,结合课程性质、学生特点和教学要求,将目标分解为具体的学习成果。

通过本课程的学习,使学生掌握EDA技术的基本知识,具备实际电子工程设计能力,为未来从事相关工作打下坚实基础。

同时,培养学生积极的学习态度、团队协作精神和创新能力,提高职业素养。

二、教学内容1. EDA技术概述- EDA技术发展历程- EDA技术的基本概念与分类- EDA技术在现代电子工程领域的应用2. EDA工具介绍- 常用EDA工具软件特点及功能对比- EDA工具的基本操作与使用方法- EDA工具在实际电子设计中的应用案例3. 原理图绘制- 电路原理图的基本元素与绘制方法- 元器件库的创建与管理- 原理图的层次化设计方法4. 印制电路板(PCB)设计- PCB设计的基本流程与方法- PCB布局、布线原则与技巧- PCB设计中的信号完整性分析5. 电路仿真与验证- 仿真软件的基本使用方法- 电路仿真模型的建立与参数设置- 仿真结果的分析与验证6. 项目实训- 项目需求分析- 项目设计、仿真与验证- 项目总结与汇报教学内容按照教学大纲安排,结合课本章节进行组织,确保科学性和系统性。

eda课程设计数字钟实验

eda课程设计数字钟实验一、课程目标知识目标:1. 学生能够理解数字时钟的基本原理,掌握EDA工具的使用方法,并能够运用Verilog HDL语言描述数字时钟的基本功能。

2. 学生能够掌握数字时钟设计中涉及的计数器、分频器等基本模块的工作原理和设计方法。

3. 学生了解数字时钟系统的层次化设计方法,并能够根据设计需求进行模块划分。

技能目标:1. 学生能够运用所学知识,使用EDA工具设计并实现一个简单的数字时钟,培养动手实践能力。

2. 学生能够通过分析问题、解决问题,培养逻辑思维能力和团队协作能力。

情感态度价值观目标:1. 学生通过实际操作,体验数字电路设计的乐趣,激发对电子信息技术学习的兴趣。

2. 学生在课程学习过程中,培养严谨的科学态度和良好的工程意识,提高对电子产品质量的追求。

3. 学生通过团队合作,培养沟通协作能力,增强团队意识和集体荣誉感。

课程性质:本课程为电子设计自动化(EDA)的实践课程,结合数字电路设计原理,让学生通过实际操作,掌握数字时钟的设计与实现。

学生特点:学生已经具备一定的电子信息技术基础,对数字电路有一定的了解,具备基本的编程能力。

教学要求:注重理论与实践相结合,强调学生的动手实践能力,鼓励学生独立思考和团队协作,培养解决实际问题的能力。

通过本课程的学习,使学生能够将所学知识应用于实际工程项目中,提高学生的综合素质。

二、教学内容本课程教学内容主要包括以下三个方面:1. 数字时钟原理及设计方法- 理解数字时钟的基本原理,包括计时原理、分频原理等。

- 学习数字时钟的模块化设计方法,掌握计数器、分频器等基本模块的设计与实现。

关联教材章节:第五章《数字时钟的设计与应用》2. EDA工具及Verilog HDL语言- 学习EDA工具的使用方法,如Quartus II等。

- 掌握Verilog HDL语言的基本语法和编程技巧,能够使用Verilog描述数字电路。

关联教材章节:第四章《EDA工具与Verilog HDL编程》3. 数字时钟设计与实现- 学习数字时钟的整体设计流程,包括模块划分、代码编写、仿真验证等。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

EDA实验指导

1

实验要求

• 实验和报告必须补上,同时 扣除该实验所占平时成绩。

• 实验中主要调试程序,练习软件的应用。 • 实验报告:内容充实,程序清单可以打印后附于实

验报告中;小结内容必须填写,并以经验总结的形 式回答思考题。

2

EDA实验设施

工程名

工程路径

16

(1)建立源程序

1)启动File \ New 菜单命令 2)选择Text Editor file,点击OK; 3)键入Verilog HDL代码:

用Verilog编写模块实现3-8译码器 模块名test1 输入:a,b,c 输出d0,d1,d2,d3,d4,d5,d6,d7

case({c,b,a})

钟 信 号 选 择 区 7

MAX+PLUS II 的操作环境

工程路径 和工程名称

工具栏 提供常 用功能 的快速 启动

“MAX+PLUS II” 菜单使你访问到 MAX+PLUS II的 所有功能

“Help ”菜单为 你提供 联机帮 助

状态提示条简要描述被选中的 菜单命令和工具栏按钮 8

MAX+plus II使用指南

endcase

4)保存为test1 .v文件

17

(2) 电路的编译与适配

1) 选择芯片型号 选择当前项目文件欲设计实现的实际芯片进行编译适配,点击Assign\Device 菜单选择芯片。

18

2)编译适配 启动MAX+plus II \ Compiler 菜单,按Start 开始编译,并显示编译结果, 生成下载文件。 如果编译时选择的芯片是CPLD,则生成 * ·pof 文件;如果是FPGA 芯片的 话,则生成* ·sof 文件,以备硬件下载编程时调用。同时生成 * ·rpt 报告文 件,可详细查看编译结果。如有错误待修改后再进行编译适配,如下图所 示。注意,此时在主菜单栏里的 Processing菜单下有许多编译时的选项,视 实际情况选择设置。

.GW48-CK EDA实验箱(硬件环境) . MAX+PLUS II (软件环境)

3

电源开关 和电源插口

25芯下 载接口

模拟信号 输入输出口

G W 48 C K E D A 实 验 箱

RS232串行 接口

4

插上 电源

25芯编程线与 PC机的并行口相接

实 验 箱

与

计

算

机

联

机

方

法

1

5

实

验

箱

将编程下载线与PC

点击‘1’,使拖黑 的电平为高电平

然后先点击此处

将弹出时钟周期

设置窗

23

6、选择仿真时间:视电路实际要求确定仿真时间长短,如下图所示。在本 实验中,我们选择软件的默认时间1us 就能观察到3-8 译码器的8 个输出状 态。

22

5、准备为电路输入端口添加激励波形,如下图所示。选中欲添加信号的管 脚,窗口左边的信号源即刻变成可操作状态,如箭头和圆括弧所示。根据 实际电路要求选择信号源种类,在本电路中我们选择时钟信号就可以满足 仿真要求。

用此键改变仿真 区域坐标到合适

位置。

先点击‘b’,将其 点为黑色

设置输入信号‘b’ 的周期为200ns

一、实验目的: 1、通过一个3-8 译码器的设计,掌握Verilog HDL设计方法。 2、掌握组合逻辑电路的静态测试方法。 3、初步了解可编程器件设计的全过程。 二、 实验步骤: MaxplusII 软件的基本操作与应用

15

(0)建立一个新工程

• 每个设计都是一个工程,都必须有一个工程名(符合命名规则) • 工程名必须与设计实体名(文本)一致(相符) • 工程路径不能包括汉字

19

(3)电路仿真与时序分析

MaxplusII 教学版软件支持电路的功能仿真(或称前仿真)和时序分析(或 称后仿真)。 1)添加仿真激励信号波形 1、启动MaxplusII\Wavefrom editor 菜单,进入波形编辑窗口,如下图 所 示。

从SNF文件中 输入设计文件 的信号节点

点击“LIST”

20

2、将鼠标移至空白处并单击右键,出现窗口。 3、选择Enter nodes from snf 选项并按左键确认,出现下图对话筐, 单击list和=>按钮,选择欲仿真的I/O管脚。

SNF文件中 的信号节点

最后点击“OK”

用此键选择左窗 中需要的信号

进入右窗

21

4、单击OK按钮,列出仿真电路的输入、输出管脚图,如下图所示。在 本电路中,3-8译码器的输出为灰色,表示未仿真前其输出是未知的。

与

机的打印机口相接

计

算

机

联

机

方

法

2

6

目标

注意,PCB板面抗高频芯片 干扰的细密栅孔铺层!

适配板

电路结构 模式接N向O.目1 标器件

的时钟信号 CLOCK1

实 验 箱 的 主 要 部 件

编程下载 ASIC

通过短路帽, CLOCK0上可选的 时钟频率有14种:

DSP与1HEzD---A50实MH验z

外 部 注意时钟 时 频率选择

3’b 000 : d[7..0]=1;

3’b 001 : d[7..0]=2;

3’b 010 : d[7..0]=4;

3’b 011 : d[7..0]=8;

3’b 100 : d[7..0]=16;

3’b 101 : d[7..0]=32;

3’b 110 : d[7..0]=64;

default: d[7..0]=128;

9

MAX+plusII的原理图编辑器

10

MAX+plusII的HDL文本编辑器

DSP与EDA实验

11

MAX+plusII的波形编辑器

12

MAX+PLUSII设计框图

设计输入

编译

修改设计

仿真与定时分析 管脚编辑

再编译

编程下载 硬件测试

13

MAX+PLUSII设计流程

14

实验一 MAX+PLUS II 软件的使用