计算机组成原理与体系结构_04_Cache Memory

计算机组成原理第四章作业答案

第四章作业答案解释概念:主存、辅存,Cache, RAM, SRAM, DRAM, ROM, PROM ,EPROM ,EEPROM CDROM, Flash Memory.解:1主存:主存又称为内存,直接与CPU交换信息。

2辅存:辅存可作为主存的后备存储器,不直接与CPU交换信息,容量比主存大,速度比主存慢。

3 Cache: Cache缓存是为了解决主存和CPU的速度匹配、提高访存速度的一种存储器。

它设在主存和CPU之间,速度比主存快,容量比主存小,存放CPU最近期要用的信息。

4 RAM; RAM是随机存取存储器,在程序的执行过程中既可读出信息又可写入信息。

5 SRAM: 是静态RAM,属于随机存取存储器,在程序的执行过程中既可读出信息又可写入信息。

靠触发器原理存储信息,只要不掉电,信息就不会丢失。

6 DRAM 是动态RAM,属于随机存取存储器,在程序的执行过程中既可读出信息又可写入信息。

靠电容存储电荷原理存储信息,即使电源不掉电,由于电容要放电,信息就会丢失,故需再生。

7 ROM: 是只读存储器,在程序执行过程中只能读出信息,不能写入信息。

8 PROM: 是可一次性编程的只读存储器。

9 EPROM 是可擦洗的只读存储器,可多次编程。

10 EEPROM: 即电可改写型只读存储器,可多次编程。

11 CDROM 即只读型光盘存储器。

12 Flash Memory 即可擦写、非易失性的存储器。

存储器的层次结构主要体现在什么地方?为什么要分这些层次?计算机如何管理这些层次?答:存储器的层次结构主要体现在Cache—主存和主存—辅存这两个存储层次上。

Cache—主存层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于Cache的速度,而寻址空间和位价却接近于主存。

主存—辅存层次在存储系统中主要起扩容作用,即从程序员的角度看,他所使用的存储器其容量和位价接近于辅存,而速度接近于主存。

计算机组成原理与体系结构

计算机组成原理与体系结构计算机组成原理(Computer Organization)是计算机科学与技术中的一门基础课程,主要研究计算机硬件与软件的组成和相互关系。

而计算机体系结构(Computer Architecture)则关注计算机系统的组织、功能和实现技术。

今天,我们将探讨计算机组成原理与体系结构的主要内容和重要性。

一、计算机组成原理的基本概念计算机组成原理是指计算机硬件和软件之间的关系。

它包括计算机的硬件设计、指令系统的设计和计算机内部结构的设计。

计算机组成原理主要研究以下几个方面:1. 计算机硬件设计:阐述了计算机中各种硬件组件的功能和相互关系,如中央处理器(CPU)、内存、输入输出设备等。

2. 指令系统的设计:指令系统是计算机硬件与软件交互的桥梁。

通过研究指令系统的设计,可以了解计算机的指令集类型、指令格式和操作码等。

3. 计算机内部结构的设计:指计算机中各个硬件组件之间的连接和数据流动方式。

这包括了数据路径、控制器和存储器等。

二、计算机体系结构的基本概念计算机体系结构是指计算机系统的组织和功能。

它描述了计算机中各个部件相互之间的关系以及这些部件的功能和特性。

计算机体系结构主要研究以下几个方面:1. 指令集体系结构(ISA):指令集体系结构确定了计算机系统中可执行的指令类型和操作。

ISA的设计决定了计算机的运算能力和适用领域。

2. 计算机层次结构:计算机系统按层次结构组织,分为硬件、操作系统和应用程序。

这些层次间的协作和接口规范对于实现高效的计算机系统至关重要。

3. 存储器系统:存储器系统包括主存储器、高速缓存和辅助存储器。

合理的存储器层次结构设计可以提高计算机系统的性能。

4. 输入输出系统:输入输出系统是计算机与外部设备之间的接口。

它负责数据的输入输出以及外设的控制和管理。

通过研究计算机组成原理与体系结构,我们可以更好地理解计算机的工作原理,为计算机系统的设计、优化和性能提升提供基础。

计算机体系结构与组成原理

计算机体系结构与组成原理计算机体系结构与组成原理是计算机科学与技术领域中的重要基础课程,它主要介绍了计算机系统的组成和工作原理。

本文将围绕这一主题展开探讨,从计算机体系结构和计算机组成原理两个方面展开论述。

一、计算机体系结构计算机体系结构指的是计算机硬件系统的架构和组织方式,它包括了计算机的指令集、寻址方式、存储器结构、总线结构、输入输出系统等。

计算机体系结构是计算机软件与硬件之间的接口,对计算机的性能和功能起着至关重要的作用。

1.1 指令集体系结构指令集体系结构定义了计算机能够执行的指令集合以及指令的格式和含义。

常见的指令集体系结构有RISC(精简指令集计算机)和CISC(复杂指令集计算机)。

这两种指令集体系结构在指令的数量、长度、执行速度等方面存在差异,对计算机的硬件设计和编程有着不同的影响。

1.2 存储器结构存储器结构是计算机中负责存储数据和指令的组成部分,包括主存储器(RAM)和辅助存储器(硬盘、固态硬盘等)。

常见的存储器结构有层次结构和并行结构。

层次结构中,各级存储器按照速度和容量的大小排列,高速缓存存储器(Cache)作为主存储器与CPU之间的缓冲区,提高数据的访问速度。

并行结构中,多个存储器模块同时工作,提高了数据的传输速率和系统的并行处理能力。

1.3 总线结构总线结构是计算机各部件之间传输数据和控制信息的通信线路,包括地址总线、数据总线和控制总线。

总线结构的设计要考虑数据传输的速度、容量和稳定性等因素,对于计算机系统的性能和可靠性有着重要影响。

二、计算机组成原理计算机组成原理是指计算机系统各个硬件组成部分的工作原理和实现方式。

它包括了算术逻辑单元(ALU)、控制器、寄存器、时钟信号等。

2.1 算术逻辑单元(ALU)算术逻辑单元是计算机中负责进行算术运算和逻辑判断的部件,它由逻辑门电路和寄存器组成。

ALU根据控制信号执行不同的运算操作,如加法、减法、乘法、除法等,同时也能够进行逻辑运算,如与、或、非等。

计算机组成原理第四章部分课后题答案(唐朔飞版)

4.1 解释概念:主存、辅存、Cache、RAM、SRAM、DRAM、ROM、PROM、EPROM、EEPROM、CDROM、Flash Memory。

主存:用于存放数据和指令,并能由中央处理器直接随机存取,包括存储器体M、各种逻辑部件、控制电路等辅存:辅助存储器,又称为外部存储器(需要通过I/O系统与之交换数据)。

存储容量大、成本低、存取速度慢,以及可以永久地脱机保存信息。

主要包括磁表面存储器、软盘存储器、磁带存储设备、光盘存储设备。

Cache:高速缓冲存储器,比主存储器体积小但速度快,用于保有从主存储器得到指令的副本很可能在下一步为处理器所需的专用缓冲器。

RAM:(Random Access Memory)随机存储器。

存储单元的内容可按需随意取出或存入,且存取的速度与存储单元的位置无关的存储器。

这种存储器在断电时将丢失其存储内容,故主要用于存储短时间使用的程序。

按照存储信息的不同,随机存储器又分为静态随机存储器(StaticRAM,SRAM)和动态随机存储器(Dynamic RAM,DRAM)。

SRAM:(Static Random Access Memory)它是一种具有静止存取功能的内存,不需要刷新电路即能保存它内部存储的数据。

DRAM:(Dynamic Random Access Memory),即动态随机存取存储器最为常见的系统内存。

DRAM 只能将数据保持很短的时间。

为了保持数据,DRAM使用电容存储,所以必须隔一段时间刷新(refresh)一次,如果存储单元没有被刷新,存储的信息就会丢失。

(关机就会丢失数据)ROM:只读内存(Read-Only Memory)的简称,是一种只能读出事先所存数据的固态半导体存储器。

其特性是一旦储存资料就无法再将之改变或删除。

通常用在不需经常变更资料的电子或电脑系统中,资料并且不会因为电源关闭而消失。

PROM:(Programmable Read-Only Memory)-可编程只读存储器,也叫One-Time Programmable (OTP)ROM“一次可编程只读存储器”,是一种可以用程序操作的只读内存。

计算机组成原理与体系结构_04_Cache Memory(补充)

2 Given the following specifications for an external cache memory: four-way set associative; line size of two 16-bit words; able to accommodate a total of 4K 32-bit words from main memory; used with a 16-bit processor that issues 24-bit addresses. Design the cache structure with all pertinent information and show how it interprets the processor’s addresses.

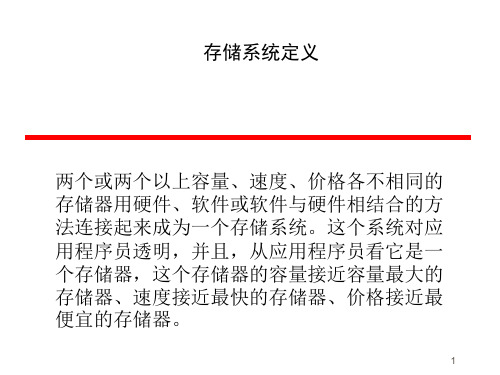

存储系统定义

两个或两个以上容量、速度、价格各不相同的 存储器用硬件、软件或软件与硬件相结合的方 法连接起来成为一个存储系统。这个系统对应 用程序员透明,并且,应用程序员看它是一 个存储器,这个存储器的容量接近容量最大的 存储器、速度接近最快的存储器、价格接近最 便宜的存储器。

1

存储系统

Homework 1 A set associative cache consists of 64 lines, or slots, divided into four-line sets, Main memory Contains 4K blocks of 128 words each, Show the format of main memory addresses.

西安电子科技大学_计算机组成与体系结构_第4章存储系统_课件PPT

存取方式 读写功能

随机读写:RAM 顺序(串行)访问:

顺序存取存储器 SAM 直接存取存储器 DAM

12

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质

在计算机中的用途

存放信息的易失(挥发)性

存取方式 读写功能

读写存储器 只读存储器

13

存储信息的介质

在计算机中的用途 存放信息的易失(挥发)性 存取方式 读写功能

易失:RAM 非易失:

ROM 磁盘

……

11

4.1 存储系统概述 4.1.2 存储器分类:不同的分类标准

存储信息的介质 在计算机中的用途 存放信息的易失(挥发)性

存储器的存取时间 与存储单元的物理 地址无关,随机读 写其任一单元所用

无

36

8086系统总线

D0~D7

A1~A13 MEMR MEMW

A0

D8~D15 A1~A13 MEMR MEMW

BHE

&

A19

A18

A17

&

A16 A15 A14

6264与8086系统总线的连接

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

6264

D0~D7

A0~A12

CS1

OE

WE

CS2

74LS138

每次读出/写入的字节数 存取周期

价格

体积、重量、封装方式、工作电压、环境条件

14

4.1 存储系统概述 4.1.2 存储器的性能指标

容量 速度 可靠性

可维修部件的可靠性: 平均故障间隔时间(MTBF)

计算机组成原理第四章课后习题及答案唐朔飞完整版

第4章存储器1. 解释概念:主存、辅存、Cache、RAM、SRAM、DRAM、ROM、PROM、EPROM、EEPROM、CDROM、Flash Memory。

答:主存:主存储器,用于存放正在执行的程序和数据。

CPU可以直接进行随机读写,访问速度较高。

辅存:辅助存储器,用于存放当前暂不执行的程序和数据,以及一些需要永久保存的信息。

Cache:高速缓冲存储器,介于CPU和主存之间,用于解决CPU和主存之间速度不匹配问题。

RAM:半导体随机存取存储器,主要用作计算机中的主存。

SRAM:静态半导体随机存取存储器。

DRAM:动态半导体随机存取存储器。

ROM:掩膜式半导体只读存储器。

由芯片制造商在制造时写入内容,以后只能读出而不能写入。

PROM:可编程只读存储器,由用户根据需要确定写入内容,只能写入一次。

EPROM:紫外线擦写可编程只读存储器。

需要修改内容时,现将其全部内容擦除,然后再编程。

擦除依靠紫外线使浮动栅极上的电荷泄露而实现。

EEPROM:电擦写可编程只读存储器。

CDROM:只读型光盘。

Flash Memory:闪速存储器。

或称快擦型存储器。

2. 计算机中哪些部件可以用于存储信息?按速度、容量和价格/位排序说明。

答:计算机中寄存器、Cache、主存、硬盘可以用于存储信息。

按速度由高至低排序为:寄存器、Cache、主存、硬盘;按容量由小至大排序为:寄存器、Cache、主存、硬盘;按价格/位由高至低排序为:寄存器、Cache、主存、硬盘。

3. 存储器的层次结构主要体现在什么地方?为什么要分这些层次?计算机如何管理这些层次?答:存储器的层次结构主要体现在Cache-主存和主存-辅存这两个存储层次上。

Cache-主存层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于Cache的速度,而寻址空间和位价却接近于主存。

主存-辅存层次在存储系统中主要起扩容作用,即从程序员的角度看,他所使用的存储器其容量和位价接近于辅存,而速度接近于主存。

计算机组成原理与体系结构_04_CacheMemory.

—Access time is independent of location or previous access

—e.g. cache

Memory Hierarchy

• Registers

—In CPU

• Internal or Main memory

—May include one or more levels of cache —“RAM”

• External memory

—Backing store

Memory Hierarchy - Diagram

Performance

• Access time

—Time between presenting the address and getting the valid data

• Memory Cycle time

—Time may be required for the memory to “recover” before next access

Pentium PowerPC 601 PowerPC 620 PowerPC G4 IBM S/390 G4 IBM S/390 G6

Pentium 4 IBM SP CRAY MTAb Itanium SGI Origin 2001 Itanium 2 IBM POWER5 CRAY XD-1

Type

• This would be very fast • This would need no cache • This would cost a very large amount

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1 Direct Mapping Cache Line Table

• Cache line • 0 • 1 • m-1 Main Memory blocks held 0, m, 2m, 3m…2s-m 1,m+1, 2m+1…2s-m+1 m-1, 2m-1,3m-1…2s-1

1 Direct Mapping Cache Organization

• Registers

—In CPU

• Internal or Main memory

—May include one or more levels of cache —―RAM‖

• External memory

—Backing store

Memory Hierarchy - Diagram

Performance

Location

• CPU • Internal • External

Capacity

• Word size

—The natural unit of organisation

• Number of words

—or Bytes

Unit of Transfer

• Internal

—Usually governed by data bus width

Locality of Reference

• During the course of the execution of a program, memory references tend to cluster • e.g. loopsnt of fast memory • Sits between normal main memory and CPU • May be located on CPU chip or module

• Cost

—More cache is expensive

• Speed

—More cache is faster (up to a point) —Checking cache for data takes time

Typical Cache Organization

Comparison of Cache Sizes

Cache Read Operation - Flowchart

4.3 Cache Design

• • • • • • Size Mapping Function Replacement Algorithm Write Policy Block Size Number of Caches

Size does matter

— 8 bit tag (=22-14) — 14 bit slot or line

• No two blocks in the same line have the same Tag field • Check contents of cache by finding line and checking Tag

Mapping Function

• Cache of 64kByte • Cache block of 4 bytes

—i.e. cache is 16k (214) lines of 4 bytes

• 16MBytes main memory • 24 bit address

—(224=16M)

1 Direct Mapping Example

1 Direct Mapping Summary

• Address length = (s + w) bits • Number of addressable units = 2s+w words or bytes • Block size = line size = 2w words or bytes • Number of blocks in main memory = 2s+w/2w = 2s • Number of lines in cache = m = 2r • Size of tag = (s – r) bits

Access Methods (2)

• Random

—Individual addresses identify locations exactly —Access time is independent of location or previous access —e.g. RAM

• Associative

1 Direct Mapping Address Structure

Tag s-r 8 Line or Slot r 14 Word w 2

• 24 bit address • 2 bit word identifier (4 byte block) • 22 bit block identifier

• External

—Usually a block which is much larger than a word

• Addressable unit

—Smallest location which can be uniquely addressed —Word internally —Cluster on disks

1 Direct Mapping

• Each block of main memory maps to only one cache line

—i.e. if a block is in cache, it must be in one specific place

• Address is in two parts • Least Significant w bits identify unique word • Most Significant s bits specify one memory block • The MSB s are split into a cache line field r and a tag of s-r (most significant)

William Stallings Computer Organization and Architecture 7th Edition Chapter 4 Cache Memory

1

4.1 Characteristics

• • • • • • • • Location Capacity Unit of transfer Access method Performance Physical type Physical characteristics Organisation

Access Methods (1)

• Sequential

—Start at the beginning and read through in order —Access time depends on location of data and previous location —e.g. tape

—Data is located by a comparison with contents of a portion of the store —Access time is independent of location or previous access —e.g. cache

Memory Hierarchy

• Transfer Rate

—Rate at which data can be moved

Physical Types

• Semiconductor

—RAM

• Magnetic

—Disk & Tape

• Optical