EDA技术及应用-第2章 可编程逻辑器件new 69页PPT

合集下载

EDA课件

输 入 … 输入 缓冲 电路 与 阵 列 或 阵 列

PLD输入缓冲 电路

输出 缓冲 电路 …

输 出

(3) 可以以组合方式输出,也可以以时序方式输出。 ) 可以以组合方式输出,也可以以时序方式输出。 可高电平有效,也可低电平有效。 可高电平有效,也可低电平有效。 内部有通路将输出信号反馈到输入端。 (4) 在PLD内部有通路将输出信号反馈到输入端。 ) 内部有通路将输出信号反馈到输入端

PAL结构 结构 逻辑功能可 变化的硬件 结构。 结构。

教材P.18的PAL16L8是一个16个输入变量, 个输出端, 教材P.18的PAL16L8是一个16个输入变量,8个输出端,输出 P.18 是一个16个输入变量 是时序( 低电平有效的器件。教材P.21 PAL16R8是时序 寄存器) P.21的 低电平有效的器件。教材P.21的PAL16R8是时序(寄存器)输 出结构。 出结构。

第2章 可编程逻辑器件简介

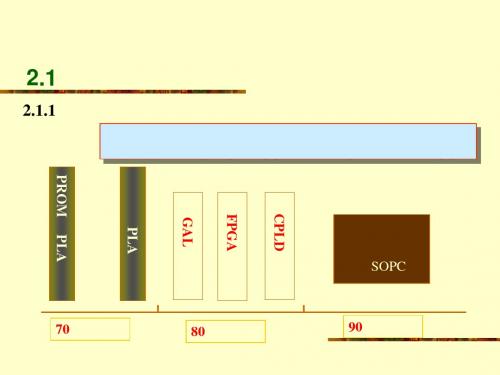

2.1

2.1.1 可编程逻辑器件的发展历程

可编程逻辑器件也称可重构器件

改 进 的 CPLD FPGA GAL 器 件 器 件 器 件 器 件 内嵌复杂 功能模块 的SOPC PLA PROM PROM 和 器 件 PLA 70

80

90

2.1.2 可编程逻辑器件的分类

1. 按集成度分类

可编程逻辑器件(PLD)

LD 简单 PLD

HD 复杂 PLD

PROM

PLA

PAL

GAL

CPLD

FPGA

2. 按内部结构分类

(1) 乘积项结构 ) 大部分CPLD都是乘积项结构,其基本结构是 都是乘积项结构, 大部分 都是乘积项结构 或阵列” “与—或阵列”; 或阵列

PLD输入缓冲 电路

输出 缓冲 电路 …

输 出

(3) 可以以组合方式输出,也可以以时序方式输出。 ) 可以以组合方式输出,也可以以时序方式输出。 可高电平有效,也可低电平有效。 可高电平有效,也可低电平有效。 内部有通路将输出信号反馈到输入端。 (4) 在PLD内部有通路将输出信号反馈到输入端。 ) 内部有通路将输出信号反馈到输入端

PAL结构 结构 逻辑功能可 变化的硬件 结构。 结构。

教材P.18的PAL16L8是一个16个输入变量, 个输出端, 教材P.18的PAL16L8是一个16个输入变量,8个输出端,输出 P.18 是一个16个输入变量 是时序( 低电平有效的器件。教材P.21 PAL16R8是时序 寄存器) P.21的 低电平有效的器件。教材P.21的PAL16R8是时序(寄存器)输 出结构。 出结构。

第2章 可编程逻辑器件简介

2.1

2.1.1 可编程逻辑器件的发展历程

可编程逻辑器件也称可重构器件

改 进 的 CPLD FPGA GAL 器 件 器 件 器 件 器 件 内嵌复杂 功能模块 的SOPC PLA PROM PROM 和 器 件 PLA 70

80

90

2.1.2 可编程逻辑器件的分类

1. 按集成度分类

可编程逻辑器件(PLD)

LD 简单 PLD

HD 复杂 PLD

PROM

PLA

PAL

GAL

CPLD

FPGA

2. 按内部结构分类

(1) 乘积项结构 ) 大部分CPLD都是乘积项结构,其基本结构是 都是乘积项结构, 大部分 都是乘积项结构 或阵列” “与—或阵列”; 或阵列

EDA技术及应用-第2章 可编程逻辑器件new共70页PPT资料

经一系列编译或转换程序,生成相应的目标文件,再 由编程器或下载电缆将设计文件配置到目标文件中。

2.1. 可编程逻辑器件概述

(1)最早的可编程逻辑器件

(Programmable Logic Array,PLA)

PLA

组成--全译码的与阵列 可编程的或阵列

其阵列规模大、速度低,主要用途是作为存储器。

(2)可编程逻辑阵列( Programmable Array Logic,PAL)

(1)简单可编程逻辑器件(SPLD)

包括可编程只读存储器(PROM)、 可编程逻辑阵列(PLA)、 可编程阵列逻辑(PAL) 通用阵列逻辑(GAL)。

GALl6V8 GAL22V10

2.2.4 PAL 一种PAL16V8的部分结构图

CLK/I 0 1

0

34

7 8 11 12 15 16 19 20 23 24 27 28 31

A0

F0

A1

F1

F1 F0

2.2.7 GAL

寄存器模式组合双向输出结构

寄存器输出结构

2.1. 可编程逻辑器件概述

(3) 通用阵列逻辑(Generic Array Logic,GAL) 熔丝编程方式。具有可擦除、可重复编程、数据 可长期保存和可重新组合结构等优点。

GAL比PAL使用更加灵活,因而在20世纪80年代得 到广泛的应用。

组成--可编程的与阵列

PAL

可编程的或阵列(固定)

它由可编程的与阵列和固定的或阵列组成。

2.2.3 PROM可编程原理

A1

A0

或阵列

(可编程)

F 1 A0 • A1

A1 A 1 A0 A 0 与阵列(固定)

F1

F0

2.1. 可编程逻辑器件概述

(1)最早的可编程逻辑器件

(Programmable Logic Array,PLA)

PLA

组成--全译码的与阵列 可编程的或阵列

其阵列规模大、速度低,主要用途是作为存储器。

(2)可编程逻辑阵列( Programmable Array Logic,PAL)

(1)简单可编程逻辑器件(SPLD)

包括可编程只读存储器(PROM)、 可编程逻辑阵列(PLA)、 可编程阵列逻辑(PAL) 通用阵列逻辑(GAL)。

GALl6V8 GAL22V10

2.2.4 PAL 一种PAL16V8的部分结构图

CLK/I 0 1

0

34

7 8 11 12 15 16 19 20 23 24 27 28 31

A0

F0

A1

F1

F1 F0

2.2.7 GAL

寄存器模式组合双向输出结构

寄存器输出结构

2.1. 可编程逻辑器件概述

(3) 通用阵列逻辑(Generic Array Logic,GAL) 熔丝编程方式。具有可擦除、可重复编程、数据 可长期保存和可重新组合结构等优点。

GAL比PAL使用更加灵活,因而在20世纪80年代得 到广泛的应用。

组成--可编程的与阵列

PAL

可编程的或阵列(固定)

它由可编程的与阵列和固定的或阵列组成。

2.2.3 PROM可编程原理

A1

A0

或阵列

(可编程)

F 1 A0 • A1

A1 A 1 A0 A 0 与阵列(固定)

F1

F0

EDA设计技术教学课件第2章可编程逻辑器件

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

2.3 通用逻辑阵列器件GAL

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

2.4 CPLD结构

➢ CPLD由行列式二维结构组成: ➢ 逻辑阵列块 ➢ 逻辑互联 ➢ 输入输出 ➢ 全局时钟网络单元 ➢ 用户闪存存储块

PPT文档演模板

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

FPGA的输入输出口

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

2.5.3时钟网络和锁相环逻辑块

➢FPGA的时钟网络 ➢由数目不等的时钟CLK、 ➢时钟选择开关MUX、 ➢锁相环逻辑PLL、 ➢时钟控制块等组成。 ➢ 每个锁相环逻辑模块生成五路时

2.4.4 输入输出口

➢ CPLD提供了丰富的器件资源和功能,特别是 输入输出口的端口数目、访问与控制方式

➢ CPLD的IO口支持LVTTL、LVCMOS标准 ➢ 可以在1.5V、1.8V、2.5V和3.3V等多电压内核

下工作 ➢ 利用集成开发软件进行可编程控制端口的驱动

强度、转换速率、输入延时,可配置弱上拉电 阻、三态缓冲、开路集输出、施密特触发器输 入

钟信号,经多路开关和时钟控制块, 输出全局时钟。

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

时钟选择和时钟控制块

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

➢锁相环逻辑PLL由时钟输入、时 钟切换逻辑、分频计数器、锁定 控制电路、相位比较器、滤波器、 压控振荡器、多路开关、范围检 测电路、延时补偿等组成。

EDA设计技术教学课件第2章可编程 逻辑器件

EDA设计技术教学课件第2章可编程 逻辑器件

2.3 通用逻辑阵列器件GAL

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

2.4 CPLD结构

➢ CPLD由行列式二维结构组成: ➢ 逻辑阵列块 ➢ 逻辑互联 ➢ 输入输出 ➢ 全局时钟网络单元 ➢ 用户闪存存储块

PPT文档演模板

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

FPGA的输入输出口

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

2.5.3时钟网络和锁相环逻辑块

➢FPGA的时钟网络 ➢由数目不等的时钟CLK、 ➢时钟选择开关MUX、 ➢锁相环逻辑PLL、 ➢时钟控制块等组成。 ➢ 每个锁相环逻辑模块生成五路时

2.4.4 输入输出口

➢ CPLD提供了丰富的器件资源和功能,特别是 输入输出口的端口数目、访问与控制方式

➢ CPLD的IO口支持LVTTL、LVCMOS标准 ➢ 可以在1.5V、1.8V、2.5V和3.3V等多电压内核

下工作 ➢ 利用集成开发软件进行可编程控制端口的驱动

强度、转换速率、输入延时,可配置弱上拉电 阻、三态缓冲、开路集输出、施密特触发器输 入

钟信号,经多路开关和时钟控制块, 输出全局时钟。

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

时钟选择和时钟控制块

PPT文档演模板

EDA设计技术教学课件第2章可编程 逻辑器件

➢锁相环逻辑PLL由时钟输入、时 钟切换逻辑、分频计数器、锁定 控制电路、相位比较器、滤波器、 压控振荡器、多路开关、范围检 测电路、延时补偿等组成。

EDA设计技术教学课件第2章可编程 逻辑器件

《可编程逻辑器件》PPT课件

13

2) 与、或全编程: 代表器件是FPLA(Field Programmable Logic

Array) 3)与编程、或固定: 代表器件PAL(Programmable Array Logic) 和GAL(Generic Array Logic) 、EPLD、FPGA (Field Programmable Gate Array )。

2021/7/10

35

GAL16V8逻辑图及引脚图

1

0

8

16

24

31

CK

0

19

OLM C

2

( 19)

8

18

OLM C

3

( 18)

16

4

17 OLM C ( 17)

24

16

5

OLM C ( 16)

可编程逻辑器件PLD

LDPLD (低密度 PLD)

HDPLD (高密度PLD)

PROM FPLA PAL GAL EPLD iSP FPGA

2021/7/10

16

8.2 现场可编程逻辑阵列(FPLA)

组合电路和时序电路结构的通用形式

A0~An-1

W0 D0

W(2n-1) Dm

2021/7/10

17

32

卡诺图化简:

YL 0 B A

00 DC

00 1 01 1

01 11 10

1 1 11

11

10

YL 1

BA 00

01

11 10

DC

00

01

11

11

10 1 1

1

YL 2

BA 00

01

DC

00

EDA技术及应用 (2)

第 2 章 硬件基础 利用SRAM实现组合逻辑函数时,只需列出真值表,输入作为

地址,输出作为存储内容,将内容按地址写入即可。具体步骤如 例2.2所示。

【例2.2】 利用LUT实现函数F =ABC+ABCD+AC。 解 首先列出F的真值表,如表2-1所示。

第 2 章 硬件基础

第 2 章 硬件基础 将F的值写入SRAM中(如图2-5所示),这样,每输入一组ABCD

第 2 章 硬件基础 2. 基本门电路的表示方式 PLD中的基本门电路符号如图2-2所示。图(a)为与门;图(b)

为或门;图(c)为输出恒等于0的与门及其简化表示形式;图(d) 中与门的所有输入均不接通,保持“悬浮”的1状态;图(e)为具 有互补输出的输入缓冲器;图(f)为三态输出缓冲器。

第 2 章 硬件基础 图2-2 PLD的基本门电路符号

第 2 章 硬件基础 在20世纪70年代,随着集成度的不断增加,设计师们尝试使

用更高密度的元件来实现逻辑功能,微处理器及随机访问存储器 (SRAM)这一类通用元件被设计师们广泛用于系统的设计,集成电 路的规模也发展到了大规模集成(Large Scale Integrated,LSI) 电路(通常包含几万个逻辑门),例如Intel 8008微处理器等。

第 2 章 硬件基础 20世纪80年代,借助于飞速发展的半导体技术及计算机技术,

设计师们提出了“EDA技术”的概念,即借助于计算机强大的处 理能力,利用软件及硬件描述语言HDL来完成数字系统的设计, 数字系统的设计流程也由传统的“自底向上”转换为“自顶向 下”,由此出现了ASIC技术。

第 2 章 硬件基础

第 2 章 硬件基础 SPLD的代表有可编程阵列逻辑(PAL)和通用阵列逻辑(GAL)。

EDA技术及应用(第二版)-第2章 可编程逻辑器件

2.3 复杂可编程逻辑器件(CPLD)

3.扩展乘积项

扩展乘积项有两种: (1)共享扩展项; (2)并联扩展项。

2.3 复杂可编程逻辑器件(CPLD)

3.扩展乘积项

(1)MAX7000A的 共享扩展项

2.3 复杂可编程逻辑器件(CPLD)

3.扩展乘积项

(1)MAX7000A的 并联扩展项

2.3 复杂可编程逻辑器件(CPLD)

谢谢!

输出使 能 输出信 号 输出时 钟

DQ

CE

摆率 控制

上拉或 下拉

三态输 出

缓冲器

Pad

输入 I1 信号

I2

QD

输入 缓冲器

Delay

时钟使 能

CE

输入时 钟

2.4 现场可编程门阵列器件(FPGA)

3.可编程互连PI

可编程开关点、 编程开关矩阵、 可编程连接线、 进位/借位链和全 局信号线(图中 未标出)

(3) 快速进位逻辑

快速

G 进位逻 辑

进位逻 辑

G4

为了提高FPGA的运算速

G3 G2

G′ G

度, 在CLB的两个逻辑函数发

G1

F

生器G和F之前还设计了快速进

进位逻 辑

F4

位逻辑电路。

F3 F2

F1

F′ F

CI N U P

CO UT

2.4 现场可编程门阵列器件(FPGA)

2.可编程输入/输出块IOB

A0 A1

An1

…

与阵列 (不可 编程)

W0 W1

W

p

…

1

或阵列 (可编程) …

F0 F1

Fm1

p 2n

2.2.1 可编程只读存储器(PROM)

EDA课件第2章

PLD的集成度分类 的集成度分类

可编程逻辑器件(PLD)

简单 PLD

复杂 PLD

PROM

PLA

PAL

GAL

CPLD

FPGA

一般将GAL22V10(500门~750门 )作为简单 ( 一般将 门 门 作为简单PLD 和高密度PLD的分水岭 和高密度 的分水岭

பைடு நூலகம்

四种SPLD器件的区别 器件的区别 四种

ispLSI器件的结构与特点 器件的结构与特点 (1)采用 工艺。 )采用UltraMOS工艺。 工艺 器件均支持ISP功能。 功能。 (2)系统可编程功能,所有的 )系统可编程功能,所有的ispLSI器件均支持 器件均支持 功能 (3)边界扫描测试功能。 )边界扫描测试功能。 (4)加密功能。 )加密功能。 (5)短路保护功能。 )短路保护功能。

JATG模 模 式

TCK

GND

-

-

GND

JTAG方式的在系统编程 方式的在系统编程

CPLD编程下载连接图 编程下载连接图

JTAG方式的在系统编程 方式的在系统编程

多个MAX器件的 器件的JTAG链配置方式 多个 器件的 链配置方式

FPGA器件的配置 器件的配置

Cyclone器件的 模式配置电路 器件的AS模式配置电路 器件的

2.9 FPGA/CPLD器件概述 器件概述

Xilinx公司的 公司的FPGA和CPLD器件系列 公司的 和 器件系列

1. Virtex-4系列 系列FPGA 系列 2. SpartanⅡ& Spartan-3 & Spartan 3E器件系列 Ⅱ 器件系列 3. XC9500 & XC9500XL系列 系列CPLD 系列 4. Xilinx FPGA配置器件 配置器件SPROM 配置器件 5. Xilinx的IP核 的 核

eda技术及应用PPT教学课件

输出配置区

4、输入输出单元IOC(I/O Cell) 5、巨型块(Megablock) 包括8个GLB,1个ORP,16个IOC和两个专用I/O 6、时钟分配单元 二、在系统编程 1、各种状态 2、实现方式 3、编程组态与接口

4、3低密度ISP-PLD原理 4、4 ISP-GDS原理

一、ispGDS(Generic Digital Switch)器件介绍 用于灵活配置连接状态的器件

1、3 EDA特征与工具

特征:自顶向下TOP DOWN 工具:物理工具(PCB制作等)

逻辑工具(PLD器件设计)

特别是ISP(In System Programmability) 和CPLD(Complex Programmable Logic

Device)的使用!

1、4 可编程数字ASIC

第四章、Lattice 公司可编程器件介绍 4、1 ISP器件概述

4、2高密度ISP-PLD器件

一、ispLSI器件结构原理 1、集总布线区GRP(Global Routing Pool)

完成信号互连 2、万能逻辑块GLB(Generic Logic Block)

可编程阵列 3、输出布线区ORP(Output Routing Pool)

3、3 GAL器件 一、GAL器件概述(Generic Array Logic) 1、器件特点

可以反复编程使用 2、分类与参数 二、普通型GAL器件 1、内部电路结构 2、输出逻辑宏单元(OLMC)

OLMC(Output Logic Macro Cell) 可以实现软件进行的多种配置输出形式

三、OLMC的输出结构类型 1、简单模式 2、复合模式 3、寄存器模式(时序电路基本结构) 四、GAL器件的开发与编程 1、硬件条件:编程器和计算机 2、软件条件:可编程器件编译软件 如:ABEL,FUSEMAP等等

4、输入输出单元IOC(I/O Cell) 5、巨型块(Megablock) 包括8个GLB,1个ORP,16个IOC和两个专用I/O 6、时钟分配单元 二、在系统编程 1、各种状态 2、实现方式 3、编程组态与接口

4、3低密度ISP-PLD原理 4、4 ISP-GDS原理

一、ispGDS(Generic Digital Switch)器件介绍 用于灵活配置连接状态的器件

1、3 EDA特征与工具

特征:自顶向下TOP DOWN 工具:物理工具(PCB制作等)

逻辑工具(PLD器件设计)

特别是ISP(In System Programmability) 和CPLD(Complex Programmable Logic

Device)的使用!

1、4 可编程数字ASIC

第四章、Lattice 公司可编程器件介绍 4、1 ISP器件概述

4、2高密度ISP-PLD器件

一、ispLSI器件结构原理 1、集总布线区GRP(Global Routing Pool)

完成信号互连 2、万能逻辑块GLB(Generic Logic Block)

可编程阵列 3、输出布线区ORP(Output Routing Pool)

3、3 GAL器件 一、GAL器件概述(Generic Array Logic) 1、器件特点

可以反复编程使用 2、分类与参数 二、普通型GAL器件 1、内部电路结构 2、输出逻辑宏单元(OLMC)

OLMC(Output Logic Macro Cell) 可以实现软件进行的多种配置输出形式

三、OLMC的输出结构类型 1、简单模式 2、复合模式 3、寄存器模式(时序电路基本结构) 四、GAL器件的开发与编程 1、硬件条件:编程器和计算机 2、软件条件:可编程器件编译软件 如:ABEL,FUSEMAP等等

EDA第2章-可编程逻辑器件

存储器的读写操作由地址信 号控制,通过地址解码器选 通对应的存储单元进行读写 操作。

存储器的容量和速度是衡量 其性能的重要指标,在数字 电路设计中广泛应用于数据 存储和程序存储等方面。

03

可编程逻辑器件的设计流程

设计输入

01

02

03

硬件描述语言

使用如VHDL或Verilog等 硬件描述语言进行设计输 入,描述电路的结构和行 为。

多次可编程类型的PLD可以在制造完 成后进行多次编程,用户可以通过编 程语言对器件进行配置和重构。

OTP类型的PLD在制造完成后无法更 改,需要通过特定的编程设备进行配 置。

可编程逻辑器件的应用

01

02

03

04

PLD在数字系统设计中具有广 泛的应用,如数字信号处理、

图像处理、通信等领域。

在数字信号处理中,PLD可以 用于实现滤波器、编码器等算

当触发器的输入信号发生变化 时,触发器会从当前状态翻转 到另一个状态,并保持该状态 直到再次受到输入信号的改变 。

触发器在数字电路设计中具有 重要作用,用于实现寄存器、 计数器等基本功能。

寄存器的工作原理

01

寄存器(Register)是一种可编程 逻辑器件中的存储元件,用于存储 二进制数据。

02

寄存器由多个触发器组成,可以 同时存储多个二进制位。

面临的挑战

设计和编程难度

随着可编程逻辑器件的规模不断扩大,设计和编 程的难度也在逐渐增加。

知识产权保护

可编程逻辑器件的设计涉及大量的知识产权,如 何保护知识产权成为行业面临的重要问题。

可靠性和稳定性

随着可编程逻辑器件的应用范围越来越广,其可 靠性和稳定性成为关键问题。

EDA技术与应用实践—可编程逻辑器件概述

FPGA 查找表(LUT,Look Up Table)

编程元素 非易失性(Flash,EEPROM)

易失性(SRAM)

特点

① 掉电非易失性:即使切断电源,电路中的数据 也不会丢失 ② 有限次编程、速度较慢 ③ 相对容量小,单位宏单元性价比低 ④ 直接加密,保密性好 ⑤ 无须外部存储器芯片,使用简单方便 ⑥ 上电后立即开始运作 ⑦ 可在单芯片上运作

第2章 可编程逻辑器件

第2章 可编程逻辑器件

2.1 可编程逻辑器件概述 2.2 CPLD的实现原理与典型结构 2.3 FPGA的实现原理与典型结构 2.4 FPGA/CPLD产品概述 2.5 FPGA/CPLD器件的配置与编程

2.1 可编程逻辑器件概述

2.1.1 可编程逻辑器件的基本结构

输入项

乘积项

偏向于较复杂、高速控制通道应用及数据处理

集成度

小~中规模

中~大规模

表 2 - 2 CPLD与FPGA的区别

⒉ 乘积项可编程结构PLD发展与成熟阶段 GAL(通用阵列逻辑) 采用的是EEPROM工艺。

⒊ 复杂可编程器件发展与成熟阶段 FPGA与CPLD

2.1 可编程逻辑器件概述

2.1.3 可编程逻辑器件的分类 ⒈ 按规模大小分类

图 2 - 2 可编程逻辑器件按规模分类

⒉ 按结构特点分类 基于乘积项结构和查找表结构的PLD ⒊ 按编程方式分类:一次性编程(OTP)和可多次编程(MTP)

① 掉电易失性:下载数据将存入SRAM,而SRAM掉电后 所存数据将丢失 ② 无限次、快速、动态配置 ③ 相对容量大,单位逻辑单元性价比高 ④ 一般不可以直接加密 ⑤ 需要外部配置ROM,使用相对复杂 ⑥ 内建高性能硬宏功能(PLL、存储器模块、DSP模块)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

IO...C

IO C

IO...C

IO C

IO...C

IO C

1.逻辑阵列块

逻辑阵列块由16个宏单元的阵列组成 LAB通过可编程连线阵(PLA)和全局总线连接在一起。 全局总线由所有的专用输入、I/O引线端子和宏单元 馈给信号组成。

每个LAB有如下输入信号: 来自通用逻辑输人的PlA的36个信号。 用于寄存器辅助功能的全局控制信号。

可编程逻辑器件的编程特性 有一次可编程 和重复可编程两类

2.1.4 PLD 相对于MCU的优势所在

1.MCU经常面临的难题 (1)运行速度 (2)复位 (3)程序“跑飞”LD/FPGA的优势 (1)高速性 (时钟延迟仅纳秒级 ) (2)高可靠性 (下载于同一芯片中 ) (3)编程方式 (采用JTAG在系统配置编程方式 )

或阵列用来产生乘积项之和形式的函数。

输入缓冲电路可以产生输入变量的原变量和反变量 输出结构可以是组合输出、时序输出或是可编程输出

2.1.3 可编程逻辑器件的基本结构和分类

2.可编程逻辑器件的分类 可编程逻辑器件的分类按其复杂程度及结构的不同,

可编程逻辑器件一般可分为4种: SPLD、CPLD、FPGA 和 ISP 器件。

(1)大规模 (2)低功耗 (3)模拟可编程 (4)含多种专用端口和附加功能模块的FPGA

2.1.3 可编程逻辑器件的基本结构和分类

1.可编程逻辑器件的基本结构 可编程逻辑器件的基本结构是:

组成------与阵列和或阵列 (核心) 输入缓冲电路和输出电路

------------------------------------------------------------与阵列用来产生乘积项

OE

19 I/O/Q 18 I/O/Q 17 I/O/Q 16 I/O/Q 15 I/O/Q 14 I/O/Q 13 I/O/Q 12 I/O/Q 11 I/OE

(2)复杂可编程逻辑器件

复杂PLD为逻辑板块编程,即以逻辑宏单元部的 与或阵列和外围的输入/输出模块。

不但实现了除简单逻辑控制之外的扩大了在整个 系统中的应用范围和扩展性。

它们是一种由用户根据自己要求来构造逻辑功能的数 字集成电路。

一般可利用计算机辅助设计,即用原理图、状态机、 布尔方 程、硬件描述语言(HDL)等方法来表示设计思 想。

经一系列编译或转换程序,生成相应的目标文件,再 由编程器或下载电缆将设计文件配置到目标文件中。

2.1. 可编程逻辑器件概述

(1)最早的可编程逻辑器件

2)作为寄存器使用时,每个宏单元的触发器可以单 独地编程为具有时钟控制的D、T、JK RS 触发 器。 如果需要的话,可将触发器旁路,以实现组 合逻辑工作方式

FPGA结构特点

传统 FPGA的分段布线

Source

Dest #1

连续布线和分段布线的比较

Dest #2

分段布线 - 性能不可预测, 并且,设计每重复一次,性能都会改变

(4)标准化设计语言 (标准的硬件描述语言 )

2.2 CPID的结构与工作原理

PLD( Erasable PLD),其基本结构与PAL/GAL 相仿,但集成度要高得多。

近年来器件密度越来越高,所以许多公司把原来 的EPLD的产品改称为CPLD,

但为了与FPGA、加以区别,限定采用EPROM 结构实现较大规模的PLD称为CPLD。

(1)简单可编程逻辑器件(SPLD)

包括可编程只读存储器(PROM)、 可编程逻辑阵列(PLA)、 可编程阵列逻辑(PAL) 通用阵列逻辑(GAL)。

GALl6V8 GAL22V10

2.2.4 PAL 一种PAL16V8的部分结构图

CLK/I 0 1

0

34

7 8 11 12 15 16 19 20 23 24 27 28 31

2.2.1 CPLD的基本结构

可以认为CPLD是----------将多个可编程阵列逻辑(PAL)器件集成到一个芯片, 具有类似PAL性能。

CPLD器件中至少包含三种结构:

可编程逻辑功能块(FB) 可编程I/O单元 可内部连线

(FB中包含有乘积项、宏单元等。)

2.2.2 Altera 公司MAX7000系列CPLD简介

LE(LC)结构图

进位输入 级联输入

数据1 数据2 数据3 数据4

Lab 控制 1 Lab 控制 2

Lab 控制 3 Lab 控制 4

查找表 (LUT)

进位链

级联链

清零和 预置逻辑

时钟选择

进位输出 级联输出

D

Q

CLRN

LE 输出

2.宏单元

MAX7000宏单元独立地配置为时序或组合工作方式。 宏单元由三个功能模块组成-----

a) 它是一种新型的高密度PLD。 内部由许多独立的可编程逻辑模块组成,逻辑块之间 灵活地相互连接。 b) 具有密度高、编程速度快、设计灵活等可再配置设 计能力等许多优点。

c) 器件的可用逻辑门数超过了百万门,并出现了内嵌 复杂功能模块(如加法器、乘法器、RAM、CPU核、 DSP核、PLI。等)

2.1.2 目前流行可编程器件的特点

LAB LE

FLEX 10K系列FPGA结构图

IOC

...

IOC

IOC

...

IOC

IOC

...

IOC

IOC

...

IOC

嵌入式 阵列块

IO...C

IO...C

IOC

IOC

EAB

IOC

...

IO...C

IOC

IOC

EAB

IO...C

IO C

IO...C

IO C

IO...C

IO C

IO...C

IO C

(1) 逻辑单元LE

(3)现场可编程门阵列(FPGA)

是由用户自行定义配置的高密度专用集成电路

它将定制的VLSI电路的单片逻辑集成优点和用户可 编程逻辑器件的设计灵活、工艺实现方便、产品上 三处结合起来;

器件采用逻辑单元阵列结构,静态随机存取存储工艺, 设计灵活,可重复编程,并可现场模拟调试验证。

(4)在系统编程(ISP)逻辑器件

MAX7000系列是高密度、高性能的CMOS CPLD

a)MAX7000系列提供600到5000可用门 b)b) 引线端子到引线端子的延时为6ns,计数器频 c) 率可达151.5MHz。

c) 它主要由逻辑阵列块、宏单元、扩展乘积项、 可编程连线阵列和 I/O 控制模块组成

三、基于乘积项的结构模块

0 0 0 0 0 1 1 0 0 0 0 0 0 0 1 1

输入C 输入D

多路选择器

查找表 输出

MAX7000S 系列的内部互连结构

Logic Array Block

可编程连线阵列

(2) 宏单元

(3) 扩展乘积项 局 部 连 线

共享扩展 项提供的 “与非” 乘积项

宏单元的 乘积项

逻辑

宏单元的 乘积项

19 I/O7 18 I/O6

2.2.5 GAL

图2-18 GAL16V8的结构图

I/CLK 1

0

34

78

11 12

15 16

19 20

23 24

27 28

31

0

7

I

2

8

15

I

3

16

23

I

4

24

31

I

5

32

39

I

6

40

47

I

7

48

55

I

8

56

63

I

9

CLK

OLMC OLMC OLMC OLMC OLMC OLMC OLMC OLMC

第2章 可编程逻辑器件

2.1. 可编程逻辑器件概述 2.2 CPLD的结构与工作原理 2.3 Xilinx公司XC4000系歹U FPGA简介 2.4 CPLD/FPGA开发应用选择 思考题与习题

2.1. 可编程逻辑器件概述

20世纪80年代以来出现了发展迅猛的新型集成电路, 可编程逻辑器件(Programmable Logic Devices,PLD)。

逻辑阵列、 乘积项选择矩阵

可编程触发器

见EPM7128E的宏单元如图2—9所示

2.宏单元

1) 逻辑阵列用于实现组合逻辑。 它可给每个宏单元提供 5个乘积项。

乘积项作为到“或”门和“异或”门的主要逻辑 输入,以实现组合逻辑函数;

乘积项作为宏单元中触发器的辅助输入:置位、清 除、时钟和时钟使能控制

宏单元

IOC

逻辑单元

IO C

...

IO C IO C

...

IO C

IO...C

IO C

FLEX 10K系列FPGA结构图

IOC

...

IOC

IOC

...

IOC

IOC

...

IOC

IOC

...

IOC

嵌入式 阵列块

IO...C

IO...C

IOC

IOC

EAB

IOC

...

IO...C

IOC

IOC

EAB

IO...C

IO C

0

7 I1 2

8

15 I2 3

11

10 01

R

00

11

10 01

R

00

SL0 7 SG1 SL17

SL0 6 SG1 SL16

11

10 01

R

Vcc 00

DQ Q

11

10 01

R

00

11

R

10 01

IO C

IO...C

IO C

IO...C

IO C

1.逻辑阵列块

逻辑阵列块由16个宏单元的阵列组成 LAB通过可编程连线阵(PLA)和全局总线连接在一起。 全局总线由所有的专用输入、I/O引线端子和宏单元 馈给信号组成。

每个LAB有如下输入信号: 来自通用逻辑输人的PlA的36个信号。 用于寄存器辅助功能的全局控制信号。

可编程逻辑器件的编程特性 有一次可编程 和重复可编程两类

2.1.4 PLD 相对于MCU的优势所在

1.MCU经常面临的难题 (1)运行速度 (2)复位 (3)程序“跑飞”LD/FPGA的优势 (1)高速性 (时钟延迟仅纳秒级 ) (2)高可靠性 (下载于同一芯片中 ) (3)编程方式 (采用JTAG在系统配置编程方式 )

或阵列用来产生乘积项之和形式的函数。

输入缓冲电路可以产生输入变量的原变量和反变量 输出结构可以是组合输出、时序输出或是可编程输出

2.1.3 可编程逻辑器件的基本结构和分类

2.可编程逻辑器件的分类 可编程逻辑器件的分类按其复杂程度及结构的不同,

可编程逻辑器件一般可分为4种: SPLD、CPLD、FPGA 和 ISP 器件。

(1)大规模 (2)低功耗 (3)模拟可编程 (4)含多种专用端口和附加功能模块的FPGA

2.1.3 可编程逻辑器件的基本结构和分类

1.可编程逻辑器件的基本结构 可编程逻辑器件的基本结构是:

组成------与阵列和或阵列 (核心) 输入缓冲电路和输出电路

------------------------------------------------------------与阵列用来产生乘积项

OE

19 I/O/Q 18 I/O/Q 17 I/O/Q 16 I/O/Q 15 I/O/Q 14 I/O/Q 13 I/O/Q 12 I/O/Q 11 I/OE

(2)复杂可编程逻辑器件

复杂PLD为逻辑板块编程,即以逻辑宏单元部的 与或阵列和外围的输入/输出模块。

不但实现了除简单逻辑控制之外的扩大了在整个 系统中的应用范围和扩展性。

它们是一种由用户根据自己要求来构造逻辑功能的数 字集成电路。

一般可利用计算机辅助设计,即用原理图、状态机、 布尔方 程、硬件描述语言(HDL)等方法来表示设计思 想。

经一系列编译或转换程序,生成相应的目标文件,再 由编程器或下载电缆将设计文件配置到目标文件中。

2.1. 可编程逻辑器件概述

(1)最早的可编程逻辑器件

2)作为寄存器使用时,每个宏单元的触发器可以单 独地编程为具有时钟控制的D、T、JK RS 触发 器。 如果需要的话,可将触发器旁路,以实现组 合逻辑工作方式

FPGA结构特点

传统 FPGA的分段布线

Source

Dest #1

连续布线和分段布线的比较

Dest #2

分段布线 - 性能不可预测, 并且,设计每重复一次,性能都会改变

(4)标准化设计语言 (标准的硬件描述语言 )

2.2 CPID的结构与工作原理

PLD( Erasable PLD),其基本结构与PAL/GAL 相仿,但集成度要高得多。

近年来器件密度越来越高,所以许多公司把原来 的EPLD的产品改称为CPLD,

但为了与FPGA、加以区别,限定采用EPROM 结构实现较大规模的PLD称为CPLD。

(1)简单可编程逻辑器件(SPLD)

包括可编程只读存储器(PROM)、 可编程逻辑阵列(PLA)、 可编程阵列逻辑(PAL) 通用阵列逻辑(GAL)。

GALl6V8 GAL22V10

2.2.4 PAL 一种PAL16V8的部分结构图

CLK/I 0 1

0

34

7 8 11 12 15 16 19 20 23 24 27 28 31

2.2.1 CPLD的基本结构

可以认为CPLD是----------将多个可编程阵列逻辑(PAL)器件集成到一个芯片, 具有类似PAL性能。

CPLD器件中至少包含三种结构:

可编程逻辑功能块(FB) 可编程I/O单元 可内部连线

(FB中包含有乘积项、宏单元等。)

2.2.2 Altera 公司MAX7000系列CPLD简介

LE(LC)结构图

进位输入 级联输入

数据1 数据2 数据3 数据4

Lab 控制 1 Lab 控制 2

Lab 控制 3 Lab 控制 4

查找表 (LUT)

进位链

级联链

清零和 预置逻辑

时钟选择

进位输出 级联输出

D

Q

CLRN

LE 输出

2.宏单元

MAX7000宏单元独立地配置为时序或组合工作方式。 宏单元由三个功能模块组成-----

a) 它是一种新型的高密度PLD。 内部由许多独立的可编程逻辑模块组成,逻辑块之间 灵活地相互连接。 b) 具有密度高、编程速度快、设计灵活等可再配置设 计能力等许多优点。

c) 器件的可用逻辑门数超过了百万门,并出现了内嵌 复杂功能模块(如加法器、乘法器、RAM、CPU核、 DSP核、PLI。等)

2.1.2 目前流行可编程器件的特点

LAB LE

FLEX 10K系列FPGA结构图

IOC

...

IOC

IOC

...

IOC

IOC

...

IOC

IOC

...

IOC

嵌入式 阵列块

IO...C

IO...C

IOC

IOC

EAB

IOC

...

IO...C

IOC

IOC

EAB

IO...C

IO C

IO...C

IO C

IO...C

IO C

IO...C

IO C

(1) 逻辑单元LE

(3)现场可编程门阵列(FPGA)

是由用户自行定义配置的高密度专用集成电路

它将定制的VLSI电路的单片逻辑集成优点和用户可 编程逻辑器件的设计灵活、工艺实现方便、产品上 三处结合起来;

器件采用逻辑单元阵列结构,静态随机存取存储工艺, 设计灵活,可重复编程,并可现场模拟调试验证。

(4)在系统编程(ISP)逻辑器件

MAX7000系列是高密度、高性能的CMOS CPLD

a)MAX7000系列提供600到5000可用门 b)b) 引线端子到引线端子的延时为6ns,计数器频 c) 率可达151.5MHz。

c) 它主要由逻辑阵列块、宏单元、扩展乘积项、 可编程连线阵列和 I/O 控制模块组成

三、基于乘积项的结构模块

0 0 0 0 0 1 1 0 0 0 0 0 0 0 1 1

输入C 输入D

多路选择器

查找表 输出

MAX7000S 系列的内部互连结构

Logic Array Block

可编程连线阵列

(2) 宏单元

(3) 扩展乘积项 局 部 连 线

共享扩展 项提供的 “与非” 乘积项

宏单元的 乘积项

逻辑

宏单元的 乘积项

19 I/O7 18 I/O6

2.2.5 GAL

图2-18 GAL16V8的结构图

I/CLK 1

0

34

78

11 12

15 16

19 20

23 24

27 28

31

0

7

I

2

8

15

I

3

16

23

I

4

24

31

I

5

32

39

I

6

40

47

I

7

48

55

I

8

56

63

I

9

CLK

OLMC OLMC OLMC OLMC OLMC OLMC OLMC OLMC

第2章 可编程逻辑器件

2.1. 可编程逻辑器件概述 2.2 CPLD的结构与工作原理 2.3 Xilinx公司XC4000系歹U FPGA简介 2.4 CPLD/FPGA开发应用选择 思考题与习题

2.1. 可编程逻辑器件概述

20世纪80年代以来出现了发展迅猛的新型集成电路, 可编程逻辑器件(Programmable Logic Devices,PLD)。

逻辑阵列、 乘积项选择矩阵

可编程触发器

见EPM7128E的宏单元如图2—9所示

2.宏单元

1) 逻辑阵列用于实现组合逻辑。 它可给每个宏单元提供 5个乘积项。

乘积项作为到“或”门和“异或”门的主要逻辑 输入,以实现组合逻辑函数;

乘积项作为宏单元中触发器的辅助输入:置位、清 除、时钟和时钟使能控制

宏单元

IOC

逻辑单元

IO C

...

IO C IO C

...

IO C

IO...C

IO C

FLEX 10K系列FPGA结构图

IOC

...

IOC

IOC

...

IOC

IOC

...

IOC

IOC

...

IOC

嵌入式 阵列块

IO...C

IO...C

IOC

IOC

EAB

IOC

...

IO...C

IOC

IOC

EAB

IO...C

IO C

0

7 I1 2

8

15 I2 3

11

10 01

R

00

11

10 01

R

00

SL0 7 SG1 SL17

SL0 6 SG1 SL16

11

10 01

R

Vcc 00

DQ Q

11

10 01

R

00

11

R

10 01