5.7GHzCMOS级间匹配低噪声放大器设计

一种5.7GHz CMOS全集成低噪声放大器的设计

一种5.7GHz CMOS全集成低噪声放大器的设计

邓桂萍;王春华

【期刊名称】《微电子学》

【年(卷),期】2007(37)2

【摘要】提出并设计了一种可以完全单片集成的5.7 GHz低噪声放大器(LNA)。

该电路结构利用MOSFET自身的栅寄生电阻,通过简单的LC网络变换实现输入匹配;并采用跨阻结构,实现输出匹配。

该电路采用TSMC 0.35μm CMOS工艺,用ADS模拟软件进行分析与优化。

结果表明,设计的低噪声放大器,其增益为11.34 dB,噪声系数为2.2 dB,功耗12 mW,输入反射系数-33dB,线性度-4 dBm。

【总页数】4页(P214-216)

【关键词】低噪声放大器;CMOS;输入匹配;输出匹配;噪声系数

【作者】邓桂萍;王春华

【作者单位】湖南大学计算机与通信学院

【正文语种】中文

【中图分类】TN722.3;TN432

【相关文献】

1.用于80

2.11a系统的5.8GHz 0.18μm CMOS全集成低噪声放大器设计 [J], 蒋东铭;黄风义;陆静学;赵亮

2.2.4GHz CMOS全集成低噪声放大器的设计 [J], 尹玉军

3.5.8 GHz CMOS全集成低噪声放大器设计 [J], 张尚坤;宋树祥

4.一种新型全集成CMOS低噪声放大器优化设计方法 [J], 黄晓华;王先锋;陈抗生;周金芳

5.一种应用于GPS接收机的全单片CMOS低噪声放大器 [J], 铁宏安

因版权原因,仅展示原文概要,查看原文内容请购买。

CMOS低噪声放大器的分析与设计的开题报告

CMOS低噪声放大器的分析与设计的开题报告一、选题背景随着现代电子技术的迅速发展,各种高性能、低功耗的电子设备被广泛应用到各个领域中。

而这些电子设备中,低噪声放大器(Low Noise Amplifier,LNA)则是至关重要的一个组成部分。

在通信领域中,LNA扮演着接收信号的第一道防线,因此其性能决定了整个系统的灵敏度、抗干扰能力和信噪比等重要指标。

而随着通信系统的发展,对LNA的性能要求也越来越高,要求其具备高增益、宽带、低噪声等优秀特性。

CMOS 技术因其具有低成本、低功耗、集成度高等优势,逐渐成为LNA研究领域的热点。

因此,LNA的分析与设计成为了当前重要的研究方向之一。

二、研究目的本课题旨在对CMOS低噪声放大器的原理和性能进行深入分析,设计出符合高性能LNA的设计需求的电路,并对其进行仿真与验证,最终得到性能优秀的LNA电路。

三、研究内容1. CMOS低噪声放大器的原理与基本结构2. LNA设计中常用的两种匹配方式——L型匹配和电感-电容匹配3. CMOS LNA的关键参数——增益、带宽、噪声系数等的计算与分析4. 所设计LNA电路的仿真与验证四、研究方法本课题首先进行对CMOS LNA的低噪声放大器原理、结构和匹配等分析,在此基础上,采用ADS软件设计出LNA电路,并通过仿真与验证对电路的性能进行评估和分析。

仿真时采用S 参数仿真,验证时则采用实验测试数据进行对比。

五、预期成果通过本次研究,预计可以得到以下成果:1. 对CMOS LNA的低噪声放大器原理、结构和匹配等方面有进一步的深入了解。

2. 成功设计出符合高性能LNA的需求的电路。

3. 对电路的实际性能进行评价,得出优秀的性能指标,并在仿真和实验中进行验证。

4. 通过实验的验证,为CMOS LNA的未来研究提供一定的参考。

六、论文结构1. 绪论:介绍论文的研究背景、意义和目的2. CMOS低噪声放大器的原理与设计3. LNA的匹配方式4. CMOS LNA的关键参数分析与计算5. LNA电路的仿真与验证6. 结束语:总结论文的研究内容和取得的成果,并对未来研究提出展望和建议。

低噪声高增益CMOS运算放大器设计的开题报告

低噪声高增益CMOS运算放大器设计的开题报告一、选题背景作为模拟电路中的一种重要电路,运算放大器具有很广泛的应用,被用于模拟信号的增益、滤波、混频、反相、微分和积分等处理。

在实际生产中,为了满足高质量、低功耗、小尺寸等需求,人们对运算放大器提出了更高的要求。

因此,本次设计将着重研究低噪声高增益CMOS 运算放大器的设计。

二、研究目的本次设计旨在设计一种低噪声高增益的CMOS运算放大器,使其具有以下特点:1. 低噪声2. 高增益3. 低功耗4. 小尺寸三、研究内容1. 分析低噪声高增益CMOS运算放大器设计的一般流程;2. 选择适合的MOS管工作状态,设计适合的偏置电路,优化电路增益和带宽;3. 利用MOS管的退化器原理,抑制共模干扰;4. 采用差分对和共模反馈,进一步降低噪声和增加增益;5. 综合以上措施,得到一种低噪声高增益CMOS运算放大器。

四、研究方法1. 对CMOS工艺进行分析,确定工作电压、电路结构和器件尺寸等参数;2. 选择合适的偏置电路,确定运算放大器工作点;3. 采用差分对和共模反馈技术,设计运算放大器电路;4. 通过仿真软件对设计的运算放大器进行仿真;5. 制作芯片并进行测试。

五、预期成果设计完成后,应该能够得到一种低噪声高增益CMOS运算放大器,具有以下特点:1. 低噪声2. 高增益3. 低功耗4. 小尺寸六、可行性分析本设计采用现有的CMOS工艺,通过分析和优化设计方法,针对低噪声高增益的要求,选用合适的器件尺寸和工作电压,经过仿真与验证后可以得到预期成果。

七、进度计划第1-2周:研究并确定设计方案第3-4周:仿真设计,优化电路结构第5-6周:制作芯片并进行测试第7周:数据处理与结果分析第8周:撰写完结论,准备答辩材料八、参考文献[1] Gray P,Hurst P.J,Lewis S.H,et al.亚微米精度的模拟集成电路设计原理 [M]。

俞学礼等杨晶坚译。

北京:科学出版社,2000。

CMOS射频低噪声放大器的设计

49 0 电 子 器 件

第 28 卷

dBm [2]。 在 LNA 设计中, 应力求上述各性能指标达 到最优, 但通常较难实现。 在实际设计中, 这些性能 指标会相互牵制、影响甚至矛盾; 因此在进行 LNA 设计时, 如何采用折衷原则兼顾各项指标是尤为重 要的[3 ]。

图 4 采用级间串联谐振技术的 CM O S LNA 除了漏 源级到衬底的寄生效应之外, 硅衬底电

阻的存在, 对M O S 管的源、漏极以及电感等重要元 件的电阻分量也产生重要影响。 这些寄生电阻的存 在不仅消耗了信号功率而且还产生热噪声; 最终对 LNA 的增益、噪声等性能指标产生不利影响[8]。 由 于衬底寄生电阻主要是由有效体电阻 (R b )、内部衬 底电阻 (R subi)、外部衬底电阻 (R ) subx 组成, 因此减小 衬底寄生电阻的措施就是围绕减小这三部分展开 的。在设计时, 将M O S 管周围的衬底相连可以减小 R subi、将体终端与外部接地相连可以使得 R subx 为零。 如图 5[7] 所示, 对于共源管M 1 而言, 较高的衬底阻

第3期

王 磊, 余宁梅: CM O S 射频低噪声放大器的设计

491

效应严重降低了噪声系数和功率增益[7]; 同时在输 出节点的电抗性并联谐振或者电抗性匹配中, 由于 低品质因数的衬底阻抗效应严重降低谐振峰值阻 抗, 导致增益降低。 而且在高频段应用 CM O S 技术 进行 LNA 的设计时, 由于漏 源级到衬底的寄生效 应使得信号损失, 严重降低了噪声系数和功率增益。 采取级间串联谐振技术可以比较合理地解决漏 源 级到衬底的寄生效应问题。 级间串联谐振技术的优 点在于它不仅能够改善电压增益, 而且避免了信号 通过衬底的损失。

图 2 变压器反馈技术 实现的片上集成变压器不仅占据的芯片面积更小而 且能够提供更好的性能指标[6]。在图 3[5]中, 初、次电 感线圈 L 11和 L 22组成一个差分变压器, 并且它们的 互感为 M ; 由 CM 1 和 L M 1 组成 L 形输入匹配网络; CTU RE和变压器的次级电感谐振于工作频率。

CMOS低噪声放大器中的输入匹配研究与设计

CMOS低噪声放大器中的输入匹配研究与设计1引言作为接收机的第一级,LNA的性能对整个接收机系统的性能起着至关重要的作用,因为整个系统的信噪比(SNR)很大程度上取决于LNA的噪声系数(NF)和增益。

因此,设计性能良好的LNA成为射频前端设计的重要目标。

由于低噪声放大器的各个指标常常会发生矛盾,彼此不能兼顾,因此设计是在噪声系数、增益、稳定性、阻抗匹配以及线性范围等指标之间采取折中考虑。

最近很多射频集成电路都是采用CMOS工艺来实现的,尤其是0.18μm的CMOS工艺很适于集成的SOC设计[1-2]。

目前最常见的输入匹配结构是源极电感负反馈结构,该结构有利于获得高增益和低噪声系数,但是存在较大的缺陷,即需要提供一个大感值的栅极电感(Lg)。

在实际标准的CMOS工艺下集成实现一个大感值的片上螺旋电感往往比较困难,而采用片外电感又不利于实现电路的集成及小型化,并且由于大感值栅极电感的寄生阻抗比较大,相应地产生热噪声也会比较大。

该文采用改进型输入匹配结构,用一个并联的小值LC网络来代替电感值比较大的栅极电感,并从进一步降低噪声系数和简化电路的角度考虑,移除源极负反馈电感(Ls)[3]。

2理论分析传统的输入阻抗匹配结构是源极电感负反馈结构,其输入阻抗表达式为[4]为满足式(3),栅极电感的感抗通常比较大。

如前所述,从利于电路集成实现和降低噪声系数的角度考虑,应当尽量避免使用大值电感。

该设计采用一个小值LC并联网络来代替。

图1是LC并联网络及其等效电路。

,在并联LC网络中,假设电感为一个理想的感抗L1和一个电阻R1的串联,其等效阻抗为Z=jωL2+R2(ω为低噪声放大器的中心工作根据式(4),如果能满足0<1-ω2L1C1<1,那么L2的电感值将比L1大,并且随ω趋近ω01,L1将产生更大的电感L2。

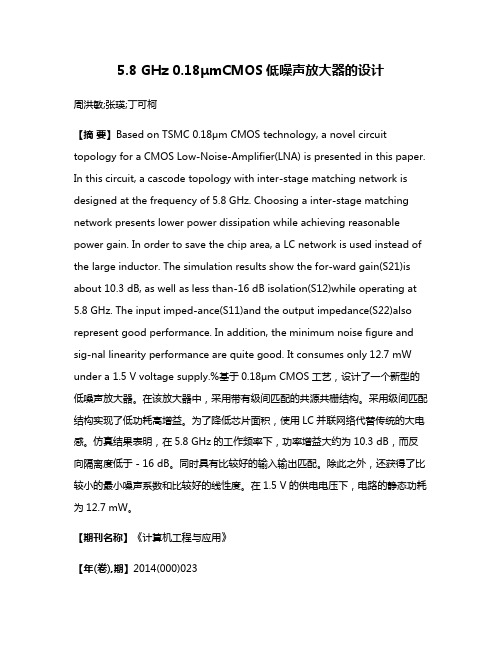

5.8 GHz 0.18μmCMOS低噪声放大器的设计

5.8 GHz 0.18μmCMOS低噪声放大器的设计周洪敏;张瑛;丁可柯【摘要】Based on TSMC 0.18μm CMOS technology, a novel circuit topology for a CMOS Low-Noise-Amplifier(LNA) is presented in this paper. In this circuit, a cascode topology with inter-stage matching network is designed at the frequency of 5.8 GHz. Choosing a inter-stage matching network presents lower power dissipation while achieving reasonable power gain. In order to save the chip area, a LC network is used instead of the large inductor. The simulation results show the for-ward gain(S21)is about 10.3 dB, as well as less than-16 dB isolation(S12)while operating at 5.8 GHz. The input imped-ance(S11)and the output impedance(S22)also represent good performance. In addition, the minimum noise figure and sig-nal linearity performance are quite good. It consumes only 12.7 mW under a 1.5 V voltage supply.%基于0.18μm CMOS工艺,设计了一个新型的低噪声放大器。

基于CMOS工艺的超宽带低噪声放大器设计的开题报告

基于CMOS工艺的超宽带低噪声放大器设计的开题报告一、研究背景和意义超宽带(Ultra-WideBand, UWB)是近年来新兴的无线通信技术,其传输带宽一般大于20 MHz,一般以极短脉冲时间间隔传输数据。

UWB技术具有以下优越性:(1)高速传输:UWB技术的传输速度可达到数Gbps,比传统的通信技术(如WLAN、Bluetooth)快上几个数量级。

(2)高保真度:UWB技术具有极好的时域特性,可提供准确可靠的位置和距离信息,适用于高精度定位和跟踪应用。

(3)抗干扰:UWB信号是低功率、短脉冲的宽带信号,干扰产生的能量很小,因此UWB信号不容易被其他无线设备干扰。

低噪声放大器(Low-Noise Amplifier,LNA)作为UWB系统中一项重要且难以实现的关键电路,承担着接收器前端的信号放大和噪声降低的任务。

在UWB系统中,LNA的主要目标是最大限度地提高接收器的灵敏度,并提高传输速率和特征值的信噪比。

此外,LNA还需要尽可能降低功耗、占用面积和成本,以提高整个系统的性能。

基于CMOS工艺的LNA已经成为了UWB通信领域的核心研究方向。

CMOS工艺具有功耗低、占用面积小、成本低等优点,可以满足UWB通信系统对电路设计的要求。

因此,设计一种基于CMOS工艺的超宽带LNA,具有促进新一代UWB无线通信技术发展的重要意义。

二、研究内容和方法本文旨在设计一种基于CMOS工艺的超宽带LNA,并分析其性能表现。

具体研究内容和方法如下:(1)分析UWB系统的要求和LNA的设计指标,建立设计模型。

(2)根据设计模型,利用Cadence软件设计出LNA电路,并进行仿真验证。

该电路包括放大器的结构、调制方式、传输媒介和双平衡混频器(Double Balanced Mixer,DBM)的设计。

(3)根据仿真结果优化LNA电路,进一步提高其性能表现,并进行特性分析。

(4)在TSMC 65nm工艺下进行电路实现,对电路进行测试评估,比较仿真结果和实验结果,验证设计结果的准确性和性能表现。

用于802.11a系统的5.8GHz 0.18μm CMOS全集成低噪声放大器设计

第30卷 第2期2007年4月电子器件Ch inese Jou r nal Of Elect ro n DevicesVol.30 No.2Ap r.20075.8GHz All 2on 2Chip L ow N oise Amplif ier in 0.18μm CMOS f orApplicat ion of 802.11a System 3J IA N G D on g 2mi n g ,H U A N G Fen g 2y i3,L U J i n g 2x ue ,Z H AO L i a ng(Ins ti t ute of R F &O E 2IC ,S out heast Universit y ,N anj i ng 210096,China)Abstract :A n a nal ysi s of i nput 2matchi ng and noi se and linearit y i s present ed ,which follows up a met hod t o upgrade t he general performa nce of Low Noise Amplifier.Noi se opt imization i s t aken on by sof tware and a 5.8GHz al l 2on 2chip Low Noi se Amplifier i n 0.18μm CMOS t echnology i s present ed.Wit h t he mea sure 2ment dat a of i nduct ors applied by t he Foundry ,paramet er ext raction i s carri ed on for t hese i nduct ors.An accurate on 2chip inductor s model i s realized for t he ci rcui t sim ulation.The result is t hat t he total circuit ’s power consumption i s 13mW ,t he power gain i s 14dB ,t he noi se fi gure i s 2.05dB ,and t he li neari t y per 2for ma nce i s t he IIP3of -1dBm.K ey w or ds :low noi se amplifier ;CMOS technology ;noi se opti mization ;inductor model EEACC :2570;1220用于802.11a 系统的 5.8GH z 0.18μm CMOS 全集成低噪声放大器设计3蒋东铭,黄风义3,陆静学,赵 亮(东南大学射频与光电集成电路研究所,南京210096,China)收稿日期62823基金项目江苏省自然科学基金资助(B K 66)作者简介蒋东铭(2),男,在读硕士生从事射频集成电路设计研究,y_j @63;黄风义(62),男,教授,博士生导师,f y @摘 要:通过对输入匹配、噪声和线性度的分析,给出了改进低噪声放大器综合性能的方法.利用软件对电路进行噪声优化,设计出了一个0.18μm CMOS 工艺的5.8GHz 全集成低噪声放大器.采用工艺厂家提供的电感测试数据进行参数提取,得到精准的电感模型并用于电路仿真.设计结果是整个电路功耗13mW ,功率增益为14dBm ,噪声系数为2.05dB ,线性度指标IIP3为-1dBm.关键词:低噪声放大器;CMOS 工艺;噪声优化;电感模型中图分类号:TN 722.3;TN 702 文献标识码:A 文章编号:100529490(2007)022******* 随着宽带无线通信技术的不断发展和市场的不断扩大,5GHz 无线射频频段得到了越来越广泛的应用[1].CMOS 工艺的高集成度、低价、低功耗使其生产的射频芯片比砷化镓工艺或双极性硅工艺的芯片具有明显的性价比优势[2];在芯片系统(Syst em On Chip ,SOC)的提出,要求越来越多的电路元件集成到单个芯片上.低噪声放大器(LNA )是无线射频接收机前端的重要模块,它的噪声系数、增益和线性度等指标对整个射频接收机系统的性能有重要影响,其中噪声系数几乎决定了整个接收机的噪声性能[1,2].本文设计的低噪声放大器使用0.18μm CMO S 工艺,可应用于WLAN 802.11a 标准的5.725~5.825GHz 频段.全部采用片上元件来实现,其中电感采用的是片上螺旋电感.基于螺旋电感的测量数据进行了电感模型参数提取,并用于电路仿真,提高了电感模型的精确度,也避免了使用键合线电感时感值不易控制的缺点.8:20001:20040:1979do m ian g 1.co m 194hua n g se 1 低噪声放大器电路设计在满足输入匹配前提下获得低噪声一般都采用源极电感负反馈的方式来实现[7].实际电路中则采用共源-共栅(Cascode )结构,可以减小MOS 管的密勒效应,减小输入匹配和输出匹配之间的影响,同时增加反向隔离度[3].本次设计采用的电路结构如图1所示.通过对传统结构的改进,在输入电感L g 和MOS 管M 1之间并联了接地电容C p 来调节输入功率匹配和最小噪声匹配,并适当增加输入响应的平坦度.图1 L NA 电路图1.1 输入匹配对于射频信号,隔直电容C in 可以忽略.输入信号电路如图2.图中将电路划分了两个参考平面.参考平面1的左侧所表现的信号输入阻抗即为信号源图2 输入匹配电路的输入阻抗R s ,一般为50Ω.现定义参考平面2的右侧,即晶体管一侧的输入阻抗为Z in =R eq +j ω0L eq .因此为了实现功率匹配,则需要使参考平面2左侧的输入阻抗匹配为R eq -j ω0L eq .此时有R eq =R sω2C 2pR 2s+(1-ω20C p L g )2(1)L eq=L g -C p (ω20L 2g +R 2s )2ω20C 2p R 2s +(1-ω20C p L g )2(2)而根据[5],有Z =j ωL +j ω+L =L +j (ωL ω)(3)C gs 为栅极和源极之间的电容,g m 为MOS 管的跨导.当输入电路谐振在ω0频率时,参考平面2两侧电路的实数部分相等,而复数部分则相互抵消,从而实现最大功率传输.1.2 噪声优化共源共栅结构的低噪声放大器,其噪声系数主要由共源的NMOS 管决定,而共栅管对噪声系数的影响很小,可以忽略[8].源极电感L s 形成源极去偶结构,在提高线性度的同时并不引起噪声系数的增加[7].本次设计所用的片内电感由于Q 值不高,提高了设计难度.采用精确的片上电感模型,提高仿真模型的精确度,能更精确的仿真和优化噪声系数[3].片上电感模型将在后文叙述.根据功率约束噪声优化设计方法[4],可以得到M 1的最优栅宽为W opt =13ω0LC o x R ′s(4)上式中C o x 为栅氧化层电容,L 为有效沟道长度,R ′s 为等效电源内阻,输入匹配时近似为R eq .这一最优栅宽W opt 在20%范围内变化对噪声系数的影响不大,一般小于0.2dB 左右.对于栅宽W opt 的器件,得到最小噪声系数为[7]F min =1+2.4γαω0ωT(5)γ和α是与沟道长度相关的参数,由工艺给出,ωT 为MO S 管的截止频率ωT ≈g mC gs(6)通过增加栅极电压可增大MO S 管的跨导g m ,能够提高MOS 截至频率ωT ,降低噪声系数.1.3 电路的线性度共源共栅结构的电路,其线性度主要由共栅管M 2决定.因此改善M 2管的栅宽W 和提高栅极直流偏压V gs 能有效地提高整个电路的线性度[5].但是M 2管的V gs 的增加又会导致M 1管的源漏电压V ds 的降低,降低了M 1管的线性度.因此,在不增加整体电路直流电压的情况下,电路线性化的改善主要通过M 2管的栅宽优化来得到.2 电路仿真与优化本次设计采用TSMC 的0.18μm CMOS 工艺库,基于BSIM3模型,采用Agilent 公司的ADS2003C 来进行电路仿真.为了提高片上电感的准确度,对片上电感单独进行了建模和参数提取仿真时采用的为电感模型为双π模型,如图3利用工艺厂家提供的片上电感的S 参数测试数据,183第2期蒋东铭,黄风义等:用于802.11a 系统的5.8GHz 0.18μm CMO S 全集成低噪声放大器设计8i n0s 10C g s g m C gssg m C gs s 0s -10C gs..用自主开发的模型参数提取方法[6]对模型进行了参数提取.参数提取结果再进行S参数仿真并和测试结果进行对比,如图4.片上电感品质因素Q的测试结果与仿真结果的对比如图5.从图4和图5可以看出,该模型在0~15GHz频段内能够很精确地模拟片上电感的性质.图3 片上螺旋电感的双π模型图4 电感S参数仿真与测试结果对照图5 电感品质因素仿真与测试结果对照通过ADS软件对电路进行优化得到LNA主要参数选择如下:M1栅宽90μm,栅极偏压为0.8 V,M2栅宽80μm.仿真在25℃、输入输出负载50Ω条件下,采用1.8V电源供电,得到的结果如图6~图9.(1)图6为S11和S22参数曲线,分别表征了输入端口与输出端口的匹配程度.在5.8GHz频率上,输入反射系数和输出反射系数都达到了-25 dB,实现了较好的匹配.(2)图7为S21参数曲线,表征了整个电路的增益情况.由图可知,在5.8GHz时,正向传输增益接近14dB.(3)图8为噪声系数曲线在中心频率58G z处整个电路的噪声系数为5B对于L和L都用片内电感实现,由于Q值较低,因此这个噪图6 输入与输出反射系数S11,S22图7 功率增益S21声系数是比较合理的.图8 噪声系数(4)图9为电路的1dB压缩点和三阶互调点的曲线.从图中可知,电路的1dB压缩点输入功率(P1dB)约为-12dBm,三阶互调点输入功率(IIP3)约为-1dBm.图9 线性度P1dB与IIP33 版图设计版图设计采用Cadence设计工具和TSMC的0.18μm CMO S元件库.在设计中,对于高频信号采用8边形焊盘,并使用顶层金属,减小焊盘的寄生电容和耦合引起的损耗整个版图如图所示由于电感都选用片内元件,因此面积较大版图将交付工艺厂家流片加工283电 子 器 件第30卷8..H2.0d.g s.10...图10 低噪声放大器版图4 结论通过理论推导和软件优化,并采用精确电感模型进行了电路仿真,设计了一个中心频率5.8GHz,噪声系数为2.05dB的CMO S全集成低噪声放大器,且实现了输入输出的良好匹配.本文所采用的电路优化方法,可为射频集成电路在芯片系统设计提供参考.随着工艺的提高和成本的继续降低,CMOS工艺能够更多地利用片上电感来设计射频集成电路.参考文献:[1] Lee Tho m as H,Hi rad Samavat i,Ham i d R R.52GHz CMOSWi reless LANs[J].IEEE TM T T,2002,50(1):2682280.[2] Asad A Abi di.R F C MOS Comes of Age[J],IEEE Micro waveMagazine,Decem ber2003,47260.[3] Chi u Hu ng2Wei,Lu Shey2Shi,Li n Y o2Sheng.A2.172dB NF5GHz Band Mo nol it hic CMOS LNA wit h102mW DC PowerC o nsumpt ion[J],IEEE TM T T,Mar.2005,53(3):8132824.[4] M.Kumarasamy,et al.A Full y Integrat ed Vari abl e Gai n5.752GHz LNA wi t h on Chip Act ive Bal un fo r WL AN[C]//IEEE RFIC Sym po s i um,2003,4392442.[5] VojkanVidoj kovic,et al.Fully2Int er grat ed D EC T/Bl uet oot hMult i2ban d LNA In0.18μm CMOS[C]//IEEE ISCAS,2004, 5652568.[6] Lu J ingxue,Huang Fengyi,Yusong Chi.An Anal ytical Ap2p roach t o Paramet er Ext ract ion fo r On2Chip Spiral Induct ors Wit h Symmet ric Do ubl e2πEqui valent Circui t[C]//IEEE R FIC Symposiu m,2006,2212224.[7] Lee Tho mas H.CMOS射频集成电路设计[M],电子工业出版社,2004.[8] Behzad Razavi.模拟CMOS集成电路设计[M],西安交通大学出版社,2004.(上接第379页)[4] 李子东.实用粘结手册[M].上海:上海科学技术出版社,1987:1.[5] 浩宏奇,金志浩,王笑天.陶瓷钎焊的研究[J],兵器材料科学与工程,1994,17(1):13.[6] 陈铮.陶瓷2金属活性金属钎焊研究的现状和进展[J],华东船舶工业学院学报(自然科学版),2001,15(2):1.[7] Treheux D.et al.Metal/Ceram i c S oli d St at e Bo ndi ng:Mecha2nis ms and Mechanics[J].Script a Metall urgi cal et Mat eri alia,1994,31(8):1055.[8] IINO Y.Part ial Transient Li qui d2Phase Met al s L ayer Tech2nique of Ceramic2Met al B o ndi ng[J].J Mat er Sci L et t,1999,(10):104.[9] 陈铮,周飞,李志章等.陶瓷与金属活性钎焊的研究进展[J].材料科学与工程,1995,13(3):61.[10] 刘联宝.陶瓷2金属封接技术指南[M].国防工业出版社,1990.6:69.[11] 盛文彦,曾令可,王慧等.结构陶瓷表面改性技术[J],佛山陶瓷,2005,(4):[12] 郑立允,熊惟皓.金属陶瓷表面处理的研究进展[J],机械工程材料,2004,28(9):9.[13] 戴家辉,刘秀忠,陈立博.无铅钎料的立法与发展[J],山东机械,2005,(1):7.[14] 胡志田,何前进,徐道荣.无铅软钎料国内外的研究动态与发展趋势[J],焊接技术,200534(3):4[15] 李明雨,冯武锋,王春青.无焊剂钎焊技术的最新发展现状[J],焊接,1998,(2):2.[16] Lug scherder E,Zhuang H,et al.Alloy,in Parti cular a S ol derAl loy,Met hod for Joi ni ng W o rkpieces b y Solderi ng Using t heS ol der Allo y and Use of t he Allo y for S ol deri ng[P].WO97/03789.[17] Lug s cherder E,Zhuang H,et al.Lot legi erungen2Verwend2ung der Lo tlegierung und Verf ahrer zum Verbi nden vonWerkst offen durch L oten[P].DE Pat ent19526822c2. [18] Hil len F,Casti llo P,Ras s A et al.Solder Alloys and S ol de2ri ng Processes for Fl ux2Free S ol deri ng of Diffi cult2to2Wet Ma2 t eri al s[J],Wel ding&Cut ti ng,2000,(8):162.383第2期蒋东铭,黄风义等:用于802.11a系统的5.8GHz0.18μm CMO S全集成低噪声放大器设计8。

CMOS射频集成电路设计-CMOS低噪声射频放大器

而式(5.2.2)中,iu 与噪声电压un 完全不相关。

CMOS低噪声射频放大器 又

根据噪声因子的定义,可写出噪声系数的表达式为 联立式(5.2.2)~式(5.2.5),解得噪声因子为

CMOS低噪声射频放大器 从式(5.2.6)可以看出,它含有三个独立的噪声源,可将它

CMOS低噪声射频放大器

5.4 TH-UWB低噪声放大器设计实例

5.4.1 近年来关于 UWBLNA的研究现状 近年来有文献报道通过电阻反馈和匹配滤波器[14,15]获

得宽的频带而平坦的增益。 分布式放大器用来在 UWB 通 信中实现低功耗工作。关于 UWB 应用的差分 CMOS LNA 也有介绍。在这些文献中,带有管联拓扑结构的 LNA 介绍较 多,原因是这种结构 在增益和噪声控制方面有更好的性能。

CMOS低噪声射频放大器

CMOS低噪声射频放大器

5.1 概述 5.2 低噪声放大器网络的噪声分析 5.3 CMOS低噪声放大器的基本电路 结构和技术指标 5.4 TH-UWB低噪声放大器设计 实例 5.5 本章小结 习题

CMOS低噪声射频放大器

5.1 概述

目前,基于不同的集成电路工艺,低噪声放大器采用的工 艺技术有 GaAsPHEMT、 MESFET、HBT 以及 CMOS技术 等。

而

CMOS低噪声射频放大器 又

CMOS低噪声射频放大器

CMOS低噪声射频放大器

CMOS低噪声射频放大器 于是,MOS晶体管的二端口网络噪声参数为

CMOS低噪声射频放大器

5.3 CMOS低噪声放大器的基本电路结构和技术指标

5.3.1 CMOS低噪声放大器的几种电路结构 1. 输入端并联电阻的共源放大器 输入端并联电阻的共源放大器的电路结构如图5-3所示。 该放大器的输入阻抗为

CMOS低噪声高增益放大器的设计及仿真分析

CMOS低噪声高增益放大器的设计及仿真分析本科学生毕业论文论文题目: CMOS低噪声高增益放大器的设计及仿真分析学院: 电子工程学院年级:专业: 集成电路设计与集成系统姓名:学号:指导教师:摘要运算放大器已经成为模拟电路设计中用途最广、最重要的部分。

运算放大器简称运放被广泛应用于无线电接收机的高频或中频前置放大级和一些高灵敏度电子设备中。

运放在电路中会产生噪声,在一些需要放大微弱信号的情况下,运放自身的噪声对有用信号的干扰可能会很严重,所以设计了一款低噪声系数、高功率增益、工作稳定性强、有足够带宽和较大动态范围的运算放大器电路。

MOS场效应晶体管会在电路中产生噪声,而且随着MOSFET尺寸的减小与信号幅度的降低,电路中低频噪声特性变得越来越重要。

论文首先分析运放电路中主要产生噪声的原因,然后结合基本噪声理论对电路中相应的元器件参数进行分析设计,然后针对电路的各项指标要求再对电路的元器件的参数进行调整。

运放输入级采用PMOS差分输入的结构,可以提高增益,也起到了抑制噪声的目的,输出级也采用共源共栅形式,可进一步抑制噪声。

通过对电路整体的噪声性能分析,优化了电路的噪声特性。

最后电路达到了设计的目标:增益带宽积大于60MHz、输入噪声功率谱密度在10MHz时小于35nV/rtHz、DC增益大于60dB、相位裕度大于45º。

关键词CMOS;运算放大器;低噪声;高增益;带宽IAbstractOperational amplifier (Op amp) is the most important and comprehensive element in CMOS analog integrated circuits. Operational amplifier is widely used in various types of high-frequency or intermediate frequency as a radio receiver pre-amplifier stage or the high sensitivity of electronic devices. MOS field effect transistor (MOSFET) circuit would bring noise under weak signal amplification. Noise interference may be very serious for useful signal in an op amp. Thus, it is very necessary that designing an op amp circuit with low noise, high gain, good stability, sufficient bandwidth and large dynamic range.MOS field effect transistor circuit would bring noise. With the MOSFET sizes decreasing and the signal amplitude decreasing, the low-frequency noise characteristics of the circuit are becoming increasingly important. This paper analyzes mainly noise sources of thee op ampcircuit firstly, then designs the corresponding component parameters of the circuit considering of the basic noise theory, and adjusts the parameters of certain components. The input stage of Op amp used PMOS differential input gain enhances direct telescopic structure to improve gain and suppress noise. The output stage is horizontal+output+stage to further suppress noise. Seen from the whole circuit noise performance,the noise characteristics are optimized. At last the simulated result also indicated that it reached the requirement of design: gain bandwidth product should be larger than 60dB, input noise power spectral density should be lower than 35nV/rtHz, DC gain shoud be higher than 60dB, phase margin should be larger than 45º.Key wordsCMOS; Operational amplifier; Low noise; High gain; BandwidthII目录摘要 ..................................................................... .. (I)Abstract ........................................................... .. (II)第一章绪论 ..................................................................... ................................................... 1 1.1 论文课题的价值及其意义 ..................................................................... ............... 1 1.2 运算放大器的发展过程及现状 ..................................................................... ........ 1 1.3 论文的章节安排 ..................................................................... . (2)第二章运算放大器的性能分析 ..................................................................... .................... 3 2.1 噪声 ..................................................................... .. (3)2.1.1 噪声类型 ..................................................................... .. (3)2.1.1.1 热噪声 ..................................................................... .. (3)2.1.1.2 散弹噪声 ..................................................................... . (4)2.1.1.3 闪烁噪声 ..................................................................... . (5)2.1.1.4 爆裂噪声 ..................................................................... . (5)2.1.2 MOS管中影响较大的噪声源 ....................................................................52.1.2.1 散弹噪声 ..................................................................... . (6)2.1.2.2 闪烁噪声 ..................................................................... . (6)2.1.2.3 沟道热噪声 ..................................................................... (6)2.1.3 噪声系数与计算噪声的基本方法 (7)2.1.3.1噪声系数 ..................................................................... .. (7)2.1.3.2噪声计算方法 ..................................................................... ..................... 7 2.2 开环增益 ..................................................................... .......................................... 8 2.3 开环带宽和增益带宽积 ..................................................................... ................... 8 2.4 输出摆幅 ..................................................................... .......................................... 9 2.5 相位裕度 ............................................................................................................... 9 2.6 DC功耗 ..................................................................... ............................................ 9 2.7 共模输入范围...................................................................... . (9)2.8 运放中各性能指标之间的关系 ..................................................................... ........ 9 2.9 两种常用结构CMOS放大器 ..................................................................... ........ 10 2.9.1 差分结构放大器 ..................................................................... ......................... 10 2.9.2 共源共栅结构放大器 ..................................................................... .. (13)第三章低噪声高增益运算放大器的设计 ..................................................................... ... 15 3.1 电路设计的指标 ..................................................................... ............................. 15 3.2 电路结构的设计 ..................................................................... .. (15)3.2.1 电路结构的确定 ..................................................................... (15)3.2.2 电路的噪声分析 ..................................................................... (17)3.2.3 电路的增益分析 ..................................................................... .................. 18 3.3 电路参数的确定 ..................................................................... ............................. 19 3.4 电路参数的验证 ..................................................................... .. (21)3.4.1 增益指标的验证 ..................................................................... (21)3.4.2 噪声指标的验证 ..................................................................... (22)第四章电路的仿真分析 ..................................................................... .............................. 23 4.1 理论值仿真分析 ..................................................................... .. (23)4.1.1 直流参数仿真 ..................................................................... . (23)4.1.2 交流小信号仿真 ..................................................................... .................. 24 4.2 电路的改进及仿真分析 ..................................................................... .. (25)4.2.1 M1管与M2管宽长比为20/1的仿真结果 (25)4.2.2 M1管与M2管宽长比为30/1的仿真结果 (26)4.2.3 增益提高的总结 ..................................................................... .................. 26 4.3 考虑噪声的仿真分析 ..................................................................... (27)4.3.1 噪声仿真 ..................................................................... (27)4.3.2 直流仿真 ..................................................................... (28)4.3.3 交流分析 ..................................................................... (28)4.3.4 与设计目标的比较 ..................................................................... .. (29)第五章版图的设计 ..................................................................... . (30)结论 ..................................................................... .. (33)参考文献 ..................................................................... . (34)致谢 ..................................................................... .. (36)CMOS低噪声高增益放大器的设计及仿真分析第一章绪论本章内容主要介绍运算放大器的发展过程,现阶段运算放大器的发展状况论文研究的意义与背景及论文的章节安排。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

5.7GHzCMOS 级间匹配低噪声放大器设计邓桂萍,王春华(湖南大学计算机与通信学院,湖南长沙,410082)摘要:提出并设计了一种工作于5.7GHz 的低噪声放大器。

该电路结构利用MOSFET 自身的栅寄生电阻通过简单的LC 网络变换实现输入匹配,级间接入并联电感以加强匹配,并采用跨阻结构实现输出匹配。

用ADS 模拟软件进行分析与优化,模拟过程中选用的器件采用TSMC0.35umCMOS 工艺。

结果表明,所设计的LNA 增益为10.35dB,噪声系数为2.2dB,功耗为16mW,输入反射系数为-10.63 dB,线性度为-4 dBm。

关键词:低噪声放大器,CMOS,输入匹配,输出匹配,噪声系数Design of 5.7GHz CMOS Low Noise AmplifierUsing Inter-stage Matching NetworkDeng Gui-ping, Wang Chun-hua(School of Computer and Communication, Hunan University,Changsha,Hunan,410082)Abstract: A 5.7GHz fully integrated CMOS low noise amplifier (LNA) simulated with TSMC 0.35um standard CMOS technology is presented. The proposed LNA make the parasitic input resistance of a metal-oxide-semiconductor field-effect transistor (MOSFET) converted to 50W by a simple LC network for input matching and use the transimpedance structure for output matching. In order to improve the inter-stage matching,an parallel inductor is introduced.Analyzed and optimized by the ADS software, the following parameters are achieved: the gain is 10.35dB,the noise figure is 2.2dB,the power is 16mW, the input reflection is – 10.63dB,the IIP3 is -4dBm .Keywords: low noise amplifier, CMOS, input matching, output matching, noise figure1引言随着无线的概念被广泛应用和接受,无线通信在社会生活中将扮演越来越重要的角色。

由于对无线通信设备的日益增长需求,无线通信系统将向低成本、低功耗、高度集成方向发展。

低噪声放大器(Low Noise Amplifier ,简称LNA )作为无线接收机中第一个有源电路,它在将接收信号放大过程中起到了非常关键的作用,它的性能将直接影响整个接收机的性能。

LNA 需要有良好的噪声系数,有足够的增益,非常好的线性度,为实现最大功率传输所要求的LNA 输入与天线匹配,良好的隔离度,以及现今移动通信设备所要求的低电压低功耗[1]。

本文设计了一种工作在5.7GHz 的LNA 电路,输入匹配采用简单的LC 网络把MOSFET 的自身寄生电阻转化为50W ,放大电路部分仍采用的是共源共栅级联结构,引入级间并联电感以加强级间匹配,而输出匹配则采用与LC 调谐电路作用相当的跨阻结构[2],但是跨阻结构可以克服级联结构的输出动态范围受到了限制而降低了放大器的线性度的缺陷。

2 电路设计本文所采用的电路原理图如图1所示。

电路采用共源-共栅级联结构,M 1为输入器件,产生与输入电压成正比的小信号漏电流,共栅晶体管M 2用于减小输入与输出之间的相互作用提RF out+V cc供良好的隔离性能并抑制了M 1的Miller 效应。

为实现输入匹配,这里我们采用简单的LC 网络,考虑将栅分布电阻R g 和沟道电阻R ch 转换为50W ,根据图2,我们得到输入阻抗为2222)1()(])1([2C L R C R C C L L j R Zp p p p p p p INw w w w -+--+=(1) 其中,)(12C L L gs g w -=,R R R ch g p +=。

根据输入匹配的条件,输入阻抗的实部为50W ,虚部为零,因此,可以得到w250RRL pp-=(2) )50(502R R R Cp p p pw -=(3)上面两式表明,只要恰当的选择L g 和C p ,MOSFET 的栅寄生电阻即很容易转化为50W 。

在输出匹配方面,为克服级联结构的输出动态范围受到了限制而降低了放大器的线性度的缺陷,采用M 3,R 2,R 3组成的跨阻输出结构。

虽然反馈电阻可能对噪声系数某种程度上的影响,但这并不关键,因为跨阻结构是用在第二级,第一级的增益可使这种影响大大减小。

由图1,我们可以得到输出电阻:W =++=50||||))||(1||(3312131212Z R ZR g Z R R Zd d m d OUT(4) C 1用于将射频与直流隔离,选择适当的电容(如10nF),使其电抗值对于信号频率可忽略不计。

R 4,R 5,M 4组成偏置电路,给M 1提供偏置电压。

M 4与M 1形成电流镜,M 4的宽度相对很小,这里取为M 1宽度的十分之一,从而偏置电路消耗的电流最小。

电阻R 5要取足够的阻值以减小偏置电路的噪声电流;电阻R 4用来调节输入级晶体管M 1的栅源电压和漏极电流以决定静态功耗。

根据g m 的值,由下式可以推出管子的栅源电压V gs : )(V VLW C g t gsox n m -=m a (5)从而得到漏极电流I D:p 1 INp gs 图 2 本文采用的输入匹配结构及其小信号等效RF in)](||))[((2E L V VV V LWW C I sat t gst gsox n D --×=m (6)根据电流镜的比例关系,可以得到R 5上的偏压电流。

由于V gs 已知,从而可以推算出R 4。

由于共源级的负载是共栅极的输入阻抗,而共栅极的输入阻抗是容性的,因此级间电感L a 的引入可使共源级与共栅极之间能够实现更好的耦合,加强级间匹配,因而能够有效的提高功率增益,降低整个系统的噪声系数。

但是,加入级间并联网络加强耦合不能影响放大器的稳定性,因而在确定La 的时候需综合考虑其对功率增益,噪声系数及稳定性的影响。

3 噪声分析对低噪声放大器进行小信号等效电路分析,如图3,在这里我们主要考虑四个主要噪声源。

V ns 为源电阻R s 引起的噪声电压。

V ns 的功率谱密度为:f R kT v s ns D =4 (7) V ng 是由栅阻抗引起的噪声电压,这里的栅阻抗包括栅分布电阻及其他寄生电阻。

在射频电路中,MOS 管一般采用多指结构实现,以降低寄生电阻的影响。

V ng 的功率谱密度为:f R kTv gngD =342(8)其中因子1/3是当栅指单接时栅电阻的分布效应引起的,如果栅指双接,分布效应因子则减小为1/12。

图3 LNA 的噪声分析模型i nd 是沟道噪声电流,是MOS 器件中的主要噪声源,它的功率谱密度为:fgkT i d ndD =024g (9)式中g d0是V ds =0时的源漏间跨导,g 为常数,是MOSFET 的沟道热噪声系数,对长沟道MOSFET ,当V ds =0时为1,在饱和时为2/3。

i ng 是栅极噪声电流,它的功率谱密度为:f g kT i g ngD =d 42(10)式中g C gd gsg225w=,d 是栅噪声系数。

在MOSFET 中,栅极噪声和漏极噪声具有相关性,它们的相关系数定义为:22*i i i i c ndngnd ng ×=(11)对长沟道MOSFET 相关系数c 为0.395j 。

根据二端口噪声理论,LNA 的噪声系数为:gsi i i i i i i i F so n d g o n R g o n d o n g o n s o n s o n total ,,,,,,,,,,,,,,,++++== (12) 根据图3以及式(7)~(12),经过一系列的冗长计算,得LNA 的噪声系数表达式为: F F F F F 43211++++=)1(32221RCR sR Fspgw +×=])()[(5(222220202C R RL R CL RR R g Fp s gg s pg gs sd T ++-+××=wwa d w w 222202003)[(25)(1)(R RRRL CRRRRCL Rg gFs chpchpchspspsm TTd ++-+××´+=wwwa ww wwg)(22022C R R L R Cgs s ps pw w--++++-××´+×=+L RRRRL RRCR g c g Fschpchchspsm TmTw wgd a wwww 20202204[(5||225)(1)(]1)()()()22CR RCL R C R R L L R R R R C gss pps p s g g g s gp s p×--×++-+×www4 仿真结果设计的LNA 采用TSMC0.35umCMOS 工艺,使用ADS 软件对该LNA 进行模拟与分析优化。

图4(a )~(c )给出了噪声系数NF ,输入反射系数S11及增益S21随频率变化的趋势的仿真结果。

除噪声系数,输入反射系数及增益外,线性度也是一个重要的性能指标,这里用IIP3来模拟估计,图4(d )给出了线性度仿真结果。

表1给出了本文提出的LNA 仿真结果与近几年来提出的部分LNA 仿真结果的比较。

(a )噪声系数NF (b )输入反射系数S11(c)增益S21 (d)输入三阶交叉点图4 CMOSLNA的仿真结果表 1 本文提出的LNA结构仿真结果与以前的LNA结构仿真结果比较工艺频率(GHz) 电源电压(V) 增益(dB) 噪声系数(dB) 功耗(mW) IIP3(dBm) S11(dB) 参考文献0.18umCMOS 5.7 1.0 16.4 3.5 3.2 Na -11 [3] 0.25umCMOS 5.2 2 10 3 10 0.3 -30 [4] 0.18umCMOS 5.8 1.0 13.2 2.5 22.2 Na -5.3 [5]0.18umCMOS 5.7 1.8 21.4 4.4 16.2 -18.5 <-7 [6] 0.18umCMOS 5.7 1.8 11.45 3.4 4 Na - 14 [7] 0.25umCMOS 5.2 3 16 2.5 48 -1.5 -12 [8] 0.35umCMOS 5.7 1.4 10.35 2.2 16 -4 -10.63 本文5 结论本文设计了一种可用于无限局域网(WLAN)的LNA电路,输入匹配采用简单的LC网络把MOSFET的自身寄生电阻转化为50W,避免了源极引入电感对整个结构性能的影响,并且详细噪声分析时考虑了栅分布电阻及沟道电阻,更全面地考虑了噪声因素。