ADC0809接口电路

计算机接口与微机原理-第9周-模拟数字转换器ADC0809

模拟数字转换器ADC0809n模/数转换器n模/数转换器的性能参数n模/数转换原理n ADC 0809的内部结构图n ADC 0809的工作方式n ADC 0809芯片的接口电路中山大学信息科学与技术学院陈任数/模和模/数转换v当用计算机来构成数据采集或过程控制等系统时,所要采集的外部信号或被控制对象的参数,往往是温度、压力、流量、声音和位移等连续变化的模拟量。

v计算机只能处理不连续的数字量,即离散的有限值。

v因此,必须用模数转换器即A/D转换器,将模拟信号变成数字量后,才能送入计算机进行处理。

v计算机处理后的结果,也要经过数模转换器即D/A转换器,转换成模拟量后,在示波器上显示结果波形和在记录仪上描记下来,或驱动执行部件,达到控制的目的。

模/数转换器v我们时常需要把模拟信号转化为数字信号, 以便进行数据的存储,处理和传输,如:把电压,电流,光,声音等模拟信号转化为数字信号。

v模/数转换器可以把模拟信号转换为数字信号,也称为ADC(Analog-to-Digital Converter)。

模数转换器ADC模拟信号数字信号模拟信号8位模数转换器ADC8位二进制数X 参考电压: V refv输入模拟信号(如,电压值0~+5V) ,启动模数转换,产生8位二进制数输出。

start模/数转换器原理v实现A/D转换的基本方法有十几种,常用的有计数法,逐次逼近法,双斜积分法和并行转换法。

v逐次逼近式A/D转换具有速度快,分辨率高等优点,且采用这种方法的ADC芯片成本较低,因此在计算机数据采集系统中获得了广泛的应用。

v逐次逼近式A/D转换器的转换原理是建立在逐次逼近的基础上,把输入电压V i和一组从参考电压分层得到的量化电压进行比较,比较从最大的量化电压开始,由粗到细逐次进行,由每次比较的结果来确定相应的位是1还是0。

不断比较和逼近到两者差别小于某一误差范围时即完成了一次转换。

逐次逼近型ADC逐次逼近型ADC 由逐次逼近寄存器SAR ,D/A 转换器,比较器A 和缓冲器等组成。

ADC0809与AT89C51的一种接口方法

ADC0809与AT89C51的一种接口方法一、本文概述本文将详细介绍ADC0809与AT89C51之间的一种接口方法。

ADC0809是一种常用的8位模数转换器,广泛应用于数据采集和处理系统中。

AT89C51则是一款经典的8位微控制器,以其稳定的性能和广泛的应用场景而受到工程师的青睐。

通过合理的接口设计,可以实现ADC0809与AT89C51之间的有效通信,从而实现对模拟信号的精确采集和控制。

本文将详细阐述接口电路的设计原理、连接方式、信号传输过程以及可能遇到的问题和解决方案,旨在为工程师提供一套实用的参考方案,促进ADC0809与AT89C51在各类应用中的高效集成。

二、ADC0809与AT89C51简介ADC0809是一种8位逐次逼近型模拟数字转换器(ADC)。

它可以将连续的模拟信号转换为离散的数字信号,以便于数字系统进行处理。

ADC0809具有8路模拟输入通道,可以独立地选择其中的一路进行模数转换。

转换结束后,转换结果会通过三态输出锁存器输出到数据总线上。

ADC0809还具有转换启动、转换结束以及清零等控制功能,可以通过相应的控制引脚实现。

由于其转换速度快、精度高等特点,ADC0809在嵌入式系统、工业自动化等领域有着广泛的应用。

AT89C51是Atmel公司生产的一种基于8051内核的低功耗、高性能CMOS 8位微控制器。

它采用Atmel公司的高密度、非易失性存储技术生产,与工业标准的80C51指令集和引脚兼容。

AT89C51具有4K字节的可在系统编程(ISP)Flash存储器,这意味着用户可以在不将芯片从系统中取出的情况下,对其进行重新编程。

AT89C51还集成了多种功能强大的外设,如两个16位定时/计数器、一个5向量两级中断结构、一个全双工串行通信口、一个片内振荡器和时钟电路等。

由于其强大的功能和灵活的编程能力,AT89C51在嵌入式系统、智能仪表、工业控制等领域得到了广泛的应用。

将ADC0809与AT89C51进行接口设计,可以实现模拟信号的数字化处理和控制功能。

第五章 5.7节 模拟电路接口技术ADC0809

2、主要性能指标 (1)、分辨率

分辨率反映A/D 转换器对输入微小变化响应的能力,通常用数字输

出最低位(LSB)所对应的模拟输入的电平值表示。n 位A/D 能反应 1/2^n 满量程的模拟输入电平。

由于分辨率直接与转换器的位数有关,所以一般也可简单地用数字

量的位数来表示分辨率,即n 位二进制数,最低位所具有的权值,就 是它的分辨率。

值得注意的是,分辨率与精度是两个不同的概念,不要把两者相混

淆。即使分辨率很高,也可能由于温度漂移、线性度等原因,而使其 精度不够高。

例如,ADC输出为八位二进制数, 输入信号最大值为 5V,其分辨率为: U m 19 .61mV 8

2 1

(2)、转换时间

转换时间是指完成一次A/D 转换所需的时间,即由发出启动转换

/**********(C) ADC0809.C**************/ #include <reg51.h> #include "1602.h" #define uchar unsigned char #define uint unsigned int sbit ADC_START=P2^0; //四个控制引脚的定义 sbit ADC_ALE =P2^1; sbit ADC_EOC =P2^2; sbit ADC_OE =P2^3; sbit D0=P0^0; //八盏灯的定义 sbit D1=P0^1; sbit D2=P0^2; sbit D3=P0^3; sbit D4=P0^4; sbit D5=P0^5; sbit D6=P0^6; sbit D7=P0^7;

AD转换速度: 500K频率:130us 640K频率:100us 分辨率:8位

4、ADC0809接口电路

ADC0809与单片机的接口电路

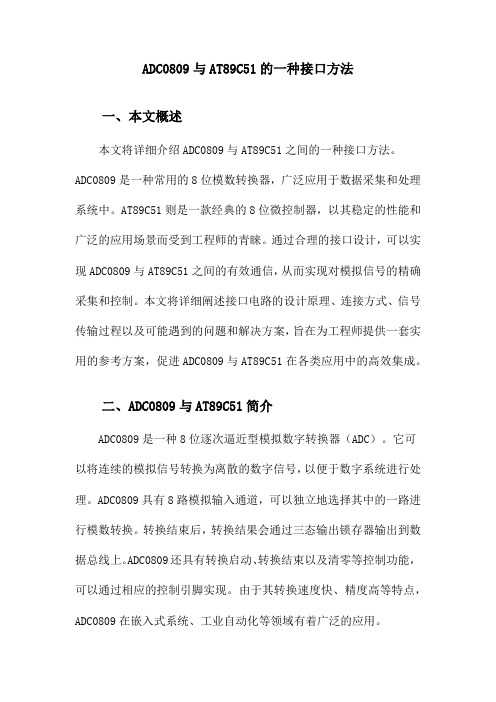

ADC0809是一种CMOS单片型逐次比较式8路模拟输入、8位数字量输出的A/D转换器。

在多点巡回检测和过程控制、运动控制中应用十分广泛。

1.主要特性如下:1)8路8位A/D转换器,即分辨率8位。

2)具有转换起停控制端。

3)转换时间为100μs4)单个+5V电源供电5)模拟输入电压范围0~+5V,不需零点和满刻度校准。

6)工作温度范围为-40~+85摄氏度7)低功耗,约15mW。

2.外部特性(引脚功能)ADC0809芯片有28条引脚,采用双列直插式封装。

下面说明各引脚功能IN0~IN7:8路模拟量输入端。

2-1~2-8:8位数字量输出端。

ADDA、ADDB、ADDC:3位地址输入线,用于选通8路模拟输入中的一路。

ALE:地址锁存允许信号,输入,高电平有效。

START:A/D转换启动信号,输入,高电平有效。

EOC:A/D转换结束信号,输出,当A/D转换结束时,此端输出一个高电平(转换期间一直为低电平)。

OE:数据输出允许信号,输入,高电平有效。

当A/D转换结束时,此端输入一个高电平,才能打开输出三态门,输出数字量。

CLK:时钟脉冲输入端。

要求时钟频率不高于640KHZ。

REF(+)、REF(-):基准电压。

VCC:电源,单一+5V。

GND:地。

ADC0809的工作过程是:首先输入3位地址,并使ALE=1,将地址存入地址锁存器中。

此地址经译码选通8路模拟输入之一到比较器。

START上升沿将逐次逼近寄存器复位。

下降沿启动A/D转换,之后EOC输出信号变低,指示转换正在进行。

直到A/D转换完成,EOC变为高电平,指示A/D转换结束,结果数据已存入锁存器,这个信号可用作中断申请。

当OE输入高电平时,输出三态门打开,转换结果的数字量输出到数据总线上。

单片机与ADC0809的接口电路图。

ADC0809引脚图与接口电路

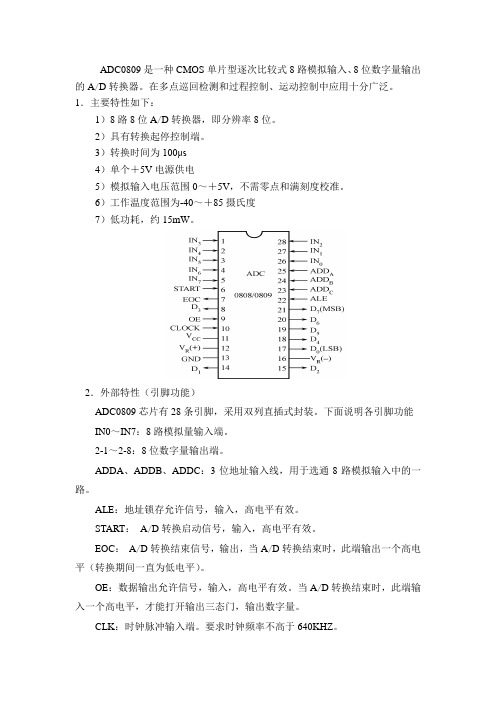

ADC0809引脚图与接口电路A/D转换器芯片ADC0809简介 8路模拟信号的分时采集,片内有8路模拟选通开关,以及相应的通道抵制锁存用译码电路,其转换时间为100μs左右。

图9.8 《ADC0809引脚图》1. ADC0809的内部结构ADC0809的内部逻辑结构图如图9-7所示。

图9.7 《ADC0809内部逻辑结构》图中多路开关可选通8个模拟通道,允许8路模拟量分时输入,共用一个A/D转换器进行转换,这是一种经济的多路数据采集方法。

地址锁存与译码电路完成对A、B、C 3个地址位进行锁存和译码,其译码输出用于通道选择,其转换结果通过三态输出锁存器存放、输出,因此可以直接与系统数据总线相连,表9-1为通道选择表。

表9-1 通道选择表2.信号引脚ADC0809芯片为28引脚为双列直插式封装,其引脚排列见图9.8。

对ADC0809主要信号引脚的功能说明如下:IN7~IN0——模拟量输入通道ALE——地址锁存允许信号。

对应ALE上跳沿,A、B、C地址状态送入地址锁存器中。

START——转换启动信号。

START上升沿时,复位ADC0809;START下降沿时启动芯片,开始进行A/D转换;在A/D转换期间,START应保持低电平。

本信号有时简写为ST.A、B、C——地址线。

通道端口选择线,A为低地址,C为高地址,引脚图中为ADDA,ADDB和ADDC。

其地址状态与通道对应关系见表9-1。

CLK——时钟信号。

ADC0809的内部没有时钟电路,所需时钟信号由外界提供,因此有时钟信号引脚。

通常使用频率为500KHz的时钟信号EOC——转换结束信号。

EOC=0,正在进行转换;EOC=1,转换结束。

使用中该状态信号即可作为查询的状态标志,又可作为中断请求信号使用。

D7~D0——数据输出线。

为三态缓冲输出形式,可以和单片机的数据线直接相连。

D0为最低位,D7为最高OE——输出允许信号。

用于控制三态输出锁存器向单片机输出转换得到的数据。

FPGA与ADC0809接口电路详解

FPGA与ADC0809接口电路详解注:(1)本程序基于FPGA和vhdl编写有详尽的程序解释和原理分析以及原理图,状态图(2)对于adc0809具体资料可上网查在此不累述一.FPGA与ADC0809的接口电路图原理二.关于ADC0809的说明(重点)(1)ale信号(引脚):高电平时把三个地址信号送入地址锁存器,并经译码器得到地址数据,以选择相应的模拟输入通道。

(2)oe信号(引脚)en使能信号:电平由低变高时,打开数据输出锁存器,将转换数据送到数据总线上(3)eoc信号(引脚):eoc为高电平时完成转换,为低电平时正在转换。

(4)start信号(引脚):要给start线送一个100ns宽的启动正脉冲,start下跳沿时,开始进行A/D转换,在转换期间start以保持低电平。

三.转换状态图对于状态图的真值表未列出 注意对应的注释为vhdl 语句ale<='1';start<='0';en<='0';----eoc='1' ale<='0';start<='0';en<='0';--再次检测数据是否转换完 if eoc='0' then next_state<=st4;else next_state<=st5;器,将数据送入数据总线存器四.ADC0809采样接口电路程序--*********ADC0809采样控制*************--******因为FPGA 的时钟频率为50MHz ,则256分频后,即ADC0809输入时钟为195KHz****** --******对ADC0809进行简单的采样控制,得到的数据进FPGA 送到8个并排的数码管显示***** library ieee;use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; use ieee.std_logic_arith.all; entity PL_AD isport ( d : in std_logic_vector(7 downto 0); --ADC0809输出的采样数据输入FPGA clk,eoc: in std_logic; --clk 为系统时钟,eoc 为ADC0809转换结束信号输入FPGA lock1,start, ale,en: out std_logic; --ADC0809控制信号FPGA 输出信号 abc_in :in std_logic_vector(2 downto 0); --模拟选通信号abc_out :std_logic_vector(2 downto 0);--ADC0809模拟信号选通信号q : out std_logic_vector(7 downto 0));送至8个并排数码管信号FPGA 输出数字信号 end pl_AD;architecture behav of PL_AD istype states is ( st0,st1, st2, st3, st4,st5,st6);--定义状态类型枚举类型signal current_state, next_state:states:=st0;--定义总体两个状态现态和次态并且初值为st0态signal regl :std_logic_vector(7 downto 0);--定义中间寄存器signal lock : std_logic;signal qq:std_logic_vector(7 downto 0);--定义计数器用于分频begincom:process(current_state,eoc) –此进程主要是驱动ADC0809工作即数据转换过程begincase current_state iswhen st0=>next_state<=st1;ale<='0';start<='0';en<='0';--准备when st1=>next_state<=st2;ale<='1';start<='0';en<='0';--三个地址信号送入地址锁存器when st2=>next_state<=st3;ale<='0';start<='1';en<='0';--开始数据转换when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完if eoc='1' then next_state<=st3;else next_state<=st4;end if;when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完if eoc='0' then next_state<=st4;else next_state<=st5;end if;when st5=>next_state<=st6;ale<='0';start<='0';en<='1'; --打开输出数据锁存器,将数据送入数据总线when st6=>next_state<=st0;ale<='0';start<='0';en<='1';regl<=d;--打开输出数据锁存器,将数据送入寄存器regl when others=> next_state<=st0;ale<='0';start<='0';en<='0';end case;end process;clock:process(clk) --对系统时钟进行分频,得到驱动ADC0809的时钟信号beginif clk'event and clk='1' then qq<=qq+1;if QQ="01111111" THEN lock<='1';--实现分频current_state <=next_state;--在lock上升沿,转换至下一状态elsif qq<="01111111" then lock<='0';end if;end if;end process;q<=regl;--寄存器数据输出即FPGA输出lock1<=lock;abc_out<=abc_in;--模拟选通信号送往ADC0809end behav;注:有错when st3=> ale<='0';start<='0';en<='0';--检测数据是否转换完if eoc='1' then next_state<=st3;else next_state<=st4;end if;when st4=> ale<='0';start<='0';en<='0';--再次检测数据是否转换完if eoc='0' then next_state<=st4;else next_state<=st5;end if;不过我这里的注释好像错了,这两个when合起来才是检测数据是否转换完的。

常用ADDA芯片的使用:并行ADC0809、串行ADC0832、串行PCF8591

⑶ 延时等待方式

工作在延时等待方式时,0809 EOC端可不必与80C51相连 端可不必与80C51相连, 工作在延时等待方式时,0809 EOC端可不必与80C51相连,是根 据时钟频率计算出A/D转换时间,略微延长后直接读A/D转换值。 A/D转换时间 A/D转换值 据时钟频率计算出A/D转换时间,略微延长后直接读A/D转换值。 14】 20中 EOC端开路 fosc=6MHz, 端开路, 【例9-14】 图9-20中,0809 EOC端开路,fosc=6MHz,试用延 时等待方式编制程序, 路模拟信号依次A/D转换一次, A/D转换一次 时等待方式编制程序,对8路模拟信号依次A/D转换一次,并把 结果存入以50H为首址的内RAM 50H为首址的内RAM中 结果存入以50H为首址的内RAM中。 编程如下: 解:编程如下:

ORG LJMP ORG LJMP ORG STAT: MOV MOV SETB SETB SETB MOV MOVX LJMP 0000H STAT 0013H PINT1 0100H R1,#30H R7,#8 IT1 EX1 EA DPTR,#0FEF8H @DPTR,A MAIN ;复位地址 ;转初始化程序 ;中断服务子程序入口地址 中断,转中断服务子程序; ;中断,转中断服务子程序; ;初始化程序首地址 ;置数据区首址 ;置通道数 ;置边沿触发方式 ;开中 ;CPU开中 ;CPU开中 0809通道 通道0 ;置0809通道0地址 启动0通道A/D ;启动0通道A/D 转主程序,并等待A/D A/D中断 ;转主程序,并等待A/D中断

⑵ 查询方式

工作在查询方式时,0809 EOC端可不必通过反相器与或相连 端可不必通过反相器与或相连, 工作在查询方式时,0809 EOC端可不必通过反相器与或相连, 直接与80C51 P1口或P3口中任一端线相连 口或P3口中任一端线相连。 直接与80C51 P1口或P3口中任一端线相连。 13】 20中 P1.0直接与 直接与0809 EOC端相连 端相连, 【例9-13】 图9-20中,用P1.0直接与0809 EOC端相连,试用查 询方式编制程序, 路模拟信号依次A/D转换一次, A/D转换一次 询方式编制程序,对8路模拟信号依次A/D转换一次,并把结果 存入以40H为首址的内RAM 40H为首址的内RAM中 存入以40H为首址的内RAM中。 解:

实验四 ADC0809的采样控制电路实现

实验四 ADC0809的采样控制电路实现一、实验目的1、学习和理解状态机的设计和工作原理。

2、学习用状态机对A/D转换器ADC0809的采样控制电路的实现。

二、实验仪器PC机,操作系统为Windows2000/XP,本课程所用系统均为WindowsXP(下同),Quartus II 5.1设计平台,GW48系列SOPC/EDA实验开发系统。

三、实验原理ADC0809是CMOS的8位A/D转换器,片内有8路模拟开关,可控制8个模拟量中的一个进入转换器中。

ADC0809的分辨率为8位,转换时间约100us,含锁存控制的8路多路开关,输出有三态缓冲器控制,单5V电源供电。

主要控制信号说明:如图4-1所示,START是转换启动信号,高电平有效;ALE是3位通道选择地址(ADDC、ADDB、ADDA)信号的锁存信号。

当模拟量送至某一输入端(如IN1或IN2等),由3位地址信号选择,而地址信号由ALE锁存;EOC是转换情况状态信号(类似于AD574的STATUS),当启动转换约100us后,EOC产生一个负脉冲,以示转换结束;在EOC的上升沿后,若使输出使能信号OE为高电平,则控制打开三态缓冲器,把转换好的8位数据结果输至数据总线。

至此ADC0809的一次转换结束了。

图4-1 波形仿真图四、实验步骤1、利用Quartus II 5.1对附录4-1的程序进行文本编辑输入和仿真测试;给出仿真波形。

最后进行引脚锁定并进行测试,硬件验证附录4-1电路对ADC0809的控制功能。

2、测试步骤:根据图4-2,建议引脚锁定为:START接PIO34,OE接PIO35,EOC接PIO8,ALE接PIO33,状态机时钟CLK接clock0(PIN2,可选“65536Hz”或更高),ADDA接PIO32(ADDB和ADDC都接GND),ADC0809的8位输出数据线接PIO23~PIO16,锁存输出Q显示于数码8/数码7(PIO47~PIO40),具体查EDA/SOPC技术实验讲义附录第三节(P55)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

8位A/D转换器芯片ADC0809

ADC0809是CMOS单片型逐次逼近式A/D转换器,ADC0809的主要特性:

● 它是具有8路模拟量输入、8位数字量输出功能的A/D转换器。

● 转换时间为100μs。

● 模拟输入电压范围为0V~+5V,不需零点和满刻度校准。

● 低功耗,约15mW。

(1)ADC0809结构框图及引脚说明

图4.24 ADC0809的结构框图和引脚

通道选择开关

通道地址锁存和译码

逐次逼近A/D转换器

8位锁存器和三态门

(2)ADC0809的工作过程

对ADC0809的控制过程是:

① 首先确定ADDA、ADDB、ADDC三位地址,决定选择哪一路模拟信号;

② 使ALE端接受一正脉冲信号,使该路模拟信号经选择开关到达比较器的输入端;

③ 使START端接受一正脉冲信号,START的上升沿将逐次逼近寄存器复位,下降沿启动A/D转换;

④ EOC输出信号变低,指示转换正在进行。

⑤ A/D转换结束,EOC变为高电平,指示A/D转换结束。

此时,数据已保存到8位三态输出锁存器中。

此时CPU就可以通过使OE信号为高电平,打开ADC0809三态输出,由ADC0809输出的数字量传送到CPU。

(3)CPU读取A/D转换器数据的方法

① 查询法

优点:接口电路设计简单。

缺点:A/D转换期间独占CPU,致使CPU运行效率降低。

② 定时法:

优点:接口电路设计比查询法简单,不必读取EOC的状态。

缺点:A/D转换期间独占CPU,致使CPU运行效率降低;另外还必须知道A/D转换器的转换时间。

CPU读取A/D转换器数据的方法

③ 中断法

优点:A/D转换期间CPU可以处理其它的程序,提高CPU的运行效率。

图4.25 ADC0809接口电路

缺点:接口电路复杂。

(4)ADC0809接口电路

图 4. 25 ADC0809接口电路

[例4.1]利用图4.25,采用无条件传送方式,编写一段轮流从IN0~IN7采集8路模拟信号,并把采集到的数字量存入0100H开始的8个单元内的程序。

程序如下:

MOV DI, 0100H;设置存放数据的首址

MOV BL,08H;采集8次计数器

MOV AH,00H;选0通道

AA1∶MOV AL,AH

MOV DX,ADPORT;设置ADC0809芯片地址

OUT DX,AL;使ALE、START有效,选择模拟通道,见图10.18

MOV CX, 0050H

WAIT∶LOOP WAIT;延时,等待A/D转换

IN AL,DX;使OUTPUTENABLE有效,输入数据,见图10.18

MOV[DI],AL;保存数据

INC AH;换下一个模拟通道

INC DI;修改数据区指针

DEC BL

JNZ AA1

更多datasheet搜索: 。