大师教你如何制作一个简单的16位CPU

16位CPU综合设计 计算机组成原理课程设计

16位CPU综合设计计算机组成原理课程设计西安科技大学高新学院计算机组成原理课程设计题目16位CPU综合设计专业及班级计算机科学与技术06级组长卢燕妮成员赵雯、徐静蕾、刘佳、王大伟、焦彤指导教师温乃宁日期 2009年1月目录1 教学目的、任务与实验设备 (1)1.1 学习目的 (1)1.2 学习任务 (1)2 CPU指令系统的设计 (1)2.1 指令格式 (1)2.2 寻址方式 (2)2.3 指令类型 (4)3 运算器的设计 (8)3.1 SN74181概述 (8)3.2 ALU的组成 (10)4 数据通路结构的建立 (11)4.1 部件设置 (12)4.2 总线与数据通路结构 (12)4.3 各类信息的传送路径 (12)4.4 微命令的设置 (14)5 组合逻辑控制器的设计 (15)5.1 功能描述和结构 (15)5.2 输入和输出端口定义 (15)5.3 指令译码器 (16)5.4 时序发生器 (20)5.5 编码器 (21)5.6 微操作信号发生器 (24)6 下载调试和验证 (24)6.1 实验接线 (24)6.2 连接实验线路,仔细查线无误后接通电源。

(25)6.3 写微程序和程序 (25)6.4 运行程序 (28)7 设计总结及体会 (29)8 参考文献 (29)1 教学目的、任务与实验设备1.1 学习目的从计算机的基本概念、基本组成及基本功能着手,对计算机的各个基本组成部件及控制单元的工作原理进行学习,掌握有关软、硬件的基本知识,尤其是各基本组成部件有机连接构成整机系统的方法,为培养自身对计算机系统的分析、设计、开发和使用能力打下基础。

通过本门课程的学习,能在自己的脑中建立计算机的整机概念。

1.2 学习任务掌握数字化信息编码及运算方法,运算器的逻辑构成;熟悉半导体存储器、磁表面存储器基本原理,掌握存储体系构成;掌握寻址和指令系统;熟悉中央处理器组成、时序控制方法,掌握控制器设计技术;熟悉系统总线和I/O系统。

计算机组成原理课程设计报告16位模型机的设计

石家庄经济学院华信学院计算机组成原理课程设计报告计算数据块中所有数据的累加和并存储到内存单元中题目16位模型机的设计姓名学号4114170801班号一班指导老师成绩2014年1月目录一、引言 (3)1.1设计目的 (3)1.2设计任务 (3)二、详细设计及实现 (4)2.1 拟定指令系统 (4)2.2指令格式 (5)2.3寻址方式 (5)三、16位CPU的模型 (7)3.1 各功能部件的VHDL设计 (9)3.2 16位模型机的设计与实现 (22)四、总结 (27)五、参考文献: (27)六、代码 (28)一、引言1.1设计目的为掌握并巩固本学期所学习的计算机组成原理知识,设计本次试验。

运用整合所学的相关知识,一步步设计构造一台基本的模型计算机,明确计算机的控制原理与控制过程,巩固和灵活应用所学的理论知识,掌握计算机组成的一般设计方法,提高学生设计能力和实践操作技能,为从事计算机研制与设计打下基础。

1.2设计任务本机功能:计算数据块中所有数据的累加和并存储到内存单元中。

汇编代码如下:START:MOV SI, OFFSET SRC1 ;源操作数地址送SIMOV DI,OFFSET DXT ;目的操作数地址送DIMOV BX,OFFSET SRC2 ;结束地址送BXMOV BL 0 ;设置BL中初值为0NEXT:MOV AL,[SI] ;取数ADD BL , AL ; 数据相加MOV [DI],AL ;存数CMP SI, BX ;JE START ;如果SI=BX,则转向STARTINC SI ;修改源地址JMP NEXT ;转向NEXT二、详细设计及实现2.1 拟定指令系统分析:1)依据汇编语言程序得出部件间的数据流的方向为●立即数→寄存器●寄存器↔内存内存操作数采用寄存器间址寻址方式●源与目的寄存器内容比较,如果源等于目的转移,转向地址在指令中提供●寄存器加1指令●无条件转移指令,转向地址在指令中提供。

一个16位RISC CPU设计

二.主要模块设计首先给出了系统的总体结构图如图1:图1. 16位RISC CPU结构简图图1中,与外围器件相连的线均为粗体表示。

同时按照要求,设计了MEM 用于存放数据和指令,按照便于程序执行的原则,外围设计及连接示意如图2所示:图2. CPU 外部电路及连接关系图在设计的部件中,针对不同功能的实现,采取了比较繁琐的射击方式。

在MEMORY之外存在几大设计部件。

主要部件设计如下:一.状态控制机:contr_enaclk1Inc_pc Data_enaaux1aux2rd Into_pc Load_pc Load_reg Load_irZero Counter_ena halt wr这是最关键的部件,而且,在选定8个状态为一个运行周期的格局以后,对所有指令包括HAL T 全部在用统一的指令周期。

这不可避免的导致了单元和面积的增加。

此处存在较大的改进余地。

指令分为五部分:取指,译码,执行,存储器访问,结果写回。

最后一部分很有可能进行第二次寄存器读写。

指令运行周期:(八个时钟周期) 第一周期:取指令 第二周期:指令译码 第三周期:空第四周期:地址线跳转,需要运算的数据送到数据线。

第五周期:ALU 时钟信号,ALU 运算。

第六周期:根据情况,对不同指令,分别进行数据的寄存器读写。

第七周期:对于需要再次读写寄存器的操作,如跳转指令中的地址写回寄存器,完成存储。

第八周期:FETCH信号,指令跳转到下面要运行得指令地址,包括正常PC+1和指令跳转地址,为下条指令取指做准备。

控制信号说明:输入信号:Op_code[4:0]:操作数,输入现在是什么指令。

Clk1:时钟信号,大多数的控制信号需要时钟信号的上跳沿触发。

Contro_ena:由控制机产生的信号,控制机复位。

Zero : 由ALU送来,用于条件转移指令(BZ,BNZ)的辅助信号。

输出信号:(十二个控制信号)Halt:为“1”停机信号。

Wr:为“1”写存储器。

组成原理课程设计(16位全加器电路的设计与实现)

16位全加器电路的设计与实现学生姓名:杨传福指导老师:王新摘要本课程设计主要利用门电路完成一个16位的全加器电路的设计与实现。

本设计采用逐步求解的方法,即先设计一位全加器,再利用一位全加器设计出四位全加器,最后在四位全加器的基础上设计出16位全加器,并使用VHDL语言编写程序,在MAX-PLUSⅡ仿真平台上进行仿真。

仿真结果表明,本课程设计中设计出的16位全加器能正确完成16位二进制数的加法运算。

关键词全加器;门电路;先行进位Abstract:This curriculum design primarily use the gate circuit to complete a 16-bit full-adder circuit.The design solve this problem with step-by-step approach, namely start designing one full-adder, and then use one full-adder design a four full-adder , the last design the 16-bit full-adder based on the four full-adder,and use VHDL language programming, at MAX-PLUS Ⅱsimulation on simulation platform. The simulation results show that the design of the curriculum design of the 16-bit full-adder to add a 16-bit binary number addition operations.Keywords:Full-adder; Gate circuit; First binary1引言1.1课程设计的背景随着计算机科学技术的发展,人们获得信息的途径更加多样,获取信息的速度更加快捷。

CPU完整制造流程(带图)

作为计算机的核心组件,CPU(Central Processor Unit,中央处理器)在用户的心中一直是十分神秘的:在多数用户的心目中,它都只是一个名词缩写,他们甚至连它的全写都拚不出来;在一些硬件高手的眼里,CPU也至多是一块十余平方厘米,有很多脚的块块儿,而CPU的核心部分甚至只有不到一平方厘米大。

他们知道这块不到一平方厘米大的玩意儿是用多少微米工艺制成的,知道它集成了几亿几千万晶体管,但鲜有了解CPU的制造流程者。

今天,就让我们来详细的了解一下,CPU是怎样练成的。

基本材料多数人都知道,现代的CPU是使用硅材料制成的。

硅是一种非金属元素,从化学的角度来看,由于它处于元素周期表中金属元素区与非金属元素区的交界处,所以具有半导体的性质,适合于制造各种微小的晶体管,是目前最适宜于制造现代大规模集成电路的材料之一。

从某种意义上说,沙滩上的沙子的主要成分也是硅(二氧化硅),而生产CPU 所使用的硅材料,实际上就是从沙子里面提取出来的。

当然,CPU的制造过程中还要使用到一些其它的材料,这也就是为什么我们不会看到Intel或者AMD只是把成吨的沙子拉往他们的制造厂。

同时,制造CPU 对硅材料的纯度要求极高,虽然来源于廉价的沙子,但是由于材料提纯工艺的复杂,我们还是无法将一百克高纯硅和一吨沙子的价格相提并论。

制造CPU的另一种基本材料是金属。

金属被用于制造CPU内部连接各个元件的电路。

铝是常用的金属材料之一,因为它廉价,而且性能不差。

而现今主流的CPU大都使用了铜来代替铝,因为铝的电迁移性太大,已经无法满足当前飞速发展的CPU制造工艺的需要。

所谓电迁移,是指金属的个别原子在特定条件下(例如高电压)从原有的地方迁出。

很显然,如果不断有原子从连接元件的金属微电路上迁出,电路很快就会变得千疮百孔,直到断路。

这也就是为什么超频者尝试对Northwood Pentium 4的电压进行大幅度提升时,这块悲命的CPU 经常在“突发性Northwood死亡综合症(Sudden Northwood Death Syndrome,SNDS)”中休克甚至牺牲的原因。

EDA创新性实验项目——16位CPU设计

EDA创新性实验项目——16位CPU设计一、项目背景随着计算机科学和技术的不断发展,人们对计算机处理速度和性能的需求也在不断增加。

在这种背景下,为了满足人们对计算速度和性能的需求,研究者们开始将目光投向了新型的CPU设计。

传统的CPU设计多为32位或64位,但这种设计可能会带来一些不必要的复杂性和成本。

因此,设计一种16位CPU成为了当前研究的热点之一二、项目目标本实验项目旨在设计一款16位CPU,以满足轻量级计算需求,并保证其性能和效率。

通过设计一款16位CPU,可以降低处理器的成本和复杂度,提高计算性能,并且更好地满足轻量级计算需求。

三、项目内容1.CPU指令设计:设计新的16位CPU指令集,包括运算指令、数据传输指令、分支跳转指令等,以实现更加高效的计算功能。

2.CPU架构设计:设计16位CPU的整体架构,包括寄存器文件、数据通路、控制单元等,确保CPU的稳定性和高效性。

3.性能优化:对设计的CPU进行性能优化,提高其计算速度和响应速度,确保其在轻量级计算中的高效性。

4.性能评估:通过仿真和实验对设计的16位CPU进行性能评估,检验其计算速度和稳定性,以保证其满足设计需求。

四、项目实施步骤1.设计CPU指令集:根据实际需求设计新的16位CPU指令集,包括指令的格式、操作码和功能,保证其具有高效的计算能力。

2.设计CPU架构:设计16位CPU的整体架构,包括寄存器文件、数据通路和控制单元,确保其能够稳定运行和高效计算。

3.性能优化:对设计的CPU进行性能优化,优化数据通路和控制单元的设计,提高CPU的计算速度和响应速度。

4.实验仿真:通过基于EDA工具进行CPU的设计仿真,检验设计的CPU在不同场景下的计算性能和稳定性。

5.性能评估:对设计的CPU进行性能评估,比较其与传统32位CPU 的性能差异,确保16位CPU在轻量级计算中的优越性。

五、项目成果通过本实验项目的实施,设计一款16位CPU并进行性能评估1.设计一款高效、稳定的16位CPU,满足轻量级计算需求。

手把手教你编写一个超级简单的CPU

手把手教你编写一个超级简单的CPUFPGA的处理能力固然强大,但在进行程序化的任务时,用状态机来实现有时就显得不如CPU写程序那么简洁。

在FPGA里面也可以用逻辑来搭出简单的CPU,并固化一小段代码去实现特定的功能。

考虑下最简单的CPU是什么样子呢?最少,需要有读取程序(指令),并执行指令的过程。

指令存放在一块内存当中,CPU每步取一条指令来执行,根据读出的指令内容,内部的状态发生转变——比如寄存器按指令要求进行运算,比如访问外部的端口(或总线)。

指令是一个编码,描述这一步需要做的事情;执行指令的过程就是状态转移的过程。

我实验的这个超简单CPU是这样:上图中,PC是Program Counter,就是程序计数器,选择ROM中程序执行的地址。

opr用来存放当前的指令,它的内容从ROM 中读到。

寄存器还有A寄存器和R0~R7寄存器,用来计算和存放结果,另外还有一个1-bit的“零'标志位zflag,是给条件转移指令用的。

当然,若只是里面的寄存器变来变去,这个CPU就没有实用价值了,所以还有一个输入端口,以及一个输出端口,用来和寄存器A交换数据。

设计指令字长为8-bit,寄存器宽度也为8-bit。

每条指令都是从ROM中读8-bit,可以最多有256种不同的指令,当然指令中能编码立即数,所以指令不会有那么多种。

我给这个CPU设计了14条指令:跳转指令有2条,无条件转移和Z条件转移,转移范围为5-bit相对地址,即-16~+15。

带立即数指令有4条,因为指令才8-bit,立即数只好分配4-bit了。

装入A寄存器的高4位或低4位,以及与A做加减法。

R0~R7寄存器只能与A 寄存器进行copy和比较操作。

影响zflag标志的指令有位测试指令TESTB, 比较指令COMP和加减法指令。

指令空间并没有用完,可以根据需要再补充指令。

用Verilog语言来写这个CPU的状态转移部分:module cpu0(clk, Iaddr, Ibus, PortI, PortO);input clk;output [9:0] Iaddr;input [7:0]Ibus;input [7:0] PortI;output reg [7:0] PortO;reg [9:0] pc;reg [7:0] RA;reg [7:0] Rn[0:7];reg zflag;assign Iaddr=pc;reg [7:0] opr;always @(posedge clk)opr wire [1:0]opc1=opr[7:6];wire [5:0] opx=opr[5:0];wire [1:0]opc2=opr[5:4];wire [3:0] imm4=opr[3:0];wire [2:0]sel=opr[2:0];reg branch;always @(posedge clk) beginpc branch if(~branch) beginif(opc1==2'd3)if(opr[5] | zflag) beginpc branch endendendalways @(posedge clk) beginif(~branch) beginif(opc1==2'd1 &&opc2==2'd0)Rn[sel] endendalways @(posedge clk) beginif(~branch) begincase(opc1)2'd0:beginif(opx==6'd0)RA end2'd1: beginif(opc2==2'd1)RA end2'd2: begincase(opc2)2'd0: RA[7:4] 2'd1: RA[3:0] 2'd2:RA 2'd3: RA endcaseendendcaseendendalways@(posedge clk) beginif(~branch) beginif(opc1==2'd0 && opx==6'd1)PortO endendalways @(posedge clk)beginif(~branch) beginif(opc1==2'd1) begincase(opc2)2'd3: zflag 2'd2: zflag endcaseendif(opc1==2'd2)beginif(opc2[1])zflag endendendendmodule除了指令所描述的寄存器的操作外,还多了一个branch寄存器和条件判断,这是做什么呢?请注意,PC寄存器所指的是下一条要执行的指令地址(默认总是pc 写测试程序了,没有编译器,汇编程序都得自己写呢。

16位实验CPU设计实例介绍

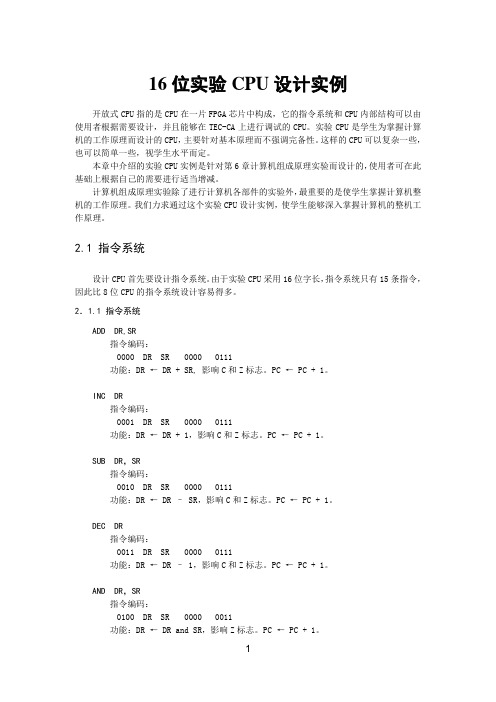

16位实验CPU设计实例开放式CPU指的是CPU在一片FPGA芯片中构成,它的指令系统和CPU内部结构可以由使用者根据需要设计,并且能够在TEC-CA上进行调试的CPU。

实验CPU是学生为掌握计算机的工作原理而设计的CPU,主要针对基本原理而不强调完备性。

这样的CPU可以复杂一些,也可以简单一些,视学生水平而定。

本章中介绍的实验CPU实例是针对第6章计算机组成原理实验而设计的,使用者可在此基础上根据自己的需要进行适当增减。

计算机组成原理实验除了进行计算机各部件的实验外,最重要的是使学生掌握计算机整机的工作原理。

我们力求通过这个实验CPU设计实例,使学生能够深入掌握计算机的整机工作原理。

2.1 指令系统设计CPU首先要设计指令系统。

由于实验CPU采用16位字长,指令系统只有15条指令,因此比8位CPU的指令系统设计容易得多。

2.1.1 指令系统ADD DR,SR指令编码:0000 DR SR 0000 0111功能:DR ← DR + SR, 影响C和Z标志。

PC ← PC + 1。

INC DR指令编码:0001 DR SR 0000 0111功能:DR ← DR + 1,影响C和Z标志。

PC ← PC + 1。

SUB DR,SR指令编码:0010 DR SR 0000 0111功能:DR ← DR – SR,影响C和Z标志。

PC ← PC + 1。

DEC DR指令编码:0011 DR SR 0000 0111功能:DR ← DR – 1,影响C和Z标志。

PC ← PC + 1。

AND DR,SR指令编码:0100 DR SR 0000 0011功能:DR ← DR and SR,影响Z标志。

PC ← PC + 1。

OR DR,SR指令编码:0101 DR SR 0000 0011功能:DR ← DR or SR,影响Z标志。

PC ← PC + 1。

NOT DR指令编码:0110 DR SR 0000 0011功能:DR ← not DR,影响Z标志。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

mv指令将Ry的数据转移到Rx中,mvi将立即数D转移到Rx当中,add将Rx和Ry的和放到Rx中,sub同上,不过执行的是减法。 首 先来说明mv指令是如何执行的:mv指令将Ry的值移入Rx寄存器当中,这两个寄存器都是由一组D触发器构成,而D触发器的个数取决 于寄存器的宽度,就像 32位机、64位机这样,那他们的寄存器使用的D触发器的个数就是不一样的。当执行mv rx,ry时,中间的多路器(图 中最大的那个multiplexer)选通Ry,让Ry寄存器驱动总线,这个时候Bus上的信号就是Ry的值;然后再看到 R0~R7上分别有R0in~R7in信 号,这个信号是使能信号,当这个信号有效时,在上升沿此触发器会将din的数据输入,所以说到这里大家一定想到 了,这个时候Rx触发 器上的Din信号就会变为有效,这样过了一个时钟周期后Ry的值就被送到了Rx当中。 与mv指令类似,mvi指令也将一个数据送入Rx当中,只不过这次的数据存在指令当中,是立即数,所以Rx的Din信号会变为有效,而多路 器会选择IR中的数据,因为mvi指令的立即数存在指令当中。并且进行一定处理,例如扩展等。 add 指令会让多路器先选择Rx,然后Ain信号有效,这样一个时钟周期后,Rx数据被送入Alu的A寄存器当中,这时多路器选择 Ry,addsub信号为 add以指示ALU进行加法操作,Gin有效让G寄存器存放运算结果,然后再过一个时钟周期G当中的数据就是Rx与Ry的 和,这时多路器再选择 Gin,Rx的Din有效,过了一个时钟周期后数据就被存放到Rx当中了。 sub的过程与add差不多,不过addsub信号是sub指示ALU进行减法。 【分页导航】

当然,实际的时钟信号可能远没有这么理想,可能上升沿是斜的,而且占空比也可能不是50%,有抖动,有偏移(相对于两个器件),可 能因为导线的寄生电容效应变得走形。 上面那段如果没听懂也没关系~~~反正就是告诉你,实际的时钟信号测出来肯定没这么标准。 而 cpu的工作频率,是外频与倍频的积(cpu究竟怎么算频率,其实这个我也不太清楚呵呵),因为cpu是通过外部的晶振产生一个时钟信 号,然后再通过内部 的电路(锁相环),倍频至需要的频率。当然,有人问,为什么要这么麻烦呢?直接在电路外边做个时钟晶振能产生 那么高的时钟信号就可以了嘛,这个是可以的, 在某些简单的系统上(例如51单片姬)就是这样的,但是计算姬的cpu比较复杂,因为一 些原因所以必须要做到cpu内。 下面简单说一下CPU的两种指令集:CISC和RISC。 说下我的看法(个人看法,如有错误还请高手指正): RISC是Reduced Instruction Set Computer,精简指令集计算机,典型例子是MIPS处理器。 CISC 是Complex Instruction Set Compute,复杂指令集计算机,典型例子是x86系列处理器(当然现在的x86指令还是当初cisc的指 令,但是实际处理器的结构都已经变成了 risc结构了,risc的结构实现流水线等特性比较容易,在计算机前的你如果用的是intel某系列的 处理器,则它使用的指令集看上去还是像cisc的 指令,但是实际上你的cpu的结构已经是risc的了)。 一般CISC的处理器需要用微指令配合运行,而RISC全部是通过硬连线实现的, 也就是说,当cisc的处理器在执行你的程序前,还得先从另 外一个rom里面读出一些数据来“指导”处理器怎么处理你的命令,所以cisc效率比较低,而 risc是完全通过部件和部件之间的连接实现 某种功能,极大的提高了工作效率,而且为流水线结构的出现提供了基础。cisc的寄存器数量较少,指令能够实 现一些比较特殊的功能, 例如8086的一些寄存器: ax,bx,cx,dx,si,di等;段寄存器有:cs,ds,es,ss等。相对的指令功能比较特殊,例如xlat将bx中的值作为基地址,al中的值作为偏移,在内存 中寻址到的数据送到al当中(以ds为段寄存器) 而risc的处理器则通用寄存器比较多,而指令的功能可以稍微弱一点,例如: 以nios嵌入式处理器来说明,nios处理器有32个通用寄存器(r0~r31),而指令功能相对x86的弱一些,而且x86进行内存访问是直接使 用mov指令,nios处理器读内存用的是load,写内存用的是store, 二 者响应中断的方式也不一样,举一个典型的例子,x86的处理器将中断向量表放在了内存的最低地址(0-1023,每个中断向量占四个字 节),能容纳256 个中断(以实模式的8086举例)响应中断时,将中断号对应的地址上的cs和ip的值装入到cs和ip寄存器而将原来的地址 保存,并且保存状态寄存器然后 进入中断处理,而risc则拥有一个共同的中断响应函数,这个函数会根据中断号找到程序向系统注册的函 数的地址,并且调用这个函数。一般来说而是用的 cisc指令的长度是不定的,例如x86的xor ax,bx对应机器码是0x31d8、而push ax是 0x50、pop cx是0x59。而risc的指令确是定长的,例如】

第1页:CPU是做什么的 第2页:什么是单周期CPU,什么是多周期CPU,什么是RISC,什么是CISC 第3页:一个CPU的基本结构以及必要组件 第4页:重头戏:我做的CPU模型

什么是单周期CPU,什么是多周期CPU,什么是RISC,什么是CISC 首 先大家得有时钟的概念:这个问题不好解释啊。。。。。。可以理解为家里面的机械钟,上上电池之后就会滴答滴答走,而它“滴答滴 答”的速度就是频率,滴答一 下用的时间就是周期,而人的工作,下班,吃饭和学习娱乐都是按照时钟的指示来进行的(熬夜的网瘾少年 不算),一般来说,时钟信号都是由晶体振荡器产生 的,0101交替的信号(低电平和高电平)。 数字电路都需要一个“时钟”来驱动,就像演奏交响乐的时候需要一个指挥家在前面指挥一样,所有的人都会跟着指挥的拍子来演奏,就 像数字电路中所有的部件都会跟着时钟节拍工作一样。 如下是一个理想的时钟信号:(注意是理想的)。

大师教你如何制作一个简单的16位CPU

大师教你如何制作一个简单的16位CPU 上网时间:2016年03月10日

如何制作一个简单的16位CPU,首先我们要明个CPU,首先得明白下计算机的组成结构(或者计算机的替代品,因为并不是只有计算机有CPU,现在的电子产品都很先 进,很多设备例如手机、洗 衣机甚至电视和你家的汽车上面都得装一个CPU),数字电路基础,还最好有点编程的基础(当然,没有也没 关系,这些知识都很容易获得,各种书上面都会提 到,并且在接下来的过程中我会提到这些知识) 我们要实现的是一个RISC指令集的CPU,并且我们最后要自己为这个CPU设计指令并且编码。 首先我们来听个故事,关于CPU的诞生的故事: 日 本客户希望英特尔帮助他们设计和生产八种专用集成电路芯片,用于实现桌面计算器。英特尔的工程师发现这样做有两个很大的问题。 第一,英特尔已经在全力开发 三种内存芯片了,没有人力再设计八种新的芯片。第二,用八种芯片实现计算器,将大大超出预算成本。英 特尔的一个名叫特德?霍夫(Ted Hoff)的工程师仔细分析了日本同行的设计,他发现了一个现象。这八块芯片各实现一种特定的功能。 当用户使用计算器时,这些功能并不是同时都需要的。比 如,如果用户需要计算100个数的和,他会重复地输入一个数,再做一次加法, 一共做100次,最后再打印出来。负责输入、加法和打印的电路并不同时工作。 这样,当一块芯片在工作时,其他芯片可能是空闲的。 霍夫有了一个想法:为什么不能用一块通用的芯片加上程序来实现几块芯片的功能呢?当需要某种功能时,只需要把实现该功能的一段程 序代码(称为子程序)加载到通用芯片上,其功能与专用芯片会完全一样。 经 过几天的思考后,霍夫画出了计算器的新的体系结构图,其中包含4块芯片:一块通用处理器芯片,实现所有的计算和控制功能;一块 可读写内存(RAM)芯片, 用来存放数据;一块只读内存(ROM)芯片,用来存放程序;一块输入输出芯片,实现键入数据和操作命 令、打印结果等等功能。 看完这个故事后,可以总结:CPU是一种用来代替专用集成电路的器件(这只是我的理解,不同人有不同理解,这个就智者见智了,我在 接下来的例子中也会说明我的想法)。 然后考虑如下这个例子: 例1-1: mov eax,0 repeat:inc eax jmp repeat 例1-2: int main() { unsigned int i = 0; while(1) i++; } 例1-3:

第1页:CPU是做什么的 第2页:什么是单周期CPU,什么是多周期CPU,什么是RISC,什么是CISC 第3页:一个CPU的基本结构以及必要组件 第4页:重头戏:我做的CPU模型

一个CPU的基本结构以及必要组件

这 个例子引用自DE2开发板套件带的光盘上的Lab Exercise 9,我们从图中可以看到,一个CPU包含了通用寄存器组R0~R7,一个 ALU(算术逻辑单元),指令寄存器IR,控制器(一般这部分是一个有限状态机或 者是用微指令实现),还有就是数据通路(图中的连 线)。当然真正的CPU不可能只包含这么一点点组件,这是一个模型CPU,也就是说只是说明CPU的原 理,真正复杂的CPU要涉及到很多 复杂的结构和时序,例如虚拟模式需要使用一些特殊的寄存器、为了支持分页需要使用页表寄存器等,为了加速内存的访问需要 使用 TLB,加速数据和指令的访问而使用data cache和instruction cache等等。。。。。当然,那都是后面该考虑的,所以我们先从这个简单 的部分开始讲起。 例子中能实现如下指令: