如何设计最优化的状态机(有图版)

如何设计最优化的状态机

前言:数字电路通常分为组合逻辑电路和时序电路,

组合逻辑电路outputs = F(current inputs)

时序电路outputs = F(current inputs,past inputs)

有限状态机就是时序电路的数学抽象,一个有限状态机系统包括inputs ,outputs, states .状态机分为同步状态机(synchronous)和异步状态机(asynchronous),异步状态机由于输出信号不稳定,所以不详细讨论,对绝大多数设计来说,用的最广泛的是同步状态机。下面主要讨论了同步状态机的设计。

一.状态机的基础知识

1.1. moore状态机和mealy状态机的区别:

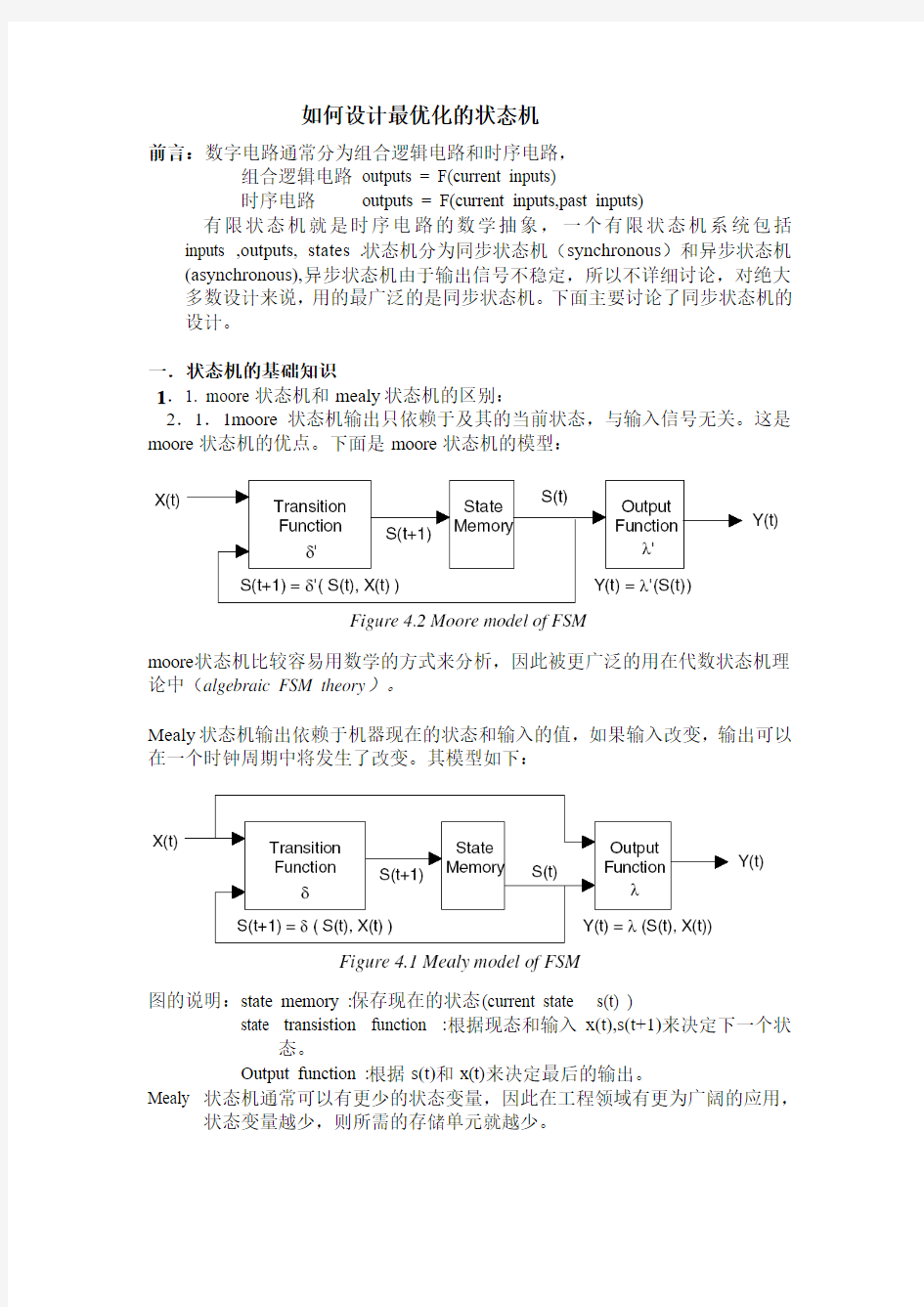

2.1.1moore状态机输出只依赖于及其的当前状态,与输入信号无关。这是moore状态机的优点。下面是moore状态机的模型:

moore状态机比较容易用数学的方式来分析,因此被更广泛的用在代数状态机理论中(algebraic FSM theory)。

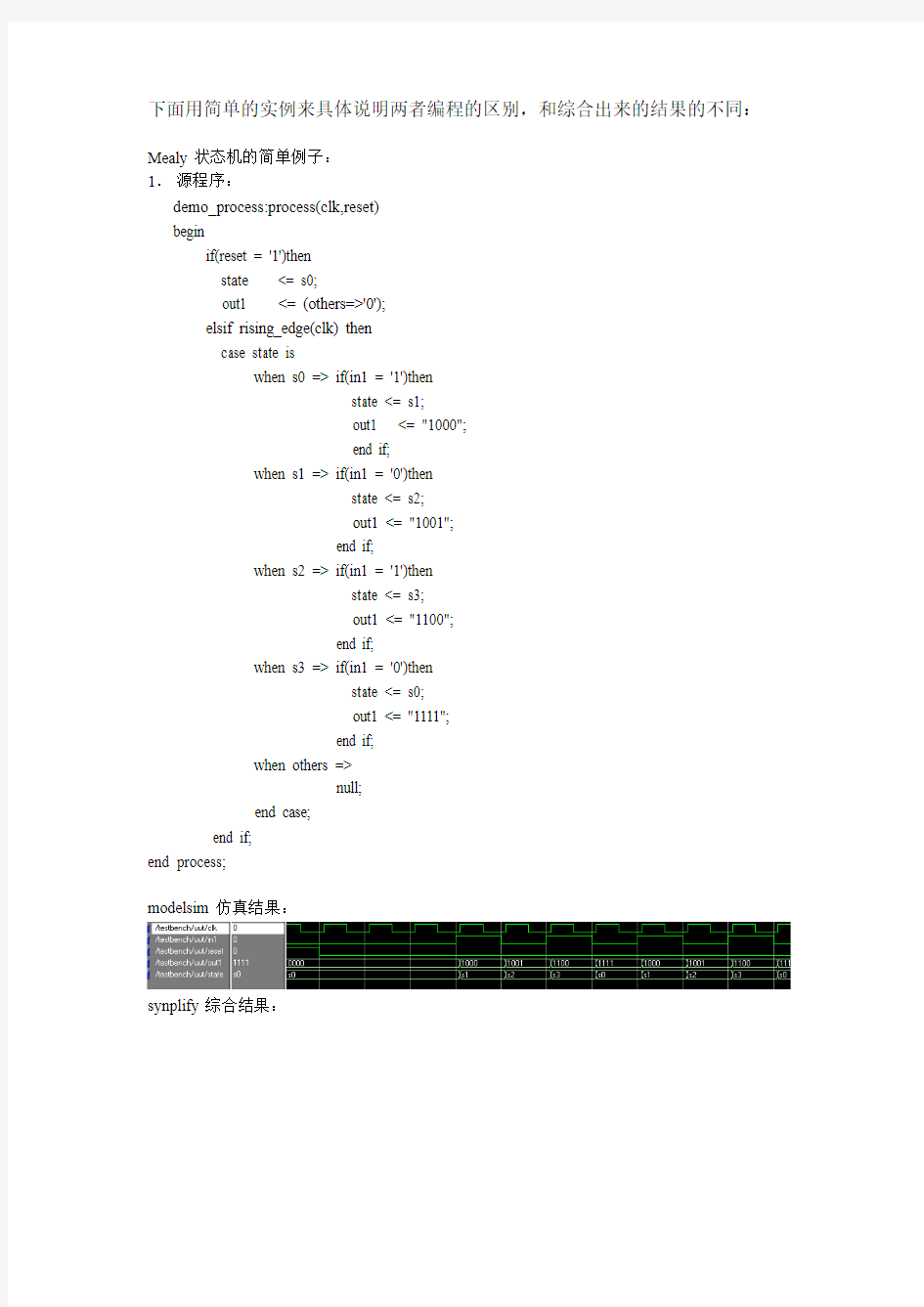

Mealy状态机输出依赖于机器现在的状态和输入的值,如果输入改变,输出可以在一个时钟周期中将发生了改变。其模型如下:

图的说明:state memory :保存现在的状态(current state s(t) )

state transistion function :根据现态和输入x(t),s(t+1)来决定下一个状态。

Output function :根据s(t)和x(t)来决定最后的输出。

Mealy 状态机通常可以有更少的状态变量,因此在工程领域有更为广阔的应用,状态变量越少,则所需的存储单元就越少。

下面用简单的实例来具体说明两者编程的区别,和综合出来的结果的不同:

Mealy状态机的简单例子:

1.源程序:

demo_process:process(clk,reset)

begin

if(reset = '1')then

state <= s0;

out1 <= (others=>'0');

elsif rising_edge(clk) then

case state is

when s0 => if(in1 = '1')then

state <= s1;

out1 <= "1000";

end if;

when s1 => if(in1 = '0')then

state <= s2;

out1 <= "1001";

end if;

when s2 => if(in1 = '1')then

state <= s3;

out1 <= "1100";

end if;

when s3 => if(in1 = '0')then

state <= s0;

out1 <= "1111";

end if;

when others =>

null;

end case;

end if;

end process;

modelsim仿真结果:

synplify综合结果:

1.模块表示图:

在这张综合图上可以明显得看出红线即input所参与决定的是状态的产生和输出。而且输出out1为了防止输出的波形不好(因为通过组合电路输出的波形不稳定),所以加了一个触发器。

2.门级综合结果(仅作参考):

其中状态机模块编码采用两个触发器,见下图:

所以如果在语言中没有对状态进行编码,那么综合器会自动将编码方式设为顺序编码。

Moore状态机的简单例子:

1源程序:

demo_process:process(clk,reset)

begin

if(reset = '1')then

state <= s0;

out1 <= (others=>'0');

elsif rising_edge(clk) then

case state is

when s0 => if(in1 = '1')then

state <= s1;

end if;

out1 <= "1000";

when s1 => if(in1 = '0')then

state <= s2;

end if;

out1 <= "1001";

when s2 => if(in1 = '1')then

state <= s3;

end if;

out1 <= "1100";

when s3 => if(in1 = '0')then

state <= s0;

end if;

out1 <= "1111";

when others =>

null;

end case;

end if;

end process;

2.Modelsim仿真结果:

3.ynplfy综合结果:

1.原理图模块:

从图中可以看出红线即输入仅仅参与决定了状态机产生状态。

2.门级综合结果:(仅作参考)

从以上两种状态机的例子可以看出,同一周期对同样的输入,两种仿真结果一致,只是在综合上有所区别。

1.2 创建状态图或者状态转换表。

设计者通常可以用两种工具来简化状态表的建立过程:状态图和转换表。状态图提供了一种图形化的,易理解的对FSM操作的描述,但限制于相对较小的设计,当设计太复杂而无法创建状态图时,应使用转换表。

2.2.1 创建状态图

状态图应该从复位状态开始,每一个圈表示一个状态,状态图是有向图,圈内部应标上状态的名称和此状态的输出赋值,两个状态之间的转变通过一个有向线段表示,转变条件应标志在有向线段上面,该条件与时钟的上升沿同步。

下面是一个简单的图例:

1.2.2 创建转换表

状态图是帮助理解状态之间关系的有效一种方法,然而对于许多状态的大电路,状态会变得凌乱,极难画出可用的形式。这时,普遍采用一种称作转换表的文本描述方式,创建转换表的方法与状态图相同,不同的是转换列在一个表中。

上图的转换表如下:

注意:在写状态图或者转换表的时候要坚持互斥原则,离开任何节点的线段上的逻辑表达式必须成对互斥,即没有在离开同一节点不同线段上的两个表达式同时为真的情况,如果两个这样的表达式同时是逻辑1,那么状态机就进入了两个不同的次状态,这是不容许的。

互斥测试的是离开同一节点的两个表达式的逻辑and必须为逻辑0。

1.4 状态的编码方式

在vhdl原码中是否对状态机编码作出规定并不影响状态机的功能,综合工具提供状态优化器,他可以在综合过程中确定状态编码。

状态编码主要有5种编码方式:

1.顺序编码。

2.格雷码编码。

3.单热编码(one-hot)。

4.随机编码。

5.自动编码(面积最小化)。

状态机在传统上是按二进制编码的。然而采用Gray编码,相邻状态可减少瞬变的次数。有时不可能在所有状态中使用Gray编码,则应在状态矢量中增加触发器的数量以减少开关的次数。另一种方法是使用one-hot编码,虽然该编码使用的触发器较多,即可减少组合逻辑的使用,在带多个输出且每个输出是几个状态的函数的状态机中更是如此。根据状态机的形式,设计者可在Gray、One-hot或二进制间进行选择。

现在就详细说一下one-hot 状态机:

1.ne-hot编码:s0 = “0001” ; s1 = “0010”; s2 = “0100”; s3 = “1000”;

每一个状态用掉一个触发器,状态数等于触发器的数目。这就意味着触发器数目增加,而状态译码组合电路被优化掉了。对于寄存器资源丰富的xilinx器

件来说,是非常适合的。

2.one-hot 状态机的好处:

现在的FPGA每一个逻辑块中都包含了一个和多个触发器,对于仅需要触发器的one-hot编码解码来说,提供了很好的条件。下面列举了一些用one-hot 设计的

好处:

a)对寄存器资源丰富xilinx fpga 来说更易于适配和布线。

b)one-hot状态机是典型的相当快速的状态机。他的速度与状态的个数没有任何关系,

仅仅决定于状态变迁到一个特殊状态的这种转换的数量(instead depend only on the

number of transitions into a particular state)。

c)不用担心你会在发现最佳的状态机编码方式。因为其他设计的状态机如果在加入一

些状态或者改变其他一些什么的话,那就可能不再最优了。One-hot 编码方式在

所有状态机中是最佳的,最优的。

d)one-hot 状态机很容易设计。状态图能够直接被画成原理图或者被直接用vhdl语言

写出来,而不用编码成状态表。

e)修改起来简单明了。增加和删掉一些状态或者改变一些敏感量等式能被综合器很容

易的执行,而不会影响余下的状态机。

f)很容易从vhdl 或者verilog 综合。

g)比其他一些高性能的状态机没有任何的布线面积的浪费。

h)能够用静态时序分析的方法很容易的找出危险的不合理的状态机转换路径。

3.举例说明:

type STA TE_TYPE is (s0, s1, s2, s3);

attribute ENUM_ENCODING: STRING;

attribute ENUM_ENCODING of STA TE_TYPE: type is "0001 0010 0100 1000"; signal CS, NS: STA TE_TYPE;

begin

-- build the state flops

SYNC_PROC: process (clk, reset)

begin

if (reset='1') then

CS <= s0;

elsif rising_edge(clk) then

CS <= NS;

end if;

end process;

-- state machine

COMB_PROC: process (CS,in1)

begin

case CS is

when s0 =>out1 <= (others=>'0');

if(in1 = '1')then

NS <= s1;

out1 <= "1000";

end if ;

when s1 => if(in1 = '0')then

NS <= s2;

out1 <= "1001";

end if;

when s2 => if(in1 = '1')then

NS <= s3;

out1 <= "1100";

end if;

when s3 => if(in1 = '0')then

NS <= s0;

out1 <= "1111";

end if;

when others =>

null;

end case;

end process;

在s0状态里,有一个细节,out1 <= (others=>'0');这句话在if外面,和在if里面的out1 <= "1000";这句话不会自相矛盾。第一句话是s0状态的输出。而第二句话则是s1状态的输出。

Modelsim仿真结果:

上例输出赋值随着时钟的跳变而赋值,这样在输出时就放了一个触发器。

如果在output中不想加入触发器的话,那么,就可以把输出单独拿出来,输出就直接经过组合逻辑,不经过触发器。

process(cs)

begin

case cs is

when s0 => out1 <= "0000";

when s1 => out1 <= "1000";

when s2 => out1 <= "1001";

when s3 => out1 <= "1100";

when others => null;

end case;

end process;

如果在程序中不对状态进行one-hot编码的话,那么有综合器生成的编码方式只能是顺序编码,或者格雷码,所以尽量在程序中确定编码的格式。

二.状态机的设计步骤:

1.深入的理解问题(Understand the problem)。用非常严谨的风格去解释问题的描述是非常重要的。对于状态机,你必须搞清楚什么样的输入会产生什么样的输出。

2.获得一个对状态机的理论性的描述(Obtain an abstract representation of the FSM)。一旦你理解了问题,你必须用一种易于操作的形式表达出来,状态图是一种比较好的表示方法。

3.对状态机进行优化(Perform state minimization. )。从上一步过来,通常会导致很多状态,很多状态会有相同的行为描述,这些状态应该被优化成同一个状态。

4.进行状态编码的赋值(Perform state assignment)。编码方式好坏决定了执行的速度。

5.选择何种类型的触发器来实现状态机(Choose flip-flop types for implementing the FSM's state),J-K触发器会减少门,但会改变转换表。D触发器是比较简明的实现过程。

6.实现有限状态机(Implement the finite state machine)。

三.具体实例:

为了说明以上的设计步骤,我们设计并综合一个状态机的来控制一个简单的自动售货机。下面是怎样控制自动售货机去工作:

当自动售货机收到15分硬币时,它就送出一包口香糖。售货机只有一个口来接收五分的硬币和一角的硬币,而且每次只能有一个硬币投入。一个机械传感器可以指示出这个口中投入的是五分的或是一角的硬币,控制器的输出控制着单包的口香糖通过出物口送到消费者的手里。

更进一步补充:如果一个顾客送入的是两个一角的硬币,那么他就能找回一个5分的硬币。每次口香糖输出后,状态机就会自动复位。

1.深入理解这个问题

设计状态机的第一步是理解所要设计的问题。于是我们画了一个模块图来理解输入和输出。

N(nickel)表示当一个五分硬币投入硬币投入口中产生的一个脉冲,D(dime)表示当一个一角的硬币投入产生的一个脉冲,open表示机器收到一角五分后产生打开物品输出口。

2.理论上的表达(Abstract Representations)

一旦你理解了这个控制模型,就该设计更加完全具体的理论表达(abstract representation)。列举所有可能的输入和系统的构造,对确定一个有限状态机的各个状态非常有用。

下面为可能的输入:

1.三个五分的硬币顺序投入:

2.先投两个五分的硬币,再投一个一角的硬币:

3.先投一个五分的硬币,再投一个一角的硬币:

4.先投一个一角的硬币,再投一个五分的硬币:

5.顺序投入两个一角的硬币:

描述成状态图如下:

举个例子,如果机器顺序收到三个五分硬币,则状态机将走s0,s1,s3,s7 状态。

为了保持状态图的简单和可读性,我们的状态图中仅仅包括了引起状态改变的转变。例如,对于状态s0,如果N,D都无效,我们就默认状态仍然为s0。同样,我们也只在状态机中包括了输出有效(open)。

3.状态的最简化(State Minimization)

这九个状态并不是最优的状态。譬如,s4,s5,s6,s8这四个状态有着同样的功能,他们应该被组合成单个状态。

为了尽可能的减少状态机的数量,我们可以认为,不管是收到一角硬币,或者是两个五分的硬币,对状态机来说效果都是一样的。

所以状态机可以被描述成下图:

我们用四个状态机就实现了前面所用九个状态机所能完成的过程。作为一个比较有用的简略描述,从状态10¢到15¢.,我们将条件标志成"N, D",表示如果N有效,或者D有效,状态将转换到15¢。

4.状态编码(State Encoding)

通过上面的做法,我们得到了状态机的最小状态数目,但是这仍然是一个符号,下面的图就是一个状态转换表,下一步就是状态编码。

用这种编码状态机方法能够对状态机综合所需要的硬件资源产生较大的影响。状态机自然的被按照以下编码,

转换表如下:

5.实现(Implementation)

在选定好实现的存储单元后,下一步就是如何实现状态转换表了,我们将看到基于D触发器和J-K触发器的实现方式。

下图是设计通过D触发器地K-map来实现的:

我们可以根据状态转换表直接得出下面最简的等式:

用逻辑门来实现的图如下所示:一共用了8个门,和两个触发器。

为了用J-K触发起来实现状态机,我们重新映射专门为J-K触发器而改变状态转换表。

实现如下图所示

k-maps的图如下所示:

根据图示所得到的最优的等式如下

门级电路描述如下:

从图上可以看出,用J-K触发器的方法用了七个门,和两个触发器,适度的减少了硬件的资源。

6.讨论

我们主要通过设计一个简单的自动售货机来描述了一个完全的有限状态机的设计过程

我们采用了状态图的方法。

因为不止一个状态图能得到同样的输入输出功能,找到一个尽可能少的状态的描述方法是非常重要的。这样通常会减少状态机实现的复杂度。例如,这个例子开始时,我们用了9个状态,这样就需要4个触发器,但是通过优化状态,我们将四个触发器减少到两个触发器。

一旦我们得到了一个最优化的状态描述,下一步就是选择一个好的状态编码方式,正确的编码方式能够更深一步的减少下一状态和输出模块所需要的逻辑门。在这个例子中,我们仅仅用了最明显,最简单的状态赋值。

最后一步是选择适合状态寄存器的触发器类型。在这个例子中,基于D触发器的实现方式更为易懂。我们不用重新映射状态转换表,但是我们比基于J-K触发器的实现方式多用了一些门。

7.用mealy 和moore状态机来实现区别:

两者实现的状态图如下图所示:

对于moore状态机,输出赋值在他被声明的状态机里面,输入条件的改变被标志在弧线上,组合逻辑功能能被合理的作为弧线上的标志合理的接受。

对于mealy状态机,输出被放在状态转换弧线上。输入和输出被坚决的分开了,譬如,如果我们在10¢状态,D或者N有效的话,OPEN将会被有效。任何一个N后者D产生的脉冲都会导致口香糖被错误的送出。

四:写状态机需要注意的问题:

设计方案完全取决于设计要求:面积,速度。

1:如果有可能的话,选择output = state 类型状态机是一个理想的方案,因为速度最快,使用的面积最小。

2:在设计状态机时,对于所有的输出信号在每一个时钟周期的取值,都必须作出非常明确的定义。也就是说在每一个状态周期里面,对每一个输出值,在该状态可能的各种情况下,都必须有明确的赋值。否则,综合结果会多很多不必要的门。

这是因为:由于没有在每一个状态周期里面给输出信号赋值,因而需要有硬件来维持原来的输出信号值保持不变。综合工具解决的唯一办法:把输出信号值反馈给多路选择器,当某一时钟周期没有给输出信号赋值时,多路选择器再把这个值送给输出信号,使得输出信号值得以维持不变。

3:注意消除锁存器,看下面的例子

type state_type is (grant0, grant1, idle0, idle1);

signal state, next_state: state_type;

begin

state_diagram: process (state, req0, req1) begin

case state is

when grant0 =>

gnt0 <= '0'; gnt1 <= '1';

if req0 = '1' and req1 = '0' then next_state <= grant1;

elsif (req0 and req1) = '1' then next_state <= idle0;

else next_state <= grant0;

end if;

when grant1 =>

gnt0 <= '1'; gnt1 <= '0';

if req0 = '0' and req1 = '1' then next_state <= grant0;

elsif (req0 and req1) = '1' then next_state <= idle1;

else next_state <= grant1;

end if;

when idle0 =>

gnt0 <= '1'; gnt1 <= '1';

if req1 = '0' then next_state <= grant1;

elsif req0 = '0' and req1 = '1' then next_state <= grant0;

else next_state <= idle0;

end if;

when idle1 =>

gnt0 <= '1'; gnt1 <= '1';

if req0 = '0' then next_state <= grant0;

elsif req0 = '1' and req1 = '0' then next_state <= grant1;

else next_state <= idle1;

end if;

end case;

end process;

人们很可能会忽略case语句每个分支的else子句。也就是说,如果没有提供else子句,那么next_state应该保留它以前的值。它所带来的问题是,为了保持它原来的值,必须产生一个混合锁存器。但这并不是所希望的结果。下面讨论一下其中的原因。假定状态机处于idle0,而信号req1在下一个时钟边缘之前早就变化了,从1到0,然后又回到1。req1从1到0时,执行state_diagram过程,next_state赋值为grant1;当req1变回1时,再次执行该过程,这一次,if和elseif子句为假。由于没有一个else子句规定next_state应该为idle0,因而next_state仍将保持它以前的值,grant1。在下一个时钟的上升沿,状态机将在它不应该变化的时候发生变化。因此,利用描述组合逻辑的过程产生不需要的锁存器时,应该小心。幸运的是,对描述组合逻辑的所有过程来说,它们总是包含一个else子句,能够明确地指出在该过程中被赋值的所有信号的值。

五:附件

参考书目和文章:

1.Vhdl设计电子线路清华大学出版社

2.Vhdl 设计表示和综合机械工业出版社

3.4-FSM.pdf

4. golson_snug94.pdf

5. state machine design consideration and methodologies.pdf

6. state machine.pdf

7. golson_pldcon93.pdf

8. Algorithmic State Machine.pdf

9. Finite State Machine Design 网址:

http://www2.ele.ufes.br/~ailson/digital2/cld/chapter8/chapter08.doc.html

用状态机设计的交通灯控制器

/module traffic (clock, reset, sensor1, sensor2, red1, yellow1, green1, red2, yellow2, green2); input clock, reset, sensor1, sensor2; output red1, yellow1, green1, red2, yellow2, green2; // Define the states. Enumerated type pragma allows Spectrum to chose encoding. parameter /*exemplar enum ee1 */ st0 = 0, st1 = 1, st2 = 2, st3 = 3, st4 = 4, st5 = 5, st6 = 6, st7 = 7; reg [2:0] /* exemplar enum ee1 */ state, nxstate ; reg red1, yellow1, green1, red2, yellow2, green2; // Update the state with the next state on the clock edge // or reset value. always @(posedge clock or posedge reset) begin if (reset) state = st0 ; else state = nxstate; end // // Calculate the next state and the outputs // based on the present state and the inputs // always @(state or sensor1 or sensor2) begin // Default values for the outputs

第14章 状态机设计(state machine design)

第14章 状态机设计(State Machine Design) 讲到VHDL设计而不讲state machine,感觉上就是不太完整,我们先来看看什么是state machine,它应该是一种流程控制的设计,在有限的状态中,根据判别信号的逻辑值决定后面要进入哪一个状态,这样的讲法似乎有些抽象,我们先来看看下面的状态图。 图14-1所显示的是一个十字路口的红绿灯控制设计,在一开始时信号Reset 会被设为逻辑’0’,此时state machine会在Reset状态,一直等到信号Reset变成逻辑’1’时,state machine才会进入真正的控制状态。在之后的三个状态中,我们各定义了一个counter,当进入Red或是之后的Green及Yellow状态时,相对的counter值即会开始递减。当counter值递减到0时,state machine即会改变到下一个状态。 当然state machine的执行就是依照这种方式进行,但是其中仍有许多的细节是设计者所要注意的,在接下来的章节中,我们会依据实际的例子来介绍state machine的设计方式。 14-1State Machine的建立 在这一节我们所举的例子是一个类似检查密码的设计,在一般办公室的门口都会有门禁管制,进门前须先输入一组四个数字的密码,当密码确认无误后门才会打开,除此之外还有更改密码的功用。我们先来看看其状态图。 在图14-2中一共有四个状态,一开始会维持在idle状态,当要更改或是第一次输入密码时,需要按下一个特殊的“密码更改”按键,此时InpinN信号会变成逻辑’0’的状态,状态机即会进入LoadPin的状态,接着再输入四个数字的密码,密码输入完毕按下“输入”按键,状态机即回到原先的idle状态。 在另一方面,当处于平时状态,有人进入门口要输入密码前,他也必需要按下另一个特殊键“密码输入”,表示之后输入的数字是待验证的密码,此时InData 信号会变成逻辑’0’,于是状态机进入InPin的状态。在输入四个数字之后,一个

实验四 有限状态机设计(2学时)

实验四有限状态机设计(2学时) 实验内容一: 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 根据时序电路输出信号的特点可将时序电路划为Mealy 型和Moore 型两种。Moore型电路中,输出信号仅仅取决于存储电路的状态。Mealy型电路中,输出信号不仅取决于存储电路的状态,而且还取决于输入变量。图1是某Mealy型电路的状态转换图,图中圆圈内的S0、S1等代表电路的状态,状态转换箭头旁斜杠“/”上边的数字代表输入信号,斜杠“/”下边的数字代表输出信号。假设电路的当前状态为S0,当输入信号为0时,电路的下一个状态仍为S0,输出信号为0;当输入信号为1时,电路的下一个状态为S1,输出为1。 图1 Mealy状态机 下面的程序中使用两个进程来描述该状态机。第一个进程负责状态转化,在CP上升沿到达时,当前状态(PresetState)向下一个状态(NextState)的转换;第二个进程负责检测输入信号(DIN)和当前状态(PresetState)的值,并由CASE-WHEN 语句决定输出信号(OP)和下一个状态值(NextState)的值。请补充下图中虚线“…”部分省略掉的程序,然后对完整程序进行编译,并用Tools->Netlist Views->State Machine Viewer和RTL Viewer工具查看该状态机的状态图和RTL顶层图。

… … 实验内容二: 论文《基于VHDL的一个简单Mealy状态机》中设计了一个Mealy状态机用来检测数据流“1101010”,用以验证状态机在数据检测上的应用。请在读懂文中程序的基础上,在Quartus Ⅱ软件中通过编译仿真得到状态图和波形图,仿真中输入波形的设置应能体现该状态机的用途。 实验报告: 本次实验占用两个学时,请于12周周四(5月12日)上课时交实验报告。对于实验内容一,报告的内容应重在程序的完善上,对于实验内容二,报告的内容应重在对论文中源程序的分析和理解,以及仿真的波形图上。

如何设计最优化的状态机(有图版)

如何设计最优化的状态机 前言:数字电路通常分为组合逻辑电路和时序电路, 组合逻辑电路outputs = F(current inputs) 时序电路outputs = F(current inputs,past inputs) 有限状态机就是时序电路的数学抽象,一个有限状态机系统包括inputs ,outputs, states .状态机分为同步状态机(synchronous)和异步状态机(asynchronous),异步状态机由于输出信号不稳定,所以不详细讨论,对绝大多数设计来说,用的最广泛的是同步状态机。下面主要讨论了同步状态机的设计。 一.状态机的基础知识 1.1. moore状态机和mealy状态机的区别: 2.1.1moore状态机输出只依赖于及其的当前状态,与输入信号无关。这是moore状态机的优点。下面是moore状态机的模型: moore状态机比较容易用数学的方式来分析,因此被更广泛的用在代数状态机理论中(algebraic FSM theory)。 Mealy状态机输出依赖于机器现在的状态和输入的值,如果输入改变,输出可以在一个时钟周期中将发生了改变。其模型如下: 图的说明:state memory :保存现在的状态(current state s(t) ) state transistion function :根据现态和输入x(t),s(t+1)来决定下一个状态。 Output function :根据s(t)和x(t)来决定最后的输出。 Mealy 状态机通常可以有更少的状态变量,因此在工程领域有更为广阔的应用,状态变量越少,则所需的存储单元就越少。

有限状态机设计

有限状态机设计 实验报告 一.实验题目 有机状态机设计 二.实验目的 掌握有机状态机设计的基本方法。 三.实验远离 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 四.实验内容

实验内容一: 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 根据时序电路输出信号的特点可将时序电路划为Mealy 型和Moore 型两种。Moore型电路中,输出信号仅仅取决于存储电路的状态。Mealy型电路中,输出信号不仅取决于存储电路的状态,而且还取决于输入变量。图1是某Mealy型电路的状态转换图,图中圆圈内的S0、S1等代表电路的状态,状态转换箭头旁斜杠“/”上边的数字代表输入信号,斜杠“/”下边的数字代表输出信号。假设电路的当前状态为S0,当输入信号为0时,电路的下一个状态仍为S0,输出信号为0;当输入信号为1时,电路的下一个状态为S1,输出为1。 图1 Mealy状态机 下面的程序中使用两个进程来描述该状态机。第一个进程负责状态转化,在CP上升沿到达时,当前状态(PresetState)向下一个状态(NextState)的转换;第二个进程负责检测输入信号(DIN)和当前状态(PresetState)的值,并由CASE-WHEN 语句决定输出信号(OP)和下一个状态值(NextState)的值。请补充下图中虚线“…”部分省略掉的程序,然后对完整程序进行编译,并用Tools->Netlist Views->State Machine Viewer和RTL Viewer工具查看该状态机的状态转移图和RTL原理图。

状态机及其VHDL设计

第7章状态机及其VHDL设计 内容提要:有限状态机(Finite State Machine,简称FSM)是一类很重要的时序电路,是许多数字系统的核心部件,也是实时系统设计中的一种数学模型,是一种重要的、易于建立的、应用比较广泛的、以描述控制特性为主的建模方法,它可以应用于从系统分析到设计的所有阶段。有限状态机的优点在于简单易用,状态间的关系清晰直观。建立有限状态机主要有两种方法:“状态转移图”和“状态转移表”。标准状态机通常可分为Moore和Mealy两种类型。本章主要介绍了基于VHDL的常见有限状态机的类型、结构、功能及表达方法,重点是如何有效地设计与实现。 学习要求:了解状态机的基本结构、功能和分类,掌握有限状态机的一般设计思路与方法、状态机编码方案的恰当选取、Moore和Mealy状态机的本质区别及设计实现。 关键词:状态机(State Machine),Moore,Mealy,VHDL设计(VHDL Design) 状态机的基本结构和功能 一般状态机的VHDL设计 状态机的一般组成 状态机的编码方案 摩尔状态机的VHDL设计 米立状态机的VHDL设计 状态机的基本结构和功能 状态机的基本结构如图所示。除了输人信号、输出信号外,状态机还包含一组寄存器记忆状态机的内部状态。状态机寄存器的下一个状态及输出,不仅同输入信号有关,而且还与寄存器的当前状态有关,状态机可以认为是组合逻辑和寄存器逻辑的特殊组合。它包括两个主要部分:即组合逻辑部分和寄存器。组合逻辑部分又可分为状态译码器和输出译码器,状态译码器确定状态机的下一个状态,即确定状态机的激励方程,输出译码器确定状态机的输出,即确定状态机的输出方程。寄存器用于存储状态机的内部状态。 状态机的基本操作有两种: 1.状态机的内部状态转换。 状态机经历一系列状态,下一状态由状态译码器根据当前状态和输入条件决定。2.产生输出信号序列。

利用有限状态机进行时序逻辑的设计

利用有限状态机进行时序逻辑的设计 1. 实验目的: (1)掌握利用有限状态机实现一般时序逻辑分析的方法; (2)掌握用Verilog编写可综合的有限状态机的标准模板; (3)掌握用Verilog编写状态机模块的测试文件的一般方法。 (4)在数字电路中已经学习过通过建立有限状态机来进行数字逻辑的设计,而在VerilogHDL硬件描述语言中,这种设计方法得到进一步的发展。通过Verilog HDL提供的语句,可以直观的设计出更为复杂的时序逻辑的电路。关于有限状态机的设计方法在教材中已经作了较为详细的阐述。 2.实验环境 PC机一台,安装有quartusII13.0软件以及modulsim软件 3.实验内容 设计一个简单的状态机,功能是检测一个5位二进制序列“10010”。考虑到序列重叠的可能。有限状态机共提供8个状态(包括初始状态IDLE). 4.实验步骤 1) 源程序: module seqdet(x,z,clk,rst,state); input x,clk ,rst ;

output z; output [2:0] state ; reg[2:0] state ; wire z; parameter IDLE='d0, A='d1, B='d2, C='d3, D='d4, E='d5, F='d6, G='d7; assign z=(state == E && x==0)?1:0; always @(posedge clk) if(!rst) begin state <= IDLE; end else casex(state) IDLE:if(x==1)

有限状态机设计

实验七有限状态机设计 一、实验目的 1、掌握利用有限状态机实现一般时序逻辑分析的方法; 2、掌握用VHDL或Verilog编写可综合的有限状态机的标准模板; 3、掌握用VHDL或Verilog编写序列检测器以及其他复杂逻辑电路的设计; 二、实验内容 1、用MOORE型状态机设计一个具有双向步进电动机控制实验:该控制电路有三个输入信号:clk时钟信号,clr复位信号,dir方向控制信号。输出信号为phase[3..0]用来控制步进电机的动作。当dir=1时要求phase[3..0]按照“0001”,“0010”,“0100”,“1000”的顺序变化;当dir=0时要求phase[3..0]按照“0001”,“1000”,“0100”,“0010”的顺序变化。 2、设计一个简单的状态机,功能是检测一个5位的二进制序列“10010”。 3、设计一个串行数据检测器,要求是:连续4个或4个以上为1时输出为1,其他输入情况为0。(选做) 4、根据状态图,写出对应于结构图b,分别由主控组合进程和主控时序进程组成的VERILOG 有限状态机描述。(选做) 三、实验步骤 实验一: 1、建立工程

2、创建Verilog HDL文件 3、输入程序代码并保存 module moore1(clk,clr,dir,phase); input clk,clr,dir; output[3:0] phase; reg[3:0] phase; reg[1:0] state; parameter s0='b00,s1='b01,s2='b10,s3='b11; always@(posedge clk) begin if(clr)begin phase<='b0000;state<=s0;end else begin case(state) s0:if(dir) begin phase<='b0010;state<=s1;end else begin phase<='b1000;state<=s3;end s1:if(dir) begin phase<='b0100;state<=s2;end else begin phase<='b0001;state<=s0;end s2:if(dir) begin phase<='b1000;state<=s3;end

状态机设计仿真

状态机设计仿真 一、实验例题 设计一个序列检测器电路,检测出串行输入数据data中的二进制序列110,当检测到该序列时,电路输出1 out=;没有检测到该序列时,电路输出0,电路的状态图如1所示: 图1 电路状态转换图 二、实验原理分析 由电路的状态图分析,可列出对应的状态转换表,如图2所示: 图2 状态转换表 +相同,将图1,图2简化可得: 从状态转化表分析可得S3与S0对应的S n1

改进的状态转换表 三、实验任务:依据图1状态图2表,S 存在时,用VerilogHDL设计的参考程序如 3 下: module pulse_check(data,clk,rst,out); input data,clk,rst; output out; reg out; reg[1:0] CST,NST; parameter[1:0] s0=0,s1=1,s2=2,s3=3; always@(posedge clk or negedge rst) if (!rst) CST<=s0;//复位有效,进入下一个状态 else CST<=NST; always@(CST or data) begin case(CST) s0: if(data==1'b1) NST<=s1; else NST<=s0; s1: if(data==1'b1) NST<=s2; else NST<=s0; s2: if(data==1'b0) NST<=s3; else NST<=s2; s3: if(data==1'b0) NST<=s0; else NST<=s1;

default: NST<=s0; endcase end always@(CST or data) case(CST) s0:out=1'b0; s1:out=1'b0; s2: if(data==1'b0) out=1'b1; else out=1'b0; s3:out=1'b0; endcase endmodule rst复位信号(低电平有效),clk状态时钟。四:仿真图形

状态机设计总结

状态机设计 简介 状态机的设计被广泛地用于时序控制逻辑中,它是许多数字系统的核心。状态机可以应付众多应用场合的需求,覆盖宽范围的性能和复杂度;例如微处理器与VLSI外围接口的低级别控制,常规微处理器中的总线裁决和时序产生,定制的位片微处理器,数据加密和解密,传输协议等。 通常在设计周期中,控制逻辑的细节安排在最后处理,因为系统需求的改变和特征的增强会对其造成影响。对于控制逻辑设计,可编程逻辑是一个很宽松的解决方案,因为它允许简单的修改而不必扰乱PCB板布局。其灵活性提供了在不影响市场化时间的前提下,允许设计改动的机会。大多数带寄存器的PAL器件应用都是需要使用状态机设计技术的时序控制逻辑。随着技术的发展,新的高速、高性能的器件不断出现,它们简化了状态机设计的任务。对于状态机设计,宽范围的不同功能与性能的解决方案是可行的。在本次讨论中,我们将检验状态机执行的功能,它们在多种器件中的实现,以及它们的选择。 什么是状态机? 状态机是一个以有序的方式,遍历预定的状态序列的数字设备。状态是在电路的不同部分,测量到的一组数值。一个简单状态机可以由以下几部分构成:基于PAL器件的组合逻辑,输出寄存器和状态寄存器。这样一个序列发生器中的状态由状态寄存器和/或输出寄存器中所存储的值来决定。 状态机的通用形式可以用图1所示的设备来描述。除了这一设备的输入和输出,状态机还有两个必需的组成元件:组合逻辑和存储器(寄存器)。这类似于前面所讨论的带寄存器的记数器设计,它们本质上就是简单的状态机。存储器用来存储状态机的状态,组合逻辑可以看成两个截然不同的功能模块:下一状态解码器和输出解码器(图2)。当输出解码器产生实际的输出时,下一状态解码器决定状态机的下一状态。尽管它们执行截然不同的两个功能,但是它们通常被组合成如图1所示的组合逻辑阵列。 状态机的基本操作有两部分: 1、状态机遍历状态序列,下一状态解码器基于当前状态和输入条件来决定下一状态。

状态机设计

集成电路实验 状态机设计实验报告 专业:电子信息工程 姓名:江燕婷 学号:2011301200025

状态机设计(实验五)实验报告 一.实验目的 1. 掌握状态机设计的基本方法 2.学习利用状态机的方法实现控制电路 二.实验原理 有限状态机(Finite State Machine FSM)是时序电路设计中经常采用的一种方式,尤其适合设计数字系统的控制模块,在一些需要控制高速器件的场合,用状态机进行设计是一种很好的解决问题的方案,具有速度快、结构简单、可靠性高等优点。有限状态机非常适合用FPGA器件实现,用Verilog HDL的case 语句能很好地描述基于状态机的设计,再通过EDA工具软件的综合,一般可以生成性能极优的状态机电路,从而使其在执行时间、运行速度和占用资源等方面优于用CPU实现的方案。 有限状态机一般包括组合逻辑和寄存器逻辑两部分,寄存器逻辑用于存储状态,组合逻辑用于状态译码和产生输出信号。根据输出信号产生方法的不同,状态机可分为两类:米里型(Mealy)和摩尔型(Moore)。摩尔型状态机的输出只是当前状态的函数,如图1-1所示;米里型状态机的输出则是当前状态和当前输入的函数,如图1-2所示。米里型状态机的输出是在输入变化后立即变化的,不依赖时钟信号的同步,摩尔型状态机的输入发生变化时还需要等待时钟的到来,必须在状态发生变化时才会导致输出的变化,因此比米里型状态机要多等待一个时钟周期。 图1-1 摩尔型状态机图1-2 米里型状态机 状态机在硬件描述语言实现上,可使用单过程、双过程或三过程等不同的结构实现。状态机的状态实现上,可采用符号编码或显式数字编码。编码方式有顺序编码(自然二进制编码),一位热码(one-hot encoding),格雷(gray code)码等。顺序编码,简单状态寄存器占用少;一位热码输出译码电路简单;在状态顺序变化时,格雷码每次只有一位变化,避免产生输出信号毛刺。

利用有限状态机进行时序逻辑的设计

实验三利用有限状态机进行时序逻辑的设计 1.实验目的: (1)掌握利用有限状态机实现一般时序逻辑分析的方法; (2)掌握用Verilog编写可综合的有限状态机的标准模板; (3)掌握用Verilog编写状态机模块的测试文件的一般方法。 (4)在数字电路中已经学习过通过建立有限状态机来进行数字逻辑的设计,而在VerilogHDL硬件描述语言中,这种设计方法得到进一步的发展。通过Verilog HDL提供的语句,可以直观的设计出更为复杂的时序逻辑的电路。关于有限状态机的设计方法在教材中已经作了较为详细的阐述。 2.实验环境 PC机一台,安装有quartusII13.0软件以及modulsim软件 3.实验内容 设计一个简单的状态机,功能是检测一个5位二进制序列“10010”。考虑到序列重叠的可能。有限状态机共提供8个状态(包括初始状态IDLE). 4.实验步骤 1)源程序: module seqdet(x,z,clk,rst,state); input x,clk ,rst ; output z; output [2:0] state ; reg[2:0] state ; wire z; parameter IDLE='d0, A='d1, B='d2, C='d3, D='d4, E='d5, F='d6, G='d7; assign z=(state == E && x==0)?1:0; always @(posedge clk) if(!rst) begin state <= IDLE; end else casex(state) IDLE:if(x==1) begin state <= A; end A: if(x==0) begin state <= B; end B: if(x==0) begin state <= C; end else begin state <= F; end C: if(x==1) begin state <= D; end else begin

第五讲状态机设计及其指导原则

第五讲状态机设计及其指导原则1/ 38第五讲状态机设计及其指导原则1/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学第五讲状态机设计及其指导原则 1 状态机是一种设计思想方法2状态机结构 3状态机设计的其他技巧4状态机设计步骤 第五讲状态机设计及其指导原则2/ 38 第五讲状态机设计及其指导原则2/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学z 状态机是一种设计思想方法 第五讲状态机设计及其指导原则3/ 38 第五讲状态机设计及其指导原则3/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学原语描述 module noconditional (clk,nrst,state,event);input clk,nrst input state;output event;reg event;reg [2:0] CS; //CurrentState reg [2:0] NS; //NextState parameter [2:0] //one hot with zero idle idle = 3’b000,dorm = 3'b001,diningroom = 3'b010,classroom = 3'b100; 第五讲状态机设计及其指导原则4/ 38第五讲状态机设计及其指导原则4/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学//sequential state transition always @ (posedge clk or negedge nrst) if (!nrst) CS <= idle; else CS <= NS; //combinational condition judgment always @ (nrst or CS) begin case (CS) idle:idle_task;NS = dorm; dorm:dorm_task;NS = diningroom; diningroom:diningroom_task;NS = classroom;classroom:classroom_task;NS = dorm;default:idle_task;NS = dorm; endcase end endmodule 第五讲状态机设计及其指导原则5/ 38第五讲状态机设计及其指导原则5/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学第五讲状态机设计及其指导原则6/ 38 第五讲状态机设计及其指导原则6/ 38制作人:梁瑞宇单位:河海大学制作人:梁瑞宇单位:河海大学 状态机的本质--对具有逻辑顺序或时序规律事件的一种描述方法 状态机的两个应用思路:-从状态变量入手-明确电路的输出的关系

实验八:利用有限状态机进行时序逻辑的设计

实验八:利用有限状态机进行时序逻辑的设计一:利用有限状态机进行时序逻辑的设计的源程序: module seqdet(x,z,clk,rst,state); input x,clk,rst; output z; output[2:0] state; reg[2:0] state; wire z; parameter IDLE='d0, A='d1, B='d2, C='d3, D='d4, E='d5, F='d6, G='d7; assign z = ( state==E && x==0 )? 1 : 0; always @(posedge clk) if(!rst) begin state <= IDLE; end else casex(state) IDLE : if(x==1) begin state <= A; end A: if(x==0) begin state <= B; end B: if(x==0) begin state <= C; end else begin state <= F; end C: if(x==1) begin state <= D; end else begin

state <= G; end D: if(x==0) begin state <= E; end else begin state <= A; end E: if(x==0) begin state <= C; end else begin state <= A; end F: if(x==1) begin state <= A; end else begin state <= B; end G: if(x==1) begin state <= F; end default:state=IDLE; endcase endmodule 二:利用有限状态机进行时序逻辑的设计的测试代码:`timescale 1ns/1ns `include "./seqdet.v" module seqdet_Top; reg clk,rst; reg[23:0] data; wire[2:0] state; wire z,x; assign x=data[23]; always #10 clk = ~clk;

浅谈状态机的设计方法及应用

浅谈状态机的设计方法及应用 刘成玉 李明 陈洁 (中国兵器工业第214研究所 蚌埠 233042) 摘 要 有限状态机(Fi n ite S tate M achine ,FS M )是时序电路设计中经常采用的一种方式,尤其适用于设计数字系统的控制模块。有限状态机不是孤立的一个状态,它依赖于输入输出关系,系统需求,编程语言的条件限制以及其他诸多因素。本文主要介绍了有限状态机的原理及实际应用。 关键词 有限状态机(Fi n ite State M achine ,FS M ) 二进制编码(B inary S tate M achine) 格雷编码(Gray Code State M ach i n e) 一位热码编码(One-H ot S tate M ach i n e Encod i n g ) 1 引 言 我们可以把有限状态机(F i n ite State M a ch i n e ,FSM )想象成一个能够接受输入信号的系统,系统内部包含状态寄存器,并且在可能的条件下产生输出信号。在任何特定的时刻,状态机内部所有寄存器的状态和形成这个状态的完整的条件构成了那个时刻的状态(state)。因为状态的个数是有限的,所以称之为有限状态机。 根据输出信号产生方法的不同,状态机可以分为米里型(M ealy )和摩尔型(M oore )两类。M ealy 型状态机输出与当前状态和输入有关,而M oore 型状态机的输出只与当前状态有关。在实际设计工作中,M ealy 型状态机应用较为普遍,而在设计高速电路时,常常把状态变量直接用作输出,以提高运行速度,则M oore 型状态机更为适合。有限状态机的结构如图1所示: 我们可以从图1 中清楚地看出两类状态机的 图1 有限状态机的结构 第25卷第1期 2007年3月 集成电路通讯 JICHENGDIANLU TONGXUN V o.l 25 N o .1 M ar .2007

安全状态机的设计

W H I T E P A P E R Creating Safe State Machines By Sam Zhong Zhang Technical Marketing Engineer Mentor Graphics Corporation

Creating Safe State Machines Introduction Finite state machines are widely used in digital circuit designs. Generally, when designing a state machine using an HDL, the synthesis tools will optimize away all states that cannot be reached and generate a highly optimized circuit. Sometimes, however, the optimization is not acceptable. For example, if the circuit powers up in an invalid state, or the circuit is in an extreme working environment and a glitch sends it into an undesired state, the circuit may never get back to its normal operating condition. This paper discuses a general methodology when creating a state machine using the HDL Designer Series TM State Diagram Editor. You can specify the design so that synthesis tools will not optimize away those unused states, thus a “safe” state machine can be generated. . “Safe” and “Unsafe” State Machines Not all state machine designs are “unsafe.” “Safe” depends on how many states are in a design and how you define the state encoding styles: “Safe” State Machines If the number of states (N) is a power of 2, and you use a binary or gray-code encoding algorithm, the state machine is “safe”. This ensures that you have M number of registers where N = 2M. Because all of the possible state values (or register statuses) are reachable, the design is “safe.” “Unsafe” State Machines If the number of states is not a power of 2, or if you do not use binary or gray-code encoding algorithm, e.g. one-hot, the state machine is “unsafe.” For example, Figure 1 shows a design that contains 4 states: Figure 1. NRZ-to-Manchester Conversion The number of states is 4, if you use the one-hot encoding algorithm. For example: s0 => 0001 s1 => 0010 s2 => 0100 s3 => 1000

状态机及其VHDL设计说明

第7章状态机及其VHDL设计 容提要:有限状态机(Finite State Machine,简称FSM)是一类很重要的时序电路,是许多数字系统的核心部件,也是实时系统设计中的一种数学模型,是一种重要的、易于建立的、应用比较广泛的、以描述控制特性为主的建模方法,它可以应用于从系统分析到设计的所有阶段。有限状态机的优点在于简单易用,状态间的关系清晰直观。建立有限状态机主要有两种方法:“状态转移图”和“状态转移表”。标准状态机通常可分为Moore和Mealy 两种类型。本章主要介绍了基于VHDL的常见有限状态机的类型、结构、功能及表达方法,重点是如何有效地设计与实现。 学习要求:了解状态机的基本结构、功能和分类,掌握有限状态机的一般设计思路与方法、状态机编码方案的恰当选取、Moore和Mealy状态机的本质区别及设计实现。 关键词:状态机(State Machine),Moore,Mealy,VHDL设计(VHDL Design) 7.1 状态机的基本结构和功能 7.2 一般状态机的VHDL设计 7.2.1 状态机的一般组成 7.2.2 状态机的编码方案 7.3 摩尔状态机的VHDL设计 7.4 米立状态机的VHDL设计 7.1 状态机的基本结构和功能 状态机的基本结构如图7.1所示。除了输人信号、输出信号外,状态机还包含一组寄存器记忆状态机的部状态。状态机寄存器的下一个状态及输出,不仅同输入信号有关,而且还与寄存器的当前状态有关,状态机可以认为是组合逻辑和寄存器逻辑的特殊组合。它包括两个主要部分:即组合逻辑部分和寄存器。组合逻辑部分又可分为状态译码器和输出译码器,状态译码器确定状态机的下一个状态,即确定状态机的激励方程,输出译码器确定状态机的输出,即确定状态机的输出方程。寄存器用于存储状态机的部状态。 状态机的基本操作有两种: 1.状态机的部状态转换。 状态机经历一系列状态,下一状态由状态译码器根据当前状态和输入条件决定。 2.产生输出信号序列。 输出信号由输出译码器根据当前状态和输入条件确定。 用输入信号决定下一状态也称为“转移”。除了转移之外,复杂的状态机还具有重复和历程功能。从一个状态转移到另一状态称为控制定序,而决定下一状态所需的逻辑称为转移函数。

怎样写好三段式状态机

第6章 如何写好状态机 节选自《Verilog设计与验证》作者:吴继华、王诚 状态机是逻辑设计的重要内容,状态机的设计水平直接反应工程师的逻辑功底,所以许多公司的硬件和逻辑工程师面试中,状态机设计几乎是必选题目。本章在引入状态机设计思想的基础上,重点讨论如何写好状态机。 本章主要内容如下: ?状态机的基本概念; ?如何写好状态机; ?使用Synplify Pro分析FSM。 6.1 状态机的基本概念 本节的重点在于帮助读者理解状态机的基本概念和应用场合。 6.1.1 状态机是一种思想方法 相信大多数工科学生在学习数字电路时都学习过状态机的基本概念,了解一些使用状态机描述时序电路的基本方法。但是,笔者希望大家能扩展思维,认识到状态机不仅仅是一种时序电路设计工具,它更是一种思想方法。 我们先看下面一个简单的例子。在大学生活中,某学生的在校的学习生活可以简单地概括为宿舍、教室、食堂之间的周而复始,用图6-1就可以形象地表现出来。这里画这张图,并不是要讨论这个学生是否是一个“乖乖”类型学生,请大家注意,如果将图中的“地点”认为是“状态”,将“功能”认为是状态的“输出”,这张图就是一张标准的状态转移图,也就是说,我们用状态机的方式清晰地描述了这个学生的在校生活方式。

第6章如何写好状态机 138

状态机的基本概念 139 就是状态机所要描述的核心和强项,换言之,所有具有逻辑顺序和时序规律的事情都适合用状态机描述。 很多初学者不知道何时应用状态机。这里介绍两种应用思路:第一种思路,从状态变量入手。如果一个电路具有时序规律或者逻辑顺序,我们就可以自然而然地规划出状态,从这些状态入手,分析每个状态的输入,状态转移和输出,从而完成电路功能;第二种思路是首先明确电路的输出的关系,这些输出相当于状态的输出,回溯规划每个状态,和状态转移条件与状态输入。无论那种思路,使用状态机的目的都是要控制某部分电路,完成某种具有逻辑顺序或时序规律的电路设计。 其实对于逻辑电路而言,小到一个简单的时序逻辑,大到复杂的微处理器,都适合用状态机方法进行描述。请读者打开思路,不要仅仅局限于时序逻辑,发现电路的内在规律,确认电路的“状态变量”,大胆使用状态机描述电路模型。由于状态机不仅仅是一种电路描述工具,它更是一种思想方法,而且状态机的HDL 语言表达方式比较规范,有章可循,所以很多有经验的设计者习惯用状态机思想进行逻辑设计,对各种复杂设计都套用状态机的设计理念,从而提高设计的效率和稳定性。 6.1.2 状态机基本要素与分类 状态机的基本要素有3个,其实我们在第一节的举例中都有涉及,只是没有点明,它们是:状态、输出和输入。 ? 状态:也叫状态变量。在逻辑设计中,使用状态划分逻辑顺序和时序规律。 比如:设计伪随机码发生器时,可以用移位寄存器序列作为状态;在设计电机 控制电路时,可以以电机的不同转速作为状态;在设计通信系统时,可以用信 令的状态作为状态变量等。 ? 输出:输出指在某一个状态时特定发生的事件。如设计电机控制电路中,如 果电机转速过高,则输出为转速过高报警,也可以伴随减速指令或降温措施 等。 ? 输入:指状态机中进入每个状态的条件,有的状态机没有输入条件,其中的 状态转移较为简单,有的状态机有输入条件,当某个输入条件存在时才能转移 到相应的状态。 根据状态机的输出是否与输入条件相关,可将状态机分为两大类:摩尔(Moore )型状态机和米勒(Mealy )型状态机。 ? 摩尔状态机:摩尔状态机的输出仅仅依赖于当前状态,而与输入条件无关。 例如图6-1所示的例子,将图中的“地点”认为是“状态”,将“功能”认为 是状态的“输出”,则每个输出仅仅与状态相关,所以它是一个摩尔型状态 机。 ? 米勒型状态机:米勒型状态机的输出不仅依赖于当前状态,而且取决于该状 态的输入条件。例如图6-2所示的例子,将图中的“地点”认为是“状态”, 将“功能”认为是状态的“输出”,将“条件”认为是状态转移的“输入条 件”,大家可以发现,该学生到达什么地方,做什么事情都是由当前状态和输

FSM状态机设计规则

状态机设计 FSM简介: FSM 分两大类:米里型和摩尔型,组成要素有输入(包括复位),状态(包括当前状态的操作),状态转移条件,状态的输出条件,图1为状态机结构图。设计FSM 的方法和技巧多种多样,但是总结起来有两大类:第一种,将状态转移和状态的操作和判断等写到一个模块(process、block)中。另一种是将状态转移单独写成一个模块,将状态的操作和判断等写到另一个模块中(在V erilog代码中,相当于使用两个“always”block)。其中较好的方式是后者。其原因如下: 首先FSM 和其他设计一样,最好使用同步时序方式设计,好处不再赘述。而状态机实现后,状态转移是用寄存器实现的,是同步时序部分。状态的转移条件的判断是通过组合逻辑判断实现的,之所以第二种比第一种编码方式合理,就在于第二种编码将同步时序和组合逻辑分别放到不同的程序块(process,block)中实现。这样做的好处不仅仅是便于阅读、理解、维护,更重要的是利于综合器优化代码,利于用户添加合适的时序约束条件,利于布局布线器实现设计。 图1为状态机结构图 显式的FSM 描述方法可以描述任意的FSM(参考V erilog 第四版P181 有限状态机的说明)。两个always 模块。其中一个是时序模块,一个为组合逻辑。时序模块设计与书上完全一致,表示状态转移,可分为同步与异步复位。 同步: always @(posedge clk) if (!reset) ………… 异步: always @(posedge clk or negedge reset) if (!reset) …………

组合逻辑用case 语句,sensitive list 包括当然状态(current state)和输入(a,b,c…)。 编者注:以下是编者从“State Machine Coding Styles for Synthesis”一文中摘取的程序代码,是一个简单状态机的示例,采用两个always块的方法: module bm1_s (err, n_o1, o2, o3, o4,i1, i2, i3, i4, clk, rst); output err, n_o1, o2, o3, o4; input i1, i2, i3, i4, clk, rst; reg err, n_o1, o2, o3, o4; parameter [2:0] //可以在此处添加综合约束属性来限定状态机的编码:binary,one-hot,gray,etc… IDLE = 3'd0, S1 = 3'd1, S2 = 3'd2, S3 = 3'd3, ERROR = 3'd4; reg [2:0] state, next; always @(posedge clk or posedge rst)//异步复位,时序逻辑 if (rst) state <= IDLE; else state <= next; always @(state or i1 or i2 or i3 or i4) begin //组合逻辑,敏感列表包含当前状态以及所有的状态机输入 next = 3'bx;//设置默认值,以便防止因为if或者case语句不完整综合生成锁存器 err = 0; n_o1 = 1; o2 = 0; o3 = 0; o4 = 0; case (state)