笙泉8051单片机选型表

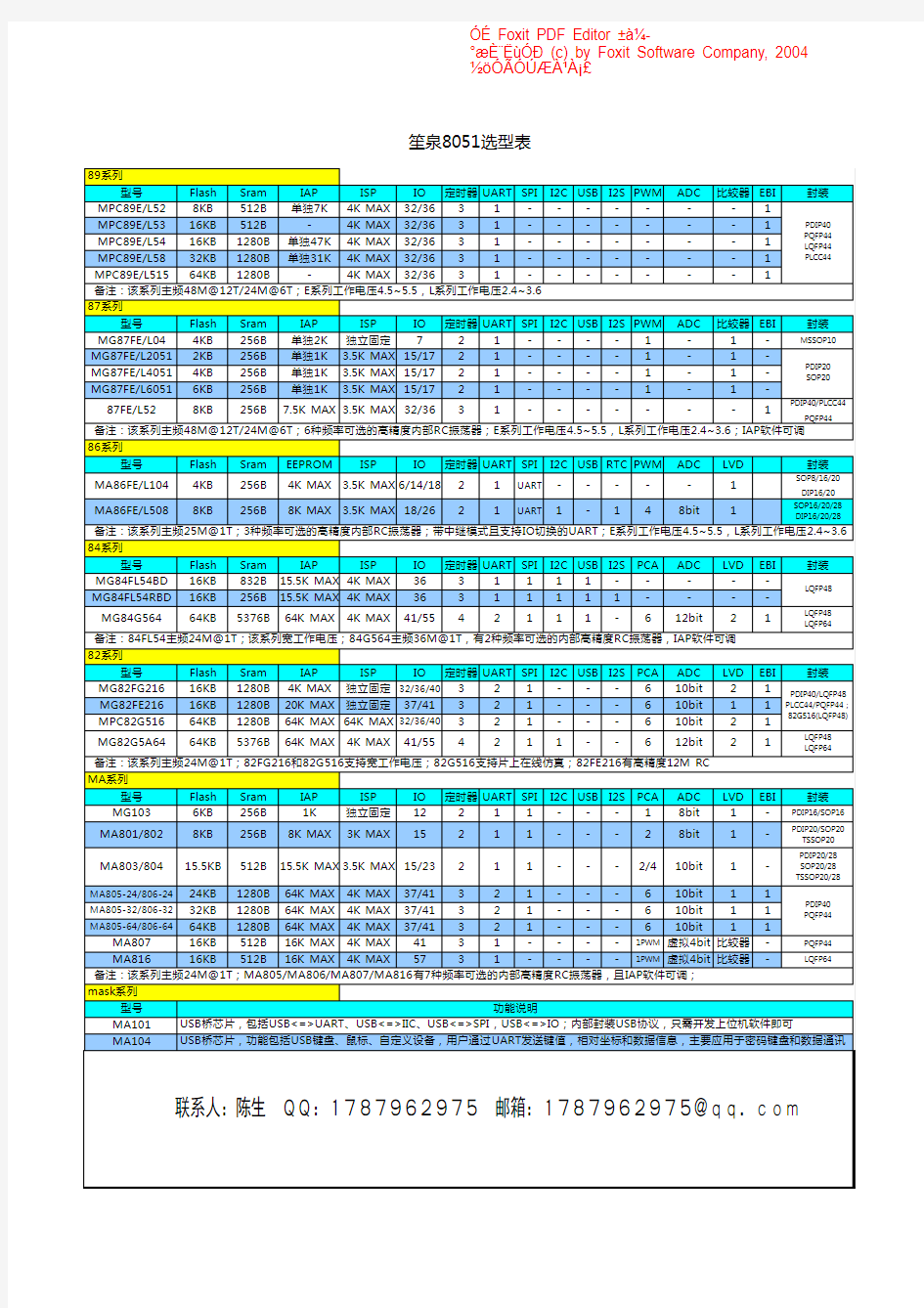

笙泉8051选型表

??ó?óú?à1à?£

°?è¨?ùóD (c) by Foxit Software Company, 2004óé Foxit PDF Editor ±à?-

单片机考试常见试题简答题-整理版

简答题部分 1、什么叫堆栈? 2、进位和溢出? 3、在单片机中,片内ROM的配置有几种形式?各有什么特点? 4、什么是单片机的机器周期、状态周期、振荡周期和指令周期?它们之间是什么关系? 5、MCS-51单片机通常内部包含哪些主要逻辑功能部件? 6、MCS-51单片机的存储器从物理结构上可划分几个空间? 7、存储器中有几个保留特殊功能的单元用做入口地址?分别作什么作用? 8、MCS-51单片机片内256B的数据存储器可分为几个区?分别起什么作用? 8、MCS-51单片机的P0~P3四个I/O端口在结构上有何异同?使用时应注意的事项? 9、存储器空间在物理结构上可划分为几个部分? 10、开机复位后,CPU使用是的哪组工作寄存器?它们的地址是什么?CPU如何确定和改变当前工作寄存器组? 11、MCS-51的时钟周期、机器周期、指令周期的如何分配的?当振荡频率为8MHz时,一个单片机时钟周期为多少微秒? 12、程序状态存储器PSW的作用是什么?常用状态标志有哪几位?作用是什么? 13、EA/VPP引脚有何功用?8031的引脚应如何处理?为什么? 14、单片机有哪几个特殊功能寄存器?各在单片机的哪些功能部件中? 15、什么是指令?什么是程序?简述程序在计算机中的执行过程。 16、什么叫寻址方式?MCS51有几种寻址方式? 17、SJMP(短转移)指令和AJMP(绝对转移)指令的主要区别。 18、中断服务子程序与普通子程序有哪些异同之处? 19、MCS-51响应中断的条件是什么?CPU响应中断后,CPU要进行哪些操作?不同的中断源的中断入口地址是什么? 20、单片机对中断优先级的处理原则是什么? 21、MCS-51的外部中断有哪两种触发方式?他们对触发脉冲或电平有什么要求? 22、什么是中断和中断系统?其主要功能是什么? 23、MCS-51有哪些中断源? 24、说明外部中断请求的查询和响应过程 25、MCS-51响应中断的条件?。 26、简述MCS-51单片机的中断响应过程。 27、在执行某一中断源的中断服务程序时,如果有新的中断请求出现,试问在什么情况下可响应新的中断请求?在什么情况下不能响应新的中断请求? 28、MCS-51单片机外部中断源有几种触发中断请求的方法?如何实现中断请求? 29、什么是中断优先级?中断优先级处理的原则是什么?

如何选择适合的单片机-单片机选型

专利证书 网站首页 由单片机实现检测控制,其中一个首要的工作就是选择合适的单片机。目前国内在使用单片机作控制系统的微处理器时多选择51系列或Motorola 系列单片机,而本系统选用的PIC系列单片机在多个方面较其它系列单片机更有优越性。下面对PIC单片机作较详细介绍。 2.4.l 由单片机实现检测控制,其中一个首要的工作就是选择合适的单片机。目前国内在使用单片机作控制系统的微处理器时多选择51系列或Motorola 当今世界上涌现出各种各样的单片机,目前应用较广的主要有美国Intel公司开发和生产的MCS一51,MCS一96系列、台湾ICSI公司的8051系列、美国Motorola公司的MC68系列和美国Microchip公司的PIC系列等,其中各个系列的单片机都有其各自的优点,与其它系列相比,美国

力,从而提高了工业电脑自动控制器的适应能力,以下分几个方面通过与其它类型单片机的比较来说明它的优越之处。 (l)哈佛总线结构 PIC系列单片机在架构上采用了与众不同的设计手法,PIC系列单片机不仅采用了哈佛体系结构(也就是两种存储器位于不同的逻辑空间里,这种架构的微控制器、微处理器、数字信号处理器或者微型计算机系统,称为哈佛体系结构),而且还采用了哈佛总线结构。在PIC系列单片机中采用的这种哈佛总线结构,就是在芯片内部将数据总线和指令总线分离,并且采用不同的宽度,这样做的好处是,便于实现指令提取的“流水作业”,也就是在执行一条指令的同时对下一条指令进行取指令操作;便于实现全部指令的单字节化、单周期化,从而有利于提高CP U执行指令的速度。在一般的单片机中,指令总线和数据总线是共用的(即分时复用)Motorola公司开发的MC68H C05/08系列单片机,其程序存储器和数据存储器统一编址(也就是两种存储器位于同一个逻辑空间里,这种架构的微控制器、微处理器、数字信号处理器或者微型计算机系统,称为普林斯顿体系结构),早期在国内市场上最流行的单片机产品Intel开发生产的MCS一51系列单片机,其程序存储器和数据存储器虽然独立编址;但是它们与CP U之间传递信息必须共用同一条总线,仍然摆脱不了瓶颈效应的制约,于是影响到CP U运行速度的进一步提高。见图2.6。 (2)指令单字节化 因为数据总线和指令总线是分离的,并且采用了不同的宽度,所以程序器R OM和数据存储器RA M的寻址空间(即地址编码空间)是互相独立的,而且存储器度也不同。这样设计不仅可以确保数据的安全性,还能提高运行速实现全部指令的单字节化。在此所说的字节,特指PIC单片机的指令字节,是常说的8位字节。例如, PIC12C50X/PIC16CS X系列单片机的指令字节12位,PIC16C6X/PIC16C7X/PIC16CS X系列的指令字节为14位;PIC18FXXX系列的字节为16位。它们的数据存储器全为8位宽。而MCS一51系列单片机的R OM和宽度都是8位,指令长度从一个字节(8位)到3个字 节长短不一。另外,PIC 微控制器的取指令和执行指令采用指令流水线结构,当一条指令被执行时允一条指令同时被取出,使得在每个时钟周期内可以获得的最高效率。 其指令线结构见图2.7。

单片机简答题汇总

单片机简答题汇总 1、计算机经历了几个时代? 电子管、晶体管、集成电路、大规模集成电路和超大规模集成电路、智能计算机。 2、冯诺依曼设计思想? a.计算机包括运算器、存储器、输入/输出设备。 b.内部采用二进制表示指令和代码。 c.将编号的程序送入内存储器中,然后启动计算机工作,能够顺序逐条取出指令和执 行指令。 3、MCS-51的内部结构? 8位CPU、8位并行I/O口、128个字节的内部RAM、21个SFR、4KB的内部ROM、一个全双工串行I/O口、2个16位定时器/计数器、5个中断源,2个中断优先级、 4、ROM和RAM ROM:片内4KB,地址范围0000H – 0FFFH 片外扩展64KB 地址范围0000H - FFFFH 片内外统一编址方式复位后PC为0 RAM:片内256字节地址范围00H – FFH 低128字节为一般RAM区00H-7FH 00H – 1FH 工作寄存器区,4组通用寄存器区,一组8个寄存器 20H - 2FH 位寻址区,也可字节寻址 30H – 7FH堆栈区和数据缓冲区 高128字节为SFR地址范围为80H- FFH 实现各种控制功能 5、堆栈?堆栈指针? 一种按照“先进后出”为原则的线性表数据结构。 存放堆栈的栈顶地址的寄存器(8位),系统复位后SP为07H。 6、单片机正常工作的条件? a.电源正常 b.时钟正常 c.复位正常 7、C51外扩的ROM和RAM可以有相同的地址空间,但不会发生数据冲突,为什么? 访问外扩的ROM和RAM的指令不同,所发出的控制信号也不同。读外部RAM时,RD/信号有效,写外部RAM时,WR/有效,读外部ROM时,PSEN/有效。在程序执行的过程中只能有一个信号有效,因此即使有相同的地址也不会发挥数据冲突。 8、C51外部引脚EA/的作用? EA/是内外部RAM的选通信号 EA/ = 0 时,只选择外部ROM EA/ = 1 时,PC<0FFFH时,选择内部ROM PC>0FFFH时,选择外部ROM 9、位寻址区? 内部RAM的20H – 2FH为位寻址区,位寻址范围为00H – 7FH SFR中地址能被8整除的字节地址单元,地址范围是80H – FFH 10、中断?中断响应和中断返回? 由于内部或外部的某种原因,CPU必须终止当前的程序,转去执行中断请求的那个外设

松翰MCU选型表

SN8F2250/2270 Series USB Type Part No. Program Memory RAM (8bit) Stack IO ADC DAC Timer PWM Buzzer SIO LCD Interrupt Int Ext Package Other Features SN8F22511B10K-Flash 512 8 8 - - 4 - 1 - 7/1 SSOP16 Full speed USB2.0,Support Control/3 Interrupt SN8F2251B10K-Flash 512 8 8 - - 4 - 1 - 7/0 QFN16 Full speed USB2.0,Support Control/3 Interrupt SN8F22521B10K-Flash 512 8 12 - - 4 2 1 - 7/2 SOP20/SSOP20 Full speed USB2.0,Support Control/3 Interrupt SN8F22531B10K-Flash 512 8 16 - - 4 2 1 - 7/2 QFN24 Full speed USB2.0,Support Control/3 Interrupt SN8F2253B10K-Flash 512 8 16 - - 4 2 1 - 7/2 SOP24 Full speed USB2.0,Support Control/3 Interrupt SN8F2255B10K-Flash 512 8 24 - - 4 2 1 - 7/2 LQFP32 Full speed USB2.0,Support Control/3 Interrupt SN8F2271B5K-Flash 192 8 10 - - 2 - 1 - 5/1 QFN16 Low speed USB2.0,Support Control/2 Interrupt SN8F22721B5K-Flash 192 8 14 - - 2 1 1 - 5/2 DIP20/SOP20/SSOP20 Low speed USB2.0,Support Control/2 Interrupt SN8F2280 Series USB Type Part No. Program Memory RAM (8bit) Stack IO ADC DAC Timer PWM Buzzer SIO LCD Interrupt Int Ext Package Other Features

单片机简答题整理

1.MSC-51单片机内部包含哪些主要逻辑功能部件? (1)一个8位微处理器CPU。 (2)数据存储器RAM和特殊功能寄存器SFR。(3)内部程序存储器ROM。(4)两个定时/计数器,用以对外部事件进行计数,也可用作定时器。(5)四个8位可编程的I/O(输入/输出)并行端口,每个端口既可做输入,也可做输出。(6)一个串行端口,用于数据的串行通信 内部结构特点: 1.内部程序存储器(ROM)和内部数据存储器(RAM)容量(如表2-1所示)。2.输入/输出(I/O)端口。 3.外部程序存储器和外部数据存储器寻址空间。4.中断与堆栈。5.定时/计数器与寄存器区。6.指令系统。 2.片机的EA,AL,PS EN信号个自动功能是什么? EA:为片外程序存储器选用端,该引脚有效(低电平)时,只选用片外程序存储器,否则单片机上电或复位后选用片内程序存储器。ALE:地址索存有效信号输出在访问片外程序存储器期间,ALE以每机器周期两次进行信号输出,其下降沿用于控制锁存P0输出的低8位地址;在不访问片外程序存储器期间,ALE端仍以上述频率(振荡频率f os c的1/6)出现,可作为对外输出的时钟脉冲或用于定时目的.端,PSEN:片外程序存储器读选通信号输出端,低电平有效. 3.80C51系列单片机有哪些信号需要芯片引脚以第二功能方式提供? ●p1.0:定时计数器2的计数脉冲输入端T2P1.1:定时计数器2的外部控制端T2EXP3.0:PxD串行口输入端P3.1:T xD 串行口输出端P3.2:INT0外部中断0请求输入端,低电平有效P3.3:INT1外部中断1请求输入端,低电平有效P3.4:T0定时/计数器0技术脉冲输入端P3.5:T1定时/计数器1技术脉冲输入端P3.6:W R外部数据存数器写选通信信号输出端,低电平有效P3.7:RD外部数据存数器读选通信信号输出端,低电平有效.4.51系列单片机的程序状态字PSW中存放 什么信息?其中的OV标志位在什么情况下 被置位?置位是表示什么意思? ●PSW是一个8位标志寄存器,它保存指令 执行结果的特征信息,以供程序查询和判别。 ●1)做加法时,最高位,次高位之一有进位 则OV被置位2)做减法时,最高位,次高 位之一借位则OV被置位3)执行乘法指令 MULA B,积大于255,OV=14)执行处罚 指令DIV AB,如果B中所放除数为0,OV=1 ●0V=1,置位反映运算结果超出了累加器的 数值范围. 5.MCS-51系列单片机的存储器可划分为几 个空间?其地址范围和容量是多少?在使用 上有什么不同? 1)MCS-51单片机的存储器从物理结构上分 为:片内和片外数据存储器,片内和片外程 序存储器。2)从逻辑上分别可划分为:片内 统一寻址的64K程序存储器空间 (0000H---FFFFH);64KB的片外数据存储 器空间(0000H---FFFFH);256B的片内数 据存储器空间(00H---FFH)。 6.片内RA M低128单元划分为哪几个区 域?应用中怎么样合理有效的使用? ●工作寄存器区,位寻址区,数据缓冲区① 工作寄存器区用于临时寄存8位信息,分成4 组,每组有8个寄存器,每次只用1组,其他 各组不工作②位寻址区(20H~2FH),这16 个单元的每一位都赋予了一个位地址,位地 址范围为00H~7FH,位寻址区的每一位都可 能当作软件触发器,由程序直接进行位处理。 ③由于工作寄存器区,位寻址区,数据缓冲 区统一编址,使用同样的指令访问,因此这 三个区的单眼既有自己独特的功能,又可统 一调度使用,前两个已未使用的单元也可作 为一般的用户RAM单元。 7.51系列单片机的堆栈与通用微机中的堆栈 有何异同?在程序设计时,为什么要对堆栈 指针sp重新赋值? ①堆栈是按先进后出或后进先出的远侧进行 读/写的特殊RAM区域51单片机的堆栈区 时不固定的,可设置在内部RAM的任意区 域内。 ②当数据压入堆栈时,s p的内容自动加1, 作为本次进栈的指针,然后再存取数据sp 的值随着数据的存入而增加,当数据从堆栈 弹出之后,sp的值随之减少,复位时,sp 的初值为07H,堆栈实际上从08H开始堆放 信息,即堆栈初始位置位于工作寄存器区域 内,所以要重新赋值。 8.MCS-51单片机有4个并行口,在使用上如 何分工?试比较各口的特点,并说明“准双 向口”的含义? 一般P0做数据口和地址的低八位。P2做地 址的高八位。如果没有外部扩展存储器可以 作为一般的I/O使用。P1一般作为普通I/O 用。P3有第二功能,所以一般做特殊情况使 用,比如串行通信,按键中断,定时中断等。 “准”就是“基本上的意思”,也就是“准双 向口”不是真正的双向口。正常的双向口通 过方向寄存器设置后要作输出可以直接向数 据寄存器写,做输入可以直接读。而51的结 构造成他不能正样用,输出直接用就可以了, 输入必须先写全1然后再读。 9.定时器/计数器定时与计数的内部工作有 何异同? 定时工作模式和技术工作模式的工作原理相 同,只是计数脉冲来源有所不同:处于计数 器工作模式时,加法计数器对芯片端子 T0(P3.4)或T1(P3.5)上的输入脉冲计数;处 于定时器工作模式时,加法计数器对内部机 器周期脉冲计数。

应广单片机选型表-2014

Series 系列型号 FPPA 核心数 OTP ROM (K Word) RAM (Byte) ADC (bit*ch) I/O LCD (bit*ch) PWM INT Special Functions Package Re. PMS150-S081160-6--1-SOP82501C,12C509 PMC150-S081160-6--1-SOP8131,513 PMC153-S141164-12--2- SOP14153,2511,16C505 PMC156-S161164-14?VDD*4-2- SOP16156 PMC156-S181164-16?VDD*4-2- SOP1816C56 PMC251-S082160-6--1-SOP8153+ PMC251-D082160-6--1-DIP82511+ PMC251-S14 2160-12--2- SOP14 PMC251-D142160-12--2-DIP14 PMC271-S0821648*26?VDD*2-2-SOP816C71 PMC271-S1421648*512?VDD*4-2-SOP14 PMC271-S1621648*614?VDD*4-2-SOP16 PMC271-S1821648*716?VDD*4-2- SOP18 P201CS082158-69*321-SOP8EM78P152 P201CD082158-69*321-DIP8SN8P2501 P201CS142158-129*422- SOP148P53 P201CD142158-129*422- DIP14 EM78P163N P201CS162158-149*422- SOP16 P201CD162158-149*422-DIP16 PMC131-S081 1.58812*46-218*8加乘器SOP82711+ PMC131-S141 1.58812*912-448*8加乘器 SOP1671AS+ PMC131-S161 1.58812*1114-648*8加乘器 SOP16712+ PMC232-S14 2216012*61213*312- SOP1478P259 PMC232-S162216012*71413*422- SOP162712+ PMC232-S20 2216012*91813*422- SOP20 PMC234-S202420812*101821*432- SOP2078P346 PMC234-S242420812*102221*432- SOP242712+ PMC234-S28 2420812*102621*432- SOP28 P232CS142220012*612-12- SOP14EM78P259 P232CD142220012*612-12- DIP14SN8P2711/22 P232CS202220012*1018-22- SOP20HT46R064/65 P232CD202220012*1018-22- DIP20 HT46R46/47 P234CSS202420012*101816*422- SSOP20EM78P418 P234CS202420012*101816*422- SOP20EM78P346 P234CS242420012*102216*432- SOP24HT46R066/67 P234CK242420012*102216*432- SKDIP24 P221CS1821648*41611*4-2- SOP18EM78P156/159、SH69P20 P221CD1821648*41611*4-2- SOP18SN8P2602B/C、HT48R05/06 ① 产品名称说明: P232CS14 P = PADAUK 2 = FPPA Count 3 = Series 2 = ROM size(K word) C = Program Memory Type(C=OTP/F=FLASH/R=MASK) S = Package Type 14 = Pin Count ② PMC为P的升级版,引入单一FPPA运作模式,降低功耗,工作电压更宽,内部基准电压更准。但P系列比PMC系列多了一个硬件比较器。 P201C、PDK22、P211C、P221C、P232C、P234C全系列将于2015年停产,请优先选择PMC系列芯片。 ③ 全系列都带16位定时器,含PWM功能的芯片另带8位定时器并可产生PWM波形。 ④ 含A/D功能的芯片,晶圆上均有1个通道为内置Band-gap参考电压生成器,可用于绝对电压的测量。 ⑤ PMC系列通常为金线封装,高抗干扰(High EFT),工作温度(-40℃ ~ 85℃)。 ⑥ PMS系列通常为合金线封装,请勿使用于AC阻容降压供电,强电源纹波,或高EFT要求的应用场景,工作温度(0℃ ~ 70℃)。 ⑦

单片机简答题与答案

1、MCS-51单片机的时钟周期与振荡周期之间有什么关系?一个机器周期的时序如何划分? 答:时钟周期是单片机最基本的时间单位。机器周期则是完成某一个规定操作所需的时间。一个机器周期为 时钟周期,共12个振荡周期性,依次表示为S1P1、S1P2、S6P1、S6P2。 2、MCS-51单片机有几种复位方法?应注意的事项? 答:上电复位和开关复位。上电复位要求接通电源,自动实现复位操作。开关复位要求在电源接通的条件下,在 单片机运行期间,如果发生死机,用按钮开关操作使单片机复位。 3、MCS-51单片机内部包含哪些主要逻辑功能部件? 答: (1) 一个8位微处理器CPU。 数据存储器RAM和特殊功能寄存器SFR。 内部程序存储器ROM 。 两个定时/计数器,用以对外部事件进行计数,也可用作定时器。 四个8位可编程的I/O (输入/输出)并行端口,每个端口既可做输入,也可做输出。 (6) 一个串行端口,用于数据的串行通信。 4、什么是堆栈?堆栈有何作用?在程序设计时,有时为什么要对堆栈指针SP重新赋值?如果CPU在操作中要使用 两组工作寄存器,你认为SP的初值应为多大? 答:堆栈是一种按照“先进后出”或者“后进先出”规律存取数据的RAM区域由于程序中没有表识,所以要对 SP重新赋值对指针SP重新赋值是因为堆栈空间有限,要给他赋首地址。要使用两组工作寄存器, SP的值应该设置为10H。 5、MCS-51单片机的P0-P3四个I/O端口在结构上有何异同?使用时应注意的事项? 答:80C51单片机的4个I/O端口在结构上时基本相同的, 但又各具特点。在无片外扩展存储器的系统中,这 个端口的每1位都可以作为I/O端口使用。在作为一般的通用I/O输入时,都必须先向锁存器写入“1”,使输出驱动场效应管FET截止,以免误读数据。在系统扩展片外存储器时, P2 口作为高8位地址,P0 口分时作为低8位地址和 双向数据总线。 它们的主要不同点如下: (1)P0 口的每一位可驱动8个LSTTL负载。P0 口即可作I/O端口使用,也可作地址/数据总线使用。当它作通 用口输出时,只有外接上拉电阻,才有高电平输出,作地址/数据总线时,无需外接电阻,此时不能再作I/O端口使用。 (2)P1- P3 口输出级接有内部上拉电阻,每位可驱动4个LSTTL负载,能向外提供上拉电流负载,所以不必再 外接上拉电阻。 6、简述8051汇编指令格式。 答:操作码助记符[目的操作数],[原操作数]。

8031和8051是最常见的mcs51系列单片机

8031和8051是最常见的mcs51系列单片机,是inter公司早期的成熟的单片机产品,应用范围涉及到各行各业,下面介绍一下它的引脚图等资料。 <8031,8051管脚图> 8031,8051引脚功能 (1)主电源引脚Vss和Vcc ① Vss接地 ② Vcc正常操作时为+5伏电源 (2)外接晶振引脚XTAL1和XTAL2 ① XTAL1内部振荡电路反相放大器的输入端,是外接晶体的一个引脚。当采用外部振荡器时,此引脚接地。 wk_ad_begin({pid : 21});wk_ad_after(21, function(){$('.ad-hidden').hide();}, function(){$('.ad-hidden').show();}); ② XTAL2内部振荡电路反相放大器的输出端。是外接晶体的另一端。当采用外部振荡器时,此引脚接外部振荡源。 (3)控制或与其它电源复用引脚RST/VPD,ALE/ ,和 /Vpp ① RST/VPD 当振荡器运行时,在此引脚上出现两个机器周期的高电平(由低到高跳变),将使单片机复位 在Vcc掉电期间,此引脚可接上备用电源,由VPD向内部提供备用电源,以保持内部RAM 中的数据。

② ALE/ 正常操作时为ALE功能(允许地址锁存)提供把地址的低字节锁存到外部锁存器,ALE 引脚以不变的频率(振荡器频率的)周期性地发出正脉冲信号。因此,它可用作对外输出的时钟,或用于定时目的。但要注意,每当访问外部数据存储器时,将跳过一个ALE 脉冲,ALE 端可以驱动(吸收或输出电流)八个LSTTL电路。对于EPROM型单片机,在EPROM编程期间,此引脚接收编程脉冲(功能) ③外部程序存储器读选通信号输出端,在从外部程序存储取指令(或数据)期间,在每个机器周期内两次有效。同样可以驱动八LSTTL输入。 ④ /Vpp 、 /Vpp为内部程序存储器和外部程序存储器选择端。当 /Vpp为高电平时,访问内部程序存储器,当 /Vpp 为低电平时,则访问外部程序存储器。 对于EPROM型单片机,在EPROM编程期间,此引脚上加21伏EPROM编程电源(Vpp)。 ⊙IC-8031 ☆8031/8051/8751引脚功能: Vcc:+5V电源电压。 Vss:电路接地端。 P0.0~P0.7:通道0,它是8位漏极开路的双向I/O通道,当扩展外部存贮器时,这也是低八位地址和数据总线,在编程校验期间,它输入和输出字节代码,通道0吸收/发出二个TTL 负载。 P1.0~P1.7:通道1是8位拟双向I/O通道,在编程和校验时,它发出低8位地址。通道1吸收/发出一个TTL负载。 P2.0~P2.7:通道2是8位拟双向I/O通道,当访问外部存贮器时,用作高8位地址总线。通道2能吸收/发出一个TTL负载。 P3.0~P3.7:通道3准双向I/O通道。通道3能吸收/发出一个TTL负载,P3通道的每一根线还有 ☆另一种功能: P3.0:RXD,串行输入口。 P3.1:TXD,串行输出口。 P3.2:INT0,外部中断0输入口。 P3.3:INT1,外部中断1输入口。 P3.4:T0,定时器/计数器0外部事件脉冲输入端。 P3.5:T1,定时器/计数器1外部事件脉冲输入端 P1.0-- 1 40 --VCC P1.1-- 2 39 --P0.0/AD0 P1.2-- 3 38 --P0.1/AD1 P1.3-- 4 37 --P0.2/AD2 P1.4-- 5 36 --P0.3/AD3 P1.5-- 6 35 --P0.4/AD4 RTS P1.6-- 7 34 --P0.5/AD5 CTS P1.7-- 8 33 --P0.6/AD6 RST/Vpp-- 9 32 --P0.7/AD7 I/O RXD/P3.0-- 10 31 --EA /VPP DATA TXD/P3.1-- 11 30 --ALE/PLOG INT0/P3.2-- 12 29 --PSEN INT1/P3.3-- 1 3 28 --P2.7/A15 T0/P3.4-- 14 27 --P2.6/A14 SCLK T1/P3.5-- 15 26 --P2.5/A13 WR/P 3.6-- 16 25 --P2.4/A12 RD/P3.7-- 17 24 --P2.3/A11 XTAL1-- 18 23 --P2.2/A10 XTAL 2-- 19 22 --P2.1/A9 VSS 20 21 --P2.0/A8 P3.6:WR,外部数据存贮器写脉冲。 P3.7:RD,外部数据存贮器读脉冲。 RST/VpD:引脚9,复位输入信号,振荡器工作时,该引脚上2个机器周期的高电平可以实现

松翰单片机问答集_IO口

松翰单片机问答集——IO口 Q322001. 当SONIX MCU的I/O口作OPEN DRAIN输出时,外接上拉电阻的供电电压比IC电源电压高,是否允许? Ans: 我们IC 的open drain 是属于pseudo open drain, 外接上拉电阻的电压要小于等于MCU 的VDD, 主要目的是应用在多个output 并接bus 上(例如I2C), 或者是电压比VDD低的接口电压电平的转换。用户可以通过外接三极管来解决这个问题。 Q322002. 低功耗I/O口应如何设置? Ans: 正确设定I/O口状态,可以避免I/O口的漏电流: 1.对空闲口的设置,空闲口一般设定为输入上拉或输出低电平。 2.对ADC I/O通道,应用P4CON的设定,可以避免I/O口的漏电流。 3.对于不同的外部硬件电路,考虑I/O的状态设置,设定不当,会有漏电流,特别注意上拉电阻的正确设定,若I/O 口外接低点平,又将pull-up enable会造成漏电,例如:VDD=5V 会有约5V / 100K = 50uA 漏电。 Q322003. SONIX MCU的I/O上拉电阻是多少? Ans: 此点在芯片的规格书中(电气特性章节)有所描述。 Vdd=3V时,上拉电阻典型值为200K欧姆。 Vdd=5V时,上拉电阻典型值为100K欧姆。 Q322004. 独立按键与MCU如何连接能有效避免I/O口损伤? Ans: 在产品开发时,按键是最常见的功能,由于考虑到成本等因素,很多客户都是将按键的两端分别与MCU和GND 相连,这种做法在大部分情况下是没有问题的。但是,当该产品的工作环境比较差时,比如静电、电源噪声等,此时若按键被按下,则相当于将MCU的一个I/O口直接与GND相连,此时就很可能会有瞬间大电流或高电压甚至负压灌入I/O口,造成I/O损坏。 减少这种问题的防范措施是:根据实际电路的需要,在按键与MCU的I/O之间串接100ohm ~ 1Kohm电阻,可有效避免上述问题带来的损伤。 Q322005. I/O外接下拉电阻,没有外接信号时芯片为何读不到低电平? Ans: SONIX MCU的普通I/O口内建上拉电阻,其等效阻值大概是100 Kohm@5V、200 Kohm@3V。如果客户在程序中将某I/O的上拉电阻使能,同时又在该I/O的外围接有下拉电阻,在没有信号输入的情况下,相当于内置上拉电阻与外接下拉电阻串联分压,所以会导致I/O口读不到低电平。例如,在VDD=5V的情况下,内置上

新茂SyncMOS单片机型号选型列表

SyncMOS MCU Selection Guide V e r. K 2012/1 SM59RXX 系列 (RISC 1T/2T) Part No. VCC Speed FLASH RAM Size I/O Pin Package EEPROM SPI IIC UART ISP&ICP WDT Power Down Wake-Up OPA PCA PWM ADC EEI&KBI RTC&MDU IRC ICE Function SM59R02A1 3.0/5 25MHZ 8KByte 256+1KB 36/40/44 P/J/Q/V Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI 16bit 4ch 10/16bit 8ch10bit 8ch KBI MDU Yes Dual DPTR SM59R03A1 3.0/5 25MHZ 12KByte 256+1KB 36/40/44 P/J/Q/V Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI 16bit 4ch 10/16bit 8ch10bit 8ch KBI MDU Yes Dual DPTR SM59R04A1 3.0/5 25MHZ 16KByte 256+1KB 36/40/44 P/J/Q/V Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI 16bit 4ch 10/16bit 8ch10bit 8ch KBI MDU Yes Dual DPTR SM59R04A2 3.0/5 25MHZ 16KByte 256+1KB 36/40/44 P/J/Q/V Yes Yes Yes X2 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI 16bit 4ch 10/16bit 8ch10bit 8ch KBI MDU Yes Yes Dual DPTR SM59R08/16A2 3.0/5 25MHZ 32/64KB 256+2KB 48 W/U Yes Yes Yes X2 ISP/ICP Yes(2)Reset/INT/ KBI 16bit 4ch 12/16bit 4ch10bit 8ch EEI MDU Yes Yes Dual DPTR SM59R05A3 3.0/5 25MHZ 20KByte 256+2KB 38/42/46 P/J/Q/V Yes Yes Yes X2 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI 16bit 4ch 10/16bit 8ch10bit 8ch KBI MDU Yes Yes Dual DPTR SM59R09A3 3.0/5 25MHZ 36KByte 256+2KB 38/42/46 P/J/Q/V Yes Yes Yes X2 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI 16bit 4ch 10/16bit 8ch10bit 8ch KBI MDU Yes Yes Dual DPTR SM59R16A3 3.0/5 25MHZ 64KByte 256+2KB 38/42/46 P/J/Q/V Yes Yes Yes X2 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI 16bit 4ch 10/16bit 8ch10bit 8ch KBI MDU Yes Yes Dual DPTR SM59R05A5 3.0/5 25MHZ 20KByte 256+2KB 38/42/46 P/J/Q/V Yes Yes Yes X2 ISP/ICP Yes RST/INT/ WDT/ KBI/ LVI/ RTC Yes 16bit 4ch 10/16bit 8ch10bit 8ch KBI RTC/MDU Yes Yes Dual DPTR SM59R09A5 3.0/5 25MHZ 36KByte 256+2KB 38/42/46 P/J/Q/V Yes Yes Yes X2 ISP/ICP Yes RST/INT/ WDT/ KBI/ LVI/ RTC Yes 16bit 4ch 10/16bit 8ch10bit 8ch KBI RTC/MDU Yes Yes Dual DPTR SM59R16A5 3.0/5 25MHZ 64KByte 256+2KB 38/42/46 P/J/Q/V Yes Yes Yes X2 ISP/ICP Yes RST/INT/WDT/KBI/LVI/RTC Yes 16bit 4ch 10/16bit 8ch10bit 8ch KBI RTC/MDU Yes Yes Dual DPTR SM59R05G6 2.7~5.5 25MHZ 20KByte 256+1KB 38/42/46 P/J/Q/V Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ LVI 16bit 4ch 10/16bit Yes Yes Dual DPTR SM59R09G6 2.7~5.5 25MHZ 36KByte 256+1KB 38/42/46 P/J/Q/V Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ LVI 16bit 4ch 10/16bit Yes Yes Dual DPTR SM59R16G6 2.7~5.5 25MHZ 64KByte 256+1KB 38/42/46 P/J/Q/V Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ LVI 16bit 4ch 10/16bit Yes Yes Dual DPTR SM59R02G1 2.7~5.5 25MHZ 8KByte 256Byte 38/42 P/J/Q/V Yes X1 ISP Yes RST/ INT/ WDT/ LVR 16bit 4ch 16bit Yes Dual DPTR SM39RXX 系列 (RISC 1T~8T , Low Pin Count) Part No. VCC Speed FLASH RAM Size I/O Pin Package EEPROM SPI IIC UART ISP&ICP WDT Power Down Wake-Up OPA PCA PWM ADC KBI IRC ICE Function SM39R02G1 2.7~5.5 25MHZ 2KByte 256Byte 12 N(14)/O Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ LVI Yes Yes Dual DPTR SM39R04G1 2.7~5.5 25MHZ 4KByte 256Byte 8/12 N(14)/O/M Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ LVI Yes Yes Dual DPTR SM39R2051 2.7~5.5 25MHZ 2KByte 256Byte 18 20(N/S) Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ LVI Yes Yes Dual DPTR/ SM39R4051 2.7~5.5 25MHZ 4KByte 256Byte 18 20(N/S) Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ LVI Yes Yes Dual DPTR/ SM39R08A2 2.7~5.5 25MHZ 8KByte 256Byte 18~26 N/S/K/G Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI Yes 16bit 2ch 10/16bit 8ch10bit 4-ch KBI Yes Yes Dual DPTR SM39R12A2 2.7~5.5 25MHZ 12KByte 256Byte 18~26 N/S/K/G Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI Yes 16bit 2ch 10/16bit 8ch10bit 4-ch KBI Yes Yes Dual DPTR SM39R16A2 2.7~5.5 25MHZ 16KByte 256Byte 18~26 N/S/K/G Yes Yes Yes X1 ISP/ICP Yes RST/ INT/ WDT/ KBI/ LVI Yes 16bit 2ch 10/16bit 8ch10bit 4-ch KBI Yes Yes Dual DPTR SM59XX 系列 (12T) Part No. VCC Speed FLASH RAM Size I/O Pin Package TWSI UART ISP WDT Power Down Wake-Up SPWM PWM ADC RTC Function SM5964A 3.3/5 25/40MHZ 64KByte 256+768 Byte(1)32/36P/J/Q Yes X1 ISP Reset/ INT 2-ch (5,8)bit VESA DDC/CI SM5964 5 40MHZ 64kByte 256+768 Byte 32/36 P/J/Q X1 ISP Yes(2)Reset 5-ch (5,8)-bit SM59264 5 40MHZ 64+64KB(D) 256+768 Byte(1)32/36 P/J/Q Yes X1 ISP Yes Reset 4-ch (5,8)-bit VESA DDC/CI SM59128 5 40MHZ 128KByte 256+768 Byte(1)32/36 P/J/Q Yes X1 ISP Yes Reset 4-ch (5,8)-bit VESA DDC/CI SM79XX 系列 (12T) Part No. VCC Speed FLASH RAM Size I/O Pin Package UART WDT Power Down Wake-Up SPWM PWM ADC RTC Function SM79108 3.3/5 40MHZ 8KByte 256Byte 32/36 P/J/Q X1 Yes Reset 1-ch (5,8)-bit 1-ch (5,8)bit 4-ch 8bit LCDD 4X14 SM79164 3.3/5 25/40MHZ 64KByte 256+3840B(1) 32/36 P/J/Q X1 Yes Reset 8-ch (5,8)bit SM89XX 系列 (12T) Part No. VCC Speed FLASH RAM Size I/O Pin Package UART WDT Power Down Wake-Up SPWM PWM ADC RTC Function SM894051 3.3/5 25MHZ 4KByte 128Byte 15 20(P/S)X1 Yes(2) Reset LED Drive sink 20mA SM8951A/52A 3.3/5 40MHZ 4/8KByte 256Byte 32/36 P/J/Q X1 Yes(2) Reset SM8954A/58A/516A 3.3/5 40MHZ 16/32/64KB 256+768 Byte(1) 32/36 P/J/Q X1 Yes Reset 5-ch (5,8)-bit SM89516 3.3/5 25MHZ 64KByte 256+768 Byte 32/36 P/J/Q X1 Yes(2) Reset SM89S16R1 3.3/5 40MHZ 64KByte 256+768 Byte(1) 32/36 P/J/Q X1 Reset/ RTC/ INT 2-ch (5,8)bit 4-ch 6bit RTC (1): Expanding RAM is default disable (2): WDT Clock is from External X’tal WDT Clock is from Internal X’tal define 250KHz (without (2) ) IIC =TWSI =Two-Wire Series Interface EX_INT=External Interrupt Wake-Up ADC = Analog and Digital Converter (類比數位轉換器) KBI=Keyboard Interface=EEI (擴充外部中斷) RTC = Real Time Clock (時鐘裝置) MDU=Multiplication-Division unit (硬件乘除法器) PCA=Programmable Counter Array (16bit Timer 2) =capture 、compare 、clock out 、16bit PWM SM59R16A5ihhkL yymmv (yy: year ,mm: month ,v: version) i: process ( L: 3.3V C: 5V W:2.7~5.5 ) hh: Max Speed (Before SM59RxxG6) or Pin Count (After SM39R & SM59RxxG6) k: package type { J:44(PLCC) M:10(MSOP-118mil) N:14/20/24/28(PDIP-300mil) O:14(SOP-150mil) {P:40(PDIP) Q:44(QFP) U:64(LQFP) V:48(LQFP) W:64(TQFP) S:20/24/28(SOP-300mil)} {K:24/28(Skinny PDIP-300mil) G:20(SSOP-150mil } L:PB Free {No text is Non-PB Free, "P" is PB Free} SZ恒信宇电子有限公司 http://wenku.baidu.com/view/44b3d4d250e2524de5187eb0.html 技术信息咨询:1091944079@Q Q.COM