运放差分放大电路原理

Differens Amplifier

差分放大电路

一. 实验目的:

1. 掌握差分放大电路的基本概念;

2. 了解零漂差生的原理与抑制零漂的方法;

3. 掌握差分放大电路的基本测试方法。 二. 实验原理:

1. 由运放构成的高阻抗差分放大电路

图为高输入阻抗差分放大器,应用十分广泛.从仪器测量放大器,到特种测量放大器,几乎都 能见到其踪迹。

nz

R4

R2 R T

V I R1//R2 = R3//R4

For mini mum offset

error due to input bias current

TL/H/7057-3

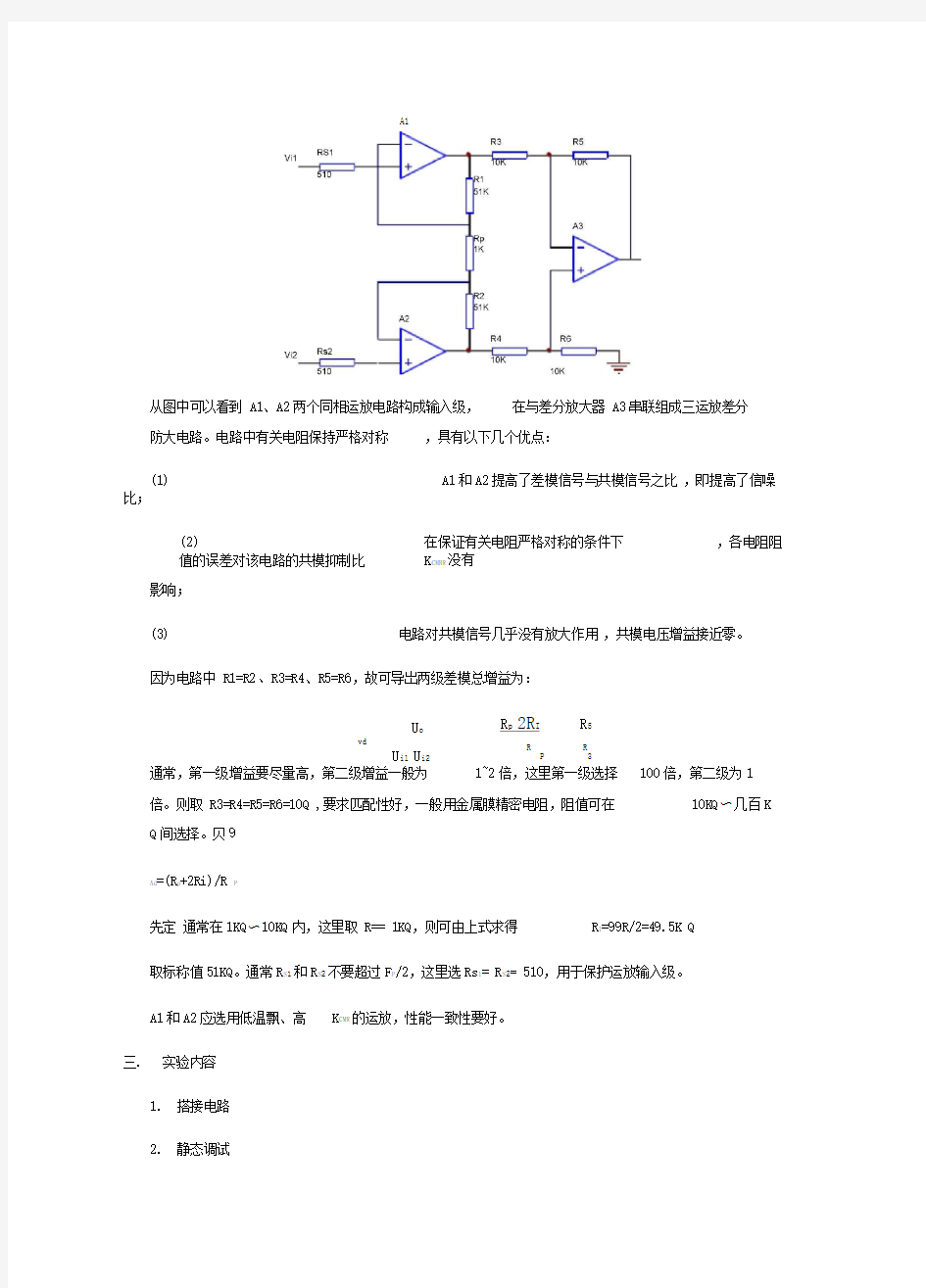

从图中可以看到 A1、A2两个同相运放电路构成输入级, 在与差分放大器 A3串联组成三运放差分

防大电路。电路中有关电阻保持严格对称

,具有以下几个优点:

(1) A1和A2提高了差模信号与共模信号之比 ,即提高了信噪

比;

(2)

在保证有关电阻严格对称的条件下 ,各电阻阻

值的误差对该电路的共模抑制比 K CMRR 没有

影响; (3)

电路对共模信号几乎没有放大作用 ,共模电压增益接近零。

因为电路中 R1=R2、R3=R4、R5=R6,故可导岀两级差模总增益为:

通常,第一级增益要尽量高,第二级增益一般为

1~2倍,这里第一级选择 100倍,第二级为1

倍。则取 R3=R4=R5=R6=10Q ,要求匹配性好,一般用金属膜精密电阻,阻值可在 10KQ ?几百K

Q 间选择。贝9

Ad

=(R p +2Ri)/R P

先定 通常在1KQ ?10KQ 内,这里取 R== 1KQ ,则可由上式求得

R 1=99R/2=49.5K Q

取标称值51KQ 。通常R S 1和R S 2不要超过F P /2,这里选Rs 1= R S 2= 510,用于保护运放输入级。 A1和A2应选用低温飘、高 K CMR 的运放,性能一致性要好。

三. 实验内容

1. 搭接电路

2. 静态调试

vd

U o

U il U i2

R p 2R I

R 5

R

P

R 3

A1

要求运放各管脚在零输入时,电位正常,与估算值基本吻合。

3.动态调试

根据电路给定的参数,进行高阻抗差分放大电路的输出测量。可分为差模、共模方式输入, 自拟实验测试表格,将测试结果记录在表格中。

1实验数据测量

改变输入信号,测量高阻抗差分放大电路的输出。输入数据表格如下:

正弦信号位与V i相反

正弦信号