数字匹配滤波器的优化设计与FPGA实现

●主题论文

1

引言

在通信系统中,匹配滤波器的应用十分广泛,尤

其在扩频通信如在CDMA系统中,用于伪随机序列(通常是m序列)的同步捕获。

匹配滤波器是扩频通信中的关键部件,它的性能直接影响到通信的质量。本文从数字匹配滤波器的理论及结构出发,讨论了它在数字通信直扩系统中的应用,并对其基于FPGA的具体实现进行了优化。

2

数字匹配滤波捕获技术

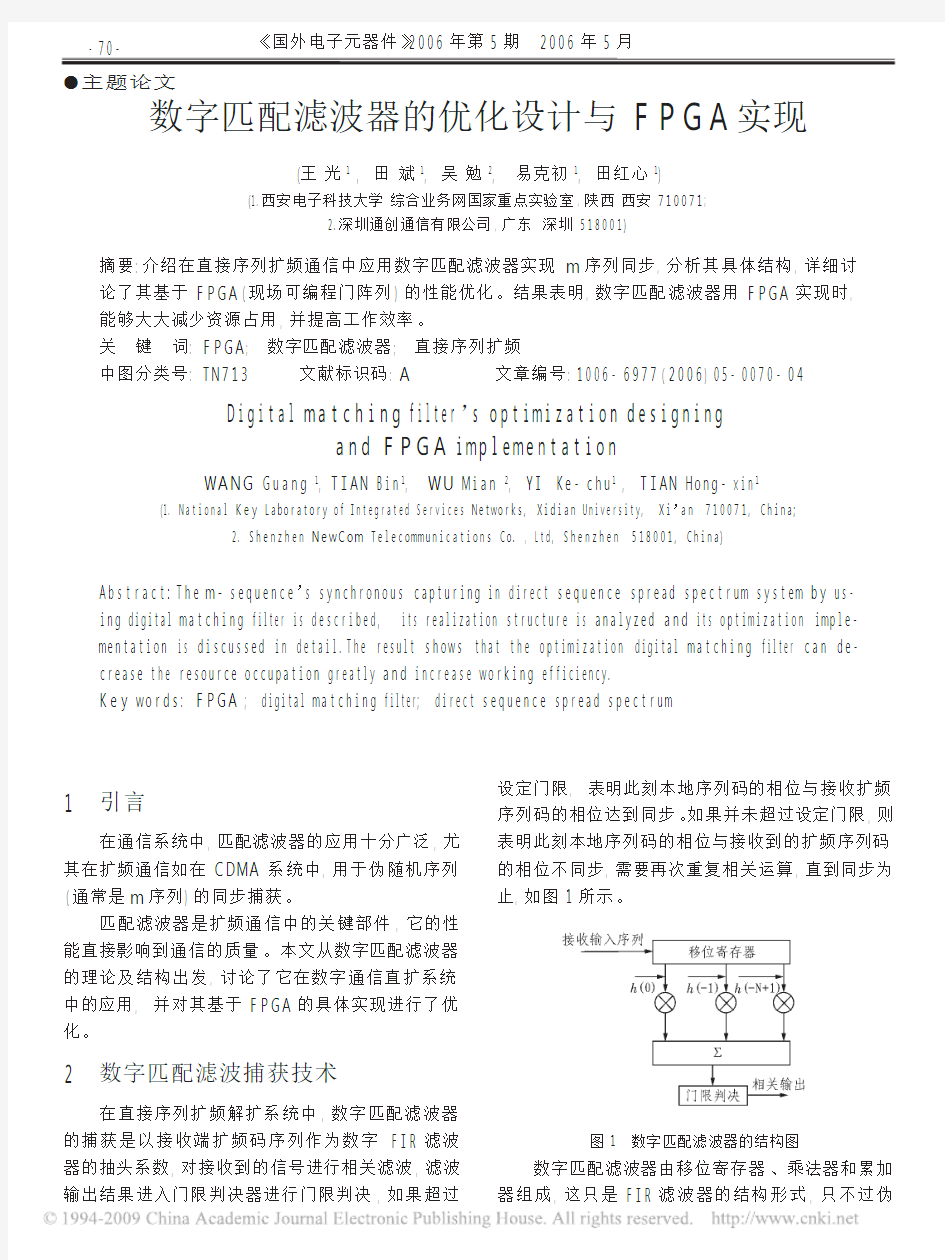

在直接序列扩频解扩系统中,数字匹配滤波器

的捕获是以接收端扩频码序列作为数字FIR滤波器的抽头系数,对接收到的信号进行相关滤波,滤波输出结果进入门限判决器进行门限判决,如果超过

设定门限,表明此刻本地序列码的相位与接收扩频序列码的相位达到同步。如果并未超过设定门限,则表明此刻本地序列码的相位与接收到的扩频序列码的相位不同步,需要再次重复相关运算,直到同步为止,如图1所示。

数字匹配滤波器由移位寄存器、乘法器和累加器组成,这只是FIR滤波器的结构形式,只不过伪

数字匹配滤波器的优化设计与FPGA实现

(王光1,田斌1,吴勉2,

易克初1,田红心1)

(1.西安电子科技大学综合业务网国家重点实验室,陕西西安710071;

2.深圳通创通信有限公司,广东深圳518001)

摘要:介绍在直接序列扩频通信中应用数字匹配滤波器实现m序列同步,分析其具体结构,详细讨论了其基于FPGA(现场可编程门阵列)的性能优化。结果表明,数字匹配滤波器用FPGA实现时,能够大大减少资源占用,并提高工作效率。关

键

词:FPGA;数字匹配滤波器;直接序列扩频

中图分类号:TN713

文献标识码:A

文章编号:1006-6977(2006)05-0070-04

Digitalmatchingfilter’soptimizationdesigning

andFPGAimplementation

WANGGuang1,TIANBin1,

WUMian2,YIKe-chu1,TIANHong-xin1

(1.NationalKeyLaboratoryofIntegratedServicesNetworks,XidianUniversity,Xi’an710071,China;

2.ShenzhenNewComTelecommunicationsCo.,Ltd,Shenzhen518001,China)

Abstract:Them-sequence’ssynchronouscapturingindirectsequencespreadspectrumsystembyus-

ingdigitalmatchingfilterisdescribed,itsrealizationstructureisanalyzedanditsoptimizationimple-mentationisdiscussedindetail.Theresultshowsthattheoptimizationdigitalmatchingfiltercande-creasetheresourceoccupationgreatlyandincreaseworkingefficiency.

Keywords:FPGA;digitalmatchingfilter;directsequencespreadspectrum

图1

数字匹配滤波器的结构图

码寄存器中的系数为-1或+1,实际并不是真正意义上的乘法。伪码寄存器中的数据可以由一种伪随机序列发生器产生。

数字匹配滤波器的表达式为:

其中,x(n)为输入信号;h(-i)为滤波系数,由接收端扩频码决定,取值-1或+1,m序列码元为1,取值为+1,m序列码元为0,取值为-1。匹配滤波器的长度N等于扩频比,也就是对于每一信息符号的扩频码元数,即Tb/Tc。当输入信号{x(n)}与本地扩频码{h

(-i)}匹配时,时输出Z达到最大,超出预先设定的门

限,表示捕获成功。

很显然,数字匹配滤波器中的关键部件是乘法器和累加器,而移位寄存器可以由信号的相互移位来实现,例如要实现8bit串行数据的移位,假设输入数据序列为din,移位寄存器中的信号为d0,d1,

d2,d3,d4,d5,d6,d7,用VHDL语言中的进程语句

实现程序为[1]:

process(clk)begin

if(clk’eventandclk=‘1’)then

d7<=d6;d6<=d5;d5<=d4;d4<=d3;d3<=d2;d2<=d1;d1<=d0;d0<=din;endif;endprocess;

每来一个时钟信号,信号同时改变1次,这就实现了和移位寄存器相同的功能。这样的进程实现并不需要太多的逻辑单元。

所以影响资源占用和工作效率的主要是乘法器和累加器。下面讨论就乘法器和累加器分别加以讨论,研究其对资源和效率的影响。

3

乘法器

由于此处采用的是0,1的二进制系统,所以将

逻辑0映射为实际电平-1,逻辑1映射为实际电

平+1,也就是伪码寄存器中的系数。

移位寄存器抽头输出为有符号二进制补码,采用乘法器实现相乘运算时,如果伪码较长,则需要耗费太多的逻辑单元且运行速度过慢。

已经知道,一个数乘以1不改变原值,而乘以-

1则改变符号,因为移位寄存器抽头系数只能是1

和-1,可以考虑用二进制的补码运算来代替相乘1和-1运算,这就避免了相乘运算对资源的大量耗费,并能提高运算速度。

可以看到,伪码寄存器中的系数为+1或-1,如对移位抽头输出进行乘1运算,相当于不改变原补码值,而对移位抽头输出进行乘-1运算,则相当于对原补码数值改变符号,并对低位二进制码元求其补码值。下面证明上述结论[2]。

假设二进制补码数为

x=xn-1xn-2xn-3…x2x1x0(2)最高位xn-1为符号位,其取值为0或1,0代表

正数,1代表负数。

不失一般性,设xn-2,xn-3,x1,x0均为1,x2到xn-4

均设为0,则二进制补码数x的后n-1位代表的真值为

2n-2+2n-3+21+20

当最高位xn-1=0时,若移位抽头输出系数为1,则x代表的正数乘1后仍然是xn-2+2n-3+21+20,正数

的补码表示还是x。

若移位抽头输出系数为-1,x代表的正数和-1相乘后变为负数,取x的后n-1位的补码值,可以表示为2n-4+2n-3+…+23+20,改变x最高位的符号位为

1,取2n-4+2n-3+…+23+20的二进制表示作为x的后(n-1)位,即为x与-1相乘的补码表示;

当最高位xn-1=1时,若移位抽头输出系数为1,则x代表的负数乘1后的真值仍然是x的后n-1位的补码值2n-4+2n-3+…+23+20,负数的补码表示还是x。

若移位抽头输出系数为-1,x代表的负数和-1相乘后变为正数,取x的后n-1位的补码值,可以表示为2n-4+2n-3+…+23+20,改变x最高位的符号位为

0,取2n-4+2n-3+…+23+20的二进制表示作为x的后(n-1)位,即为x与-1相乘的补码表示。

结论成立,二进制求补运算代替乘法器的处理框图为如图2所示。

综上所述,在数字匹配滤波器中,因为滤波系数即移位抽头系数取值只能为1或-1,所以将有符号

图2

补码器的结构

数的二进制补码的乘法运算变为求补码运算是完全可行的,这就避免了乘法运算对于资源的大量需求,运算速度也可大大提高。

在补码运算中,对每个移位抽头输出同时并行运算,并在后两个时钟得到并行求补码运算输出数据。

传统设计乘法器时,输入n1,n2位的2路有符号补码,结果输出为n1+n2位二进制补码数据。

随着移位寄存器输入有符号二进制补码矢量数据,时钟改变一次,移位寄存器每个抽头输出均和相应的抽头系数做一次相乘运算。

求补码运算代替乘法器时,不同于传统的乘法器设计,寄存器中每一数据只需求其补码即可,省略了相乘运算。从根本上说,用求补代替相乘运算只是功能相同,但可以大大减少资源浪费并提高运算速度,所以有很大的应用优势。

4

累加器

数字匹配滤波器的移位寄存器每一级抽头进行

1次乘法运算,结果输出到累加器进行累加,当运算

到最后一级时,输出累加结果,送入门限判决器进行判决。

当对2个二进制补码相加时,若2个加数都为

Bbit,考虑到数据可能溢出,则加法器的输出只需要(B+1)bit;而当3个bit二进制补码相加时,输出则需要(B+2)bit。通过观察可以发现:2N个Bbit二进制补码的值可以用(B+N)bit二进制表示。4.1传统的累加器设计

考虑到传统累加器数据可能溢出,故将数据位展宽,比如在本仿真中,63个4位有符号补码求和,最后结果最多为4+6位,其中4为每一加数的位数,因为26<64,故扩展位为6位。所以计算,如果数据位不足10位,正数在数据前加0,负数在数据前加1,这样每一数据都是10位(包括符号位),不用考虑溢出问题,完全用62个10位加法器可以实现。

4.2较优的累加器设计

随着移位级数的增加,加法器的位数当然也要相应增加,第1级加法器用(B+1)位,第2、3级用(B+

2)位,第4级到第7级用(B+3)位,后面依次类推。这

样设计,每一级并没有用考虑溢出结果的最多位的

加法器,而是递推增加,可以减少资源浪费。

4.3优化的累加器设计

将匹配滤波器的乘法器输出数据进行分组,并执行加法运算,第一级的加法器用(B+1)位,第二级用位,第三级用(B+3)位,后面依次类推。每一级的加法器数量是前面的大约一半,依几何级数递减,这样的设计在低位相加时用了较多的加法器并以几何级数递减,也就避免了高位相加的资源浪费。

以63位m序列为例,设有符号补码数为B位:将前62位输入分为2组,每一组输入和另一组中相应输入作相加运算,总共用到31个(B+1)位加法器;

余1位输入和31个(B+1)位加法器输出再次分组,用到16个(B+2)位加法器;

16个(B+2)位加法器输出再次分组,用到8个

(B+3)位加法器;

16个(B+2)位加法器输出再次分组,用到8个(B+3)位加法器;

8个(B+2)位加法器输出再次分组,用到4个

(B+4)位加法器;

4个(B+4)位加法器输出再次分组,用到2个(B+5)位加法器;

2个(B+5)位加法器输出再次分组,用到1个(B+6)位加法器。

63位累加器占用加法器的比较如表1所示。

较优累加器的运算形式是串行,而优化累加器的运算形式是并行。

可以很明显看出,优化的累加器比较优的累加

器更能减少资源占用,运行效率也可大大提高。

4.4Quatus模块化设计法

Quatus仿真软件的MegaWizardPlug-InManag-er中提供了parallel_add模块,用户可以自由设计输

入数据位宽,累加数据个数,定义累加输入数据类型,模块最终自动生成适当位宽的数据输出(考虑了所有的数据溢出)。

与上面的累加器设计比较,这样的设计很方便,可读性强,程序简练。实际中逻辑单元占用也不是很多,只比上面多出10%左右。所以,如果不是特别关注资源占用问题,这样的设计也不失为一种好方法。

5

仿真实验

笔者通过Quatus仿真实验验证了优化数字匹

配滤波器的性能。

仿真中采用Altera公司的FPGA,利用6级线性移位反馈寄存器生成长度为63的m序列。

图3是数字匹配滤波器的2个周期的相关同步过程,图4是放大后的相关同步。

在本次仿真中,clk为时钟信号,address为地址信号,输入信号为din,数字匹配滤波器抽头信号为

m。为了方便起见,做了2个只读存储器din_rom和

m_rom。din_rom中存储了63bit的m序列的二进制补码表示作为输入,其中0表示11,1表示01,16

进制表示分别为3和1。m_rom中存储了63bitm序列的二进制码元,作为数字匹配滤波器的抽头同步模块的输入。result为计算出的相关值,tongbu为同步信号。

每来一个时钟脉冲,地址加1,依次读取

din_rom中的数据,图4中的地址为10进制表示。

m_rom地址始终置

“0”,图3和图4中是m_rom中二进制数据的16进制表示。

63级移位滤波器同时做补码运算,当m_rom输出的二进制矢量位为1时,不改变相应位原补码值,

矢量位为0时,求其相反数(-1的相反数为1,1的相反数为-1)的补码值。将相关门限设为63,当同步未完成时,相关值信号result的16进制表示为FF,二进制即为1111111(1表示正数);当同步完成时,相关值信号result的16进制表示为3F,二进制即为0111111(0表示正数)。

每个时钟脉冲,计算1次相关系数,并和判决门限比较,高于门限表示完成同步捕获,否则表示没有同步,继续运算,直到达到同步为止。

6

结束语

本文从理论和实践方面分别讨论了数字匹配

滤波器在设计中遇到的问题,仿真实验证明该设计在节省硬件资源和提高工作效率方面都有其突出的优点。参考文献:

[1]侯伯亨,顾新.VHDL硬件描述语言与数字逻辑电路设计[M].西安:西安电子科技大学出版社,1999.

[2]褚振勇,翁木云.FPGA设计及应用[M].西安:西安电子科技大学出版社,2002.

作者简介:王光(1977-)男,硕士研究生,主要研究方向为数据通信网与通信信号处理;田斌,男,硕士生导师,主要研究方向为数据通信网与通信信号处理。

吴勉,男,副总工程师,主要研究方向为通信信号处理。易克初,男,博士生导师,主要研究方向为语音通信,卫星通信与通信信号处理;田红心,男,硕士生导师,主要研究方向为卫星通信与通信信号处理。

收稿日期:2005-11-08

咨询编号:060525

图3

两个周期的相关同步

图4

放大后的相关同步

实验五:FIR数字滤波器设计与软件实现

实验五:FIR数字滤波器设计与软件实现 一、实验指导 1.实验目的 (1)掌握用窗函数法设计FIR数字滤波器的原理和方法。 (2)掌握用等波纹最佳逼近法设计FIR数字滤波器的原理和方法。 (3)掌握FIR滤波器的快速卷积实现原理。 (4)学会调用MATLAB函数设计与实现FIR滤波器。 2.实验容及步骤 (1)认真复习第七章中用窗函数法和等波纹最佳逼近法设计FIR数字滤波器的原理; (2)调用信号产生函数xtg产生具有加性噪声的信号xt,并自动显示xt及其频谱,如图1所示; 图1 具有加性噪声的信号x(t)及其频谱如图 (3)请设计低通滤波器,从高频噪声中提取xt中的单频调幅信号,要求信号幅频失真小于0.1dB,将噪声频谱衰减60dB。先观察xt的频谱,确定滤波器指标参数。 (4)根据滤波器指标选择合适的窗函数,计算窗函数的长度N,调用MATLAB函数fir1设计一个FIR低通滤波器。并编写程序,调用MATLAB快速卷积函数fftfilt实现对xt的滤波。绘图显示滤波器的频响特性曲线、滤波器输出信号的幅频特性图和时域波形图。 (4)重复(3),滤波器指标不变,但改用等波纹最佳逼近法,调用MATLAB函数remezord 和remez设计FIR数字滤波器。并比较两种设计方法设计的滤波器阶数。 提示:○1MATLAB函数fir1的功能及其调用格式请查阅教材; ○2采样频率Fs=1000Hz,采样周期T=1/Fs; ○3根据图1(b)和实验要求,可选择滤波器指标参数:通带截止频率fp=120Hz,阻带截

至频率fs=150Hz ,换算成数字频率,通带截止频率p 20.24p f ωπ=T =π,通带最大衰为0.1dB ,阻带截至频率s 20.3s f ωπ=T =π,阻带最小衰为60dB 。 ○ 4实验程序框图如图2所示,供读者参考。 图2 实验程序框图 4.思考题 (1)如果给定通带截止频率和阻带截止频率以及阻带最小衰减,如何用窗函数法设计线性相位低通滤波器?请写出设计步骤. (2)如果要求用窗函数法设计带通滤波器,且给定通带上、下截止频率为pl ω和pu ω,阻带上、下截止频率为sl ω和su ω,试求理想带通滤波器的截止频率cl cu ωω和。 (3)解释为什么对同样的技术指标,用等波纹最佳逼近法设计的滤波器阶数低? 5.信号产生函数xtg 程序清单(见教材) 二、 滤波器参数及实验程序清单 1、滤波器参数选取 根据实验指导的提示③选择滤波器指标参数: 通带截止频率fp=120Hz ,阻带截至频率fs=150Hz 。代入采样频率Fs=1000Hz ,换算成数字频率,通带截止频率p 20.24p f ωπ=T =π,通带最大衰为0.1dB ,阻带截至频率

基于FPGA的FIR数字滤波器设计

1、F PGA技术简介 现场可编程门阵列FPGA是80年代末开始使用的大规模可编程数字IC器件,它充分利用EDA技术进行器件的开发与应用。用户借助于计算机不仅能自行设计自己的专用集成电路芯片,还可在计算机上进行功能仿真和时序仿真,及时发现问题,调整电路,改进设计方案。这样,设计者不必动手搭接电路、调试验证,只需短时间内在计算机上操作即可设计出与实际系统相差无几的理想电路。而且,FPGA器件采用标准化结构,体积小、集成度高、功耗低、速度快,可无限次反复编程,因此成为科研产品开发及其小型化的首选器件,其应用极为广泛。 3.1 FPGA工作原理 FPGA采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输入输出模块IOB(Input Output Block)和内部连线(Interconnect)三个部分。现场可编程门阵列(FPGA)是可编程器件,与传统逻辑电路和门阵列(如PAL,GAL及CPLD器件)相比,FPGA具有不同的结构。FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能又可实现时序逻辑功能的基本逻辑单元模块,这些模块间利用金属连线互相连接或连接到I/O模块。FPGA的逻辑是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值决定了逻辑单元的逻辑功能以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。 3.2 FIR滤波器特点 1)采用FPGA设计ASIC电路(专用集成电路),用户不需要投片生产,就能得到合用的芯片。 2)FPGA可做其它全定制或半定制ASIC电路的中试样片。 3)FPGA内部有丰富的触发器和I/O引脚。 4)FPGA是ASIC电路中设计周期最短、开发费用最低、风险最小的器件之一。 5) FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。同时,FPGA还存在以下五大优势。 1)性能:利用硬件并行的优势,FPGA打破了顺序执行的模式,在每个时钟周 期内完成更多的处理任务,超越了数字信号处理器(DSP)的运算能力。著名 的分析与基准测试公司BDTI,发布基准表明在某些应用方面,FPGA每美元的 处理能力是DSP解决方案的多倍。2在硬件层面控制输入和输出(I/ O)为满足应用需求提供了更快速的响应时间和专业化的功能。 2)上市时间:尽管上市的限制条件越来越多,FPGA技术仍提供了灵活性和快 速原型的能力。用户可以测试一个想法或概念,并在硬件中完成验证,而无需

数字滤波器的MATLAB设计与实现.

数字滤波器的MATLAB设计与实现 数字滤波器的MATLAB设计与实现 类别:电子综合 引言 随着信息时代和数字世界的到来,数字信号处理已成为今一门极其重要的学科和技术领域。数字信号处理在通信、语音、图像、自动控制、雷达、军事、航空航天、医疗和家用电器等众多领域得到了广泛的应用。在数字信号处理应用中,数字滤波器十分重要并已获得广泛应用。 1 数字滤波器的设计1.1 数字滤波器设计的基本步骤数字滤波器根据其冲激响应函数的时域特性,可分为两种,即无限长冲激响应(IIR)滤波器和有限长冲激响应(FIR)滤波器。IIR滤波器的特征是,具有无限持续时间冲激响应。种滤波器一般需要用递归模型来实现,因而有时也称之为递归滤波器。FIR滤波器的冲激响应只能延续一定时间,在工程实际中可以采用递归的方式实现,也可以采用非递归的方式实现。数字滤波器的设计方法有多种,如双线性变换法、窗函数设计法、插值逼近法和Chebyshev逼近法等等。随着MATLAB软件尤其是MATLAB的信号处理工作箱的不断完善,不仅数字滤波器的计算机辅助设计有了可能,而且还可以使设计达到最优化。数字滤波器设计的基本步骤如下:(1)确定指标在设计一个滤波器之前,必须首先根据工程实际的需要确定滤波器的技术指标。在很多实际应用中,数字滤波器常常被用来实现选频操作。因此,指标的形式一般在频域中给出幅度和相位响应。幅度指标主要以两种方式给出。第一种是绝对指标。它提供对幅度响应函数的要求,一般应用于FIR滤波器的设计。第二种指标是相对指标。它以分贝值的形式给出要求。在工程实际中,这种指标最受欢迎。对于相位响应指标形式,通常希望系统在通频带中人有线性相位。运用线性相位响应指标进行滤波器设计具有如下优点:①只包含实数算法,不涉及复数运算;②不存在延迟失真,只有固定数量的延迟;③长度为N 的滤波器(阶数为N-1),计算量为N/2数量级。因此,本文中滤波器的设计就以线性相位FIR滤波器的设计为例。(2)逼近确定了技术指标后,就可以建立一个目标的数字滤波器模型。通常采用理想的数字滤波器模型。之后,利用数字滤波器的设计方法,设计出一个实际滤波器模型来逼近给定的目标。(3)性能分析和计算机仿真上两步的结果是得到以差分或系统函数或冲激响应描述的滤波器。根据这个描述就可以分析其频率特性和相位特性,以验证设计结果是否满足指标要求;或者利用计算机仿真实现设计的滤波器,再分析滤波结果来判断。 1.2 滤波器的MATLAB设计(1)MATLAB MATLAB是一套用于科学计算的可视化高性能语言与软件环境。它集数值分析、矩阵运算、信号处理和图形显示于一体,构成了一个界面友好的用户环境。它的信号处理工具箱包含了各种经典的和现代的数字信号处理技术,是一个非常优秀的算法研究与辅助设计的工具。在设计数字滤波器时,通常采用MATLAB来进行辅助设计和仿真。(2)FIR滤波器的MATLAB设计下面以设计线性相位FIR滤波器为例介绍具体的设计方法。线性相位FIR滤波器通常采用窗函数法设计。窗函数法设

IIR数字滤波器设计原理

IIR 数字滤波器设计原理 利用双线性变换设计IIR 滤波器(只介绍巴特沃斯数字低通滤波器的设计),首先要设计出满足指标要求的模拟滤波器的传递函数)(s H a ,然后由)(s H a 通过双线性变换可得所要设计的IIR 滤波器的系统函数)(z H 。 如果给定的指标为数字滤波器的指标,则首先要转换成模拟滤波器的技术指标,这里主要是边界频率 s p w w 和的转换,对s p αα和指标不作变化。边界频率的转换关系为)21tan(2w T =Ω。接着,按照模拟低通滤波器的技术指标根据相应 设计公式求出滤波器的阶数N 和dB 3截止频率c Ω;根据阶数N 查巴特沃斯归一 化低通滤波器参数表,得到归一化传输函数 )(p H a ;最后,将c s p Ω=代入)(p H a 去归一,得到实际的模拟滤波器传输函数)(s H a 。之后,通过双线性变换法转换公式 11 112--+-=z z T s ,得到所要设计的IIR 滤波器的系统函数)(z H 。 步骤及内容 1) 用双线性变换法设计一个巴特沃斯IIR 低通数字滤波器。设计指标参数为: 在通带内频率低于π2.0时,最大衰减小于dB 1;在阻带内[]ππ,3.0频率区间上,最小衰减大于dB 15。 2) 以π02.0为采样间隔,绘制出数字滤波器在频率区间[]2/,0π上的幅频响应特 性曲线。 3) 程序及图形 程序及实验结果如下: %%%%%%%%%%%%%%%%%%

%iir_1.m %lskyp %%%%%%%%%%%%%%%%%% rp=1;rs=15; wp=.2*pi;ws=.3*pi; wap=tan(wp/2);was=tan(ws/2); [n,wn]=buttord(wap,was,rp,rs,'s'); [z,p,k]=buttap(n); [bp,ap]=zp2tf(z,p,k); [bs,as]=lp2lp(bp,ap,wap); [bz,az]=bilinear(bs,as,.5); [h,f]=freqz(bz,az,256,1); plot(f,abs(h)); title('双线性z 变换法获得数字低通滤波器,归一化频率轴'); xlabel('\omega/2\pi'); ylabel('低通滤波器的幅频相应');grid; figure; [h,f]=freqz(bz,az,256,100); ff=2*pi*f/100; absh=abs(h); plot(ff(1:128),absh(1:128)); title('双线性z 变换法获得数字低通滤波器,频率轴取[0,\pi/2]'); xlabel('\omega'); ylabel('低通滤波器的幅频相应');grid on; 运行结果: 00.050.10.150.20.25 0.30.350.40.450.500.1 0.2 0.3 0.40.50.60.70.8 0.9 1 双线性z 变换法获得数字低通滤波器,归一化频率轴 ω/2π低通滤波器的幅频相应

数字滤波器的优化设计

数字滤波器的优化设计浅析 201120003025 何志会

数字滤波器的优化设计浅析 摘要 当前,在数字信号处理和电子应用技术领域,数字滤波器以其精度高、灵活性好、便于大规模集成等突出优点,占据了至关重要的地位。按冲击响应持续时间,数字滤波器可分为有限冲击响应(FIR)滤波器和无限冲击响应(IIR)滤波器。传统的数字滤波器的设计方法有窗函数法、频率采样法和等波动最佳逼近法等。但是随着时代的发展,应用领域的广泛增加、信号处理要求变高以及计算复杂程度的不断提高,对于数字滤波器软件和硬件的要求也越来越专业、复杂。因此,数字滤波器的优化设计也显得更加重要。近年来,国内外对数字滤波器的优化算法进行了较多的研究,提出了很多优化方法和算法,如:人工鱼群算法、粒子群算法、遗传算法、最小P误差法、小波逼近法等。这些算法大大提高了数字滤波器的应用范围,使结果更加逼近于目标函数。硬件上,FPGA以其体积小、速度快、重量轻、功耗低、可靠性高、成本低等优点在数字滤波器上得到应用,具有很好的发展前景。 关键词:数字滤波器;优化;算法

Optimization design of FIR digital filter Abstract At present, the digital filter with its high precision, flexibility, ease of large-scale integration and other advantages, occupies a crucial position in the field of digital signal processing and application of technology.According to the duration of the impulse response, digital filter can be divided into finite impulse response (FIR) filters and infinite impulse response (IIR) filter. Traditional methods of digital filter design use window function method, sampling method, frequency fluctuations and the best approximation method. But with the development of the times, a wide range of applications increases, the signal processing requirements of high change and increasing complexity of the calculations for the digital filter software and hardware ,requirements have become more specialized and complex. Therefore, the digital filter design optimization is even more important. In recent years, domestic and international digital filter optimization algorithm for more research, made a lot of optimization methods and algorithms, such as: artificial fish school algorithm, particle swarm optimization, genetic algorithm, the smallest P error method, wavelet approximation method . These algorithms greatly improve the application of digital filters, so that the results more close to the target function. Hardware, FPGA with its small size, fast, light weight, low power consumption, high reliability and low cost have been applied in the digital filter, with good prospects for development. Key words:Digital filter ;Optimization;;algorithm

IIR数字滤波器的设计实验报告

IIR数字滤波器的设计 一、实验目的: 掌握冲激相应不变法和双线性变换法设计IIR数字滤波器的原理和方法; 观察冲激相应不变法和双线性变换法设计IIR数字滤波器的频率特性; 了解冲激相应不变法和双线性变换法的特点和区别。 二、实验原理: 无限长单位冲激响应(IIR)数字滤波器的设计思想: a)设计一个合适的模拟滤波器 b)利用一定的变换方法将模拟滤波器转换成满足预定指 标的数字滤波器 切贝雪夫I型:通带中是等波纹的,阻带是单调的

切贝雪夫II型:通带中是单调的,阻带是等波纹的 1.用冲击响应不变法设计一个低通切贝雪夫I型数字滤波器通带上限截止频率为400Hz 阻带截止频率为600Hz 通带最大衰减为0.3分贝 阻带最小衰减为60分贝 抽样频率1000Hz 2.用双线性变换法设计切贝雪夫II型高通滤波器 通带截止频率2000Hz 阻带截止频率1500Hz 通带最大衰减0.3分贝 阻带最小衰减50分贝 抽样频率20000Hz 四、实验程序:

1) Wp=2*pi*400; Ws=2*pi*600; Rp=0.3; Rs=60; Fs=1000; [N,Wn]=cheb1ord(Wp,Ws,Rp,Rs,'s'); [Z,P,K]=cheb1ap(N,Rp); [A,B,C,D]=zp2ss(Z,P,K); [At,Bt,Ct,Dt]=lp2lp(A,B,C,D,Wn); [num1,den1]=ss2tf(At,Bt,Ct,Dt); [num2,den2]=impinvar(num1,den1,Fs); [H,W1]=freqs(num1,den1); figure(1) subplot(2,1,1); semilogx(W1/pi/2,20*log10(abs(H)));grid; xlabel(' 频率/ Hz'); ylabel(' 模拟滤波器幅值(db)'); [H,W2]=freqz(num2,den2,512,'whole',Fs); subplot(2,1,2); plot(W2,20*log10(abs(H)));grid; xlabel(' 频率/ Hz');

简单低通滤波器设计及matlab仿真

东北大学 研究生考试试卷 考试科目: 课程编号: 阅卷人: 考试日期: 姓名:xl 学号: 注意事项 1.考前研究生将上述项目填写清楚. 2.字迹要清楚,保持卷面清洁. 3.交卷时请将本试卷和题签一起上交. 4.课程考试后二周内授课教师完成评卷工作,公共课成绩单与试卷交研究生院培养办公室, 专业课成绩单与试卷交各学院,各学院把成绩单交研究生院培养办公室. 东北大学研究生院培养办公室

数字滤波器设计 技术指标: 通带最大衰减: =3dB , 通带边界频率: =100Hz 阻带最小衰减: =20dB 阻带边界频率: =200Hz 采样频率:Fs=200Hz 目标: 1、根据性能指标设计一个巴特沃斯低通模拟滤波器。 2、通过双线性变换将该模拟滤波器转变为数字滤波器。 原理: 一、模拟滤波器设计 每一个滤波器的频率范围将直接取决于应用目的,因此必然是千差万别。为了使设计规范化,需要将滤波器的频率参数作归一化处理。设所给的实际频 率为Ω(或f ),归一化后的频率为λ,对低通模拟滤波器令λ=p ΩΩ/,则1 =p λ, p s s ΩΩ=/λ。令归一化复数变量为p ,λj p =,则p p s j j p Ω=ΩΩ==//λ。所以巴 特沃思模拟低通滤波器的设计可按以下三个步骤来进行。 (1)将实际频率Ω规一化 (2)求Ωc 和N 11010/2-=P C α s p s N λααlg 1 10 110lg 10 /10/--= 这样Ωc 和N 可求。 p x fp s x s f

根据滤波器设计要求=3dB ,则C =1,这样巴特沃思滤波器的设计就只剩一个参数N ,这时 N p N j G 222 )/(11 11)(ΩΩ+= += λλ (3)确定)(s G 因为λj p =,根据上面公式有 N N N p j p p G p G 22)1(11 )/(11)()(-+= += - 由 0)1(12=-+N N p 解得 )221 2exp(πN N k j p k -+=,k =1,2, (2) 这样可得 1 )21 2cos(21 ) )((1 )(21+-+-= --= -+πN N k p p p p p p p G k N k k 求得)(p G 后,用p s Ω/代替变量p ,即得实际需要得)(s G 。 二、双线性变换法 双线性变换法是将s 平面压缩变换到某一中介1s 平面的一条横带里,再通过标准变换关系)*1exp(T s z =将此带变换到整个z 平面上去,这样就使s 平面与z 平面之间建立一一对应的单值关系,消除了多值变换性。 为了将s 平面的Ωj 轴压缩到1s 平面的1Ωj 轴上的pi -到pi 一段上,可以通过以下的正切变换来实现: )21 tan(21T T Ω= Ω 这样当1Ω由T pi -经0变化到T pi 时,Ω由∞-经过0变化到∞+,也映射到了整个Ωj 轴。将这个关系延拓到整个s 平面和1s 平面,则可以得到

FIR数字滤波器设计及MATLAB使用【重点】

cheng 《数字信号处理》 课程设计报告 FIR数字滤波器设计及MATLAB实现 专业:通信工程 班级:通信1101班 组次:第9组 姓名及学号: 姓名及学号:

目录 一、设计目的 (3) 二、设计任务 (3) 三、设计原理 (3) 3.1窗函数法 (3) 3.2频率采样法 (4) 3.3最优化设计 (5) 3.3.1等波纹切比雪夫逼近准则 (5) 3.3.2仿真函数 (6) 四、设计过程 (7) 五、收获与体会 (13) 参考文献 (13)

FIR 数字滤波器设计及MATLAB 实现 一、设计目的 FIR 滤波器:有限长单位冲激响应滤波器,是数字信号处理系统中最基 本的元件,它可以在保证任意幅频特性的同时具有严格的线性相频特性,同时其单位抽样响应是有限长的,因而滤波器是稳定的系统。因此,FIR 滤波器在通信、图像处理、模式识别等领域都有着广泛的应用。滤波器设计是根据给定滤波器的频率特性,求得满足该特性的传输函数。 二、设计任务 FIR 滤波器设计的任务是选择有限长度的()h n ,使传输函数()jw H e 满足一定的幅度特性和线性相位要求。由于FIR 滤波器很容易实现严格的线性相位,所以FIR 数字滤波器设计的核心思想是求出有限的脉冲响应来逼近给定的频率响应。 设计过程一般包括以下三个基本问题: (1) 根据实际要求确定数字滤波器性能指标; (2) 用一个因果稳定的系统函数去逼近这个理想性能指标; (3) 用一个有限精度的运算去实现这个传输函数。 三、设计原理 FIR 滤波器设计的任务是选择有限长度的()h n ,使传输函数()jw H e 满足一定的幅度特性和线性相位要求。由于FIR 滤波器很容易实现严格的线性相位,所以FIR 数字滤波器设计的核心思想是求出有限的脉冲响应来逼近给定的频率响应。 设计过程一般包括以下三个基本问题: (1) 根据实际要求确定数字滤波器性能指标; (2) 用一个因果稳定的系统函数去逼近这个理想性能指标; (3) 用一个有限精度的运算去实现这个传输函数。 3.1窗函数法 设计FIR 数字滤波器的最简单的方法是窗函数法,通常也称之为傅立叶级数法。FIR 数字滤波器的设计首先给出要求的理想滤波器的频率响应()jw d H e ,设计一个FIR 数字滤波器频率响应()jw H e ,去逼近理想的滤波响应()jw d H e 。然而,

实验四数字滤波器的设计实验报告

数字信号处理 实验报告 实验四 IIR数字滤波器的设计学生姓名张志翔 班级电子信息工程1203班 学号 指导教师 实验四 IIR数字滤波器的设计 一、实验目的: 1. 掌握双线性变换法及脉冲响应不变法设计IIR数字滤波器的具体设 计方法及其原理,熟悉用双线性变换法及脉冲响应不变法设计低通、高通和带通IIR数字滤波器的MATLAB编程。 2. 观察双线性变换及脉冲响应不变法设计的滤波器的频域特性,了解双线性变换法及脉冲响应不变法的特点。 3.熟悉Butterworth滤波器、切比雪夫滤波器和椭圆滤波器的频率特性。 二、实验原理: 1.脉冲响应不变法 用数字滤波器的单位脉冲响应序列模仿模拟滤波器的冲激响应 ,让正好等于的采样值,即,其中为采样间隔,如果以及分别表示的拉式变换及的Z变换,则 2.双线性变换法 S平面与z平面之间满足以下映射关系:

s平面的虚轴单值地映射于z平面的单位圆上,s平面的左半平面完全映射到z平面的单位圆内。 双线性变换不存在混叠问题。 双线性变换是一种非线性变换,这种非线性引起的幅频特性畸变可通过预畸而得到校正。 三、实验内容及步骤: 实验中有关变量的定义: fc 通带边界频率; fr阻带边界频率;δ通带波动;At 最小阻带衰减; fs采样频率; T采样周期 (1) =0.3KHz, δ=0.8Db, =0.2KHz, At =20Db,T=1ms; 设计一个切比雪夫高通滤波器,观察其通带损耗和阻带衰减是否满足要求。 MATLAB源程序: wp=2*1000*tan(2*pi*300/(2*1000)); ws=2*1000*tan(2*pi*200/(2*1000)); [N,wn]=cheb1ord(wp,ws,0.8,20,'s'); %给定通带(wp)和阻带(ws)边界角频率,通带波动波动0.8,阻带最小衰减20dB,求出最低阶数和通带滤波器的通带边界频率Wn [B,A]=cheby1(N,0.5,wn,'high','s');%给定通带(wp)和阻带(ws)边界角频率,通带波动 [num,den]=bilinear(B,A,1000); [h,w]=freqz(num,den); f=w/(2*pi)*1000; plot(f,20*log10(abs(h)));

基于FPGA的滤波器的设计

摘要 自适应滤波器是统计信号处理的一个重要组成部分。在现代滤波处理技术中,自适应滤波器的处理效果尤为突出。在众多滤波器中,特别是在一些对信号处理的实时性要求比较高,体积功耗有严格限制的场合,使用FPGA硬件实现的数字滤波器更为广泛。 本论文从自适应滤波器研究的重要意义入手,介绍了线性自适应滤波器的算法,对几种基于最小均方误差准则或最小平方误差准则的自适应滤波器算法进行研究,就滤波器的基本原理及设计方法做了简单的介绍,最终设计基于FPGA的LMS算法设计复数自适应滤波器,对设计方法进行叙述,并以VHDL语言编写程序进行仿真测试。 关键词:自适应滤波器;FPGA;自适应算法LMS;有限冲激响应滤波器

FPGA-based design of adaptive filter Student:TAN xx Teacher:CHEN xx Abstract:Adaptive filter is a statistical signal processing as an important component. Processing technology in the modern filter, the adaptive filter, particularly in the treatment effect. Among the filters, especially in some of the real-time signal processing requirements of higher power, there are strict restrictions on the size of the occasion, the use of FPGA hardware to achieve a wider range of digital filters. In this paper, adaptive filter from the importance of research to start to introduce the linear adaptive filter algorithm, based on several criteria MMSE or least square error criteria for the study of adaptive filter algorithm, it filters The basic principle and design method of a brief introduction, the final design of FPGA-based design of complex LMS adaptive filter algorithm, the design methods described, and VHDL languages in maxplus simulation test platform. Keywords: adaptive filter;FPGA;LMS adaptive algorithm;finite impulse response filter

数字滤波器的设计及实现

数字滤波器的设计及实现 【一】设计目的 1. 熟悉IIR 数字滤波器和FIR 数字滤波器的设计原理和方法; 2. 学会调用MATLAB 信号处理工具箱中的滤波器设计函数设计各种IIR 和FIR 数字滤波器,学会根据滤波要求确定滤波器指标参数; 3. 掌握用IIR 和FIR 数字滤波器的MA TLAB 实现方法,并能绘制滤波器的幅频特性、相频特性; 4. 通过观察滤波器的输入、输出信号的时域波形及其频谱,建立数字滤波的概念。 【二】设计原理 抑制载波单频调幅信号的数学表达式为 []))(2cos())(2cos(2 1)2cos()2cos()(000t f f t f f t f t f t s c c c ++-==ππππ (2.1) 其中,)2cos(t f c π称为载波,c f 为载波频率,)2cos(0t f π称为单频调制信号,0f 为调制正弦波信号频率,且满足0c f f >。由(2.1)式可见,所谓抑制载波单频调制信号,就是两个正弦信号相乘,它有2个频率成分:和频c f +0f ,差频c f -0f ,这两个频率成分关于载波频率c f 对称。所以,1路抑制载波单频调幅信号的频谱图是关于载波频率c f 对称的两根谱线。 复合信号st 产生函数mstg 清单: function st=mstg %产生信号序列st ,并显示st 的时域波形和频谱 %st=mstg 返回三路调幅信号相加形成的混合信号,长度N=800 N=800; %信号长度N 为800 Fs=10000;T=1/Fs;Tp=N*T; %采样频率Fs=10kHz ,Tp 为采样时间 t=0:T:(N-1)*T;k=0:N-1;f=k/Tp; fc1=Fs/10; %第1路调幅信号载波频率fc1=1000Hz fm1=fc1/10; %第1路调幅信号的调制信号频率fm1=100Hz fc2=Fs/20; %第2路调幅信号载波频率fc2=500Hz fm2=fc2/10; %第2路调幅信号的调制信号频率fm2=50Hz fc3=Fs/40; %第3路调幅信号载波频率fc3=250Hz fm3=fc3/10; %第3路调幅信号的调制信号频率fm3=25Hz xt1=cos(2*pi*fm1*t).*cos(2*pi*fc1*t); %产生第1路调幅信号 xt2=cos(2*pi*fm2*t).*cos(2*pi*fc2*t); %产生第2路调幅信号 xt3=cos(2*pi*fm3*t).*cos(2*pi*fc3*t); %产生第3路调幅信号 st=xt1+xt2+xt3; %三路信号相加,得到复合信号

脉冲响应不变法设计数字低通滤波器

燕山大学 课程设计说明书 题目:脉冲响应不变法设计数字低通滤波器 学院(系):电气工程学院 年级专业:09级精密仪器及机械2班 学号: 0901******** 学生姓名:范程灏 指导教师:刘永红 教师职称:讲师

电气工程学院《课程设计》任务书 课程名称:数字信号处理课程设计 基层教学单位:仪器科学与工程系指导教师: 学号学生姓名(专业)班级设计题目7、脉冲响应不变法设计数字低通滤波器 设 计技术参数给定技术指标为:Hz f p 100 =,Hz f s 300 =,dB p 3 = α,dB s 20 = α,采样频率Hz F s 1000 =。 设 计 要 求 设计Butterworth低通滤波器,用脉冲响应不变法转换成数字滤波器。 参考资料数字信号处理方面资料MATLAB方面资料 周次前半周后半周 应完成内容收集消化资料、学习MA TLAB软件, 进行相关参数计算 编写仿真程序、调试 指导教师签字基层教学单位主任签字

目录 第1章前言 (3) 第2章数字信号处理部分基础知识 (3) 第3章 MATLAB部分基础知识 (8) 3.1 MATLAB介绍 (8) 3.2 MATLAB命令介绍 (8) 第4章仿真过程及仿真图 (9) 4.1 仿真程序 (9) 4.2 仿真波形 (10) 第5章设计结论 (10) 第6章参考文献 (11)

第一章 前言 《数字信号处理》课程设计是在学生完成数字信号处理和MATLAB 的结合后的基本实验以后开设的。本课程设计的目的是为了让学生综合数字信号处理和MATLAB 并实现一个较为完整的小型滤波系统。这一点与验证性的基本实验有本质性的区别。开设课程设计环节的主要目的是通过系统设计、软件仿真、程序安排与调试、写实习报告等步骤,使学生初步掌握工程设计的具体步骤和方法,提高分析问题和解决问题的能力,提高实际应用水平。 IIR 数字滤波器具有无限宽的冲激响应,与模拟滤波器相匹配,所以IIR 滤波器的设计可以采取在模拟滤波器设计的基础上进一步变换的方法。其设计方法主要有经典设计法、直接设计法和最大平滑滤波器设计法。FIR 数字滤波器的单位脉冲响应是有限长序列。它的设计问题实质上是确定能满足所要求的转移序列或脉冲响应的常数问题,设计方法主要有窗函数法、频率采样法和等波纹最佳逼近法等。 第2章 数字信号处理基础知识部分 2.1巴特沃斯滤波器的幅度平方函数及其特点 巴特沃斯模拟滤波器幅度平方函数的形式是 )N c N c a j j j H 222 )/(11 )/(11ΩΩ+= ΩΩ+= Ω (5-6)

实验三FIR数字滤波器的设计-7页word资料

实验三 FIR数字滤波器的设计 一、实验目的 1.掌握用窗函数法,频率采样法及优化设计法设计FIR滤波器的 原理及方法,熟悉响应的计算机编程; 2.熟悉线性相位FIR滤波器的幅频特性和相频特性; 3.了解各种不同窗函数对滤波器性能的影响。 二、实验原理与方法 线性相位实系数FIR滤波器按其N值奇偶和h(n)的奇偶对称性分为四种: 1、h(n)为偶对称,N为奇数 H(e jω)的幅值关于ω=0,π,2π成偶对称。 2、h(n)为偶对称,N为偶数 H(e jω)的幅值关于ω=π成奇对称,不适合作高通。 3、h(n)为奇对称,N为奇数 H(e jω)的幅值关于ω=0,π,2π成奇对称,不适合作高通和低通。 4、h(n)为奇对称,N为偶数

H(e jω) ω=0、2π =0,不适合作低通。 (一) 窗口法 窗函数法设计线性相位FIR滤波器步骤 ?确定数字滤波器的性能要求:临界频率{ωk},滤波器单位脉冲响应 长度N; ?根据性能要求,合理选择单位脉冲响应h(n)的奇偶对称性,从而确 定理想频率响应H d (e jω)的幅频特性和相频特性; ?求理想单位脉冲响应h d(n),在实际计算中,可对H d(e jω)按M(M远 大于N)点等距离采样,并对其求IDFT得h M (n),用h M (n)代替h d (n); ?选择适当的窗函数w(n),根据h(n)= h d(n)w(n)求所需设计的FIR 滤波器单位脉冲响应; ?求H(e jω),分析其幅频特性,若不满足要求,可适当改变窗函数形式或长度N,重复上述设计过程,以得到满意的结果。 窗函数的傅式变换W(e jω)的主瓣决定了H(e jω)过渡带宽。W(e jω)的旁瓣大小和多少决定了H(e jω)在通带和阻带范围内波动幅度,常用的几种窗函数有: ?矩形窗 w(n)=R N(n); ?Hanning窗; ?Hamming窗 ;

实验五FIR数字滤波器的设计

实验六 FIR 数字滤波器的设计 一、实验目的 1.熟悉FIR 滤波器的设计基本方法 2.掌握用窗函数设计FIR 数字滤波器的原理与方法。 二、实验内容 1.FIR 数字滤波器的设计方法 FIR 滤波器的设计问题在于寻求一系统函数)(z H ,使其频率响应)(ωj e H 逼近滤波器要求的理想频率响应)(ωj d e H ,其对应的单位脉冲响应为)(n h d 。 (1)用窗函数设计FIR 滤波器的基本原理 设计思想:从时域从发,设计)(n h 逼近理想)(n h d 。设理想滤波器)(ωj d e H 的单位脉 冲响应为)(n h d 。以低通线性相位FIR 数字滤波器为例。 ?∑--∞-∞=== ππωωωωω πd e e H n h e n h e H jn j d d jn n d j d )(21)()()( (6-1) )(n h d 一般是无限长的,且是非因果的,不能直接作为FIR 滤波器的单位脉冲响应。要想得到一个因果的有限长的滤波器h(n),最直接的方法是截断)()()(n w n h n h d =,即截取为有限长因果序列,并用合适的窗函数进行加权作为FIR 滤波器的单位脉冲响应。按照线性相位滤波器的要求,h(n)必须是偶对称的。对称中心必须等于滤波器的延时常数,即 ???-==2 /)1()()()(N a n w n h n h d (6-2) 用矩形窗设计的FIR 低通滤波器,所设计滤波器的幅度函数在通带和阻带都呈现出振荡现象,且最大波纹大约为幅度的9%,这个现象称为吉布斯(Gibbs )效应。为了消除吉布斯效应,一般采用其他类型的窗函数。 (2) 典型的窗函数 ① 矩形窗(Rectangle Window) )()(n R n w N = (6-3)

FIR数字滤波器设计与实现

FIR 数字滤波器设计与实现 一.摘要:数字滤波器是一种具有频率选择性的离散线性系统,在信号数字处理中有着广泛的应 用。其中FIR 滤波器是一种常用的滤波器,它在保证幅度特性满足技术要求的同时,很容易做到严格的线性相位特性,在语音分析、图像处理、雷达监测等对信号相位要求高的领域有着广泛的应用,能实现IIR 滤波器不能实现的许多功能。 二.关键词:FIR 窗函数系统函数MATLAB 三.内容提要: 数字滤波器的功能就是把输入序列通过一定的运算变换成输出序列,因此数字滤波器的结构系 统中就必须包括一定数量和性能的运算器件和运算单元,而运算器件和运算单元的配置必须由数字滤波器的结构特点和性能特点来决定,因此在进行FIR 数字滤波器的设计之前,有必要介绍和总结FIR 数字滤波器的基本结构和相关特性(包括频响曲线(幅度和相位),单位冲激响应等),在介绍完其基本结构和相关特性后,就进行FIR 数字滤波器的设计和实现。 (一)FIR 滤波器的基本结构 在讨论任何一种滤波器时,都要着重分析其系统函数,FIR 滤波器的系统函数为: n N n z n h z H ∑-==1 0)()(。从该系统函数可看出,FIR 滤波器有以下特点: 1)系统的单位冲激响应h(n)在有限个n 值处不为零; 2)系统函数H(z)在|z|>0处收敛,极点全部在z=0处(稳定系统); 3)结构上主要是非递归结构,没有输出到输入的反馈,但有些结构中(例如频率抽样结构)也包 含有反馈的递归部分。 1.FIR 滤波器实现的基本结构有: 1) 横截型(卷积型、直接型) a.一般FIR 滤波器的横截型(直接型、卷积型)结构: 若给定差分方程为: 。则可以直接由差分方程得出FIR 滤波器结构如 下图所示: 这就是FIR 滤波器的横截型结构,又称直接型或卷积型结构。 b .线性相位FIR 滤波器的横截型结构

数字信号处理-低通滤波器设计实验

实验报告 课程名称:数字信号处理 实验名称:低通滤波器设计实验 院(系): 专业班级: 姓名: 学号: 指导教师: 一、实验目的: 掌握IIR数字低通滤波器的设计方法。 二、实验原理: 2.1设计巴特沃斯IIR滤波器 在MATLAB下,设计巴特沃斯IIR滤波器可使用butter 函数。 Butter函数可设计低通、高通、带通和带阻的数字和模拟IIR滤波器,其特性为使通带内的幅度响应最大限度地平坦,但同时损失截止频率处的下降斜度。在期望通带平滑的情况下,可使用butter函数。butter函数的用法为:

[b,a]=butter(n,Wn)其中n代表滤波器阶数,W n代表滤波器的截止频率,这两个参数可使用buttord函数来确定。buttord函数可在给定滤波器性能的情况下,求出巴特沃斯滤波器的最小阶数n,同时给出对应的截止频率Wn。buttord函数的用法为:[n,Wn]= buttord(Wp,Ws,Rp,Rs)其中Wp和Ws分别是通带和阻带的拐角频率(截止频率),其取值范围为0至1之间。当其值为1时代表采样频率的一半。Rp和Rs分别是通带和阻带区的波纹系数。 2.2契比雪夫I型IIR滤波器。 在MATLAB下可使用cheby1函数设计出契比雪夫I 型IIR滤波器。 cheby1函数可设计低通、高通、带通和带阻契比雪夫I 型滤IIR波器,其通带内为等波纹,阻带内为单调。契比雪夫I型的下降斜度比II型大,但其代价是通带内波纹较大。cheby1函数的用法为:[b,a]=cheby1(n,Rp,Wn,/ftype/)在使用cheby1函数设计IIR滤波器之前,可使用cheblord 函数求出滤波器阶数n和截止频率Wn。cheblord函数可在给定滤波器性能的情况下,选择契比雪夫I型滤波器的最小阶和截止频率Wn。cheblord函数的用法为: [n,Wn]=cheblord(Wp,Ws,Rp,Rs)其中Wp和Ws分别是通带和阻带的拐角频率(截止频率),其取值范围为0至1之间。当其值为1时代表采样频率的一半。Rp和Rs分别是通带和阻带区的波纹系数。 三、实验要求: 利用Matlab设计一个数字低通滤波器,指标要求如下: