PLL锁相环时钟设定

PLL锁相环时钟设定

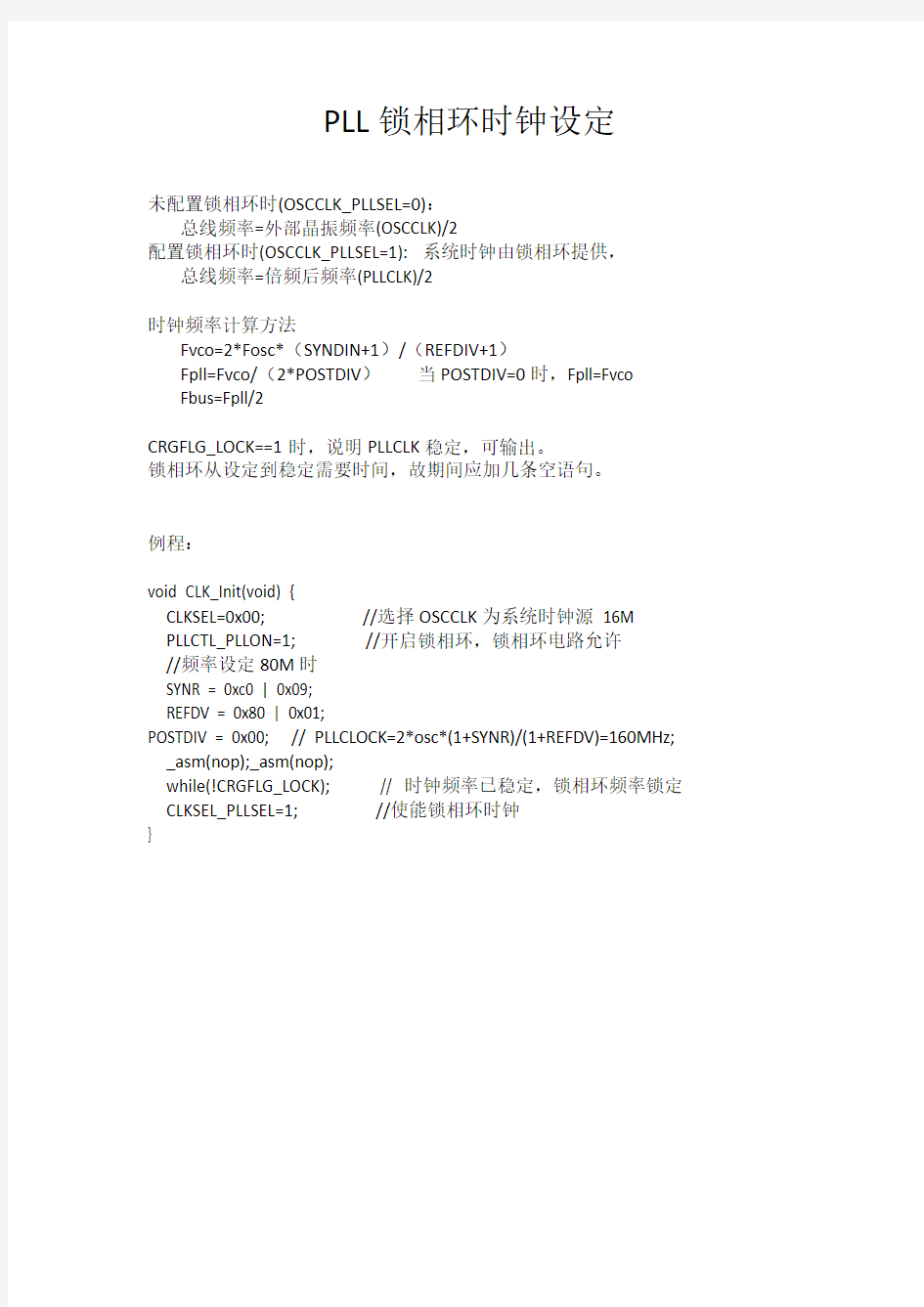

未配置锁相环时(OSCCLK_PLLSEL=0):

总线频率=外部晶振频率(OSCCLK)/2

配置锁相环时(OSCCLK_PLLSEL=1): 系统时钟由锁相环提供,总线频率=倍频后频率(PLLCLK)/2

时钟频率计算方法

Fvco=2*Fosc*(SYNDIN+1)/(REFDIV+1)

Fpll=Fvco/(2*POSTDIV)当POSTDIV=0时,Fpll=Fvco

Fbus=Fpll/2

CRGFLG_LOCK==1时,说明PLLCLK稳定,可输出。

锁相环从设定到稳定需要时间,故期间应加几条空语句。

例程:

void CLK_Init(void) {

CLKSEL=0x00; //选择OSCCLK为系统时钟源16M PLLCTL_PLLON=1; //开启锁相环,锁相环电路允许

//频率设定80M时

SYNR = 0xc0 | 0x09;

REFDV = 0x80 | 0x01;

POSTDIV = 0x00; // PLLCLOCK=2*osc*(1+SYNR)/(1+REFDV)=160MHz; _asm(nop);_asm(nop);

while(!CRGFLG_LOCK); // 时钟频率已稳定,锁相环频率锁定CLKSEL_PLLSEL=1; //使能锁相环时钟

}

PWM模块

PWME:PWM允许寄存器,置1时允许输出。

PWMPOL:极性寄存器。置1时首先输出高电平。

2、3、6、7、置1时clock SB 作为时钟源,置0时clock B作为时钟源

PWMCAE:居中对齐允许寄存器,只有当通道输出禁止时才能设置此寄存器置1时为居中对齐,置0时左对齐

PWMSCLA:比例因子寄存器A;用于提供clock SA的比例因子

Clock SA的时钟频率= clock A/(2*PWMSCLA)当PWMSCLA为0时比例因子默认为256. CLOCKSB 计算方法类似,寄存器为PWMSCLB。PWMCNTx:通道计数寄存器,一般设置值为0x00;

PWMPERx:周期寄存器;

左对齐时周期计算方法:PWMxPeriod=指定时钟周期乘以PWMPERx的值居中对齐时=指定时钟周期乘PWMPERx的值再乘2;

PWMDTYx:占空比寄存器。

占空比计算方法:极性为1时:Duty Cycle=PWMDTYx/PWMPERx*100%

极性为0时(PWMPERx-PWMDTYx)/PWMPERx

例程

void PWM_128init(void)

{

PWMPRCLK=0x00; //ClockA and ClockB等于总线时钟80M

PWMCLK=0xc2; //通道7、1选择SB、SA时钟源,通道5,3选择A,B时钟源PWMSCLB=0x14; //SB时钟源为40分频为2M

PWMSCLA=0x14; //SA时钟源2M;

PWMCTL=0xf0; //级联67 级联45 级联23 级联01

PWMCAE=0x00; //pwm左对齐输出

PWMCNT01=0;

PWMCNT23=0;

PWMCNT45=0;

PWMCNT67=0;

PWMPOL=0XFF; //初始输出高电平

PWMPER67 = 40000; //67通道输出50HZ的频率2M/40000

PWMPER45 = 8000; //45通道输出10k频率80M/8000

PWMPER23 = 8000; //23通道输出10k频率80M/8000

PWMPER01=40000;

PWMDTY67 = 2800; //67通道初始PWM高电平时间为1.5ms

PWMDTY45 = 2000; //45 通道初始占空比0%

PWMDTY23 =2000; //23通道初始占空比0

PWMDTY01=3000;

PWME=0XAA; //7,5,3,1通道使能

}

SPI模块

五、SPIDR 数据寄存器

SPI数据寄存器是SPI数据的输入和输出寄存器,写该寄存器会允许一个字节进入队列并发送。如果SPI被配置成主机,当前面的数据发送完成,排在队列的数据会立即被发送。SPISR寄存器中的发送空标志SPTEF表明SPI数据寄存器准备接收新的数据。当SPIF=1时SPIDR中接收的数据是有效的。

SPI的编程方法:

1、初始化:设置控制寄存器SPICR1、SPICR2,及波特率寄存器SPIBR。在此设

定SPI的工作方式,时钟极性,时钟相位,及各种中断允许等。

2、发送与接收数据的编写:作为主机方,只要将数据写入SPIDR,然后检查SPISR

的SPTEF位,若为1,则表示数据已经发送出去。若同时接收对方送来的数据,则接着检查SPISR的SPIF位,若为1,则表示要接的数据已经进入数据寄存器,可以取出了。

SCI模块

SCI模块复用PS口的4个引脚,(0~3)作为RXD、TXD、RXD1、TXD1. SCI波特率寄存器(SCIBDH和SCIBDL)

SCI波特率=SCI模块时钟/(16*寄存器的值)

49个运算公式

一.页码问题 对多少页出现多少1或2的公式 如果是X千里找几,公式是 1000+X00*3 如果是X百里找几,就是100+X0*2,X有多少个0 就*多少。依次类推!请注意,要找的数一定要小于X ,如果大于X就不要加1000或者100一类的了, 比如,7000页中有多少3 就是 1000+700*3=3100(个) 20000页中有多少6就是 2000*4=8000 (个) 友情提示,如3000页中有多少3,就是300*3+1=901,请不要把3000的3忘了 二,握手问题 N个人彼此握手,则总握手数 S=(n-1){a1+a(n-1)}/2=(n-1){1+1+(n-2)}/2=『n^2-n』/2 =N×(N-1)/2 例题: 某个班的同学体育课上玩游戏,大家围成一个圈,每个人都不能跟相邻的2个人握手,整个游戏一共握手152次,请问这个班的同学有( )人 A、16 B、17 C、18 D、19 【解析】此题看上去是一个排列组合题,但是却是使用的多边形对角线的原理在解决此题。按照排列组合假设总数为X人则Cx取3=152 但是在计算X时却是相当的麻烦。我们仔细来分析该题目。以某个人为研究对象。则这个人需要握x-3次手。每个人都是这样。则总共握了x×(x-3)次手。但是没2个人之间的握手都重复计算了1次。则实际的握手次数是x×(x-3)÷2=152 计算的x=19人 三,钟表重合公式 钟表几分重合,公式为: x/5=(x+a)/60 a时钟前面的格数 四,时钟成角度的问题 设X时时,夹角为30X , Y分时,分针追时针5.5,设夹角为A.(请大家掌握) 钟面分12大格60小格每一大格为360除以12等于30度,每过一分钟分针走6度,时针走0.5度,能追5.5度。 1.【30X-5.5Y】或是360-【30X-5.5Y】【】表示绝对值的意义(求角度公式) 变式与应用 2.【30X-5.5Y】=A或360-【30X-5.5Y】=A (已知角度或时针或分针求其中一个角) 五,往返平均速度公式及其应用(引用) 某人以速度a从A地到达B地后,立即以速度b返回A地,那么他往返的平均速度v=2ab/(a+b )。

飞思卡尔锁相环

备战飞思卡尔智能车大赛.开始模块总结. 锁相环设置. 公式: PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1), fbus=PLLCLK/2 void INIT_PLL(void) { CLKSEL &= 0x7f; //选用外部时钟.准备设置锁相环 PLLCTL &= 0x8F; //禁止锁相环 SYNR = 0xc9; //设置SYNR REFDV = 0x81; //设置REFDV PLLCTL |=0x70; //锁相环使能 asm NOP; asm NOP; //两个机器周期缓冲时间 while(!(CRGFLG&0x08)); //等待锁相环锁定 CLKSEL |= 0x80; //设置锁相环为时钟源 } 飞思卡尔XS128的PLL锁相环详细设置说明——关于如何提高总线工作频率PLL锁相环就相当于超频 单片机超频的原因和PC机是个一道理。分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY 这也和PC机南北桥的原理类似。总线频率设置过程 1、禁止总中断 2、寄存器CLKSEL(时钟选择寄存器)的第七位置0 即CLKSEL_PLLSEL=0。选择时钟源为外部晶振OSCCLK(外接晶振频率) 在PLL(锁相环)程序执行前 内部总线频率为OSCCLK/2 3. PLLCTL_PLLON=1 打开PLL 4.设置SYNR 时钟合成寄存器 、REFDV 时钟分频寄存器 、POSTDIV三个寄存器的参数 5、_asm(nop) _asm(nop);加入两条空指令 使锁相环稳定 6、while(!(CRGFLG_LOCK==1));//时钟校正同步 7、CLKSEL_PLLSEL=1; 下面详细说一下频率的计算一、时钟合成寄存器SYNR寄存器结构 VCOFRQ[1:0]控制压控振动器VCO的增益 默认值为00 VCO的频率与VCOFRQ[1:0]对应表

SPI时钟模式的配置

SPI时钟模式的配置 【SPI基础知识简介】设备与设备之间通过某种硬件接口通讯,目前存在很多

种接口,SPI接口是其中的一种。 SPI中分Master主设备和Slave从设备,数据发送都是由Master控制。 —个master可以接一个或多个slave o 常见用法是一个Master接一个slave,只需要4根线: SCLK : Serial Clock,(串行)时钟 MISO : Master In Slave Out,主设备输入,从设备输出 MOSI : Master Out Slave In,主设备输出,从设备输入 SS: Slave Select,选中从设备,片选 SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在EEPROM, FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。 即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash, ADC等,进行通讯。 而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。 而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。

【SPI相关的缩写或说法】 先简单说一下,关于SPI中一些常见的说法: SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有 —些其他写法,简单总结如下: (1)CKPOL (Clock Polarity) = CPOL = POL = Polarity =(时钟)极性 (2)CKPHA (Clock Phase) = CPHA = PHA = Phase =(时钟)相位 (3)SCK二SCLK二SPI 的时钟 ⑷Edge=边沿,即时钟电平变化的时刻,即上升沿(rising edge)或者下降沿 (falling edge) 对于一个时钟周期内,有两个edge,分别称为: Leading edge=前一个边沿二第一个边沿,对于开始电压是1,那么就是1变成0 的时候,对于开始电压是0,那么就是0变成1的时候; Trailing edge二后一个边沿二第二个边沿,对于开始电压是1,那么就是0变成1 的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候; 本文采用如下用法? 极性二CPOL 相位=CPHA SCLK二时钟 第一个边沿和第二个边沿

时钟上角度大小的计算问题

时钟上角度大小的计算问题 时钟钟面上的时针和分针之间的夹角问题,历来是许多同学求解的困惑问题之一,事实上,只要同学们能弄清时针、分针之间的关系: 时针1小时转1大格1小时30°1分钟0.5° 抓住起始和终止两个时刻算出分针走了多少分钟,由上述表格算出时针和分针各转了多少度,再在钟面上比较,求出结果.现举例说明. 一、整点时刻两针的夹角 例1 求下午4时,时针与分针之间的夹角. 分析:下午4时,时针指在4上,分针指在12上,于是可求出它们之间的夹角. 解:因为下午4时,时针指在4上,分针指在12上,所以4×30°=120°. 评注:因为整点时,分针始终指向12,所以可把分针看作角的始边,时针看作角的终边,时针旋转一周360o需要12个小时,所以时针每小时旋转的角度为360o÷12=30o.由于我们现在研究的角都是小于平角的角,所以在1到6小时,两针的夹角为30o×n(n=1,2,…,6);在7到12小时,两针的夹角为360o-30o×n(n=7,8,…,12).显然,任意整点时刻时针与分针的夹角我们都可以通过上面的两个公式求出来,值得注意的是,钟面上两针的夹角有可能会相等,如3点和9点时两针的夹角都是90o,但在不同时刻. 二、任意时刻两针的夹角 例2 钟表上2时15分时,时针与分针所形成的锐角的度数是多少? 分析要求解此问题,只要弄清时针每小时转过多少度的角,弄清该时针该分针的位置,即经过15分钟转过的角度即可. 解因为360 12 ×21 4 =30°× 4 9=67.5°,360 60 ×15=90°, 所以90°-67.5°=22.5°. 评注:通过对本题的求解,同学们可以记住每分钟分针比时针多转了5.5°,必要时可以利用方程求解此类问题,有时会显得更加简捷.

锁相环基本原理及其应用

锁相环及其应用 所谓锁相环路,实际是指自动相位控制电路(APC),它是利用两个电信号的相位 误差,通过环路自身调整作用,实现频率准确跟踪的系统,称该系统为锁相环路,简称环路,通常 用PLL表示。 称VCO )三个部件组成闭合系统。这是一个基本环路,其各种形式均由它变化而来 PLL概念 设环路输入信号V i= V im Sin( 3 i t+ 0 i) 环路输出信号V o= V om Sin( 3 o t+ 0 o) 其中 3 o = 3 r +△ 3 o 率的自动控制系统称为锁相环路 PLL构成 由鉴相器(PD环路滤波器(LPF)压控振荡器(VCO组成的环路 通过相位反馈控制, 最终使相位保持同步, 实现了受控频率准确跟踪基准信号频锁相环路是由鉴相器(简称PD)、环路滤波器(简称LPF或LF )和压控振荡器(简

ejt 戶心(tAejt)谋差相檯 PLL 原理 从捕捉过程一锁定 A.捕捉过程(是失锁的) 0 i — 0 i 均是随时间变化的,经相位比较产生误差相位 0 e = 0 i - 0 o ,也是变化的。 b. 0 e (t)由鉴相器产生误差电压 V d (t)= f ( 0 e )完成相位误差一电压的变换作用。 V d (t)为交流电压。 C. V d (t)经环路滤波,滤除高频分量和干扰噪声得到纯净控制电压,由 VCO 产生 控制角频差△ 3 0,使3 0随3i 变化。 B.锁定(即相位稳定) 即 3 0= 3 r + △ 3 Omax 。 3 r 为VCO 固有振荡角频率。) 锁相基本组成和基本方程(时域) 各基本组成部件 鉴相器(PD) a. 一旦锁定0 e (t)= 0 e -(很小常数) V d (t)= V d (直流电压) b. 3 0= 3 i 输出频率恒等于输入频率(无角频差,同时控制角频差为最大△ 3 Omax

RCC时钟配置

时钟配置RCC_Configuration() 在比较靠前的版本中,我们需要向下面那样设置时钟: ErrorStatus HSEStartUpStatus; /*********************************************************************** *************** * FunctionName : RCC_Configuration() * Description : 时钟配置 * EntryParameter : None * ReturnValue : None ************************************************************************ **************/ void RCC_Configuration(void) { /* 复位所有的RCC外围设备寄存器,不改变内部高速振荡器调整位(HSITRIM[4..0])以及 备份域控制寄存器(RCC_BDCR),控制状态寄存器RCC_CSR */ RCC_DeInit(); // RCC system reset(for debug purpose) /* 开启HSE振荡器*/ /* 三个参数: RCC_HSE_ON-开启RCC_HSE_OFF-关闭RCC_HSE_BYPASS-使用外部时钟振荡器*/ RCC_HSEConfig(RCC_HSE_ON); // Enable HSE /* HSEStartUpStatus为枚举类型变量,2种取值,0为ERROR,非0为SUCCESS 等待HSE准备好,若超时时间到则退出*/ HSEStartUpStatus = RCC_WaitForHSEStartUp(); // Wait till HSE is ready if (HSEStartUpStatus == SUCCESS) // 当HSE准备完毕切振荡稳定后 { /* 配置AHB时钟,这个时钟从SYSCLK分频而来分频系数有1,2,4,8,16,64,128,256,512 */ RCC_HCLKConfig(RCC_SYSCLK_Div1); // HCLK = SYSCLK /* 设置低速APB2时钟,这个时钟从AHB时钟分频而来分频系数为1,2,4,8,16 */ RCC_PCLK2Config(RCC_HCLK_Div1); // PCLK2 = HCLK /* 设置低速APB1时钟,这个时钟从AHB时钟分频而来分频系数为1,2,4,8,16 */ RCC_PCLK1Config(RCC_HCLK_Div2); // PCLK1 = HCLK/2 FLASH_SetLatency(FLASH_Latency_2); // Flash 2 wait state FLASH_PrefetchBufferCmd(FLASH_PrefetchBuffer_Enable); // Enable Prefetch Buffer /* 设置PLL的时钟源和乘法因子 第一个入口参数为时钟源,共有3个 RCC_PLLSource_HSI_Div2 RCC_PLLSource_HSE_Div1

角带的计算公式

皮带规格及长度计算理论长度=(半径1+半径2)*3,14 +(圆中心距*2) 怎样计算三角皮带的长度(大轮直径350小轮直径180中心距420)计算长度L=2×A+[π×(D1+D2)÷2]+[(D2-D1)×(D2 -D1)÷(4×A)] A=420 D1=180 D2=350 L= 皮带的规格: 一、O带/M带: 皮带面宽度为~10mm,皮带厚度为8 mm,长度20英寸~70英寸长,即500 mm~1775 mm长,其余长度很少用到。皮带分为带齿和不带齿两种。 二、A带皮带面宽度为~13mm,皮带厚度为9mm,长度为23英寸~100英寸长,即580 mm~2300mm长,其余长度很少用到。皮带分为带齿和不带齿两种。 三、B带皮带面宽度为15mm~17mm,皮带厚度为11 mm,长度24英寸~99英寸长,即600 mm~2540 mm长,其余长度很少用到。皮带带齿。 四、C带皮带面宽度为20mm~22mm,皮带厚度为13 mm,长度28英寸~98英寸长,即725 mm~2500 mm长,其余长度很少用到。皮带带齿。 五、其它特殊工程汽车带为25mm~38mm宽,皮带长度、厚度,均可按皮带样板订做。 注:皮带表面有“recmf”字母为带齿切边三角带,remf为无齿切 边三角带三角带长度计算1(inch)英寸= 一、O带/M带:外周长la=内周长(li)+50 mm ,或外周长=节线长(lw/le)+8 mm。 二、A带:外周长la=内周长li+56 mm,或外周长=节线长(lw/ le)+10 mm。三、B带:外周长la=内周长li﹢70 mm,或外周长=节线

长(lw /le)﹢13 mm。四、C带:外周长la=内周长li﹢81 mm,或外周长=节线长(lw / le)﹢16 mm。注:la-表示v带外周长le(lw)-表示v带拉力线长度li表示v带内周长多楔带(pk)型(multi-rib)肋距为belt长度mm:一:汽车用pk带:肋距为mm ,厚度为:二: 肋距为第一个肋中间到第二个肋中间的直线距离。三:3pk-31pk 时规带:主要经营欧美日名厂时规带

锁相环的基本原理和模型

1.锁相环的基本原理和模型 在并网逆变器系统中,控制器的信号需要与电网电压的信号同步,锁相环通过检测电网电压相位与输出信号相位之差,并形成反馈控制系统来消除误差,达到跟踪电网电压相位和频率的目的。一个基本的锁相环结构如图1-1所示,主要包括鉴相器,环路滤波器,压控振荡器三个部分。 图1-1 基本锁相环结构 鉴相器的主要功能是实现锁相环输出与输入的相位差检测;环路滤波器的主要作用应该是建立输入与输出的动态响应特性,滤波作用是其次;压控振荡器所产生的所需要频率和相位信息。 PLL 的每个部分都是非线性的,但是这样不便于分析设计。因此可以用近似的线性特性来表示PLL 的控制模型。 鉴相器传递函数为:)(Xo Xi Kd Vd -= 压控振荡器可以等效为一个积分环节,因此其传递函数为:S Ko 由于可以采用各种类型不同的滤波器(下文将会讲述),这里仅用)(s F 来表示滤波器的传递函数。 综合以上各个传递函数,我们可以得到,PLL 的开环传递函数,闭环传递函数和误差传递函数分别如下: S s F K K s G d o op )()(=,)()()(s F K K S s F K K s G d o d o cl +=,) ()(s F K K S S s H d o += 上述基本的传递函数就是PLL 设计和分析的基础。 2.鉴相器的实现方法 鉴相器的目的是要尽可能的得到准确的相位误差信息。可以使用线电压的过零检测实现,但是由于在电压畸变的情况下,相位信息可能受到严重影响,因此需要进行额外的信号处理,同时要检测出相位信息,至少需要一个周波的时间,动态响应性能可能受到影响。 一般也可以使用乘法鉴相器。通过将压控振荡器的输出与输入相乘,并经过一定的处理得到相位误差信息。 在实际的并网逆变器应用中还可以在在同步旋转坐标系下进行设计,其基本的目的也是要得的相差的数值。同步旋转坐标系下的控制框图和上图类似,在实际使用中,由于pq 理论在电网电压不平衡或者发生畸变使得性能较差,因而较多的使用dq 变换,将采样得到的三相交流电压信号进行变化后与给定的直流参考电压进行比较。上述两种方法都使用了近似,利用在小角度时正弦函数值约等于其角度,因而会带来误差,这个误差是人为近似导致的误差,与我们要得到的相位误差不是一个概念,最终的我们得到相位误差是要形成压控振荡器的输入信号,在次激励下获得我们所需要的频率和相位信息。 2.1乘法鉴相器

PLL锁相环时钟设定

PLL锁相环时钟设定 未配置锁相环时(OSCCLK_PLLSEL=0): 总线频率=外部晶振频率(OSCCLK)/2 配置锁相环时(OSCCLK_PLLSEL=1): 系统时钟由锁相环提供,总线频率=倍频后频率(PLLCLK)/2 时钟频率计算方法 Fvco=2*Fosc*(SYNDIN+1)/(REFDIV+1) Fpll=Fvco/(2*POSTDIV)当POSTDIV=0时,Fpll=Fvco Fbus=Fpll/2 CRGFLG_LOCK==1时,说明PLLCLK稳定,可输出。 锁相环从设定到稳定需要时间,故期间应加几条空语句。 例程: void CLK_Init(void) { CLKSEL=0x00; //选择OSCCLK为系统时钟源16M PLLCTL_PLLON=1; //开启锁相环,锁相环电路允许 //频率设定80M时 SYNR = 0xc0 | 0x09; REFDV = 0x80 | 0x01; POSTDIV = 0x00; // PLLCLOCK=2*osc*(1+SYNR)/(1+REFDV)=160MHz; _asm(nop);_asm(nop); while(!CRGFLG_LOCK); // 时钟频率已稳定,锁相环频率锁定CLKSEL_PLLSEL=1; //使能锁相环时钟 }

PWM模块 PWME:PWM允许寄存器,置1时允许输出。 PWMPOL:极性寄存器。置1时首先输出高电平。 2、3、6、7、置1时clock SB 作为时钟源,置0时clock B作为时钟源 PWMCAE:居中对齐允许寄存器,只有当通道输出禁止时才能设置此寄存器置1时为居中对齐,置0时左对齐 PWMSCLA:比例因子寄存器A;用于提供clock SA的比例因子 Clock SA的时钟频率= clock A/(2*PWMSCLA)当PWMSCLA为0时比例因子默认为256. CLOCKSB 计算方法类似,寄存器为PWMSCLB。PWMCNTx:通道计数寄存器,一般设置值为0x00; PWMPERx:周期寄存器; 左对齐时周期计算方法:PWMxPeriod=指定时钟周期乘以PWMPERx的值居中对齐时=指定时钟周期乘PWMPERx的值再乘2;

stm32如何配置时钟

学习STM32笔记2 如何配置时钟 学习STM32笔记2 如何配置时钟 /************************************************************* 该程序目的是用于测试核心板回来后是否能正常工作。包括 两个按键、两个LED现实。按键为PC4、PC5,LED为PA0\PA1。LED为 低电平时点亮。按键为低电平时触发。 ************************************************************/ #i nclude "stm32f10x_lib.h" void RCC_Configuration(void);//设置系统主时钟 void GPIO_Configuration(void);//设置邋邋IO参数 void NVIC_Configuration(void);//设置中断表地址 void delay(void);//延时函数 int main(void) { #ifdef DEBUG debug(); #endifRCC_Configuration(); NVIC_Configuration(); GPIO_Configuration(); while (1) { delay(); //设置指定的数据端口位 GPIO_SetBits(GPIOA,GPIO_Pin_0); //设置指定的数据端口位 delay(); GPIO_ResetBits(GPIOA,GPIO_Pin_0); //清除指定的数据端口位 GPIO_SetBits(GPIOA,GPIO_Pin_1); delay(); GPIO_ResetBits(GPIOA,GPIO_Pin_1); delay(); /********************************************* 使用setbits 与resetbits 是比较简单,其实还是可以使用 其它函数。例如可以使用GPIO_WriteBit GPIO_WriteBit(GPIOA, GPIO_Pin_1, Bit_SET); GPIO_WriteBit(GPIOA, GPIO_Pin_1, Bit_RESET);对于好像流水灯呀这些一个整段IO,可以使用GPIO_Write(GPIOA, 0x1101); *********************************************/

钟面上时针与分针之间夹角的计算公式与应用

钟面上时针与分针之间夹角的计算公式与应用 钟面上时针与分针之间夹角的计算公式与应用(初一) 提示一下你钟面上时针与分针之间 夹角的计算在新课标教材七年级数学习题中常常出现。我们在教学过程中按探究性教学模式进行教学设计,将钟面角计算转化为钟表行程问题,让同学们通过类似于科学研究的方式“做数学”得到了计算钟面角的公式,使这一问题的解决方法更具一般性和更易于操作。下面是我们关于《钟面角计算》的探究性教学过程:教材背景:学习了角的画法,会画一个角等于已知角,会画角的和、差、倍。创设情景1:如图1,时钟在12点20分时分针、时针成多少度的角?分析引导:从图1中抽象出几何图形如图2,时钟在12点时分针与时针重合,设为射线OA,分针、时针绕O点旋转,时钟在12点20分时,时针旋转到OB,分针旋转到OC,此时分针与时针的夹角:∠COB = ∠COA-∠BOA。时针的速度V时针= 0.5°/分,分针的速度V分针= 6°/分,时间t时针= t分针=20分,而路程=速度×时间,所以若将分针与时针之间的夹角看作是分针与时针的距离,则:∠COA = V分针×t分针∠BOA = V时针×t时针∠COB = V分针×t分针-V时针×t时针解:设12点20分时分针、时针所成角为α α = V分针×t分针-V时针×t时针= 6°/分×20分-0.5°/分×20分= 5.5°创设情景2:如图3,时钟在4点10分时分针、时针成多少度同学们很快就画出了图4,找到等量关系:∠COB = ∠BOA-∠COA 解:时钟在4点10分时分针、时针所成角为α α = V时针×t时针-V分针×t分针= 0.5°/分×(4×60分+10分)-6°/分×10分= 65°创设情景3:时钟在m点n分时分针、时针成多少度的角?经过同学们的热烈讨论,找到了计算时钟在m点n分时分针、时针夹角α的公式:α =∣V时针×t时针-V分针×t分针∣=∣0.5°/分×(m×60分+n分)-6°/分×n分∣=∣3 0°×m +0.5°×n-6°×n∣=∣30°×m -5.5°×n∣同学们探究得到这一公式后,所有钟面角计算问题就变的十分容易了。人教版三年制初中几何第一册(2001年5月第一版)复习题一A组习题12:时钟在8点时分针、时针成多少度的角?8时30分呢?利用上述公式解:设8点时分针、时针所成角为x,设8点30分时分针、时针所成角为y。α1 =∣30°×m-5.5°×n∣=∣30°×8 -5.5°×0∣= 240°表示为0°~180°的角:x = 360°-240°= 120°y = 30°×m -5.5°×n∣=∣30°×8 -5.5°×30∣= 75°答:时钟在8点时分针、时针成的角为120°,8时30分时分针、时针成的角为75°。再看几个练习:1、时钟在1 2点时时针与分针是重叠的,问时针至少转过多少角度时,时针与分针又重叠了?(精确到1″)分析:12点后时针与分针第一次重叠一定是在1点到2点之间。解:设1点n分时分针与时针第一次重叠,则∣30°×1-5.5°×n∣= 0°n = 60/11 此时时针转过的角度为:(60分+n分)×0.5°/分≈ 32°43′38″ 答:时钟至少转过32°43′38″时,时针与分针又重叠了。2、小红傍晚六点钟之后去商场买本,走到商场看到钟表上的时针与分针的夹角是1 20°,买完本后,走出商场看到钟表上的时针与分针的夹角又是120°,但已近晚上七点钟了,问小红买本用了多少时间?(精确到分)解:设6点n分时分针与时针第一次重叠,则 ∣30°×6 -5.5°×n∣= 12 0°30°×6-5.5°×n = 120°或30°×6-5.5°×n =-120°n = 1 20/11 或n = 600/11 买本所用时间为:600/11-120/11 = 480/11 ≈44 答:小红买本用了44分钟。3、在下午两点与三点之间,钟表的时针与分针何时成直角?解:设2点n分时时针与分针成直角,则∣30°×2-5.5°×n∣= 90°30°×2 -5.5°×n = 90°或30°×2-5.5°×n =-90°n1 =-60/11 (不合题意,舍去)n2 = 300/11 答:在下午两点与三点之间,钟表的时针与分针在2点300/11时成直角。4、从3点15分开始到时针与分针第一次成30°角,需要多少分钟?(精确到分)解:设3点n分时时针与分针成30°角,则∣30°×3-5.5°×n∣= 30°30°×3-5.5°×n = 30°或30°×3-5.5°×n =-3 0°n1 = 120/11 <15(不合题意,舍去)n2 = 240/11 240/11-15 = 75/11 ≈7

菜鸟学arm之arm时钟系统与锁相环的学习(基于arm7内核)

ARM7内核的时钟系统与锁相环(PLL) ——基于LPC2103(arm7内核)的讲解 注:该内容适用于大部分arm7内核的芯片 By:小飞胡 Q1906723068

概述:学过51单片机的孩子都知道单片机的时钟频率这个概念,也经常根据频率来做一些定时方面的实验。是的,51的时钟系统是比较简单的,芯片的时钟频率就等于外部所接晶振的频率,而一个机器周期又等于12个时钟周期,即6拍。关于51的时钟内容就这么多,关系也很清楚,所以很容易就可以使用。但对于arm芯片来说,时钟系统是比较复杂的,它有一个专门的时钟管理的部件。由于arm芯片要求CPU高速工作,但芯片的各个外设又不能速度太快,可见直接把所有部件的时钟同一为单一时钟源显然不合适,有时芯片又要根据不同的工作来改变不同的时钟频率,这就要求芯片内部的时钟是可以认为设定的。但芯片外接的时钟源或晶振的值一般都是确定的,这怎么解决,下边我要讲的就是这个问题。 我们先来了解一下arm7的晶体振荡器,以LPC系列的为例,其他型号的芯片可以详细查阅相关资料。 晶体振荡器输入端XTAL1可接受1MHz--50MHz占空比为50%的时钟信号,内部振荡电路支持1MHz--30MHz的外部晶体。如果片内PLL系统或引导装载程序被使用,输入时钟将被限制到10MHz-- 25MHz,先看一个图 振荡器输出频率称为Fosc,ARM处理器时钟频率成为cclk.除非使用PLL,否则Fosc和cclk的值相同。 振荡器可以工作在两种模式下:从属模式和振荡模式。

从属模式下,输入时钟信号与一个100pf相连,其幅值不少于200mVrms,X2管脚不连接。如果选用从属模式,Fosc信号的频率被限制在1MHz--50MHz。如果器件振荡器工作在振荡模式,Fosc时钟被限制在1MHz--30MHz。 注:以上的一些数值会因不同的型号而不尽相同,具体的数值要根据具体型号的芯片数据手册确定,这里我只是要让你明白其原理与思想。其实很多事重要的都是想法,只要想法是对的,剩下的就只是去把想法给变为实际行动了,这是比较简单的。

钟表中的角度计算问题

钟表中的角度计算问题 1.如图是一个时钟的钟面,下午1点30分,时钟的分针与时针所夹的角等于°.2.时钟在1点20分,时针与分针的夹角为. 3.从中午12时整到下午3时整,钟表时针所转过的角的度数是. 4.时钟在6时30分时,时针与分针的夹角等于. 5.10:10时,时针与分针的夹角为. 9.8点55分时,钟表上时针与分针的所成的角是. 10.2点30分时针和分针的夹角为度. 18.有一只手表每小时比准确时间慢3分钟,若在清晨4:30与准确时间对准,则当天上午手表指示的时间是10:50,准确时间应该是. 19.(2014?黄冈模拟)3点12分和3点40分时,时针与分针构成的角各是度和度. 20.(2013秋?吴江市期末)钟表上8点30分时,时针与分针所夹的锐角是度. 21.在下午的2点30分时,时针与分针的夹角为度. 22.(2014秋?新郑市校级期末)时钟在2点正时,其时针和分针所成的角的大小 为°. 23.(2014秋?汉阳区期末)2点30分时,时针与分针所成的角是度. 24.(2014秋?阜宁县期末)上午10点30分,时针与分针成度的角. 25.(2014秋?铜陵期末)8点20分时,钟表上时针与分针的所成的角是 . 26.(2014秋?武威校级期末)钟表在3点30分时,它的时针与分针所夹的角是 度. 27.(2014秋?长汀县期末)上午8:30钟表的时针和分针构成角的度数是.

28.(2014秋?雅安期末)现在的时间是9时20分,此时钟面上时针与分针夹角的度数是度. 29.(2014秋?衡阳县期末)9时45分时,时钟的时针与分针的夹角是. 30.(2014秋?合肥期末)上午9:40时,时针与分针夹角为度.

学习STM32笔记2如何配置时钟

学习STM32笔记2 如何配置时钟* 学习STM32笔记2 如何配置时钟 原创笔记2009-09-20 19:56 阅读116 评论0 字号:大中小 /************************************************************* 该程序目的是用于测试核心板回来后是否能正常工作。包括 两个按键、两个LED现实。按键为PC4、PC5,LED为PA0\PA1。LED为 低电平时点亮。按键为低电平时触发。 ************************************************************/ #i nclude "stm32f10x_lib.h" void RCC_Configuration(void);//设置系统主时钟 void GPIO_Configuration(void);//设置邋邋IO参数 void NVIC_Configuration(void);//设置中断表地址 void delay(void);//延时函数 int main(void) { #ifdef DEBUG debug(); #endifRCC_Configuration(); NVIC_Configuration(); GPIO_Configuration(); while (1) { delay(); //设置指定的数据端口位 GPIO_SetBits(GPIOA,GPIO_Pin_0); //设置指定的数据端口位 delay(); GPIO_ResetBits(GPIOA,GPIO_Pin_0); //清除指定的数据端口位 GPIO_SetBits(GPIOA,GPIO_Pin_1); delay(); GPIO_ResetBits(GPIOA,GPIO_Pin_1); delay(); /********************************************* 使用setbits 与resetbits 是比较简单,其实还是可以使用 其它函数。例如可以使用GPIO_WriteBit GPIO_WriteBit(GPIOA, GPIO_Pin_1, Bit_SET); GPIO_WriteBit(GPIOA, GPIO_Pin_1, Bit_RESET);对于好像流水灯呀这些一个整段IO,可以使用GPIO_Write(GPIOA, 0x1101); *********************************************/

巧用公式计算钟表角

巧用公式计算钟表角 在平日的学习过程和近几年中考试题中,我们常会遇到与钟表上的角度计算有关的问题,多数师生在解决这类问题时感到困难大,通常都会采用画简易的表盘示意图的形式,去数两针之间的所夹的格数,既费时又易错。若能仅从时针、分针转动所成的角度入手解决则较容易。我们知道,时针、分针转动一周经过12大格或60小格.因此,每小时时针转动30°,每分钟分针转动6°,每分钟时针转动0.5°。假设时间是m时n分,在教学中笔者得到了钟表角的计算公式是:∣m×30°+0.5°n-6°n ∣。下面就常见的几种典型例题对此公式的应用加以举例说明: 一、求某一时刻时针、分针的夹角. 例1.9点22分时,时针与分针的夹角是多少度? 22)×30°=281°,分针转过了22×6°=132°,解:9点22分时,时针转过了(9+ 60 其度差为∣281°-132°∣=149°,∴时针与分针的夹角是149°. 例2.7点40分时,时针与分针的夹角是多少度? 40)×30°=230°,分针转过了40×6°=240°,解:7点40分时,时针转过了(7+ 60 其度差为∣230°-240°∣=10°,∴时针与分针的夹角是10°. 例3. 2点54分时,时针与分针的夹角是多少度? 分析:求法与上两例大致相同,不过一般情况我们求出的夹角是小于180°的角。 54)×30°=87°,分针转过了54×6°=324°,解:2点54分时,时针转过了(2+ 60 其度差为∣87°-324°∣=237°,(大于180°,而习惯上所说的夹角都是小于180)∴时针与分针的夹角是360°-237°=123°. 二、求时针与分针的重合时间. 例4.12点后,时针与分针何时首次重合? 分析:时针与分针重合时,其角度差为0°,则可通过:时针转过的角度-分针转

SPI时钟模式的配置

S P I时钟模式的配置集团标准化小组:[VVOPPT-JOPP28-JPPTL98-LOPPNN]

【S P I基础知识简介】 设备与设备之间通过某种硬件接口通讯,目前存在很多种接口,SPI接口是其中的一种。 SPI中分Master主设备和Slave从设备,数据发送都是由Master控制。 一个master可以接一个或多个slave。 常见用法是一个Master接一个slave,只需要4根线: SCLK:SerialClock,(串行)时钟 MISO:MasterInSlaveOut,主设备输入,从设备输出 MOSI:MasterOutSlaveIn,主设备输出,从设备输入 SS:SlaveSelect,选中从设备,片选 SPI由于接口相对简单(只需要4根线),用途算是比较广泛,主要应用在EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。 即一个SPI的Master通过SPI与一个从设备,即上述的那些Flash,ADC等,进行通讯。 而主从设备之间通过SPI进行通讯,首先要保证两者之间时钟SCLK要一致,互相要商量好了,要匹配,否则,就没法正常通讯了,即保证时序上的一致才可正常讯。 而这里的SPI中的时钟和相位,指的就是SCLk时钟的特性,即保证主从设备两者的时钟的特性一致了,以保证两者可以正常实现SPI通讯。 【SPI相关的缩写或说法】 先简单说一下,关于SPI中一些常见的说法: SPI的极性Polarity和相位Phase,最常见的写法是CPOL和CPHA,不过也有一些其他写法,简单总结如下: (1)CKPOL(ClockPolarity)=CPOL=POL=Polarity=(时钟)极性 (2)CKPHA(ClockPhase)=CPHA=PHA=Phase=(时钟)相位 (3)SCK=SCLK=SPI的时钟 (4)Edge=边沿,即时钟电平变化的时刻,即上升沿(risingedge)或者下降沿(fallingedge) 对于一个时钟周期内,有两个edge,分别称为: Leadingedge=前一个边沿=第一个边沿,对于开始电压是1,那么就是1变成0的时候,对于开始电压是0,那么就是0变成1的时候; Trailingedge=后一个边沿=第二个边沿,对于开始电压是1,那么就是0变成1的时候(即在第一次1变成0之后,才可能有后面的0变成1),对于开始电压是0,那么就是1变成0的时候;

(完整版)锁相环工作原理

基本组成和锁相环电路 1、频率合成器电路 频率合成器组成: 频率合成器电路为本机收发电路的频率源,产生接收第一本机信号源和发射电路的发射信号源,发射信号源主要由锁相环和VCO电路直接产生。如图3-4所示。 在现在的移动通信终端中,用于射频前端上下变频的本振源(LO),在射频电路中起着非常重要的作用。本振源通常是由锁相环电路(Phase-Locked Loop)来实现。 2.锁相环: 它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域 3.锁相环基本原理: 锁相环包含三个主要的部分:⑴鉴相器(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。⑶压控振荡器(VCO):振

荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。在PLL中,压控振荡器实际上是把控制电压转换为相位。 1、压控振荡器的输出经过采集并分频; 2、和基准信号同时输入鉴相器; 3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压; 4、控制VCO,使它的频率改变; 5、这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。 锁相环电路是一种相位负反馈系统。一个完整的锁相环电路是由晶振、鉴相器、R分频器、N分频器、压控振荡器(VCO)、低通滤波器(LFP)构成,并留有数据控制接口。 锁相环电路的工作原理是:在控制接口对R分频器和N分频器完成参数配置后。晶振产生的参考频率(Fref)经R分频后输入到鉴相器,同时VCO的输出频率(Fout)也经N分频后输入到鉴相器,鉴相器对这两个信号进行相位比较,将比较的相位差以电压或电流的方式输出,并通过LFP滤波,加到VCO的调制端,从而控制VCO的输出频率,使鉴相器两输入端的输入频率相等。 锁相环电路的计算公式见公式: Fout=(N/R)Fref 由公式可见,只要合理设置数值N和R,就可以通过锁相环电路产生所需要的高频信号。 4.锁相环芯片 锁相环的基准频率为13MHz,通过内部固定数字频率分频器生成5KHz或6.25KHz的参考频率。VCO振荡频率通过IC1 内部的可编程分频器分频后,与基准频率进行相位比较,产生误差控制信号,去控制VCO,改变VCO的振荡频率,从而使VCO输出的频率满足要求。如图3-5所示。 N=F VCO/F R N:分频次数 F VCO:VCO振荡频率

数学里的钟表问题 “钟面角”

钟表问题“钟面角” 日常生活中,我们几乎每天都要看钟表,然而我们对钟表表面上的时针、分针、秒针之间的夹角(即“钟面角”)问题可能并没有在意.其实钟面角中蕴涵着丰富的数学知识,我们一起来探究一下“钟面角”问题吧. 一、认识“钟面角” 要分析钟面角,我们首先要结合其图形特点,寻找并发现它们的变化规律. ⑴钟表的表面特点:钟表的表面都是一个圆形,共有12个大格,每个大格间有5个小格.圆形的表面恰好对应着一个周角360°,每个大格对应30°角,每个小格对应6°角.表面一般有时针、分针、秒针三根指针. ⑵钟表时针、分针、秒针的转动情况:时针每小时转1大格,每12分钟转1小格,每12个小时转1个圆周;分针每5分钟转一大格,每1分钟转1小格,每小时转1个圆周;秒针5秒钟转1大格,每1秒钟转1小格,每1分钟转一个圆周. ⑶时针、分针、秒针的转速:有了以上的认识,我们很容易计算出相应指针的转速:①钟表的时针转速为:30°/小时或0.5°/分钟;②分针的转速为:6°/分钟或0.1°/秒钟;③秒针的转速为:6°/秒. 有了这些对钟面角的基本认识,我们就可以探究与钟面角有关的问题了. 二、解决与钟面角有关的数学问题 ⒈计算从某一时刻到另一时刻,时针(分针)转过的角度 ⑴公式法:时(分)针从某一时刻到另一时刻转过的角度=时(分)针转过的时间×时(分)针的转速(注意统一单位). ⑵观察法:若时(分)针转过了a大格b小格,则时(分)针从某一时刻到另一时刻转过的角度为:30a+6b°. 例1.⑴从3:15到7:45,时针转过度. ⑵从1:45到2:05,分针转过度. 分析:⑴从3:15到7:45,时针走过的时间为4.5小时(270分钟),∴时针转过的角度为:4.5×30°=135°(或270×0.5°=135°) 或用观察法:时针共走了4大格2.5小格,∴时针转过的角度为:4×30+2.5×6=135°.⑵从1:45到2:05,分钟走过的时间为20分钟,∴分针转过的角度为:20×6°=120°. 或用观察法:分针共走了4个大格(或20小格)∴分针转过的角度为:4×30°=120°(或:20×6°=120°). ⒉计算某一时刻时针(分针)与分针(秒针)之间的夹角 ⑴求差法:以0点(12时)为基准到某一时刻止,时针转过的角度与分针在整点后的时间转过的角度差,即时针、分针之间的夹角. ⑵观察法:某一时刻时针、分针相差a个大格b个小格,时针分针的钟面角=30a+6b°. 例2.⑴4:00点整,时针、分针的夹角为. ⑵11:40,时针、分针的夹角为. 分析:⑴4:00整,时针、分针相差4个大格,夹角为:4×30°=120°. ⑵①作差法:11:40,以0点(12时)为基准 时针转过的角度为:11×30°=350° 分针转过的角度为:40×6°=240° ∴时针、分针的夹角为:350°-240°=110°