位CPU设计与实现

计

算

机

组

成

原

理

论

文

姓名:某某

班级:计科一班

学号:

8位CPU的设计与实现论文CPU 的主要功能是执行指令,控制完成计算机的各项操作,包括运算操作、传送操作、输入/输出操作等。作为模型计算机设计,将重点放在寄存器组,采取较简单的组成模式,以尽量简洁的设计帮助读者掌握CPU 的基本原理。

此次设计CPU就是为了了解CPU运行的原理,从而完成从指令系统到CPU 的设计,并且通过仿真对CPU设计进行正确性评定。

关键词:CPU,设计指标,电路原理图,运算部件,寄存器组,模型机

指令系统,微命令序列,数据通路

1. 设计的任务与要求

1.1设计指标

1. 能实现IN(输入)、ADD(二进制加法)、STA(存数)、OUT(输出)、JMP

(无条件转移)这五种指令;

2. 整个系统能正常稳定工作。

1.2 设计要求

1. 画出电路原理图;

2.写出设计的全过程,附上有关资料和图纸(也可直接写在相关章节中),有

心得体会。

2. 方案论证与选择

2.1 CPU的系统方案

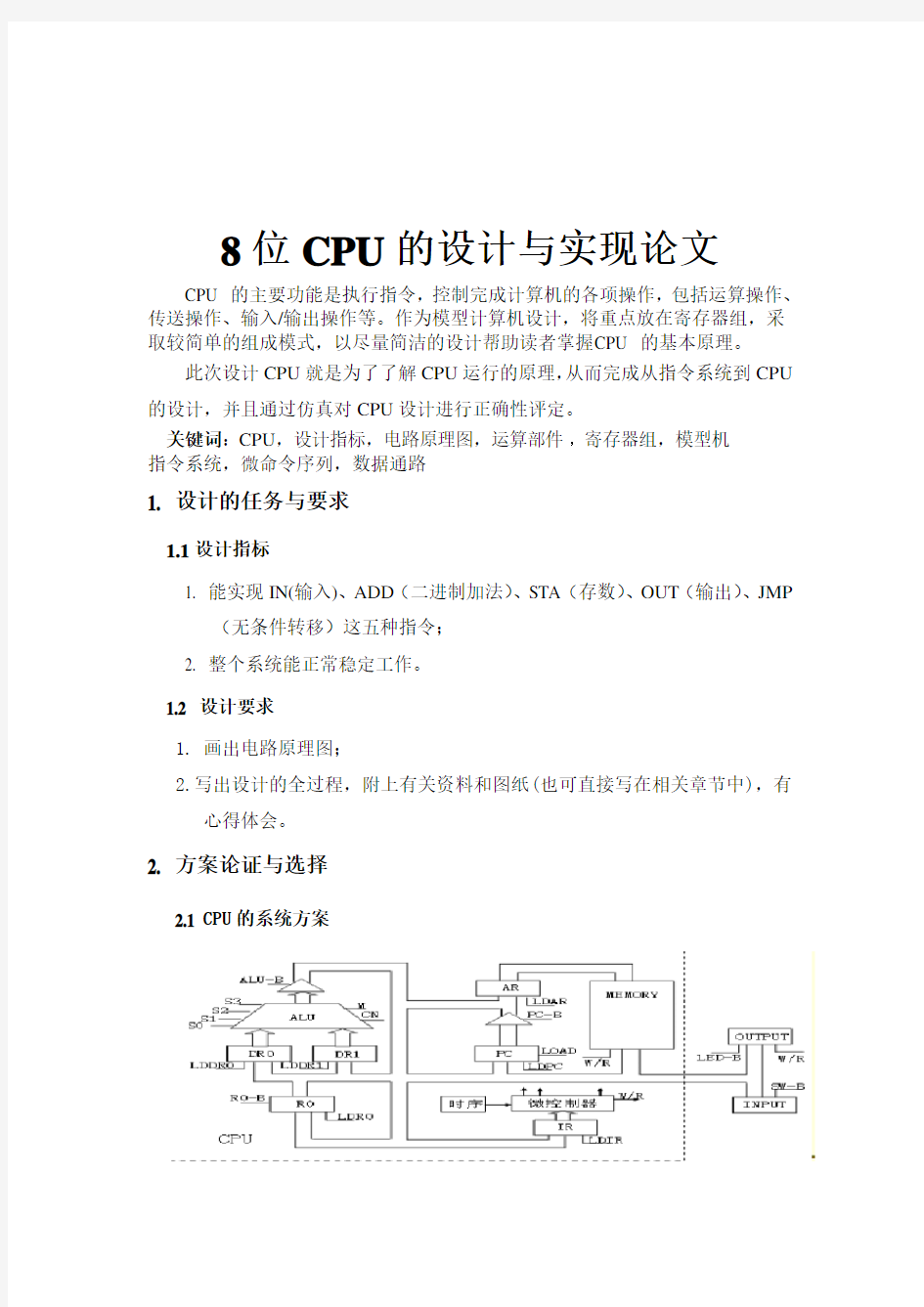

CPU 主要由算术逻辑单元ALU,数据暂存寄存器DR1、DR2,数据寄存器R0~R2,程序计数器PC,地址寄存器AR,程序/数据存储器MEMORAY,指令寄存器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所组成。图中虚线框内部分包括运算器、控制器、程序存储器、数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现。虚线框外部分主要是输入/输出装置,包括键盘、数码管、LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及观察CPU 内部工作情况及运算结果。

1.运算部件

运算部件的任务是对操作数进行加工处理。主要由三部分组成:

(1)输入逻辑。(2)算术/逻辑运算部件ALU。(3)输出逻辑

2.寄存器组

计算机工作时,CPU 需要处理大量的控制信息和数据信息。例如对指令信息进行译码,以便产生相应控制命令对操作数进行算术或逻辑运算加工,并且根据运算结果决定后续操作等。因此,在CPU 中需要设置若干寄存器,暂时存放这些信息。在模型CPU中,寄存器组由R0、R1、R2 所组成。

3.指令寄存器指令寄存器(IR)

指令寄存器指令寄存器(IR)用来存放当前正在执行的指令,它的输出包括操作码信息、地址信息等,是产生微命令的主要逻辑依据。

4.程序计数器程序计数器(PC)

程序计数器程序计数器也称指令指针,用来指示指令在存储器中的存放位置。当程序顺序执行时,每次从主存取出一条指令,PC 内容就增量计数,指向下一条指令的地址。增量值取决于现行指令所占的存储单元数。如果现行指令只占一个存储单元,则PC 内容加1;若现行指令占了两个存储单元,那么PC 内容就要加2。当程序需要转移时,将转移地址送入PC,使PC 指向新的指令地址。因此,当现行指令执行完,PC 中存放的总是后续指令的地址;将该地址送往主存的地址寄存器AR,便可从存储器读取下一条指令。

5.地址寄存器

CPU 访问存储器,首先要找到需要访问的存储单元,因此设置地址寄存器(AR)来存放被访单元的地址。当需要读取指令时,CPU 先将PC 的内容送入AR,再由AR将指令地址送往存储器。当需要读取或存放数据时,也要先将该数据的有效地址送入AR,再对存储器进行读写操作。

6.标志寄存器

标志寄存器F是用来记录现行程序的运行状态和指示程序的工作方式的,标志位则用来反映当前程序的执行状态。一条指令执行后,CPU 根据执行结果设置相应特征位,作为决定程序流向的判断依据。例如,当特征位的状态与转移条件符合时,程序就进行转移;如果不符合,则顺序执行。在后面将要介绍的较复杂模型计算机设计中设置了两个标志位:进位Fc、零位Fz。

7.微指令产生部件

实现信息传送要靠微命令的控制,因此在CPU 中设置微命令产生部件,

根据控制信息产生微命令序列,对指令功能所要求的数据传送进行控制,

同时在数据传送至运算部件时控制完成运算处理。

微命令产生部件可由若干组合逻辑电路组成,也可以由专门的存储逻辑组成。产生微命令的方式可分为组合逻辑控制方式和微程序控制方式两种。在本章所介绍的8 位模型CPU 设计中,采用微程序控制方式通过微程序控制器和微指令存储器

产生微命令,因此此CPU 属于复杂指令CISC CPU。

8.时序系统

计算机的工作常常是分步执行的,那么就需要有一种时间信号作为分

步执行的标志,如周期、节拍等。节拍是执行一个单步操作所需的时间,

一个周期可能包含几个节拍。这样,一条指令在执行过程中,根据不同

的周期、节拍信号,就能在不同的时间发出不同的微命令完成不同的微

操作。周期、节拍、脉冲等信号称为时序信号,产生时序信号的部件称

为时序发生器或时序系统,它由一组触发器组成。由石英晶体振荡器输

出频率稳定的脉冲信号,也称时钟脉冲,为CPU 提供时钟基准。时钟脉

冲经过一系列计数分频,产生所需的节拍(时钟周期)信号。时钟脉冲

与周期、节拍信号和有关控制条件相结合,可以产生所需的各种工作脉

冲。

2.2模型机指令系统

一条指令必须包含下列信息:

操作码、操作数的地址、操作结果的存储地址、下一条指令的地址。

指令的基本格式

op-code 为操作码,rs为源寄存器,rd 为目的寄存器

寄存器操作数

模型机指令系统,及其指令编码形式

设模型机指令系统中包含有五条基本指令,分为算术运算指令、存取指令和控制转移指令等三种类型。五条机器指令分别是:IN(输入)、ADD(二进制加法)、STA(存数)、OUT(输出)、JMP(无条件转移)。IN 为单字长(8 位二进制),其余为双字长指令,XX H 为addr对应的十六进制地址码。

2.3 拟定指令流程和微命令序列(计算机设计中最关键步骤)

1.微程序控制概念

(1)微命令和微操作

一条机器指令可以分解成一个微操作序列,这些微操作是计算机中最基

本的,不可再分解的操作。在微程序控制的计算机中,将控制部件向执行部

件发出的各种控制命令叫做微命令,它是构成控制序列的最小单位。因此,

微命令是控制计算机各部件完成某个基本微操作的命令。

微命令和微操作是一一对应的。微命令是微操作的控制信号,微操作是微命令的操作过程。微命令有兼容性和互斥性之分。兼容性微命令是指那些可以同时产生,共同完成某一些微操作的微命令;而互斥性微命令是指在机器中不允许同时出现的微命令。兼容和互斥都是相对的,一个微命令可以和一些微命令兼容,和另一些微命令互斥。对于单独一个微命令,就无所谓兼容性或互斥性了。

(2)微指令、微地址

微指令是指控制存储器中的一个单元的内容,即控制字,是若干个

微命令的集合,存放控制字的控制存储器的单元地址就称为微地址。一

条微指令通常至少包含两大部分信息:

微操作码字段,又称操作控制字段,该字段指出微指令执行的微操作;

微地址码字段,又称顺序控制字段,指出下一条要执行的微指令的地址。

(3)微周期

所谓微周期是指从控存中读取出一条微指令并执行规定的相应操作所需的时间。

(4)微程序

一系列微指令的有序集合就是微程序。若干条有序的微指令构成了微程序。微程序可以控制实现一条机器指令的功能。或者说一条机器指令可以分解为特定的微指令序列。一旦机器的指令系统确定以后,每条指令所对应的微程序被设计好并且存入控存后,控存总是处于只读的工作状态,所以控存一般采用只读存储器(ROM)存放。重新设计控存内容就能增加、删除、修改机器指令系统。在FPGA 中通常采用嵌入式阵列块构成的LPM_ROM 作为控存,存放微指令。

2.微指令格式

(1)水平型微指令

一次能定义并执行多个并行操作微命令的微指令。

按照操作控制字段的编码方法不同,水平型微命令又分为三种:第一种是全水平型(不译码法)微指令,第二种是字段译码法水平型微指令,第三种是直接和字段译码相混合的水平型微指令。

(2)垂直型微指令

垂直型微指令中设置操作码字段,由微操作码规定微指令的功能。

垂直型微指令的结构类似于机器指令的结构。在一条微指令中只存一二个微命令,每条微指令的功能比较简单。因此,实现一条机器指令的微程序要比水平型微指令编写的微程序长得多,它是采用较长的微程序结构去换取较短的微指令结构。

3.模型机的微指令

uA5~uA0:微程序控制器的微地址输出信号,是下一条要执行的微指令的微地址。

S3、S2、Sl、S0:由微程序控制器输出的ALU 操作选择信号,以控制执行16 种算术操作或16 种逻辑操作中的某一种操作。

M:微程序控制输出的ALU 操作方式选择信号。M=0 执行算术操作;M=l执行逻辑操作。。Cn:微程序控制器输出的进位标志信号,Cn=0 表示ALU 运算时最低位有进位;Cn=1 则表示无进位。

WE:微程序控制器输出的RAM 控制信号。当CE=0 时,如WE=0,为存储器读;如WE=1,为存储器写。A9、A8:译码后产生CS0、CS1、CS2 信号,分别作为SW_B、RAM、LED 的选通控制信号。

A 字段(15、14、13):译码后产生与总线相连接的各单元的输入选通

信号。

B 字段(12、11、10):译码后产生与总线相连接的各单元的输出选通

信号。

C 字段(9、8、7):译码后产生分支判断测试信号P(1)~P(4)和LDPC 信号。

4.微指令的执行方式

执行一条微指令的过程类似于机器指令的执行过程。首先,将微指令从

控存CM 中取出,称为取微指令。对于垂直型微指令还应包括微操作码的译

码时间。然后,执行微指令所规定的各个微操作。根据微指令的执行方式

可分为串行执行和并行执行两种。

5.时序安排

由于CPU 的工作是分步进行的,而且需要严格定时控制,因此设置时序信号,以便在不同的时间发出不同的微命令,控制完成不同的操作。组合逻辑控制方式和微程序控制方式在时序安排上有区别,前者多采用三级时序划分,而后者往往采用两级时序。

6.拟定指令流程和微命令序列

这是设计中最关键的步骤,这是由于需要根据这一步的设计结果形

成最后的控制逻辑。拟定指令流程是将指令执行过程中的每步传送操作

(寄存器之间的信息传送),用流程图的形式描述出来,拟定微命令序

列是用操作时间表列出每步操作所需的微命令及其产生条件。

7.形成控制逻辑

设计的最后一步。采用组合逻辑控制方式或采用程序控制方式,有各自不同的设计方法。在组合逻辑控制方式中,将产生微命令的条件进行综合、化简,形成逻辑式,从而构成控制器的核心逻辑电路。在微程序控制方式中,则是根据微命令来编写微指令,组成微程序,从而构成以控制存储器为核心的控制逻辑。

2.4 微程序设计

1.IN指令

为了执行输入指令,CPU 要做两件事情。首先,由INPUT 输入装置的数据开关SW输入数据送到数据总线上;其次,通过数据总线将输入的数据写入寄存器R0 中。

2.ADD指令 R0←R0+(MEM)

存储单元的地址是存放在紧跟在操作码后的字节中的,因此,首先要以该字节的内容为地址,即将该单元内容送地址寄存器AR;然后,从AR 所指向的RAM 存储单元取出操作数送给DR2。由于在取指令操作码时,PC 已经自动加1,指向下一字节,该地址就是存放操作数的存储单元的地址。

3.STA指令

向存储器RAM 写数据操作STA,以紧跟在操作码后的字节作为存放操作

数地址,将R0 中的数据存入该地址单元。首先将紧跟在操作码后的字节

的内容送给地址寄存器AR。

4. OUT指令

AR←PC,PC←PC+1;以PC的内容作为存数据的地址

BUS←RAM,AR←BUS;AR指向存放操作数的RAM单元

BUS←RAM,DR1←BUS

OUT←DR1

5.JMP指令

AR←PC,PC←PC+1 ;以PC的内容作为取数据的地址

BUS←RAM,PC←BUS ;将RAM内容送PC,实现程序转移

3. CPU设计及微代码

3.1 原理图模版

3.2取指令和指令

1.取指令阶段

取指令阶段完成的任务是将现行指令从主存中取出来并送至指令寄存器中。具体的操作如下:

(1)将程序计数器(PC)中的内容送至存储器地址寄存器(AR),并送往地址总线(AB)。

(2)PC 的内容递增,为取下一条指令做好准备。

(3)由控制单元(CU)经控制总线(CB)向存储器发读命令。

(4)从主存中取出的指令通过数据总线(DB)送到指令寄存器(IR)中。以上这些操作对任何一条指令来说都是必须要执行的操作,所以称为公共操作。完成取指阶段任务的时间称为取指周期。取出指令后,指令译码器ID 可识别和区分出不同的指令类型。此时计算机进入分析取数阶段,以获取操作数。由于各条指令功能不同,寻址方式也不同,所以分析取数阶段的操作是各不相同的。(5)指令寄存器(IR)中的内容送指令译码器(ID)进行指令译码。

(6)指令译码器(ID)的内容送操作控制器。

(7)操作控制器产生执行指令的微控制。

2. 分析取数阶段

对于无操作数指令,只要识别出是哪条具体的指令,即可以直接转至执行阶段,所以不需进入分析取数阶段。而对于带操作数指令,为读取操作数首先要计算出操作数的有效地址。如果操作数在通用寄存器内,则不需要再访问主存;如果操作数在主存中,则要到主存中去取数。对于不同的寻址方式,有效地址的计算方法是不同的,有时要多次访问主存才能取出操作数(间接寻址)。对于无操作数指令,只要识别出是哪条具体的指令,即可以直接转至执行阶段,所以不需

进入分析取数阶段。而对于带操作数指令,为读取操作数首先要计算出操作数的有效地址。如果操作数在通用寄存器内,则不需要再访问主存;如果操作数在主存中,则要到主存中去取数。对于不同的寻址方式,有效地址的计算方法是不同的,有时要多次访问主存才能取出操作数(间接寻址)。另外对于单操作数指令和双操作数指令,由于需要的操作数的个数不同,分析取数阶段的操作也不同。

3. 执行阶段

执行指令阶段完成指令规定的各种操作。执行阶段完成任务的时间称为执行周期。计算机的基本操作过程就是取指令、取操作数、执行指令,然后再取下一条指令……如此周而复始,直至遇到停机指令或外来的干预为止。

3.3设计微代码表

微程序流程图是根据每条指令的微操作流程所绘制的,操作框内给出的是该微操作要执行的动作。当拟定“取指”微指令时,该微指令的判别测试字段为P (1)测试,根据P(1)的测试结果将出现多路分支。由于操作码的位数已确定为4 位,所以可直接将操作码与微地址码的部分对应。本模型机用指令寄存器(IR7~IR0)的高4 位(IR7~IR4)与微地址码的后4 位对应。

模型机的微地址码共有六位,微地址码的高三位已固定为001,低三位从000~111 共有八种状态,现设计了五条指令,需要五个分支入口,因此,将低三位中的000B~100B 这五个地址分配给这五条指令,就得到五个分支入口微地址。

这五个分支入口(以八进制表示)分别是10、11、12、13 和14,占用五个固定的微地址单元。其余的微操作单元的微地址设置,可以将还未使用的微地址按照从小到大的顺序依次分配给这些微操作单元,微地址的分配情况见图5-4。微地址标注在每个微操作框的左上角,右上角标注的是微指令码。

3.4 建立数据通路

ALU 为运算器;DR0 和DR1 为其输入端的两个暂存寄存器;R0 是数据寄存器,用来保存数据和运算结果;PC 为程序计数器;IR 和ID 分别为指令寄存器和指令译码器;AR 和MOMERY 分别为存储地址寄存器和存储数据寄存器;INPUT 为输入装置;OUTPUT 为输出装置。各基本单元模块的输出端通过三态门控制与内部数据总线相连接;微控制器按照时序发生器的节拍,对指令进行译码后产生同步的控制信号。各部件旁边的C 是由微指令译码器输出的控制信号,用于控制数据的输入和输出。与数据总线相连的信号有些是单向的,有些则是双向的。如数据寄存器、存储器、I/O 接口的数据信号是双向的,而指令信号、地址信号、控制信号是单向的。实际上在FPGA 中,双向端口元件的表述方法是:输入和输出端口采用两个不同的端口,这时各基本元件的输出端口不能直接与内部总线连接在一起,而是需要通过三态门控制以后再连接到总线上。在向总线输出数据时,不能同时有两路或两路以上数据一起输出,否则会发生数据冲突。因此在设计微程序、确定微操作时,应注意数据传输中控制信号对时序的要求。

3.5 微程序控制的基本原理

3.6 在模型CPU中的软件执行

微指令执行情况

4.心得体会

通过此次的设计,我受益匪浅。首先,我对CPU有了基本认识,认识它的原理,结构,运行;其次,我对微指令的认识也有了进一步提高,特别是指令对应的功能以及对指令的理解;再次,我对该部件的原理及功能运行有了一定层次的理解;最后,我必须承认,不管遇到什么问题都要从底层抓起,然后去解决问题,当我对某些东西不懂时,要从书本的最基本概念看起,再到原理,运行层次,结构等去理解才能真正懂,还有和他人的交流很重要,不懂的问题彼此交换意见可以受益匪浅。我很感谢此次机会让我有了一次锻炼。

参考文献:

[1] 潘松潘明. 现代计算机组成原理. 科学出版社.

[2] 王爱英.计算机组成与结构(第四版).清华大学出版社。

精简8位cpu设计报告

精简8位cpu实验设计报告 实验介绍: 实验分为两个部分,第一部分为16*8 ROM 设计与仿真 第二部分为SAP-1 设计与仿真 实验流程: ①16*8 ROM 的设计与仿真 Rom16_8.VHDL LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ENTITY ROM16_8 is PORT( DATAOUT :OUT STD_LOGIC_VECTOR(7 DOWNTO 0); --Data Output ADDR :IN STD_LOGIC_VECTOR(3 DOWNTO 0); --ADDRESS CE :IN STD_LOGIC --Chip Enable ); END ROM16_8; ARCHITECTURE a OF ROM 16_8 IS BEGIN DATA<=“00001001”WHEN ADDR=“0000”AND CE=‘0’--LDA 9H “00011010”WHEN ADDR=“0001”AND CE=‘0’ELSE --ADD AH “00011011”WHEN ADDR=“0010”AND CE=‘0’ELSE --ADD BH “00101100”WHEN ADDR=“0011”AND CE=‘0’ELSE --SUB CH “11100000”WHEN ADDR=“0100”AND CE=‘0’ELSE --OUT “11110000”WHEN ADDR=“0101”AND CE=‘0’ELSE --HLT “00010000”WHEN ADDR=“1001”AND CE=‘0’ELSE “00010100”WHEN ADDR=“1010”AND CE=‘0’ELSE “00011000”WHEN ADDR=“1011”AND CE=‘0’ELSE

计算机硬件课程设计报告(cpu设计)

计算机硬件课程设计 设计报告 学号: 姓名:成绩: 学号: 姓名:成绩: 东南大学计算机科学与工程系 二0 10 年11 月

一、设计名称: My CPU的设计 二、本设计的主要特色: 1、熟悉挂总线的逻辑器件的特性和总线传送的逻辑实现方法。 2、掌握半导体静态存储器的存取方法。 三、设计方案: 1. 数据格式——8位二进制定点表示 2. 指令系统——CPU的指令格式尽量简单规整,这样在硬件上更加容易实现。 7条基本指令:输入/输出,数据传送,运算,程序控制。 指令格式:Array 7 6 5 4 3 2 1 0 两种寻址方式: 寄存器寻址Array 7 6 5 4 3 2 1 0 直接地址寻址,由于地址要占用一个字节,所以为双字节指令。 7条机器指令:

IN R目:从开关输入数据到指定的寄存器R目。 OUT R源:从指定的寄存器R源中读取数据送入到输出缓冲寄存器,显示灯亮。 ADD R目,R源:将两个寄存器的数据相加,结果送到R目。 JMP address : 无条件转移指令。 HALT : 停机指令。 LD R目,address : 从内存指定单元中取出数据,送到指定寄存器R 目。 ST address , R 源: 从指定的寄存器R源中取出数据,存入内存指定单元。

Address(内存地址) 3. CPU内部结构 4.数据通路设计 根据指令系统,分析出数据通路中应包括寄存器组、存储器、运算器、多路转换器等,采用单总线结构。 通用寄存器组:

运算器: 存储器: 多路转换器:

输出缓冲器: 5.控制器设计 控制通路负责整个CPU的运行控制,主要由控制单元和多路选择器MUX 完成。在每一个时钟周期的上升沿指令寄存器IR 从内存中读取指令字后,控制单元必须能够根据操作码,为每个功能单元产生相应主控制信号,以及对ALU 提供控制信号。对于不同的指令,同一个功能单元的输入不同,需要多路选择器MUX 来对数据通路中功能单元的输入进行选择。

CPU课程设计报告

课程设计报告 课程片上计算机系统 题目 CPU模型机设计 班级 专业 学生 学号 指导教师 2014年7 月 3 日 目录: 1.课程设计的目的及要求 (3) 2.处理器的设计思想和设计内容 (3)

3.设计处理器的结构和实现方法 (3) 4.模型机的指令系统 (4) 5.处理器的状态跳转操作过程 (4) 6. CPU的Verilog代码 (7) 7. 模型机在Quartus II环境下的应用 (19) 8. 仿真波形 (19) 9. 课程设计的总结 (21) 一.课程设计的目的及要求: (一)目的: 1.掌握RISC CPU与内存数据交换的方法。 2.学会指令格式的设计与用汇编语言编写简易程序。 3.能够使用VHDL硬件描述语言在QuartusⅡ软件环境下完成CPU模型机的 设计。

(二)要求: 1.以《计算机组成与设计》书中123页的简化模型为基础更改其指令系 统,形成设计者的CPU, 2.在Quartus II环境下与主存连接,调试程序,观察指令的执行是否达 到设计构想。 二.处理器的设计思想和设计内容: 处理器的字长为16b;包括四种指令格式,格式1、格式2、格式3的指令字长度为8b,格式4的指令字长度为16b;处理器内部的状态机包括七个状态。(一)关于修改后的CPU: 一共设计25条指令,主要包括空操作指令、中断指令、加法指令、减法指令、加法指令、四种逻辑运算指令、比较、算术移位操作指令、逻辑移位操作指令、加减1指令、加减2指令、数据传输指令、转移类指令、读写指令、特权指令等等。 (二)关于RAM: 地址线设置成8bits,主存空间为4096words。 三.设计处理器的结构和实现方法: (指令格式) 格式1:寄存器寻址方式 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OP Rx Ry 空白 格式2:寄存器变址寻址方式 OP Ry 空白 格式3:立即数寻址方式 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OP I 空白 格式4:无操作数寻址方式 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OP 空白空白 格式5:直接寻址方式 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0 OP Addr 内存(2的12次方) 四.模型机的指令系统 CPU的指令集: 操作码OP IR(15..1 2) 指令 格式 指令的助记指令的内容

CPU设计实验报告

实验中央处理器的设计与实现 一、实验目的 1、理解中央处理器的原理图设计方法。 2、能够设计实现典型MIPS的11条指令。 二、实验要求 1、使用Logisim完成数据通路、控制器的设计与实现。 2、完成整个处理器的集成与验证。 3、撰写实验报告,并提交电路源文件。 三、实验环境 VMware Workstations Pro + Windows XP + Logisim-win-2.7.1 四、操作方法与实验步骤 1、数据通路的设计与实现 数据通路主要由NPC、指令存储器、32位寄存器文件、立即数扩展部件、ALU、数据存储器构成。其中指令存储器和数据存储器可直接调用软件库中的ROM和RAM元件直接完成,其余部件的设计如图所示: 图1.1 NPC

图1.2 32位寄存器

图1.3 立即数扩展部件 图1.4 ALU 2、控制器的设计与实现 控制器的主要设计思想如图所示 图2.1 控制器设计思想 输入 1 1 0

输出R-type ORI LW SW BEQ JUMP RegDst 1 0 0 x x x ALUSrc 0 1 1 1 0 x MemtoReg0 0 1 x x x RegWrite 1 1 1 0 0 0 MemWrite0 0 0 1 0 0 Branch 0 0 0 0 1 0 Jump 0 0 0 0 0 1 Extop x 0 1 1 1 x ALUop2 1 0 0 0 0 x ALUop1 x 1 0 0 x x ALUop0 x 0 0 0 1 x ALUop[2:0] Funct[3:0] 指令ALUctr[2:0] 111 0000 add 010 111 0010 sub 110 111 0100 and 000 111 0101 or 001 111 1010 slt 111 010 xxxx ori 001 000 xxxx Lw/sw 010 011 xxxx beq 110 表2.1 控制器设计真值表

中国32位嵌入式CPU芯片

2015-2020年中国32位嵌入式CPU芯片行业市场调研及未来发展分析报告 Special Statenent特别声明 本报告由华经视点独家撰写并出版发行,报告版权归华经视点所有。本报告是华经视点专家、分析师调研、统计、分析整理而得,具有独立自主知识产权,报告仅为有偿提供给购买报告的客户使用。未经授权,任何网站或媒体不得转载或引用本报告内容,华经视点有权依法追究其法律责任。如需订阅研究报告,请直接联系本网站客服人员(8610-56188812 56188813),以便获得全程优质完善服务。 华经视点是中国拥有研究人员数量最多,规模最大,综合实力最强的研究咨询机构(欢迎客户上门考察),公司长期跟踪各大行业最新动态、资讯,并且每日发表独家观点。 目前华经视点业务范围主要覆盖市场研究报告、投资咨询报告、行业研究报告、市场预测报告、市场调查报告、征信报告、项目可行性研究报告、商业计划书、IPO上市咨询等领域,同时也为个阶层人士提供论文、报告等指导服务,是一家多层次、多维度的综合性信息研究咨询服务机构。 Report Description报告描述 本研究报告由华经视点公司领衔撰写。报告以行业为研究对象,基于行业的现状,行业运行数据,行业供需,行业竞争格局,重点企业经营分析,行业产业链进行分析,对市场的发展状况、供需状况、竞争格局、赢利水平、发展趋势等进行了分析,预测行业的发展前景和投资价值。在周密的市场调研基础上,通过最深入的数据挖掘,从多个角度去评估企业市场地位,准确挖掘企业的成长性,为企业提供新的投资机会和可借鉴的操作模式,对欲在行业从事资本运作的经济实体等单位准确了解目前行业发展动态,把握企业定位和发展方向有重要参考价值。报告还对下游行业的发展进行了探讨,是企业、投资部门、研究机构准确了解目前中国市场发展动态,把握行业发展方向,为企业经营决策提供重要参考的依据。 Report Directory报告目录 第一章研究范围界定及市场特征分析 第一节CPU芯片分类及应用 一、CPU芯片分类 二、CPU芯片应用

设计报告(电子版)

单片机应用设计实践报告 课程名称:单片机应用设计实践 设计题目:带温度显示的数字万年历设计 院(部):计算机与信息工程学院 学生姓名:******* 学号:************ 专业班级:************ 指导教师:******* 贵州 贵阳 年月日

课程设计任务书 设计题目万年历 学生姓名**** 所在院系***** 专业、年级、班*********** 设计要求: 1、设计制作一个用LCD1602显示的带温度显示的万年历; 2、具有年、月、日、星期、时、分、秒、温度等显示功能; 3、具备年、月、日、星期、时、分、秒校准功能; 4、具有闹钟显示、调节设定、整点鸣叫功能。 学生应完成的工作:设计万年历的工作原理,利用DXP 软件绘制电路原理图,利用Keil uVision4软件编写C语言程序并且生成HEX文件。并设计制作电路的PCB板(或万用板的元件布局和连线)。根据设计原理对电路进行安装、调试,完成课程设计工作,并提交课程设计报告。 参考文献阅读: 51单片机原理与应用案例教程(C51编程)p170的 9.1.2 LCD1602液晶应用实例 工作计划:*月*号:搜集资料;*月*号:方案论证拟定硬件方案;*月*号:讨论优化并确定硬件方案;*月*号—*号:讨论并确定程序流程并绘制流程图;*月*号:根据流程图编写程序并且进行软件的仿真与调试;*月*号—*号:硬件电路的制作并撰写课程设计报告;*月*号:烧录程序并调试;*月*号:完成课程设计报告的撰写。 任务下达日期:2017年11月30 日 任务完成日期:2017年11月01 日 指导教师(签名):学生(签名):田应焕

32位MIPS处理器设计实验报告

数字逻辑与处理器基础实验 32位MIPS处理器设计实验报告 王晗 (2013011076) July26,2015 Date Performed:July15,2015 Partners:耿天毅(2012011119) 陈志杰withdrawn 1实验目的 熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。 2设计方案 2.1总体结构 由于这次实验涉及的功能较多,我们将完整的CPU分成多个模块。指令存储器、寄存器堆、控制器、ALU控制器、ALU、数据存储器、UART等功能单元均在单独的Module中实现。其中指令存储器、寄存器堆、控制器、ALU控制器、ALU等单元在Single Cycle Core中实例化,作为单周期处理器的核心;数据存储器、UART和定时器、LED、七段数码管、开关在Peripheral中实现,作为处理器的外设。处理器核心和外设在顶层模块中实例化,互相通信。 单周期CPU模块的结构关系如Figure1所示:

Figure1:单周期处理器结构 对于流水线CPU,我们还在Pipeline Core中加入了流水线寄存器、冒险检测单元、数据转发单元: Figure2:流水线处理器结构

2.2ALU1 ALU模块的结构如图所示,输入两个操作数A、B和控制信号ALUFun、Signed,在ARITH子模块中做加减法运算,CMP子模块根据ARITH模块的输出进行比较判断,LOGIC和SHIFT模块分别进行逻辑运算和移位运算,ALUFun的最高两位用于控制多路选择器的输出。 Figure3:ALU结构 ARITH模块ARITH模块中包括减法和加法两个模块,加法模块直接通过+号运算,减法模块先对第二个操作数取补码,再调用加法模块做加法运算。Overflow和Negative信号的产生是ALU中的难点: Figure4:ADD中的Overflow和Negative 1原作者:陈志杰;修改:王晗

CPU设计实验报告

实验中央处理器的设计与实现 一、实验目的 1、 理解中央处理器的原理图设计方法。 2、 能够设计实现典型MIPS 的11条指令。 二、 实验要求 1、 使用Logisim 完成数据通路、控制器的设计与实现。 2、 完成整个处理器的集成与验证。 3、 撰写实验报告,并提交电路源文件。 三、 实验环境 VMware Workstatio ns Pro + Win dows XP + Logisim-wi n-2.7.1 四、 操作方法与实验步骤 1、数据通路的设计与实现 数据通路主要由NPC 、指令存储器、32位寄存器文件、立即数扩展部件、 ALU 、数据存储器构成。其中指令存储器和数据存储器可直接调用软件库中的 ROM 和RAM 元件直接完成,其余部件的设计如图所示: Cue ------- 吊孙 ----------- n -ar ch Zan [p]~ 图 1.1 NPC G —-- DO jlf* 04 4 D 04 nero & res?l ■&

幣> >曰CXI e Q

图1.3立即数扩展部件 图 1.4 ALU 2、控制器的设计与实现 控制器的主要设计思想如图所示 图2.1控制器设计思想 通过列真值表得到控制器的两部分电路,真值表如下 : 输入 000000 001101 100011 101011 000100 000010 immIC £it£ DOO -DO ooo n Q □□□non UOnflO OOC ?>:>0 DQ 000 指令 lnst :ruction[31:O] OP[5:OJ fu net [5:0] Jump ExBp Branch Mem Write ALUctr * RegWrite MemtoReg * ALUSrc 控制器 控制信号 LLLLLLLLLmM f ZERO A ()-- irnmmmiiiimiiiiifeiiim IIII93 1-] * 11114444 ".'O

32位MIPS处理器说明

32位MIPS处理器说明

一、实验目的 熟悉现代处理器的基本工作原理;掌握单周期和流水线处理器的设计方法。 二、实验原理及实验内容 该32位MIPS处理器主要需要设计ALU、单周期、流水线。下面分别讲述这三个部分的设计原理及实验内容。 1.ALU ALU即算数逻辑单元,要求设计一个32位的ALU,实现基本的算术、逻辑、关系、位与移位运算。输入32bit的A和B作为操作数,5bit的控制输入ALUFun和一位控制输入Sign,输出32bit的结果Z。其功能表如下图所示:

根据功能表和要求,我们在顶层模块中设计了32bit输入ALUSrc1和ALUSrc2,以及5bit控制ALUFunc,1bit控制Sign,32bit输出ALUOut。设计了四个主要模块:ALU_ADD_SUB,ALU_CMP,ALU_Logic,ALU_Shift,并根据ALUFunc的值来确定使用的模块。设计框图思路如下: (1)ALU_ADD_SUB 这部分是ALU设计中最重要的一部分。采用了8位超前进位级联,用与门来实现32位全加器。减法由加法实现,在运算的开始由ALUFunc判断进行的是加法还是减法,如果是加法则直接将两个操作数输入全加器,最低进位为0,如果是减法则取ALUSrc2的反码之后再做加法运算,最低进位是1。 需要注意的是运算结束之后需要判断结果是否为0(这个在branch指令中尤为重要),是否为负数,还有是否溢出。是否为溢出还需要检查控制符号,如果控制符号为有效(即有符号计算)则两正数相加得负或两负数相加得正则溢出,溢出则结果符号位反了,再进而判断是否为负。若为无符号运算,加法结

32位RISC处理器软核的设计与验证

32位RISC 处理器软核的设计与验证( Potato-I) 使用说明文档 1 CPU 流水线级数及各级功能 IF :取指令级,是从ROM 中读取指令,并在下一个时钟沿到来时把指令送到ID 级的指令缓冲器中。 ID :指令译码级,对IF 级来的指令进行译码,并产生相应的控制信号。整个CPU 的控制信号都是在这级上产生。 EX :执行级,对操作数进行算术或逻辑操作,此外LOAD ,STORE 指令所用的RAM 访问地址也是在EX 级上实现。 MEM :存储器访问级,只有在执行LOAD 、STORE 指令时对存储器进行读写,但对其他指令只起到缓冲一个周期的作用。 WB :回写级,把指令执行的结果回写到寄存器文件中,写入寄存器文件的数据来自于MEM 级上的缓冲值或来自于MEM 级上的存储器。 2指令集及编码格式 2.1指令集: NOP,ADD,ADC,SUB,SUBC,AND,OR,NOT,ADDI,ANDI,ORI,NOTI,LSL,LSR,ASR,ROR,ROL,STR,LDR,BTC,JUMP,JUMPR,JUMPL,RET 。 2.2指令编码格式 例:ADD R1,R2,R3; 在上面的加法指令中 OP=2、DS=1、S1=2 、S2=3,对应的机器码为: 32’b000010_00001_00010_00011_XXXXXXXXXXX; 2) ADDI,ANDI,ORI,NOTI 例:ADDI R4,R8,5; 其中 OP=1、DS=4、S1=8、IMM=5,对应的机器码为: 32’b000001_00100_01000_0000000000000101; 3) LSL,LSR,ASR,ROR,ROL

CPU设计实验报告

武汉大学计算机学院计算机科学与技术专业 CPU设计实验报告 实验名称:开放式实验CPU设计课题名称: 计算机组成原理 班级: 计科2班 指导教师:徐爱萍 组长: 组员: 二零一五年三月

目录 目录 (2) 1 实验环境(张航宇) (4) 1.1 Quartus Ⅱ介绍 (4) 1.2 硬件描述语言(VHDL) (4) 1.3实验的主要成果 (4) 2 实验要求(彭阳坤) (5) 2. 1 指令格式要求 (5) 2. 2 指令流程及微信号序列分析 (5) 2.2.1 ADD指令分析 (5) 2.2.2 ADC指令分析 (5) 2.2.3 SUB指令分析 (6) 2.2.4 SBC指令分析 (6) 2.2.5 INC指令分析 (6) 2.2.6 DEC指令分析 (6) 2.2.7 SHL指令分析 (7) 2.2.8 SHR指令分析 (7) 2.2.9 MOVR指令分析 (7) 2.2.11 MOVD指令分析 (7) 2.2.12 LDRR指令分析 (8) 2.2.13 STRR指令分析 (8) 2.2.14 JMP指令分析 (8) 2.2.15 JRZ指令分析 (8) 2.2.16 JRC指令分析 (9) 3.部件仿真实验(彭阳坤) (10) 3.1 八个通用寄存器设计与仿真 (10) 3.1.1 设计代码 (10) 3.1.2 RTL连接图 (16) 3.1.3 仿真过程 (16) 3.2算术逻辑单元设计与仿真 (17) 3.2.1 设计代码 (17)

3.2.2 RTL连接图 (22) 3.2.3 仿真过程 (23) 4. CPU设计(彭阳坤) (24) 4.1取指设计 (24) 4.2 时序节拍设计 (25) 4.3指令译码的设计 (26) 4.4执行部分设计 (29) 4.5存储器部分设计 (31) 4.6通用寄存器组设计 (32) 4.7寄存器输出设计 (38) 4.8顶层实体设计 (38) 5. 测试报告(张航宇) (42) 5.1规则文件 (42) 5.2测试文件 (42) 5.3指令测试 (44) 6 实验总结 (46) 6.1 彭阳坤的小结 (46) 6.1.1 实验收获 (46) 6.1.2 建议与意见 (46) 6.2张航宇的小结 (46) 6.2.1 实验收获 (46) 6.2.2 建议与意见 (47) 参考资料 (47)

32位cpu设计报告

CPU 设 计 报 告 姓名: 学号: 学院:信息科学与工程学院指导老师:

2013-01-12 一、设计目的 (1)学习设计CPU的基本步骤和方法,提高应用集成电路的基本技能,培养和提高独立设计计算机的工作能力。 (2)熟悉32位CPU各模块的工作原理,熟悉流水线数据通路和控制单元的工作原理从而熟悉CPU的工作机理。 (3)熟练地使用Quartus软件,做一些中等难度的课题,增加自己的一些实践经验,熟练VHDL编程。 (4)强化自身的系统设计能力,了解系统设计中的一般步骤。了解VHDL仿真和综合工具的潜力。 二、实验方法 实验要完成的工作主要包括:指令系统的设计,FPGA-CPU的整体结构设计及其细化,逻辑设计的具体实现(VHDL语言编写),软件模拟,以及硬件调试。这几部分的工作之间是先行后续的关系,也就是只有前一个步骤完成了下一个步骤才可以开始进行,不存在并行完成的情况。实验主要流程如下图所示: 指令系统设计逻辑设计 具体实现 软件模拟 硬件调试 设计FPGA-CPU的指令集。我们采用了流水线数据通路与控制单元的精简指令集计算机 分析并确定CPU主要功能模块,分析每条指令的执行过程,数据的流向和控制信号的产生,画出逻辑结构图 按模块分别实现,然后进行综合,建波形文件进行仿真 整体模拟仿真,检查时序关系配 合是否正确 下载到实验板中进行调试

三、数据格式 数据字长是32位,采用32位二进制有符号补码表示。 四、寻址方式 RSCI的四种寻址模式分别是寄存器寻址,存器间接寻址,立即寻址,相对寻址。这些寻址模式都是由操作码而不是单独的模式字段指定的。因此,对于某种给定操作来说,它的寻址模式是固定的,不能变动。三操作数数据处理指令采用寄存器寻址模式。寄存器间接寻址仅仅用于load和store这两个唯一能够访问数据存储器的指令。采用两寄存器格式的指令使用一个立即数取代寄存器地址SB。相对寻址专门用于分支和跳转指令,其产生的地址只用于指令存储器。 五、数据通路结构 下图中的流水线数据通路是我们即将设计的数据通路的基础,我们只需要做一些改进。这些改进涉及寄存器文件、功能单元和总线结构。

cpu设计报告

基于VHDL的8位CPU设计 设计要求 按给定的数据格式和指令系统,运用“数字系统设计”课学得的知识,用vhdl或verilog 语言设计一个8位的具有复杂指令的CPU系统。 指令系统 寻址方式: 1.立即数寻址 操作码r1 数据 2.立即地址寻址 操作码 地址 3.寄存器直接寻址 操作码r1 r2 r1和r2的状态为00时,为A寄存器;为01时,为B寄存器;为10时,为C寄存器。 4.寄存器间接寻址 操作码r1/11 r2/11 当r1或r2中有一处为“11”状态时,就表示这个操作数的地址在C寄存器中。 指令系统: 该机给定的指令系统共有28条指令,各条指令的编码可以是多种多样的。因此还可以扩展该指令系统。 指令的汇编符号指令的二进制编码第二字节 1.MOV r1 r2 0 0 1 1 r1 r2 2.MOV M r2 0 0 1 1 1 1 r2 3.MOV r1 M 0 0 1 1 r1 1 1 4.MVI r1 data 1 0 1 1 r1 0 0 data 5.MVI M data 1 0 1 1 1 1 0 0 data 6.STR address r2 1 1 0 0 0 0 r2 address 7.LDR r1 address 1 1 0 1 r1 0 0 address 8.ADD r1 r2 1 0 0 1 r1 r2 9.ADD r1 M 1 0 0 1 r1 1 1 10.SUB r1 r2 0 1 1 0 r1 r2 11.SUB r1 M 0 1 1 0 r1 1 1

12.INR r1 1 1 1 1 r1 XX 13.INR M 1 1 1 1 1 1 XX 14.DCR r1 0 0 0 0 r1 XX 15.DCR r1 0 0 0 0 1 1 XX 16.AND r1 r2 1 1 1 0 r1 r2 17.AND r1 M 1 1 1 0 r1 1 1 https://www.360docs.net/doc/1a4102777.html, r1 0 1 0 1 r1 XX 19.SHR r1 1 0 1 0 r1 0 0 20.SHL r1 1 0 1 0 r1 1 1 21.JMP address 0 0 0 1 0 0 0 0 address 22.JZ address 0 1 1 0 1 1 0 0 address 23.JCN address 0 0 0 1 1 0 0 0 address 24.JCZ address 0 0 0 1 1 1 1 1 address 25.IN r1 0 0 1 0 r1 XX 26.OUT r1 0 1 0 0 r1 XX 27.NOP 0 1 1 1 0 0 0 0 28.HALT 1 0 0 0 0 0 0 0 数据通路 计算机的工作过程,可以看成有许多不同的数据流和信号流在机器各部分之间进行传送,数据流所经过的路程就称作数据通路。数据通路不同,指令执行所经过的操作过程也不同,机器的结构也就不一样。本设计的要求的数据和指令都是8位的,所以同时采用并行工作方式和单总线结构。 1.算术运算类指令对数据通路的要求 完成加法指令:(r1)+(r2)=>r1 完成这个指令的基本操作为: 1)在某个控制信号的控制下,从r1指定的寄存器中取出第一操作数,送入A暂存器暂存起来。 2)在另一个控制信号的控制下,从r2指定的寄存器中取出第二操作数,送入B暂存器暂存起来。 3)对算术逻辑运算部件发出的相应的选择信号,使其完成操作码所要求的操作,对两个暂存器内的数进行运算,运算的结果定义在某一个信号控制下送回r1所指定的寄存器。 2.传送类指令对数据通路的要求 完成的指令为(r2)=>r1 1)在RE的控制下,由r2所给定的编码选择RA0,RA1从寄存器组中读出r2的内

精简8位cpu设计报告

精简8位cpu实验设计报告实验介绍: 实验分为两个部分,第一部分为16*8 ROM 设计与仿真第二部分为SAP-1设计与仿真 实验流程: ①16*8ROM得设计与仿真 部分程序代码: Rom16_8、VHDL LIBRARYIEEE; USE IEEE、STD_LOGIC_1164。ALL; USE IEEE.STD_LOGIC_ARITH。ALL; USEIEEE.STD_LOGIC_UNSIGNED。ALL;

ENTITYROM16_8 is PORT( DATAOUT :OUT STD_LOGIC_VECTOR(7DOWNTO 0); --Data Output ADDR :INSTD_LOGIC_VECTOR(3 DOWNTO0);——ADDRESS CE :IN STD_LOGIC ——Chip Enable ); ENDROM16_8; ARCHITECTURE aOFROM 16_8IS BEGIN DATA〈=“”WHEN ADDR=“0000”ANDCE=‘0’-—L DA 9H “”WHEN ADDR=“0001"AND CE=‘0’ELSE —-ADD AH “"WHENADDR=“0010”AND CE=‘0’ELSE--ADDBH “"WHEN ADDR=“0011"AND CE=‘0’ELSE —-SUB C H “”WHEN ADDR=“0100”ANDCE=‘0'ELSE --OUT “”WHEN ADDR=“0101”AND CE=‘0’ELSE —-HLT “”WHEN ADDR=“1001"ANDCE=‘0’ELSE “"WHEN ADDR=“1010"AND CE=‘0'ELSE “”WHEN ADDR=“1011"ANDCE=‘0’ELSE “"WHEN ADDR=“1100”AND CE=‘0’ELSE “”;

32位嵌入式微处理器一览

作者:杨硕 由于嵌入式系统的专用型与定制性,与全球PC市场不同,没有一种微处理器或者微处理器公司可以主导嵌入式系统。本文分析了当前市场上主流的一些32位嵌入式微处理器的特点和应用场合,并对其未来发展做一些展望。这里只是按照体系结构分类,不涉及具体的处理器芯片。 一. ARM ARM处理器是由英国的ARM公司设计的32位RISC处理器。 毫无疑问,ARM芯片是嵌入式微处理器中的佼佼者,是很多数字电子产品的核心。如今95%的手机里面的核心处理器使用的都是ARM芯片,而ARM在整个手持市场上占有90%以上的份额,这是一个惊人的比例。 ARM公司的商业模式: ARM公司的成功除了其卓越的芯片设计技术以外,还源于其创新的商业模式:提供技术许可的知识产权,而不是制造和销售实际的半导体芯片。ARM将其芯片设计技术(内核、体系扩展、微处理器和系统芯片方案)授权给Intel,Samsung,TI,高通(Qualcomm),意法半导体等半导体制造商,这些厂商拿到ARM内核以后,再设计外围的各种控制器,和ARM核整合成一块SOC芯片,也就是我们看到的市面上的各种芯片,作为用户,我们也许不知道我们使用的是ARM芯片,但是我们可能天天都在感受着ARM芯片带给我们的智能体验。 图1-1 ARM的业务模型

ARM公司正是因为没有自己生产芯片,从而省去了IC制造的巨额成本,因此可 以专注于处理器内核设计本身,ARM处理器内核不但性能卓越而且升级速度很快,以适应市场的变化。 由于所有的ARM芯片都采用一个通用的处理器架构,所以相同的软件可以在所有产品中运行,这正是ARM最大的优势,采用ARM芯片无疑可以有效缩短应用程序开发的与测试的时间,也降低了研发费用。 ARM生态产业链: ARM公司通过出售芯片技术授权,建立起新型的微处理器设计、生产和销售商业模式。围绕着芯片设计产业,ARM公司整合了上下游的资源,逐渐形成了一条完整的生态产业链。ARM的合作伙伴包括半导体制造商,开发工具商,应用软件设计商以及培训商等。ARM公司统一了芯片设计的标准,芯片制造商生产的芯片符合统一的接口,为以后的开发提供了很大的方便;工具商专门开发基于ARM芯片的仿真器和开发工具;应用软件设计商开发基于ARM芯片的应用程序,培训商则提供与ARM相关的培训服务。 这样的一套完整的产业链使得ARM芯片的开放性和通用性都很好,很多公司开发嵌入式产品都倾向于选择ARM的芯片,因为软硬件开发都有比较成熟的方案,相关的人才也比较多,可以缩短开发的周期,使得产品能够尽快上市。而作为个人如果想学习嵌入式开发,ARM芯片也是首选的学习对象,相关的学习资料和开发工具都有很多。 目前全球已有超过700家的软硬件系统公司加入了ARM Connected Community,其中中国本土公司的成长很快,目前已经有超过70家加入了ARM生态伙伴系统。 下图为以ARM公司为核心的生态产业链,这个产业链还在不断壮大: 图1-2 以ARM为核心的生态系统

位CPU设计与实现

位C P U设计与实现文档编制序号:[KK8UY-LL9IO69-TTO6M3-MTOL89-FTT688]

计 算 机 组 成 原 理 论 文 姓名:某某 班级:计科一班 学号: 8位CPU的设计与实现论文 CPU 的主要功能是执行指令,控制完成计算机的各项操作,包括运算操作、传送操作、输入/输出操作等。作为模型计算机设计,将重点放在寄存器组,采取较简单的组成模式,以尽量简洁的设计帮助读者掌握CPU 的基本原理。 此次设计CPU就是为了了解CPU运行的原理,从而完成从指令系统到CPU 的设计,并且通过仿真对CPU设计进行正确性评定。 关键词:CPU,设计指标,电路原理图,运算部件,寄存器组,模型 机指令系统,微命令序列,数据通路

1. 设计的任务与要求 1.1设计指标 1. 能实现IN(输入)、ADD(二进制加法)、STA(存数)、OUT(输出)、 JMP(无条件转移)这五种指令; 2. 整个系统能正常稳定工作。 1.2 设计要求 1. 画出电路原理图; 2.写出设计的全过程,附上有关资料和图纸(也可直接写在相关章节中), 有心得体会。 2. 方案论证与选择 2.1 CPU的系统方案 CPU 主要由算术逻辑单元ALU,数据暂存寄存器DR1、DR2,数据寄存器 R0~R2,程序计数器PC,地址寄存器AR,程序/数据存储器MEMORAY,指令寄存器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所组成。图中虚线框内部分包括运算器、控制器、程序存储器、数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现。虚线框外部分主要是输入/输出装置,包括键盘、数码管、LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及观察CPU 内部工作情况及运算结果。 1.运算部件 运算部件的任务是对操作数进行加工处理。主要由三部分组成:

32位操作系统

操作系统是硬件和应用软件中间的一个平台。 32位操作系统针对32位的CPU设计。 64位操作系统针对64位的CPU设计。 CPU从原来的8位,16位,到现在的32位和64位。 cpu处理计算的时候“数据”和“指令”是不同对待的。 8位CPU 8位的CPU,一次只能处理一个8位的“数据”或者一个8位的"指令"。比如'00001101'. 又比如:“+1”这个运算,你要先指示CPU做“+”,完成后再输 入“1”数据给CPU。 8位的CPU优点是设计简单,处理速度比较快。 缺点就是:软件设计复杂,繁琐。不利于计算机的发展。 16位CPU 后来推出了16位的CPU,我们就可以一次处理两个字节(16位)的数据了,比如“加1”这个命令。“加”是一个指令,占用8个位,余下的8位我们可以存放数据“1”了。 32位CPU 32位的CPU就更加方便了,我们就可以一次处理一个a=a+b这样的命令了。 优点:简化了软件设计的复杂度 缺点:硬件设计更加复杂,计算速度下降。 一般来讲32位的CPU对于我们来讲是最理性的CPU,对于软件开发来讲足够了。 但是2的32次方 = 4294967296bit = 4G左右

很显然32位CPU只有4G左右的内存寻址空间,对于一些服务器来讲4G的内存的远远不够的了。我们需要更加大的内存寻址空间的话就需要对CPU进升级。64位CPU就这样诞生了。64位CPU的内存寻址空间是多少你算算看!呵呵。 2的64次方(理论上)。 64位CPU 但是现在的AMD和Inter的64位CPU并不是真正意义上的64CPU,只是进行了部分64位的改进,比如64位的内存寻址等。 要是真的全部都是64位的了,那么现在市场上的软件将全部被淘汰不能使用了~呵呵,想像一下会是什么样子。 64位的操作系统针对64位CPU设计的,增加了一些64位的指令,但还是和32兼容的。对于我们普通用户来讲64位系统意义不大。

32位CPU定时器0中断实验及AD_DA实验报告

实验报告 课程名称: 微机原理与运用 指导老师:_ _成绩:实验名称: 32位CPU 定时器0中断实验 实验类型:_____ 同组学生姓名: 一、实验目的和要求(必填) 二、实验内容和原理(必填) 三、主要仪器设备(必填) 四、操作方法和实验步骤 五、实验数据记录和处理 六、实验结果与分析(必填) 七、讨论、心得 一、 实验目的和要求(必填) 1. 通过实验熟悉TMS320F2812的定时器 2. 掌握TMS320F2812定时器的控制方法 3. 掌握F2812的中断结构和对中断的处理流程 4. 掌握C 预言中中断程序设计以及运用中断程序控制程序流程 5. 要求1: 完成基本的定时闪灯功能,同时运行跑马灯 6. 要求2Timer :显示格式000000.00 : 秒表 7. 要求3Clock :显示格式小时-分钟-秒数: 时钟 8. 要求4: 按键 功能设计 8/C 小时:增加/减小 9/D 分钟:增加/减小 A/E 切换:时钟/秒表 B/F 秒表时的启动/停止 9. 设计更好的按键程序,模仿计算机上的按键:首次按键立刻响应,延时后自动重复 二、 实验内容和原理(必填) TMS320F2812内部有三个32位CPU 定时器(TIMER0/1/2)。其中保留CPU 定时器1和定时器2用于DSP BIOS 及实时操作系统(RTOS )。 三、 主要仪器设备(必填) 电脑一台、TMS320F2812芯片 四、 实验仿真及实验数据记录 加入跑马灯程序后,可以看到跑马灯跑出的效果

具体实验要求的实现还见实验程序包。 五、问题与讨论 使用定时器和中断服务程序可以运行到日常生活中哪些情况? 答:可以用在电子表、电子式定时器插座、秒表、训练定时器、生产线控制系、交通灯等。

8位CPU设计报告

8位CPU设计报告 8位CPU的系统设计 1. 设计的任务与要求 CPU 的主要功能是执行指令,控制完成计算机的各项操作,包括运算操作、传送操作、输入/输出操作等。作为模型计算机设计,将重点放在寄存器级,采取较简单的组成模式,以尽量简洁的设计帮助读者掌握CPU 的基本原理。此次设计CPU就是为了了解CPU运行的原理,从而完成从指令系统到CPU的设计,并且通过仿真对CPU设计进行正确性评定。 1.1设计指标 1. 能实现IN(输入)、ADD(二进制加法)、STA(存数)、OUT(输出)、JMP (无条件转移)这五种指令; 2. 整个系统能正常稳定工作。 1.2 设计要求 1. 画出电路原理图、仿真波形图; 2. 编写设计报告,写出设计的全过程,附上有关资料和图纸(也可直接写在 相关章节中),有心得体会。 2. 方案论证与选择 2.1 CPU的系统方案

- 1 - CPU 主要由算术逻辑单元ALU,数据暂存寄存器DR1、DR2,数据寄存器 R0,R2,程序计数器PC,地址寄存器AR,程序/数据存储器MEMORAY,指令寄存器IR,微控制器uC,输入单元INPUT 和输出单元OUTPUT 所组成。图中虚线框内部分包括运算器、控制器、程序存储器、数据存储器和微程序存储器等,实测时,它们都可以在单片FPGA 中实现。虚线框外部分主要是输入/输出装置,包括键盘、数码管、LCD 显示器等,用于向CPU 输入数据,或CPU 向外输出数据,以及观察CPU 内部工作情况及运算结果。 1(运算部件 运算部件的任务是对操作数进行加工处理。主要由三部分组成:(1)输入逻辑。 (2)算术/逻辑运算部件ALU。(3)输出逻辑 2(寄存器组 计算机工作时,CPU 需要处理大量的控制信息和数据信息。例如对指令信息进行译码,以便产生相应控制命令对操作数进行算术或逻辑运算加工,并且根据运算结果决定后续操作等。因此,在CPU 中需要设置若干寄存器,暂时存放这些信息。在模型CPU中,寄存器组由R0、R1、R2 所组成。

cpu设计实验报告

一、实验内容 设计一个八位定点二进制计算机,具有4个通用寄存器:R0~R3,能执行11条指令,主存容量为256B的cpu模型机。 二、实验过程 1.指令集设计 LDR Ri,D 格式7 4 3 2 1 0 功能: Ri←M(D) STR Ri,D 格式7 4 3 2 1 0 功能: M(D)←(Ri) ADD Ri,Rj 格式7 4 3 2 1 0 功能: Ri ←(Ri)+(Rj) SUB Ri,Rj 格式7 4 3 2 1 0 功能: Ri ←(Ri)-(Rj) AND Ri,Rj 格式7 . . . 3 2 1 0 功能: Ri ←(Ri)∧(Rj) OR Ri,Rj 格式7. . . 3 2 1 0 功能: Ri ←(Ri)∨(Rj)

MUL Ri ,Rj 格式 7 4 3 2 1 0 功能: Ri ←(Ri )× (Rj ) 转移指令 格式 7 4 3 2 1 0 功能: 条件码 00 无条件转移 PC ← D 01 有进位转移 PC ← D 10 结果为0转移 PC ← D 11 结果为负转移 PC ← D IN R i ,M j 格式 7 4 3 2 1 0 其中M j 为设备地址,可以指定四种外围设备,当M j =01时,选中实验箱的二进制代码开关。功能: R i ← (M j ) OUT R i ,M j 格式 7 4 3 2 1 0 当M j =10时,选中实验箱的显示灯。功能: (M j )← R i HALT (停机指令) 格式 7 4 3 2 1 0 功能: 用于实现停机。 其中,Ri ,Rj ,均用00表示R1,01表示R2,10表示R3,11表示R4。 2.状态图 00000

ASIC实验报告(8位CPU的设计)

ASIC设计实验报告 学院:电子工程学院 学号:2014******* 姓名:王闯 指导老师:刘雯 2014年11月13日

一、实验目的: 通过对ASIC实验课的学习,应当学会以下几点: 1.熟悉Linux操作系统的应用环境,基本命令行的应用,以及对vi编辑器熟练应用。 2.熟练掌握Verilog编程语言,包括基本组合逻辑电路的实现方法,基本时序逻辑电路的实现方法,怎样使用预定义的库文件,利用always块实现组合逻辑电路的方法已经着重了解assign与always 两种组合逻辑电路实现方法之间的区别,深入了解阻塞赋值与非阻塞赋值的概念以及应用的差别,有限状态机(FSM)实现复杂时序逻辑的方法,以及学会在Linux 系统环境当中应用Synopsys工具VCS进行仿真。 3.熟悉电路设计当中的层次化、结构化的设计方法。 4.熟悉CPU当中有哪些模块组成,模块之间的关系,以及其基本的工作原理。 5.学会利用汇编语言设计程序,注意代码规范性要求。 二、实验要求: 按照实验指导书上的要求即:CPU各个模块的Verilog语言代码的编写、编译及仿真正确,并在规定的时间内完成。要求对CPU进行语言级系统仿真结果正确之后,利用该实验当中采用的八个汇编关键字,编写一个能够实现某种功能的小程序。然后对其中的控制器电路进行综合,并检查Timing 和Power,进行门级仿真。 三、实验内容:

设计一个8位RISC_CPU 系统。(RISC: Reduced Instruction Set Computer),它是一种八十年代才出现的CPU,与一般的CPU相比,不仅只是简化了指令系统,而且通过简化指令系统使计算机的结构更加简单合理,从而提高了运算速度。从实现的方法上,它的时序控制信号部件使用了硬布线逻辑,而不是采用微程序控制方式,故产生控制序列的速度要快的多,因为省去了读取微指令的时间。此CPU所具有的功能有: (1)取指令:当程序已在存储器中时,首先根据程序入口地址取出一条程序,为此要发出指令地址及控制信号。 (2)分析指令:即指令译码。是对当前取得的指令进行分析,指出它要求什么操作,并产生相应的操作控制命令。 (3)执行指令:根据分析指令时产生的“操作命令”形成相应的操作控制信号序列,通过运算器,存储器及输入/输出设备的执行,实现每条指令的功能,其中包括对运算结果的处理以及下条指令地址的形成。 从上述具有的功能可以总结出,它有八个独立的逻辑部件所组成:时钟发生器、指令寄存器、累加器、ALU、数据控制器、状态控制器、程序计数器以及地址选择器。在本实验报告当中会一一对各个模块设计进行介绍。 四、实验设计过程: (一).多路选择器的设计(MUX) 在该模块设计当中,练习的是组合逻辑电路的设计方法,其