题514已知维持阻塞结构d触发器各输入端的电压波形

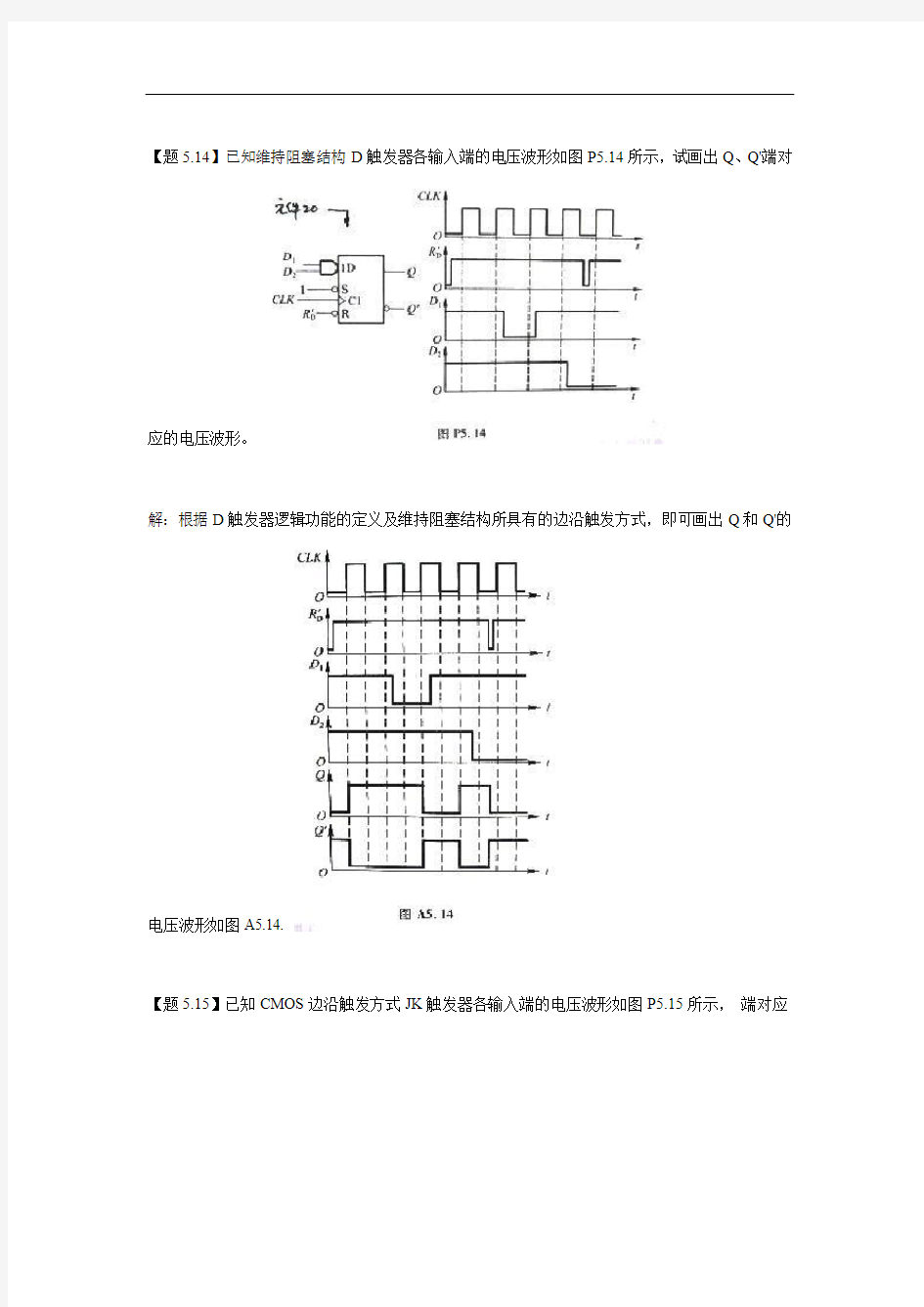

【题5.14】已知维持阻塞结构D触发器各输入端的电压波形如图P5.14所示,试画出Q、Q'端对

应的电压波形。

解:根据D触发器逻辑功能的定义及维持阻塞结构所具有的边沿触发方式,即可画出Q和Q'的

电压波形如图A5.14.

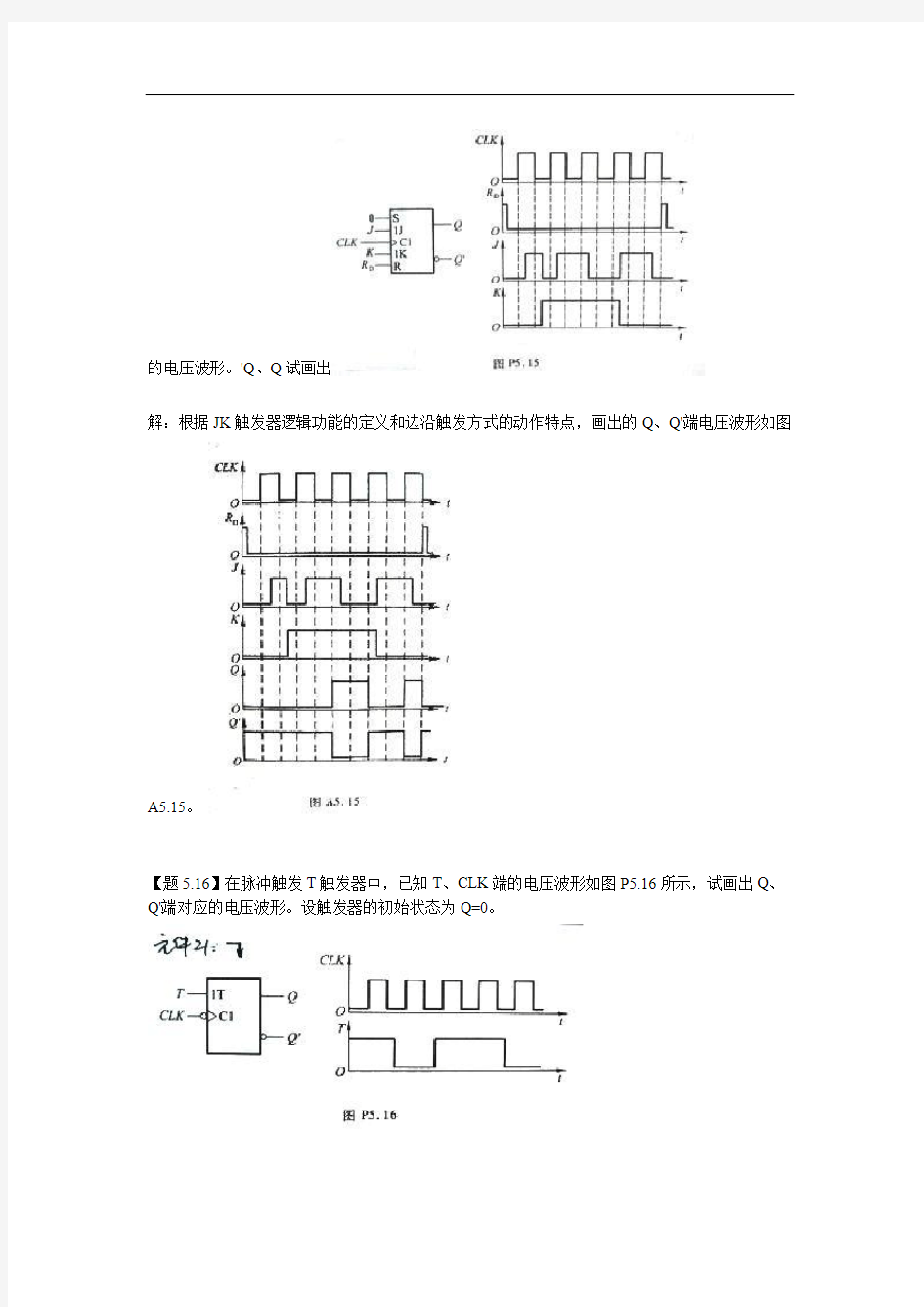

【题5.15】已知CMOS边沿触发方式JK触发器各输入端的电压波形如图P5.15所示,端对应

的电压波形。'Q、Q试画出

解:根据JK触发器逻辑功能的定义和边沿触发方式的动作特点,画出的Q、Q'端电压波形如图

A5.15。

【题5.16】在脉冲触发T触发器中,已知T、CLK端的电压波形如图P5.16所示,试画出Q、Q'端对应的电压波形。设触发器的初始状态为Q=0。

解:根据T触发器逻辑功能的定义以及脉冲触发方式的动作特点,画出的Q、Q'端电。A5.16.

压波形如图

【题5.17】在图P5.17的主从结构JK触发器电路中,已知CLK和输入信号T的电压波形如图所示,试画出触发器输出端Q和Q'的电压波形。设触发器的起始状态为Q=0。

解:将JK触发器的J和K接在一起作为输入端,就得到了T触发器。按照T触发器的逻辑功能和脉冲触发方式的动作特点,就到得到了图A5.17中Q、Q'端的电压波形。

【题5.18】设图P5.18各触发器的初始状态皆为Q=0,试画出在CLK信号连续作用下各触发器

输出端的电压波

形。.

。A5.18的电压波形,如图Q解:根据每个触发器的逻辑功能和触发方式,画出输出端

【题5.19】试写出图P5.19(a)中各电路的次态函数(即Q*、Q*、Q*、Q*与现态4231和输入变量之间的函数式),并画出在图P5.19(b)给定信号的作用下Q、Q、Q、Q的4132电压波形。假定各触发器的初始状态均为Q=0。

解:由图中可写出触发器FF的驱动方程为1J=A';K=B' 11将它们代入JK触发器的特性方程

Q*=JQ'+K'Q,得到

Q*=A'Q'+BQ111

触发器FF的驱动方程为2S=AB;R=(A+B)'22

将它们代入SR触发器的特性方程Q*=S+R'Q,得到

Q*=AB+(A+B)Q2

2触发器FF的驱动方程为T=A☉B,将它代入T触发器的特性方程Q*=TQ'+T'Q=T⊕Q,33于是得到

Q*=(A☉B)⊕Q3

3触发器FF的驱动方程为D=A⊕B,将它代入D触发器的特性方程Q*=D,得到44Q*=A⊕B 4从t=0开始依次根据每个触发器的状态方程求出它们在CLK信号作用后应有的次态,就可以画出Q、Q、Q、Q 所示。A5.19信号作用下的电压波形了,如图CLK在一系列

4321.

u的电压波形如图所示,试画出与之对应P5.20电路中已知输入信号5.20【题】在图I u的波形。触发器为维持阻塞结构,初始状态为。(提示:应考虑触发器Q=0的输出电压O和异或门的传输

延迟时间。)

uuuu也变成高电。Q=0、时,异或门的输出变为高电平以后,等于0解:当=0OIOI u也是触发

器的时钟输入端,所以经过触发器的延迟时间后,Q端被置成1状态;平。因为O uu高电平持续时间等于触发器的传再经过异或门的传输延迟时间,回到低电平。因此,OO输延迟时间与异或门的传输延迟时间之和。

u从高电平跳变至低电平以后电路的工作过程与上述过程类似。这样就得到了图I u的A5.20电

压波形。O.

【题5.21】在图P5.21所示的主从JK触发器电路中,CLK和A的电压波形如图中所示,试画出Q端对应的电压波形。设触发器的初始状态为Q=0。