数字电子钟设计说明..

数字电子钟课程设计

一、设计任务与要求

(1)设计一个能显示时、分、秒的数字电子钟,显示时间从00: 00: 00到23: 59: 59;

(2)设计的电路包括产生时钟信号,时、分、秒的计时电路和显示电路(3)电

路能实现校正

(5)整点报时

二、单元电路设计与参数计算

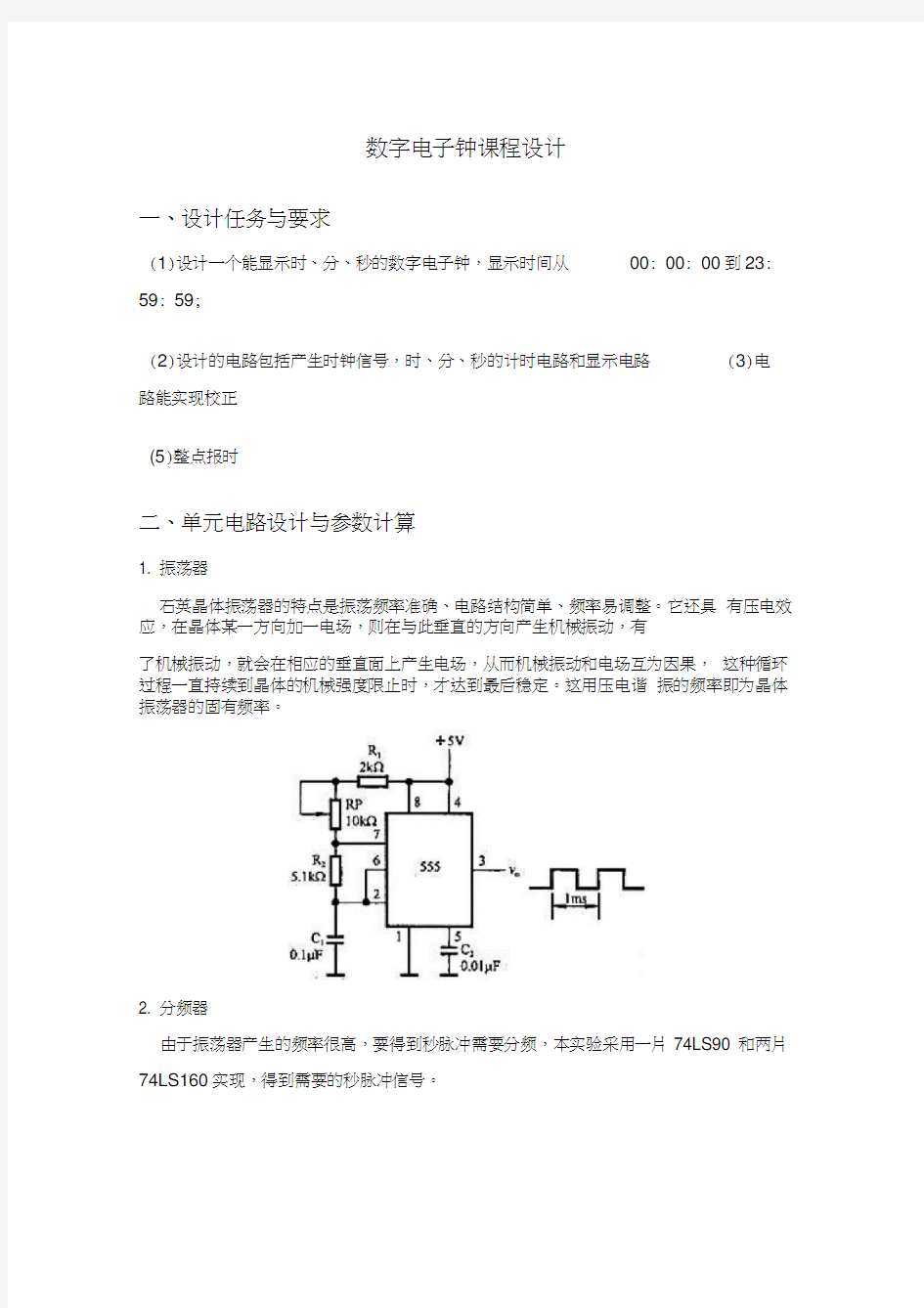

1. 振荡器

石英晶体振荡器的特点是振荡频率准确、电路结构简单、频率易调整。它还具有压电效应,在晶体某一方向加一电场,则在与此垂直的方向产生机械振动,有

了机械振动,就会在相应的垂直面上产生电场,从而机械振动和电场互为因果,这种循环过程一直持续到晶体的机械强度限止时,才达到最后稳定。这用压电谐振的频率即为晶体振荡器的固有频率。

2. 分频器

由于振荡器产生的频率很高,要得到秒脉冲需要分频,本实验采用一片74LS90 和两片74LS160实现,得到需要的秒脉冲信号。

3. 计数器

秒脉冲信号经过计数器,分别得到“秒”个位、十位、“分”个位、十位以及 “时”个位、十位的计时。“秒” “分”计数器为六十进制,小时为二十四进制。

(1)六十进制计数

由分频器来的秒脉冲信号,首先送到“秒”计数器进行累加计数,秒计数器应完 成一分钟之内秒数目的累加,并达到 60秒时产生一个进位信号。本作品选用一 片74LS161和一片74LS160采取同步置数的方式组成六十进制的计数器。

(2)二十四进制计数

“24翻1”小时计数器按照“ 00— 01—02,, 22—23— 00—01”规律计数。与生 活中计数规律相同。二十四进制计数同样选用74LS161和74LS160计数芯片。但 清零方式采用的是异步清零方式。

MMgM

加

EHagij

Z

1

进位信号

脉冲

4 ?译码器

译码是指把给定的代码进行翻译的过程。计数器采用的码制不同,译码电路也不同。

74LS48驱动器是与8421BCD编码计数器配合用的七段译码驱动器。74LS48配有灯测试LT、动态灭灯输入RBI,灭灯输入/动态灭灯输出BI/RBO,当LT=O时,

74LS48出去全1。

5 ?显示器

本系统用七段发光二极管来显示译码器输出的数字,显示器有两种:共阳极显示

器或共阴极显示器。74LS48译码器对应的显示器是共阴极显示器。

6. 校时电路

当数字钟走时出现误差时,需要校正时间。校时电路实现对“时”“分”“秒”的校准。在电路中设有正常计时和校对位置。本实验实现“时”“分”的校对。

对校时的要求是,在小时校正时不影响分和秒的正常计数;在分校正时不影响秒和小时的正常计数。需要注意的时,校时电路是由与非门构成的组合逻辑电路,开关S1或S2为“0”或“ T时,可能会产生抖动,为防止这一情况的发生我们接入一个由RS触发器组成的防抖动电路来控制。

8.整点报时电路

整点报时电路的功能要求是,每当数字钟计时快要到整点时发出声响,

通常按照

4低音1高音的顺序发出间断声响,以最后一声高音结束的时刻为整点时刻。

设

4声低音(约500HZ 分别发生在59分51秒、53秒、55秒及57秒,最后一声 高音(约1KH0发生在59分59秒,它们的持续时间均为1秒。因是额外附加电 路,所以不加入总图中

校时味冲

56 0 1 1 0 停 57 0 1 1 1 鸣低音 58 1 0 0 0 低 59 1 0 0 1 鸣高音 00

停

四、总原理图及元器件清单

1 ?总原理图

分个付

{:

Hlh SOUHz-

>

T

&-

u .l

>

LJ

3-D

ft

响

电

Hihn

n Qh_

Q 一 粉斗位{ 秒个荷

IkHz 秒个

位Q t

1元件清单

型号 数量 备注

74LS160

3 r

十进制计数器 74LS161 3 四二进制计数器 74LS48 6 译码器 74LS00 5 四二输入与非门 74LS04 1 六反相器 74LS20 1 四输入与非门

74LS90 1 r

二五十进制计数器

NE555 1

七段共阴数码管 6

7805芯片 1

红色发光LED 4 自锁开关 4

按键开关

4

电阻、电容、导线

若干

六、设计流程

1、 查找资料、通过对比确定电路模型及所选取的元件。

2、 进行Multisim 仿真,不断调试,查看仿真结果是否达到我们期望的效果

3、按照仿真电路,进行插线。首先连接信号发生器电路,进行调试,使其稳定 输出 1HZ

的脉冲信号。

Q

txti ; tisli

*羽昕

¥K?

4、连接“秒”电路部分,进行调试,使“秒”部分电路实现正常计数功能,再连接“分”电路,进行调试。

5、“秒”、“分”电路计时均正确后连接“时”部分电路,进行调试直至正确计数。

6、“秒”、“分”、“时”电路基本计数功能实现后,连接校时电路,进行调试,直至校时效果出现。

7、校时完成后,连接测试电路准确性。

8、所有部分都完成后,进行整个电路所有功能调试,出现故障一部分一部分的检查排除,直至最后效果出来为止。

七、故障分析及调试

1、在电路设计过程中存在元件使用的不当如输入端与输出端的链接失误。应多次进行仿真模拟推测失误的地方。

2、在仿真过程中由于软件应用的不熟练导致在实用软件的过程中连线不正确。器件找的不对,并且在模拟过程中易出错。比如本图中两个开关实在找不到直接进行的连线,应当反复检查是否出现错误,并通过不断地实验设计完善对软件的使用。

3、如果出现仿真错误时可能是因为在校时电路中连接的失误导致的。

八、精度分析

通过模拟仿真的得出的结论可以使得该电路实现数字电子钟的功能。但是存在一定的误差,应该是在555 定时器在发出信号时的误差。

九、收获体会

通过对数字时钟课程设计的设计和仿真,我觉得自己真的学到了很多。首先,我对数字时钟的结构及原理与了很好的了解,对时、分、秒的设计以及校时有了一定的了解;其次,我了解了不少器件功能的应用,能够较合理的选用集成电路器件,加深了对数字电路的认识和理解,将所学的理论知识与实际运用结合起来;再次,我学会了操作和使用仿真软件Multisim 以及其他版本的仿

真软件,如EWB?,能够较好地利用这些软件进行电路的仿真和调试。

更重要的是,这次课程设计的制作过程中,在不断地发现问题和调试并解决问题的过程中,我学会了在设计中独立地解决问题,也包括怎样去查找问题,同时我发现,只有不断的尝试,亲手去操作,我们才能真正发现学习的乐趣,得到我们想要的结果。

在整个设计阶段,调试过程我花的时间比较多,其间更换了不少器件。因为当我们利用Multisim 等软件对设计的电路进行计算机仿真时,软件有时会出问题,在理论上可行的电路在调试中未必能显示出来,所以我只能通过查阅相关资料,不断地尝试,更换器件,耐心、仔细地分析问题,直到得到最后正确的结果。

通过对本次课程设计的研究,将“模拟电子技术”、“数字电子技术”等课程的理论与实践有机的结合起来。每次课程设计是一次难得的锻炼机会,让我们能够充分利用所学过的理论知识还有自己的想象的能力,另外还让我们学习查找资料的方法,以及自己处理分析电路,设计电路的能力。我相信是对我的一个很好的提高。平时在学习理论知识的时候,我们应该更注重实践。这次的课程设计让我懂得了它们在实际中的用途,还有我们身边的很多数字钟电路,这些都是我们自己可以实现的,以前那些神秘的东西在不断的学习过程中变得不再那么神秘,我相信,以后还有更多的谜底被揭开。通过这次课程设计,我还更加深了理论知识的学习。

这次的设计电路我用到了计数器、译码器等,通过自己分析和设计更好地运用了它们,而且还学会了它们更多的功能,发现它们的功能远比书上说的多很多,可以利用不同的接法设计出各种各样不同的电路出来。我不仅更进一步的巩固了以往所学的知识,而且很好的了解和掌握了原来不知道或掌握不好的知识结构,特别是了解和掌握了很多时钟专用芯片的功能以及用法,这些芯片的功能和用法都是和人们的实际生产生活紧密相关的,在实际的研发过程中都具有很强的代表性。

在此次的设计中,通过对电路性能指标的测试与调试,加强了我在分析和解决设计故障方面的能力, 为以后做设计打下了基础。我还懂得理论与实际相结合是很重要的,只有书上的理论知识是远远不够的,只有把理论知识与实际相结合,在实际操作中验证理论的正确性,加强自己对知识的理解,才能加重自己在社会中拼搏的筹码。所以,我们必须好好掌握这些知识结构,为将来走上工作岗位,解决实际问题打下良好的基础。