数字电子技术期末模拟卷1答案

系、班 姓 名 座 号

…………………密……………封……………线……………密……………封……………线…………………

《数字电子技术》课程考试题(1答卷)

( 年 月 日) 题 号

一

二 三 四 五

总分

复核人

得 分 评卷人

一、单项选择题(在每小题的备选答案中选出一个正确的答案,并将答案的号码填在括号内。每小题2分,共20分)

1、指出下列各种触发器中,哪些可以用来构成移位寄存器和计数器( 2 )。 (1)基本RS 触发器(2)边沿JK 触发器(3)同步RS 触发器(4)同步D 锁存器

2、构成一个9进制加法计数器共需( 4 )个触发器。

(1)3 (2)10 (3)2 (4)4

3、基本RS-FF 由二个与非门或者由二个或非门交叉构成,由二个与非门构成的

基本RS-FF 输入端触发信号是( 1 )。

(1) 低电平 (2)高电平 (3)脉冲前边沿 (4)脉冲后边沿

4、用CMOS 门电路组成的单稳态电路,脉冲宽度Tw 由(1 )决定。

(1)R 、C (2)触发信号 (3)电源电压 (4)以上都是

5、用若干RAM 实现位扩展而组成多位的RAM 时,其方法是将下列选项中的( 2 )

以外的部件相应地并联在一起。

(1)地址线 (2)数据线(输出线) (3)片选信号线 (4)读/写线

6、在一个N 位计数器中,时钟信号到达时,各触发器的翻转有先有后,这种触

发器称为( 2 )。

(1)同步计数器 (2)异步计数器 (3)时空计数器 (4)移位寄存计数器

7.下列函数式中,是最小项之和形式的为( B )

8.和TTL 电路相比,CMOS 电路最突出的优势在于( D )

A .可靠性高;

B .抗干扰能力强;

C .速度快;

D .功耗低。

9.可以将输出端直接并联实现“线与”逻辑的门电路是(D )

A .三态输出的门电路;

B .推拉式输出结构的TTL 门电路;

C .互补输出结构的CMOS 门电路;

D .集电极开路输出的TTL 门电

路。

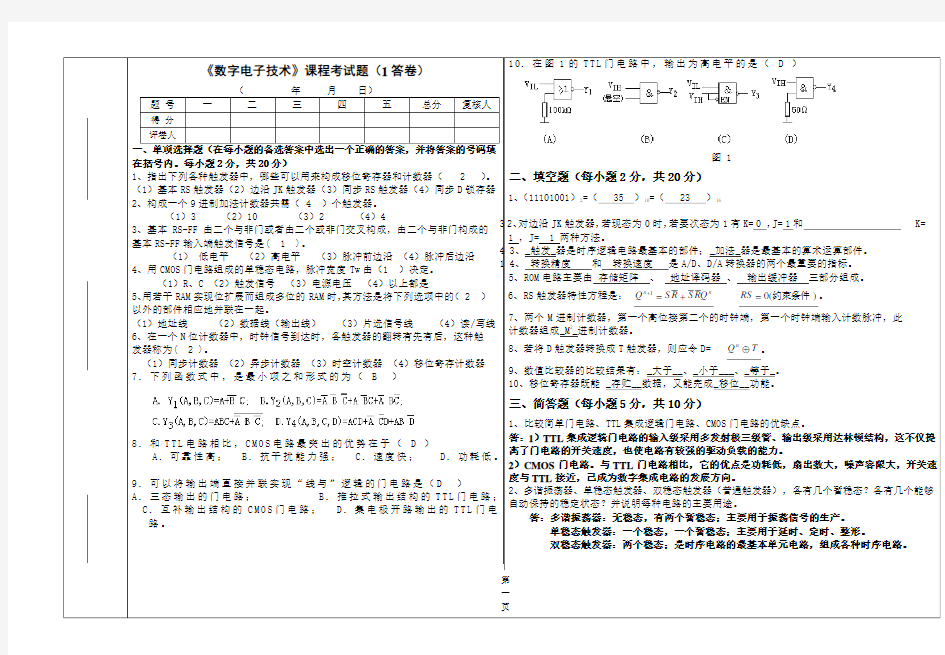

10.在图1的TTL 门电路中,输出为高电平的是( D )

图1

二、填空题(每小题2分,共20分) 1、(11101001)2=( 35 )10=( 23 )16

3 2、对边沿JK 触发器,若现态为0时,若要次态为1有K= 0 ,J= 1和 K=

1 ,J= 1 两种方法。

4 3、_触发_器是时序逻辑电路最基本的部件;_加法_器是最基本的算术运算部件。

1 4、 转换精度 和 转换速度 是A/D 、D/A 转换器的两个最重要的指标。

5、ROM 电路主要由 存储矩阵 、 地址译码器 、 输出缓冲器 三部分组成。

6、RS 触发器特性方程是: n n Q R S R S Q +=+1 )(0约束条件=RS 。

7、两个M 进制计数器,第一个高位接第二个的时钟端,第一个时钟端输入计数脉冲,此

计数器组成_M 2_进制计数器。

8、若将D 触发器转换成T 触发器,则应令D= T Q n ⊕。 9、数值比较器的比较结果有:_大于__、_小于___、_等于_。

10、移位寄存器既能 _存贮__数据,又能完成_移位__功能。

三、简答题(每小题5分,共10分)

1、比较简单门电路、TTL 集成逻辑门电路、CMOS 门电路的优缺点。

答:1)TTL 集成逻辑门电路的输入级采用多发射极三级管、输出级采用达林顿结构,这不仅提

高了门电路的开关速度,也使电路有较强的驱动负载的能力。

2)CMOS 门电路。与TTL 门电路相比,它的优点是功耗低,扇出数大,噪声容限大,开关速

度与TTL 接近,已成为数字集成电路的发展方向。

2、多谐振荡器、单稳态触发器、双稳态触发器(普通触发器),各有几个暂稳态?各有几个能够

自动保持的稳定状态?并说明每种电路的主要用途。

答:多谐振荡器:无稳态,有两个暂稳态;主要用于振荡信号的生产。

单稳态触发器:一个稳态,一个暂稳态;主要用于延时、定时、整形。

双稳态触发器:两个稳态;是时序电路的最基本单元电路,组成各种时序电路。 第一页

系、班 姓 名 座 号

…………………密……………封……………线……………密……………封……………线…………………

四、分析、设计和计算题(共40分)

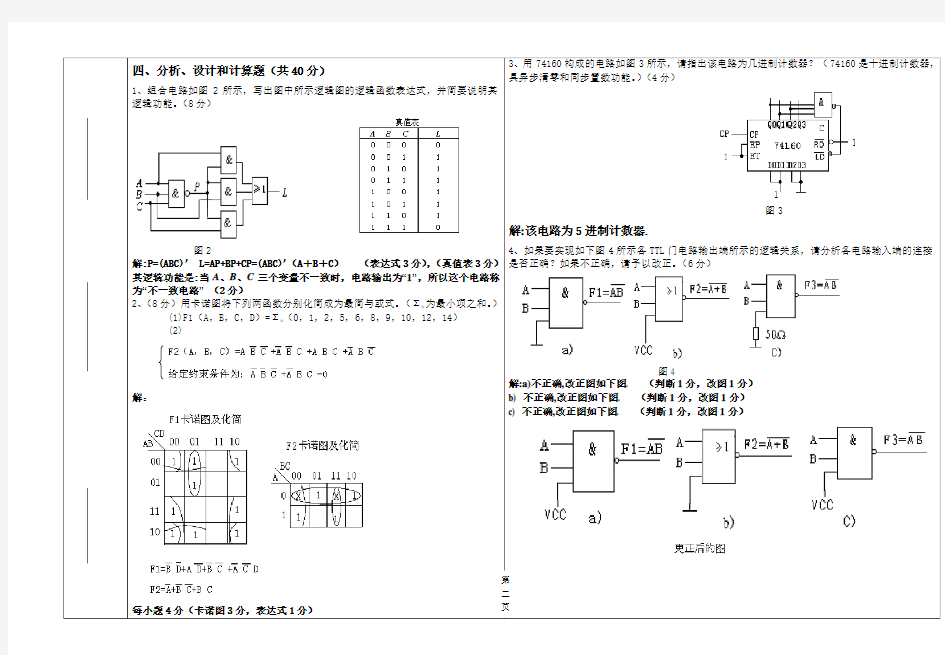

1、组合电路如图2所示,写出图中所示逻辑图的逻辑函数表达式,并简要说明其逻辑功能。(8分)

图2 解:P=(ABC)' L=AP+BP+CP=(ABC)'(A +B +C ) (表达式3分),(真值表3分) 其逻辑功能是:当A 、B 、C 三个变量不一致时,电路输出为“1”,所以这个电路称为“不一致电路” (2分) 2、(8分)用卡诺图将下列两函数分别化简成为最简与或式。(Σm 为最小项之和。)

(1)F1(A ,B ,C ,D )=Σm (0,1,2,5,6,8,9,10,12,14) (2)

解:

每小题4分(卡诺图3分,表达式1分)

3、用74160构成的电路如图3所示,请指出该电路为几进制计数器?(74160是十进制计数器,

具异步清零和同步置数功能。)(4分)

图3

解:该电路为5进制计数器.

4、如果要实现如下图4所示各TTL 门电路输出端所示的逻辑关系,请分析各电路输入端的连接

是否正确?如果不正确,请予以改正。(6分)

图4

解:a)不正确,改正图如下图. (判断1分,改图1分) b) 不正确,改正图如下图. (判断1分,改图1分) c) 不正确,改正图如下图. (判断1分,改图1分)

第二页

系、班 姓 名 座 号

…………………密……………封……………线……………密……………

封……………线…………………

5、用一个集成译码器74L138和二个与非门(自行添加)实现下列二输出逻辑函数,并画连线图。(S1、S2、S3是集成译码器74L138三个输入选通控制端)。(8分)

解:Y1=A'B'C+AB'C'+ABC+A'BC =m1+m3+m4+m7=((m1)’(m3)’(m4) ’(m7)’)’ Y2=A'B'C'+AB'C'+ABC' =m0+m4+m6=((m0)’(m4)’(m6)’)’ 画连线图如下图所示.

6、(6分)画出图5中各JK 触发器在时钟信号作用下输出端Q 0、Q 1电压的波形。设各触发器初态为0。

图5 解:

五、设计题(10分)

用与非门设计一个举重裁判表决电路。要求写出整个设计过程,并画出你所设计的逻辑图。设举重比赛有3个裁判,一个主裁判和两个副裁判,杠铃完全举上的裁决由每一个裁判按一下自己面前的按钮来确定,只有当两个或两个以上裁判判明成功,并且其中有一个为主裁判时,表明成功的灯才亮。

第三页

解:A 、B 、C 是提供给裁判用的开关,A 专门提供给主裁用,B 、C 给副裁用。设A 、B 、C 为1表示开关闭合(裁决为成功),0表示开关断开(裁决为失败); Y 为1表示灯亮(总裁决为成功),为0表示灯暗(总裁决为失败)。(2分) 真值表: (2分)

得到函数表示形式并化简为最简与或式:(2分) Y=((AB)'(AC)')'(与非-与非式)(1分)

逻辑图: (3分

)

AC AB ABC C AB C B A Y +=+'+'=