QuartusII入门详细教程实例讲解

Quartus II入门详细教程实例讲解

写在前面:

1.本教程适合以前没有接触过QuartusII开发软件的新手,本教程是基础的入门,后续的学习还得大家自己努力。

2.本教程非常详细手把手带大家入门,网上现存的很多教程,有的过于跳跃,难以跟上;有的遇到错误,但教程没有指出,导致我们不知道怎么做。

3.本教程首先通过简单的仿真实验带大家入门。VHDL源代码会附在文档最后。

4.本教程使用Quartus II 9.1版本进行演示,其他版本的操作差别不是太大,也可以进行学习。

目录

一、Quartus II开发软件基本介绍

1.1 Quartus Ⅱ简介

Quartus Ⅱ是Altera公司推出的专业EDA工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。

1.2 Quartus Ⅱ开发流程

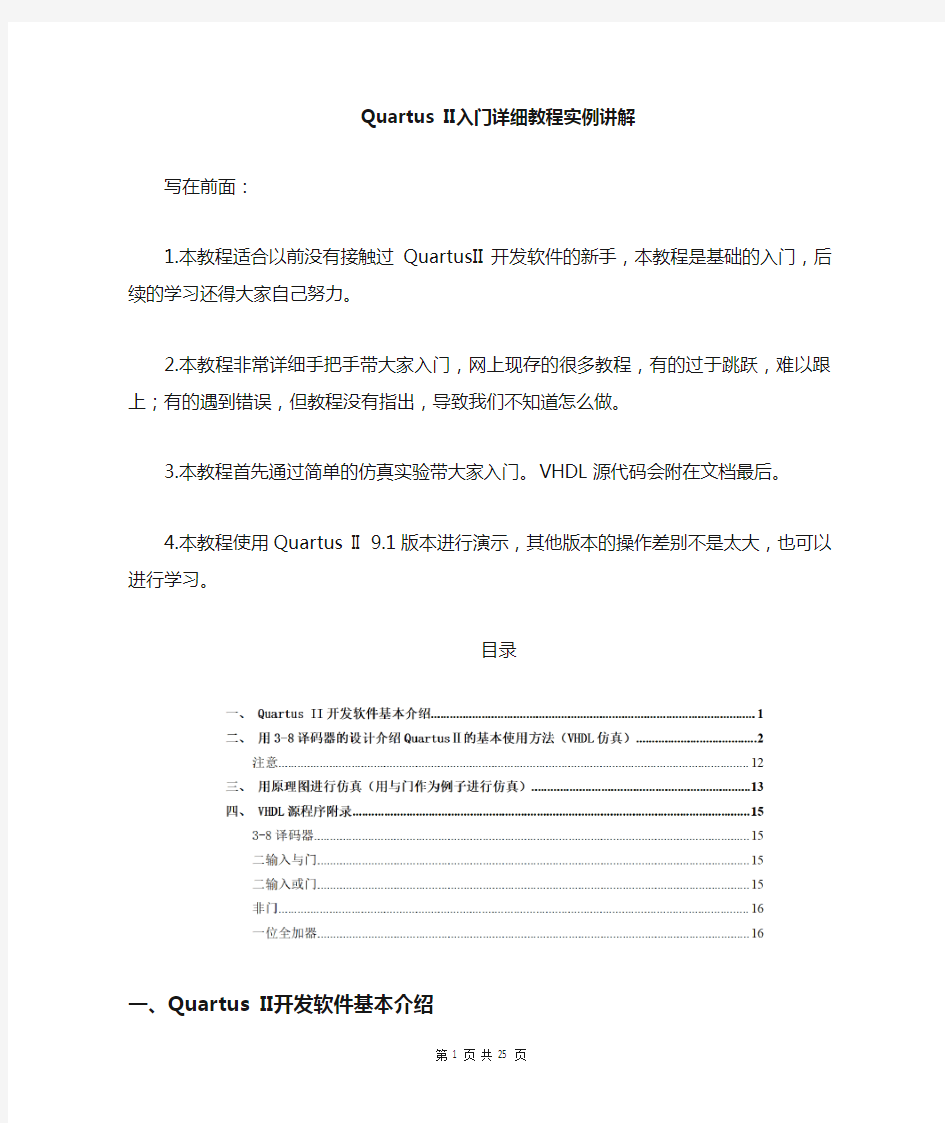

使用Quartus II 软件进行开发的流程如图1.2.1所示。需注意的是,Quartus II还可以使用命令行模式的TCL批处理脚本进行自动流程控制。

图1.2.1 Quartus Ⅱ开发流程

二、用3-8译码器的设计介绍QuartusⅡ的基本使用方法(VHDL仿真)

1.1打开软件

双击桌面安装好的QuartusⅡ 9.1图标,打开软件,主页面如图1所示。

图1

在图1中,1区为菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。2区为快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。3区为资源管理窗口。4区为编译及综合的进度栏:编译和综合的时候该窗口可以显示进度,当显示100%是表示编译或者综合通过。5区为工作区。6区为信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

2.2新建工程

运行菜单命令“File->New Project Wizard”,打开新工程向导,首先出现如图2所示的工程向导介绍对话框。点击Next按钮,进入如图3所示的下一设置页面,在其中设置工程目录、工程名称、顶层设计实体名称。工程目录点击选择我们提前在D盘altera文件中的SCU文件夹,工程名称为liuzhen,顶层设计实体名称自动与工程名称相同。

图2 工程向导介绍图3 工程设置点击Next按钮,进入如图4所示的对话框,在其中可以添加已存在的文件至工程和设定库的路径,我们在此可跳过。接着出现如图5所示的目标器件系列和具体芯片型号的设置对话框,如图5所示,用户可根据实际所使用的目标芯片和QuartusII的支持情况具体进行设置,当QuartusII不能支持时,则需要更换目标芯片或开发工具(MAX+ plus II)。因为本次测试只进行设计和软件仿真,不进行硬件仿真,故任意选择。点击“Next”进入下一步设置,选择仿真,综合工具本次实验全部利用quartus做,三项都选None,如图6所示。然后next,最后将给出一个工程信息摘要,如图7所示,点击Finish按钮,完成工程建立并退出向导过程。

图4 添加文件至工程图5器件系列和目标芯片设置

图6选择仿真,综合工具图7工程信息摘要

2.3 创建VHDL文件,编写程序

运行菜单命令“File->New”,如图8所示,点击“VHDL File”,然后点击OK。

图8 图9

3-8译码器的VHDL描述源文件如下:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY decoder_38 is

port( a: in std_logic_vector(2 downto 0);

b: out std_logic_vector(7 downto 0));

end decoder_38;

architecture Behavioral of decoder_38 is

begin

process(a)

begin

case a is

when "000"=> b <="11111110";

when "001"=> b <="11111101";

when "010"=> b <="11111011";

when "011"=> b <="11110111";

when "100"=> b <="11101111";

when "101"=> b <="11011111";

when "110"=> b <="10111111";

when "111"=> b <="01111111";

when others=> b <="11111111";

end case;

end process;

end Behavioral;

把程序写在图9所示VHDL文件中,接着按Ctrl+S 保存,文件保存在我们的工程文件夹SCU中,文件名为decoder_38.vhd,勾选Add file to current project。如图10。

图10

2.4检查语法

点击工具栏的这个按钮(start Analysis & synthesis),出现如图11所示错误:“Error: Top-level design entity "liuzhen" is undefined”。

图11

出现这个错误的原因是保存的文件名和结构体名字不一致,在quartus软件

中要求这样做,不然就出错。解决方法是点击工程里的文件本身,然后右键单击后点击“Set as Top-Level Entity”,如图12所示。

图12 Set as Top-Level Entity

再次点击工具栏的这个按钮,我们可以看见,已经没有错误了,如图13所示。

图13

然后点击工具栏的这个按钮,进行整体编译。

[在执行本步以后,若要进行硬件仿真,需要锁定引脚,锁定引脚步骤在后面的注意处会介绍,若只是进行软件仿真则直接跳过锁定引脚这步]

2.5功能仿真

把仿真类型设置为功能仿真(Assignments->setting 单击->Simulator Settings 点击 ->下拉Simulation mode >Functional),如图14所示。其中Functional表示功能仿真,既不包括时序信息,timinng表示时序仿真,加入线及寄存器的延时信息。

图14

然后建立一个波形文件:(File->new->Vector Waveform File)。添加波形文件作为信号输出文件,以便观察信号的输出情况.如图15所示。

图15

然后导入引脚,双击如图16所示Name下面空白区域,接着点击如图17所示Node Finder,然后先点击图18中的list再点击,再点击OK即可。

图16 图17

图18

接着设置激励信号,单击,再点击,如图19所示。再点击Timing,再Multiplied by 1,如图20所示。设置a[1]信号源的时候类同设置a[0]信号源,最后一步改为Multiplied by 2;设置a[2]信号源

的时候类同设置a[0]信号源,最后一步改为Multiplied by 3。

图19 图20

图21

图21中红框内为我们自定义的输入信号。

接着生成仿真需要的网表(工具栏processing->Generate Functional Simulation Netlist)。弹出如图22所示,点击“是”进行保存,我们保存为liuzhen.vwf,如图23,再点击保存跳出图24表示成功。

图22 图23

图24

接下来开始仿真,点击工具栏开始仿真,结果如图25所示。

图25 仿真结果

观察波形,3-8译码器产生的结果刚好符合我们的理论。因此该功能仿真通过,本次仿真正确。

注意:

1.在检查语法后,功能仿真前若需要下载到硬件进行仿真,要进行锁定引脚操作,下面大概介绍一下,因为一般新手刚入门还不需要进行硬件仿真。

点击工具栏的(pin planner),然后点击跳出来界面(图26)的 view-> ALL PIN LIST,接着根据实际选用的芯片的输入输出配置引脚,填写图27。这里在创建工程的时候,在器件系列和目标芯片设置处要对应选自己的芯片型号。

图26

图27

2.若需要下载到硬件进行仿真,最后一步还需要进行下载。

下载点击(Programmer),再点击Hardware Setup配置下载电缆,单击弹出窗口的“Add Hardware”按钮,选择并口下载ByteBlasterMV or ByteBlasterMVⅡ,单击“Close”按钮完成设置。CPLD器件生成的下载文件后缀名为.pof,点击下图所示方框,选中下载文件,然后直接点击start按钮开始下载

三、用原理图进行仿真(用与门作为例子进行仿真)

3.1新建工程请参考上一种方法,此处不赘述。为了不出错,请重新建一个工程,不要用第一种方法的工程。

3.2新建原理图文件(File->new->Block Diagram/Schematic File)

图3.2.1 图3.2.2

接着选择对应原器件放置并连接好,首先点击Symbol Tool(图3.2.2所示),然后再Library里面选择我们要用的器件,我们这里用的是and2,如图3.2.3,点击OK,接着再点击,同样的方法选出2个输入和1个输出,如图3.2.4所示。

图3.2.3 图3.2.4

然后把对应的引脚连接起来,同时可以点击pin_name对引脚进行改名。连接好的原理图如图3.2.5所示。

图3.2.5

接着按Ctrl+S 进行保存,我们把名字改为and_2.bdf,如图3.2.6。

图3.2.6

接下来就是进行仿真,其步骤和我们VHDL方法中的2.5是类似的,请阅读2.5步骤。最后我们会发现结果是正确的。

用原理图的方法就讲到这里。

四、VHDL源程序附录

4.1 3-8译码器

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY decoder_38 is

port( a: in std_logic_vector(2 downto 0);

b: out std_logic_vector(7 downto 0));

end decoder_38;

architecture Behavioral of decoder_38 is

begin

process(a)

begin

case a is

when "000"=> b <="11111110";

when "001"=> b <="11111101";

when "010"=> b <="11111011";

when "011"=> b <="11110111";

when "100"=> b <="11101111";

when "101"=> b <="11011111";

when "110"=> b <="10111111";

when "111"=> b <="01111111";

when others=> b <="11111111";

end case;

end process;

end Behavioral;

4.2 二输入与门

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY and2 IS

PORT(a,b:IN STD_LOGIC;

c:OUT STD_LOGIC);

END and2;

ARCHITECTURE and2_behavior OF and2 IS

BEGIN

c<= a AND b;

END and2_behavior;

4.3二输入或门

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY or2 IS

PORT(a,b:IN STD_LOGIC;

c:OUT STD_LOGIC);

END or2;

ARCHITECTURE or2_behavior OF or2 IS

BEGIN

c<=a OR b;

END or2_behavior;

4.4非门

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY not_gate IS

PORT(a:IN STD_LOGIC;

f:OUT STD_LOGIC);

END not_gate;

ARCHITECTURE not_gate_behavior OF not_gate IS

BEGIN

f<= NOT a;

END not_gate_behavior;

4.5一位半加器

LIBRARY IEEE;

LIBRARY IEEE.STD_LOGIC_1164.ALL;

ENTITY half_add_1 IS

PORT(a:IN STD_LOGIC;

b:IN STD_LOGIC;

co:OUT STD_LOGIC;

s:OUT STD_LOGIC);

END half_add_1;

ARCHITECTURE half_add_1_behavior OF half_add_1 IS

BEGIN

co<= a AND b;

s<= a XOR b;

END half_add_1_behavior;

组态王软件教程

组态王软件教程 软件教程 一、概述 1.概述 组态王软件结构由工程管理器、工程浏览器及运行系统三部分构成。 工程管理器:工程管理器用于新工程的创建和已有工程的管理,对已有工程进行搜索、添加、备份、恢复以及实现数据词典的导入和导出等功能。 工程浏览器:工程浏览器是一个工程开发设计工具,用于创建监控画面、监控的设备及相关变量、动画链接、命令语言以及设定运行系统配置等的系统组态工具。 运行系统:工程运行界面,从采集设备中获得通讯数据,并依据工程浏览器的动画设计显示动态画面,实现人与控制设备的交互操作。 2.建立应用工程的一般过程 1)创建新工程 为工程创建一个目录用来存放与工程相关的文件。 2)定义硬件设备并添加工程变量 添加工程中需要的硬件设备和工程中使用的变量,包括内存变量和I/O 变量。 3)制作图形画面并定义动画连接 按照实际工程的要求绘制监控画面并使静态画面随着过程控制对象产生动态效果。 4)编写命令语言 通过脚本程序的编写以完成较复杂的操作上位控制。 5)进行运行系统的配置

对运行系统、报警、历史数据记录、网络、用户等进行设置,是系统完成用于现场前的必备工作。 6)保存工程并运行 完成以上步骤后,一个可以拿到现场运行的工程就制作完成了。 二、建立一个新工程 1.工程管理器 组态王工程管理器是用来建立新工程,对添加到工程管理器的工程做统一的管理。工程管理器的主要功能包括:新建、删除工程,对工程重命名,搜索组态王工程,修改工程属性,工程备份、恢复,数据词典的导入导出,切换到组态王开发或运行环境等。 2.工程浏览器 工程浏览器是组态王6.55 的集成开发环境。 3.定义外部设备和数据变量 组态王把那些需要与之交换数据的硬件设备或软件程序都作为外部设备使用。外部硬件设备通常包括PLC、仪表、模块、变频器、板卡等;外部软件程序通常指包括DDE、OPC 等服务程序。按照计算机和外部设备的通讯连接方式,则分为:串行通信(232/422/485)、以太网、专用通信卡(如CP5611)等。 组态王与外部设备的通讯方式:如COM1、COM2、DDE、板卡、OPC 服务器、网络站点,其中COM1、COM2 表示组态王支持串口的通讯方式,DDE表示支持通过DDE 数据传输标准进行数据通讯,其他类似。 注意:标准的计算机都有两个串口,所以此处作为一种固定显示形式,这种形、COM2,也不表示组态王计算机上肯定有两个式并不表示组态王只支持COM1 串口;并且“设备”项下面也不会显示计算机中实际的串口数目,用户通过设备定义向导选择实际设备所连接的PC 串口即可。

quartusII图形设计过程教程

Quartus II 的使用 (2) 1 工程建立 (2) 2 原理图的输入 (5) 3 文本编辑(verilog) (15) 4 波形仿真 (16)

Quartus II 的使用 在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。 图 1.1 Quartus II 管理器 1.1 工程建立 使用New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。 建立工程的步骤如下:

(1)选择File菜单下New Project Wizard ,如图1.2所示。 图 1.2 建立项目的屏幕 (2)输入工作目录和项目名称,如图1.3所示。可以直接选择Finish,以下的设置过程可以在设计过程中完成。 图 1.3 项目目录和名称

(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。 图 1.4 加入设计文件 (4)选择设计器件,如图1.5所示。 图 1.5 选择器件

(5)选择第三方EDA综合、仿真和时序分析工具,如图1.6所示。 图 1.6 选择EDA 工具 (6)建立项目完成,显示项目概要,如图1.7所示。 图 1.7 项目概要 1.2 原理图的输入 原理图输入的操作步骤如下:

(1)选择File 菜单下New ,新建图表/原理图文件,如图1.8 所示。 图 1.8 新建原理图文件 (2)在图1.9的空白处双击,屏幕如图1.10所示: (3)在图1.10的Symbol Name 输入编辑框中键入dff后,单击 ok按钮。此时可看到光标上粘着被选的符号,将其移到合 适的位置(参考图 1.11)单击鼠标左键,使其固定; (4)重复(2)、(3)步骤,给图中放一个input、not、output 符号,如图1.11所示;在图1.11中,将光标移到右侧input 右侧待连线处单击鼠标左键后,再移动到D触发器的左侧 单击鼠标左键,即可看到在input和D触发器之间有一条 线生成;

组态王实例教程入门

组态王实例教程入门 组态王kingview6.55是亚控科技根据当前的自动化技术的发展趋势,面向低端自动化市场及应用,以实现企业一体化为目标开发的一套产品。该产品以搭建战略性工业应用服务平台为目标,集成了对亚控科技自主研发的工业实时数据库(KingHistorian)的支持,可以为企业提供一个对整个生产流程进行数据汇总、分析及管理的有效平台,使企业能够及时有效地获取信息,及时地做出反应,以获得最优化的结果。 组态王保持了其早期版本功能强大、运行稳定且使用方便的特点,并根据国内众多用户的反馈及意见,对一些功能进行了完善和扩充。组态王kingview6.55提供了丰富的、简捷易用的配置界面,提供了大量的图形元素和图库精灵,同时也为用户创建图库精灵提供了简单易用的接口;该款产品的历史曲线、报表及web发布功能进行了大幅提升与改进,软件的功能性和可用性有了很大的提高。 组态王在保留了原报表所有功能的基础上新增了报表向导功能,能够以组态王的历史库或KingHistorian为数据源,快速建立所需的班报表、日报表、周报表、月报表、季报表和年报表。此外,还可以实现值的行列统计功能。 组态王在web发布方面取得新的突破,全新版的Web发布可以实

现画面发布,数据发布和OCX控件发布,同时保留了组态王Web的所有功能:IE浏览客户端可以获得与组态王运行系统相同的监控画面,IE客户端与Web服务器保持高效的数据同步,通过网络您可以在任何地方获得与Web服务器上相同的画面和数据显示、报表显示、报警显示等,同时可以方便快捷的向工业现场发布控制命令,实现实时控制的功能。 组态王集成了对KingHistorian的支持,且支持数据同时存储到组态王历史库和工业库,极大地提高了组态王的数据存储能力,能够更好地满足大点数用户对存储容量和存储速度的要求。KingHistorian是亚控新近推出的独立开发的工业数据库。具有单个服务器支持高达100万点、256个并发客户同时存储和检索数据、每秒检索单个变量超过20,000 条记录的强大功能。能够更好地满足高端客户对存储速度和存储容量的要求,完全满足了客户实时查看和检索历史运行数据的要求。

Quartus_II使用教程-完整实例

Quartus Ⅱ入门教程 (一个Verilog 程序得编译与功能仿真) Quartus Ⅱ 就是Altera 公司推出得专业EDA 工具,支持原理图输入、硬件描述语言得输入等多种输入方式。硬件描述语言得输入方式就是利用类似高级程序得设计方法来设计出数字系统。接下来我们对这种智能得EDA 工具进行初步得学习。使大家以后得数字系统设计更加容易上手。 第一步:打开软件 快捷工具栏:提供设置(setting),编译(pile)等快捷方式,方便用户使用,用户也可以在菜单栏得下拉菜单找到相应得选项。● 菜单栏:软件所有功能得控制选项都可以在其下拉菜单中找到。 ● 信息栏:编译或者综合整个过程得详细信息显示窗口,包括编译通过信息与报错信息。 第二步:新建工程( Project Wizard ) 1 工程名称: 快捷工具栏 菜单栏 所建工程得保存路径 工作区 资源管理窗口 任务管理窗口

dqgxo 。 2添加已有文件(没有已有文件得直接跳过next ) 3 选择芯片型号(我们选择MAX3000A 系列下得EPM3256AQC208-10芯片) (注:如果不下载到开发板上进行测试,这一步可以不用设置) 工程名称 顶层模块名(芯片级设计为实体名),要求与工程名称相同 如果有已经存在得文 件就在该过程中添加, 软件将直接将用户所添加得文件添加到工程中。

4 选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None,然后next) 5 工程建立完成(点finish ) 所选得芯片得系列型号 快速搜索所需得芯片 选择芯片 选择第三方综合工具,如果使用Quartus 内部综合工具则选择none 选择第三方仿真工具,如果使用Quartus 内部仿真工具则选择none 选择时序分析仪

QuartusII教程(完整版)

Quartus II 的使用 (1) 1 工程建立 (1) 2 原理图的输入 (4) 3 文本编辑(verilog) (14) 4 波形仿真 (17)

Quartus II 的使用 在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。 图 1.1 Quartus II 管理器 1.1 工程建立 使用New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。还可以指定要在工程中使用的设计文件、其它源文件、用户库和EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。 建立工程的步骤如下:

(1)选择File菜单下New Project Wizard ,如图1.2所示。 图 1.2 建立项目的屏幕 (2)输入工作目录和项目名称,如图1.3所示。可以直接选择Finish,以下的设置过程可以在设计过程中完成。 图 1.3 项目目录和名称

(3)加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。 图 1.4 加入设计文件 (4)选择设计器件,如图1.5所示。 图 1.5 选择器件

(5)选择第三方EDA综合、仿真和时序分析工具,如图1.6所示。 图 1.6 选择EDA 工具 (6)建立项目完成,显示项目概要,如图1.7所示。 图 1.7 项目概要 1.2 原理图的输入 原理图输入的操作步骤如下:

(1)选择File 菜单下New ,新建图表/原理图文件,如图1.8 所示。 图 1.8 新建原理图文件 (2)在图1.9的空白处双击,屏幕如图1.10所示: (3)在图1.10的Symbol Name 输入编辑框中键入dff后,单击ok按钮。此时可看到光标上粘着被选的符号,将其移到合适的位置(参考图 1.11)单击鼠标左键,使其固定;(4)重复(2)、(3)步骤,给图中放一个input、not、output 符号,如图1.11所示;在图1.11中,将光标移到右侧input 右侧待连线处单击鼠标左键后,再移动到D触发器的左侧单击鼠标左键,即可看到在input和D触发器之间有一条线生成;

组态王教程1

组态王软件培训

培训内容 内容包括: 1、组态王介绍 2、新建工程 3、建立IO设备通信 4、建立数据词典 5、画面组态 6、设置,然后运行 7、脚本编程,函数等。

组态王软件是一种通用的工业监控软件, 它适用于从单一设备的生产运营管理和故障诊断,到网络结构分布式大型集中监控管理系统的开发。支持与国内外常见的PLC、智能模块、智能仪表、变频器、数据采集板卡进行数据通讯组态王软件结构由工程管理器、工程浏览器及运行系统三部分构成。

组态软件的安装 1、运行安装组态王程 序。直接安装。 2、安装完后直接安装 驱动。 3、其它内容可以不安 装。

工程管理器:工程管理器用于新工程的创建和已有工程的管理,对已有工程进行搜索、添加、备份、恢复以及实现数据词典的导入和导出等功能。 工程浏览器:工程浏览器是一个工程开发设计工具,用于创建监控画面、监控的设备及相关变量、动画链接、命令语言以及设定运行系统配置等的系统组态工具。 运行系统:工程运行界面,从采集设备中获得通讯数据,并依据工程浏览器的动画设计显示动态画面,实现人与控制设备的交互操作。

组态王软件是一种通用的工业监控软件, 它适用于从单一设备的生 产运营管理和故障诊断,到网络结构分布式大型集中监控管理系统的开发。支持与国内外常见的PLC、智能模块、智能仪表、变频器、数据采集板卡进行数据通讯组态王软件结构由工程管理器、工程浏览器及运行系统三部分构成。 工程管理器:工程管理器用于新工程的创建和已有工程的管理,对已有工程进行搜索、添加、备份、恢复以及实现数据词典的导入和导出等功能。 工程浏览器:工程浏览器是一个工程开发设计工具,用于创建监控画面、监控的设备及相关变量、动画链接、命令语言以及设定运行系统配置等的系统组态工具。 运行系统:工程运行界面,从采集设备中获得通讯数据,并依据工程浏览器的动画设计显示动态画面,实现人与控制设备的交互操作。

FPGA入门及Quartus II使用教程(内部资料)

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。 可以这样讲,ASIC(Application Specific Integrated Circuit )内部的所有资源,是用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。并且可以通过软件仿真,我们可以事先验证设计的正确性。 第一章FPGA的基本开发流程 下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。 下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管 理。 2、建立顶层图。可以这样理解,顶层图是一个容器,将整个工程的各个模块包 容在里边,编译的时候就将这些模块整合在一起。也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。 3、采用ALTERA公司提供的LPM功能模块。Quartus软件环境包含了大量的常 用功能模块,比如计数器、累加器、比较器等等。 4、自己建立模块。由于有些设计中现有的模块功能不能满足具体设计的要求, 那就只能自己设计。使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。 5、将顶层图的各个功能模块连线起来。这个过程类似电路图设计,把各个芯片 连起来,组成电路系统。 6、系统的功能原理图至此已经基本出炉了,下一步就是选择芯片字载体,分配 引脚,设置编译选项等等。 7、编译。这个过程类似软件开发里德编译,但是实际上这个过程比软件的编译 复杂的多,因为它最终要实现硬件里边的物理结构,包含了优化逻辑的组合,综合逻辑以及布线等步骤。 8、编译后会生成2个文件,一个是*.sof文件,一个是*.pof文件,前者可以通过 JTAG方式下载到FPGA内部,可以进行调试,但断电后数据丢失;后者通过AS或者PS方式下载到FPGA的配置芯片里边(EEPROM或者FLASH),重新上电后FPGA会通过配置将数据读出。 9、对于复杂的设计,工程编译好了,我们可以通过Quartus软件或者其他仿真 软件来对设计进行反复仿真和验证,直到满足要求。(主要是时序仿真)。 第二章基于Quartus II的实例 一、建立工程 首先,打开Quartus II软件。

组态王日报表例程

组态王日报表的实现例程 配置参考文档 北京亚控科技发展有限公司 技术部 目录 一、功能概述 (2) 一、功能概述 (2) 二、工程实例 (2) 三、操作步骤: (2) 1、定义设备: (2) 2、定义变量: (2) 3.制作画面: (3) 3.1) 创建报表: (3) 3.2) 创建日历控件: (5) 4.进入运行系统: (11) 四、注意事项 (12) 图表 图一报表 (4) 图二报表设计 (4) 图三日报表 (5) 图四日历控件 (6) 图五控件事件函数 (9) 图六保存报表 (9) 图七打印报表 (10) 图八打印报表 (10) 图九运行系统 (11) 图十打印预览 (12)

一、功能概述 常规需求:很多工业现场会用到报表功能,而日报是其中最基本的一种报表形式。 日报表一般为每天整点的数据,每一个变量有24个数据。 组态王中的实现方法: 利用组态王内置报表以及报表的函数来实现对日数据的查询生成日报表。 组态王内置报表的操作类似excel,操作简单、方便,并且组态王提供了大量的报表函数来实现各种复杂功能。 二、工程实例 我们举一个例子来说明日报表的实现方法。在此例程中我们定义五个变量,分别为“压力”、“温度”、“密度”、“电流”、“电压”,运行系统运行后记录历史数据,查询日报表数据时自动从历史数据中查询整点数据生成报表,并可以保存、打印报表。下面就以此为例来演示完成这一要求的具体步骤。 三、操作步骤: 1、定义设备: 根据工程中实际使用得设备进行定义,本例程使用亚控的仿真PLC设备,使用“PLC-亚控-仿真PLC-串口”驱动,定义设备名称为”PLC”。 2、定义变量: 在组态王中定义三个变量:压力(IO实数类型)、温度(IO实数类型)、密度(IO实数类型)。压力变量:最小值0,最大值100,最小原始值0,最大原始值100,连接设备PLC,寄存器INCREA100,数据类型short,读写属性为只读,采集频率1000。记录和安全区选择“数据变化记录”,变化灵敏度选择“0”。 温度变量:最小值0,最大值50,最小原始值0,最大原始值100,连接设备PLC,寄存器DECREA100,数据类型short,读写属性为只读,采集频率1000。记录和安全区选择“数据变化记录”,变化灵敏度选择

组态王 实例

一、概述 组态王软件结构由工程管理器、工程浏览器及运行系统三部分构成。工程管理器:工程管理器用于新工程得创建与已有工程得管理,对已有工程进行搜索、添加、备份、恢复以及实现数据词典得导入与导出等功能。工程浏览器:工程浏览器就是一个工程开发设计工具,用于创建监控画面、监控得设备及相关变量、动画链接、命令语言以及设定运行系统配置等得系统组态工具。运行系统:工程运行界面,从采集设备中获得通讯数据,并依据工程浏览器得动画设计显示动态画面,实现人与控制设备得交互操作。 通常情况下,建立一个应用工程大致可分为以下六个步骤: 1.创建新工程为工程创建一个目录用来存放与工程相关得文件。 2.定义硬件设备并添加工程变量添加工程中需要得硬件设备与工程中使 用得变量,包括内存变量与 I/O 变量。 制作图形画面并定义动画连接按照实际工程得要求绘制监控画面并 使静态画面随着过程控制对象产生动态效果。 4.编写命令语言通过脚本程序得编写以完成较复杂得操作上位控制。 进行运行系统得配置对运行系统、报警、历史数据记录、网络、用户 等进行设置,就是系统完成用于现场前得必备工作。 6.保存工程并运行完成以上步骤后,一个可以拿到现场运行得工程就制 作完成了。 接下来我将建立一个反应车间得监控中心。监控中心从现场采集生产数据,以动画形式直观得显示在监控画面上。监控画面还将显示实时趋势与报警信息,并提供历史数据查询得功能,完成数据统计得报表。将实时数据保存到关系数据库中,并进行数据库得查询等。 二、建立一个新工程 一) 建立一个新工程 点击“开始”---〉“程序”---〉“组态王 6、5”---〉“组态王6、5”(或直接双桌面上组态王得快捷方式),启动后得工程管理窗口如图2-1 所示: 图2-1 图2-2 新建:单击此快捷键,弹出新建工程对话框建立组态王工程。点击工程管 理器上得“新建”,弹出“新建工程向导之一”,接下来一直按下一步直到点 击完成后会出现“就是否将新建得工程设为组态王当前工程”得提示,选择 “就是”即可新建一工程如图2-2: 二) 工程浏览器

QuartusII入门详细教程实例讲解

Quartus II入门详细教程实例讲解 写在前面: 1.本教程适合以前没有接触过QuartusII开发软件的新手,本教程是基础的入门,后续的学习还得大家自己努力。 2.本教程非常详细手把手带大家入门,网上现存的很多教程,有的过于跳跃,难以跟上;有的遇到错误,但教程没有指出,导致我们不知道怎么做。 3.本教程首先通过简单的仿真实验带大家入门。VHDL源代码会附在文档最后。 4.本教程使用Quartus II 9.1版本进行演示,其他版本的操作差别不是太大,也可以进行学习。 目录 一、Quartus II开发软件基本介绍 1.1 Quartus Ⅱ简介 Quartus Ⅱ是Altera公司推出的专业EDA工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。 1.2 Quartus Ⅱ开发流程 使用Quartus II 软件进行开发的流程如图1.2.1所示。需注意的是,Quartus II还可以使用命令行模式的TCL批处理脚本进行自动流程控制。

图1.2.1 Quartus Ⅱ开发流程 二、用3-8译码器的设计介绍QuartusⅡ的基本使用方法(VHDL仿真) 1.1打开软件 双击桌面安装好的QuartusⅡ 9.1图标,打开软件,主页面如图1所示。 图1 在图1中,1区为菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。2区为快捷工具栏:提供设置(setting),编译(compile)等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。3区为资源管理窗口。4区为编译及综合的进度栏:编译和综合的时候该窗口可以显示进度,当显示100%是表示编译或者综合通过。5区为工作区。6区为信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

Quartus_II简明教程

Quartus II简明教程 Altera公司的Quartus II设计软件是用来进行SOPC(System-on-a-programmable-chip)设计的综合的设计环境。本教程适用于Quartus II软件的新用户,介绍使用Quartus II软件的进行FPGA设计的基本方法。需要注意,本教程并不是Quartus II软件的详尽的参考手册。 本教程包含的主要内容: 1、典型的FPGA设计流程; 2、开始 3、新建project 4、设计输入 5、编译 6、引脚分配 7、仿真 8、编程、配置FPGA器件 9、板级调试

1、 典型的FPGA 设计流程 计算机辅助设计(Computer Aided Design ,CAD )软件的使用使得使用可编程逻辑器件(Programmable Logic Device ,PLD)器件(比如Field Programmable Gate Array ,FPGA)进行数字逻辑电路设计变得非常容易。使用CAD 软件进行FPGA 设计的典型流程如图1所示。 图1 FPGA 设计的典型设计流程 Quartus II 软件支持以上设计流程的所有阶段。本教程介绍Quartus II 软件的基本特征。 2、 开始 在Quartus II 软件中设计的每个电路或者子电路都叫做项目(Project )。Quartus II 软件每次只能打开一个Project ,并且一个Project 的所有信息都必须保存在同一个文件夹。为了开始一个新逻辑电路的设计,首先第一步就是新建一个文件夹来保存此Project 的文件。为了保存本教程的设计项目Project ,新建文件夹D:\introtutorial 。本教程运行的例子是一个简单两路开关控制电路。 启动Quartus II 软件,会打开如图2所示启动画面。启动画面中包含了使用Quartus II 软件所需要的

组态王实例教程入门

Kingview简介:本教程是学习Kingview软件的入门课程,涵盖了Kingview软件的大多数基本功能。学习完本教程后,您将能够建立上位机监控系统的功能齐全,实用的应用程序。以下课程向您展示如何:*使用工程浏览器*创建新项目*绘制图片*使用库和控件*构造数据库*与较低端的计算机通信*生成动画效果*查看趋势曲线和警报信息*设计自定义报告*系统安全性您可以按照上述步骤配置化工厂反应车间的模型并建立监控中心。完成后的配置将具有操作按钮,趋势曲线和警报功能。以下是配置屏幕:Kingview 教程课程1了解Kingview。在本课程中,您将:·了解Kingview软件的整体结构,了解Kingview的工件模式,并了解构建应用程序的一般过程。组态王软件“组态王”的结构是在Microsoft Windows 98 / NT的中文平台上运行的配置软件。多线程和COM组件等新技术用于实现实时多任务。该软件运行稳定可靠。Kingview具有集成的开发环境“Kingview项目浏览器”。在项目浏览器中,您可以查看项目的各个组件,还可以完成构建数据库和定义外部设备的工作。屏幕的开发和操作通过项目浏览器调用图片制作系统touchmak和图片运行系统touchview来完成。Touchmak是一个应用程序开发环境。

您需要在此环境中完成设计屏幕,动画连接等。Touchmak具有先进而完善的图形生成功能;数据库中有许多数据类型,可以合理地抽象控制对象的特征。它具有重要功能的简单操作方法,例如可变警报,趋势曲线,过程记录,安全性等。Touchview是Kingview 软件的实时运行环境。在touchmap中创建的图形只能在touchview中运行。Touchview 从工业控制对象收集数据并将其记录在实时数据库中。它还负责以动画形式显示数据的变化,同时,它还可以完成诸如可变警报,操作记录和趋势曲线的监视功能,并生成历史数据文件。Kingview如何与下位计算机通信?组态王将第一台较低的计算机视为外部设备。在开发过程中,您可以根据“设备配置向导”逐步完成连接过程。在运行期间,Kingview通过驱动程序与这些外部设备交换数据,包括收集数据和发送数据/指令。每个驱动程序都是一个COM对象,使通讯程序和Kingview构成一个完整的系统,不仅保证了运行系统的高效率,而且使系统可以大规模使用。如何产生动画效果?开发人员在touchmak中制作的图片是静态的,那么它们如何通过动画来反映工业场景的情况?这需要通过实时数据库完成,因为只有数据库中的变量才与现场条件同步。数据库变量的更

Quartus_II_9.0_使用初级教程

Quartus Ⅱ 9.0 使用教程(初级) Quartus Ⅱ 是Altera 公司推出的专业EDA 工具,支持原理图输入、硬件描述语言的输入等多种输入方式。硬件描述语言的输入方式是利用类似高级程序的设计方法来设计出数字系统。接下来我们对这种智能的EDA 工具进行初步的学习。使大家以后的数字系统设计更加容易上手。 第一步:打开软件 ● 快捷工具栏:提供设置(setting ),编译( compile )等快捷方式,方便用户使用,用户也可以在菜单栏的下拉菜单找到相应的选项。 ● 菜单栏:软件所有功能的控制选项都可以在其下拉菜单中找到。 ● 编译及综合的进度栏:编译和综合的时候该窗口可以显示进度,当 显示100%是表示编译或者综合通过。 ● 信息栏:编译或者综合整个过程的详细信息显示窗口,包括编译通过信息和报错信息。

第二步:新建工程(file>new Project Wizard ) 1 工程名称: 2添加已有文件(没有已有文件的直接跳过next )

3 选择芯片型号(我们选择MAX3000A 系列下的EPM3256AQC208-10芯片) 4 选择仿真,综合工具(第一次实验全部利用quartus 做,三项都选None ,然后next )

5 工程建立完成(点finish) 第三步:添加文件(file>new> VHDL file),新建完成之后要先保存。

第四步:编写程序 3-8译码器的VHDL描述源文件如下: library ieee; use ieee.std_logic_1164.all; entity decoder3_8 is port( A:in std_logic_vector(2 downto 0); EN:in std_logic; Y:out std_logic_vector(7 downto 0)); end decoder3_8; architecture example_1 of decoder3_8 is signal sel:std_logic_vector(3 downto 0); begin sel<=A & EN; with sel select Y <= "11111110" when "0001", "11111101" when "0011", "11111011" when "0101", "11110111" when "0111", "11101111" when "1001", "11011111" when "1011",

QuartusII10.0简明教程

Quartus ii 10.0教程 说明 本文的部分章节,来源于本人翻译的Terasic DE2-115的英文入门文档。 平台 硬件:艾米电子EP2C8-2010增强版套件 软件:Quartus II 10.0 + ModelSim-Altera 6.5e (Quartus II 10.0) Starter Edition 内容 ?典型的CAD流程 ?开始 ?新建工程 ?录入Verilog设计 ?编译设计 ?引脚分配 ?仿真设计电路 ?编程及配置到FPGA器件 ?测试设计电路 典型的CAD流程 计算机辅助设计(CAD)软件,使得运用可编程逻辑器件实现所需逻辑电路,变得容易。比如现场可编程门阵列(FPGA)。典型的FPGA CAD设计流程如图1所示。

图1 典型的FPGA CAD设计流程 CAD流程包含以下步骤: ?设计输入——所需电路可通过原理图方式或硬件描述语言方式(如Verilog或VHDL)进行设计。 ?综合——输入的设计被综合进入由逻辑元素(LEs,FPGA芯片提供)组成的电路中。 ?功能仿真——综合电路被测试以验证其功能是否正确,次仿真不考虑时序因素。 ?布局布线——CAD Fitter工具决定网表中定义的LEs如何布置成FPGA芯片中的实际LEs。 ?时序分析——分析已布局布线电路中的不同路径的传播延迟,用以指示所需电路的性能。 ?时序仿真——测试已布局布线电路,验证其是否在功能和时序上都正确。 ?编程及配置——设计的电路,通过编程配置开关,被实现到一个物理的FPGA芯片。 配置开关用于配置LEs和建立所需线路连接。 本指南介绍Quartus II软件的基本特征。展示如何使用Verilog硬件描述语言来设计和实现电路。使用GUI来实现Quartus II指令。通过本份指南,读者将学习到: ?新建工程 ?使用Verilog代码录入设计 ?将综合的电路布局到Altera FPGA ?分配电路的输入输出到FPGA上的指定引脚 ?仿真设计电路 ?编程配置艾米电子EP2C8核心板上的FPGA芯片 1. 开始 在Quartus II中设计的每个逻辑电路或子电路,叫做一个工程。软件每次运行一个工程,并将所有信息保存在单一文件夹中。欲开始一个新的逻辑电路设计,第一步就是新建一个文件夹来保存文件。为了保存本指南的设计文件,在D盘新建introtutorial文件夹。指南者运行的范例为一个简单的双路灯控电路。 打开Quartus II软件,将看到类似于图2的画面。该显示画面包括若干窗口,用户可使用鼠标选择,以访问Quartus II软件的相关功能。Quartus II提供的大多数命令都可用菜单形式来访问。例如,在图2中,在File标签下点击左键,可打开如图3所示的菜单。用左键单击Exit可退出Quartus II软件。

组态王教程——很实用

组态王简明教程 组态王软件的结构 “组态王”是运行于Microsoft Windows 98/NT中文平台的全中文界面的组态软件,采用了多线程、COM组件等新技术,实现了实时多任务,软件运行稳定可靠。组态王具有一个集成开发环境“组态王工程浏览器”,在工程浏览器中您可以查看工程的各个组成部分,也可以完成构造数据库、定义外部设备等工作。画面的开发和运行由工程浏览器调用画面制作系统TOUCHMAK和画面运行系统TOUCHVEW来完成的。TOUCHMAK是应用程序的开发环境。您需要在这个环境中完成设计画面、动画连接等工作。TOUCHMAK具有先进完善的图形生成功能;数据库中有多种数据类型,能合理地抽象控制对象的特性;对变量报警、趋势曲线、过程记录、安全防范等重要功能都有简单的操作办法。TOUCHVEW是“组态王”软件的实时运行环境,在TOUCHMAK中建立的图形画面只有在TOUCHVEW中才能运行。TOUCHVEW从工业控制对象中采集数据,并记录在实时数据库中。它还负责把数据的变化用动画的方式形象地表示出来,同时完成变量报警、操作记录、趋势曲线等监视功能,并生成历史数据文件。 组态王怎样和下位机通讯 “组态王”把第一台下位机看作是外部设备,在开发过程中您可以根据“设备配置向导”的提示一步步完成连接过程。在运行期间,组态王通过驱动程序和这些外部设备交换数据,包括采集数据和发送数据/指令。每一个驱动程序都是一个COM对象,这种方式使通讯程序和组态王构成一个完整的系统,既保证了运行系统的高效率,也使系统能够达到很大的规模。 怎样产生动画效果 开发者在TOUCHMAK中制作的画面都是静态的,那么它们如何以动画方式反映工业现场的状况呢?这需要通过实时数据库,因为只有数据库中的变量才是与现场状况同步变化的。数据库变量的变化又如何导致画面的动画效果呢?通过“动画连接”就是建立画面的图素与数据库变量的对应关系。这样,工业现场的数据,比如温度、液面高度等,当它们发生变化时,通过驱动程序,将引起实时数据库中变量的变化,如果画面上有一个图素,比如指针,您规定了它的偏转角度与这个变量相关,您就会看到指针随工业现场数据的变化而同步偏转。动画连接的引入是设计人机接口的一次突破它把程序员从重复的图形编程中解放出来,为程序员提供了标准的工业控制图形界面,并且有可编程的命令语言连接来增强图形界面的功能。 建立应用程序的一般过程

Quartus II教程

第3章 Altera Quartus II软件开发向导 基于Altera Quartus II软件的设计方法有模块编辑法、文本编辑法、宏模块编辑法和包含前三种方法的混合编辑法。宏模块设计法放在第6章讲述,本章通过实例简单介绍使用Quartus II软件的模块原理图编辑法、文本编辑法和包含前两种方法的混合编辑法。 3.1模块编辑及设计流程 Quartus II软件的模块编辑器以原理图的形式和图标模块的形式来编辑输入文件。每个模块文件包含设计中代表逻辑的框图和符号。模块编辑器可以将框图、原理图或符号集中起来,用信号线、总线或管道连接起来形成设计,并在此基础上生成模块符号文件(.bdf)、AHDL Include文件(.inc)和HDL 文件。 3.1.1 原理图输入文件的建立 在这里我们设计非常简单一个二输入的或门电路。它只包含一个或门、两个输入引脚和一个输出引脚。首先创建一个原理图形式的输入文件。步骤如下: (1)打开模块编辑器 单击【File】|【New】,弹出新建文件对话框,如图3.1所示。 图3.1 新建文件对话框 选择文件类型【Block Diagram/Schematic File】,打开模块编辑器,如图3.2所示。使用该编辑器可以编辑图标模块,也可以编辑原理图。

·217· 图3.2 模块编辑器 Quartus II提供了大量的常用的基本单元和宏功能模块,在模块编辑器中可以直接调用它们。在模块编辑器要插入元件的地方单击鼠标左键,会出现小黑点,称为插入点。然后鼠标左键,弹出【Symbol】对话框,如图3.3所示。或者在工具栏中单击图标,也可打开该对话框。 图3.3 Symbol对话框 在Symbol对话框左边的元件库【Libraries】中包含了Quartus II提供的元件。它们存放在\altera\quartus60\libraries\的子目录下,分为primitives、others、megafunctions三个大类。 基本逻辑函数(primitives) 基本逻辑函数存放在\altera\quartus60\libraries\ primitives\的子目录下,分别为缓冲逻辑单元(buffer)、基本逻辑单元(logic)、其它单元(other)、引脚单元(pin)和存储单元(storage)五个子类。Buffer子类中包含的是缓冲逻辑器件,如alt_in buffer、alt_out_buffer、wire等;logic子类中包含的是基本逻辑器件,如and、or、xor等门电路器件;other子类中包含的是常量单元,如constant、vcc和gnd等;pin子类中包含的是输入、输出和双向引脚单元;storage子类中包含的是各类触发器,如dff、tff等。

QuartusII简明教程(完整版)

目录 : Quartus II 的使用 (1) 1 工程建立 (1) 2 原理图的输入 (4) 3 文本编辑(verilog) (14) 4 波形仿真 (16)

Quartus II 的使用 在这里,首先用最简单的实例向读者展示使用Quartus II软件的全过程。进入WINDOWS XP后,双击Quartus II图标,屏幕如图1.1所示。 图 1.1 Quartus II 管理器 1.1 工程建立 使用 New Project Wizard,可以为工程指定工作目录、分配工程名称以及指定最高层设计实体的名称。 还可以指定要在工程中使用的设计文件、其它源文件、用户库和 EDA 工具,以及目标器件系列和器件(也可以让Quartus II 软件自动选择器件)。 建立工程的步骤如下:

(1) 选择File菜单下New Project Wizard ,如图1.2所示。 图 1.2 建立项目的屏幕 (2) 输入工作目录和项目名称,如图1.3所示。可以直接选择Finish,以下的设置过程可以在设计过程中完成。 图 1.3 项目目录和名称

(3) 加入已有的设计文件到项目,可以直接选择Next,设计文件可以在设计过程中加入,如图1.4所示。 图 1.4 加入设计文件 (4) 选择设计器件,如图1.5所示。 图 1.5 选择器件

(5) 选择第三方EDA综合、仿真和时序分析工具,如图1.6所示。 图 1.6 选择EDA 工具 (6) 建立项目完成,显示项目概要,如图1.7所示。 图 1.7 项目概要 1.2 原理图的输入 原理图输入的操作步骤如下:

组态王实例教程入门

工业组态软件实用教程: 张岳,辽宁科技学院,教授,研究方向为特种电机与风力发电,以第一作者发表高水平学术论文12篇,其中EI检索4篇。主编出版了《集散控制系统及现场总线》、《自动控制原理》和《MATLAB 程序设计与应用基础教程》三部教材,其中《集散控制系统及现场总线》被评为“十一五”国家级规划教材。 序言: 本书以目前广泛应用的组态王Kingview6.53软件为基础,较为全面地介绍了组态王软件的基础知识和实际应用。通过简单实例的建立和运行,将如何应用组态王软件的基本步骤贯穿于各章节之中,从而使读者能由浅入深地学习和掌握组态王软件。 本书注重实用性,做到理论知识够用为度,突出实践教学和实际应用知识,针对性强,实用性强,理论与实际工程知识穿插进行。 本书在结构安排上遵循由浅入深、快速入门的原则,通过第1章对组态王软件基础知识的学习,快速掌握一般组态王工程的设计过程;经过第2~6章的理论和实例的深入学习,逐渐掌握组态王的实际应用,加深对组态王知识的理解和应用;通过第7章实训部分的学习,可以使读者根据自己的实际情况,有选择性地应用组态王软件来模拟实际工程实例进行学习。 本书在编写过程中,充分考虑到该课程的教学时数有限(计划40学时左右),而组态王软件内容丰富的特点,以及当前学生的知

识水平和能力结构的现状,力求做到理论知识“少而精,够用为度”,注重培养学生解决实际问题的应用能力。 为了方便教学,每章均安排有一定数量的习题。另外,建议采用多媒体授课方式。 全书由辽宁科技学院张岳、于会敏、韩召共同编写。其中,第1、2章由张岳编写,第4、5章由张岳和于会敏共同编写,第3、6章由于会敏编写,第7章由韩召编写,全书由张岳负责统稿。在编写过程中,借鉴了一些兄弟院校的教材和参考文献所列的部分内容,在此,对原作者表示由衷的感谢。

Quartus II FPGA烧写教程

在Quartus II中使用JTAG模式固化程序到EPCS中的方法.[Quartus II]范例 流水灯 图1 流水灯范例 实现步骤 步骤1: 在Quartus II中,单击File->Convert Programming Files..。打开编程文件转换程序,如图2所示。

图2 编程文件转换程序界面 在此界面中。在Programming file type:标签后选择JTAG Indirect Configuration File (.jjc);在C onfiguration device:标签后选择你所使用的EPCS型号,此外我选择EPCS4。在Input file to conv ert方框中,单击Flash Leader,再单击Add Device..,如图3一样选择EP2C8(请根据自己的FPG A型号自行选择);单击SOF Data,再单击Add File..,选择Quartus II编译后的sof文件。配置完成界面如图4所示。

图3 Add Device

图4 配置完成界面 单击Generate,开始生成jjc文件。成功界面如图5。 图5 成功界面 关闭Convert Programming Files界面,进入下一步骤。

步骤2: 在Quartus II中,单击Tools->Programmer,进入下载界面,如图6所示。 图6 下载界面 在此界面,单击Hardware Setup,选择下载线缆。双击选择Usb-Blaster,如图7所示。

图7 选择Usb-Blaster 回到下载界面,单击led_water.sof,再单击Change File..,选择刚才转换的output_file.jjc。添加完成后,安装图8所示勾选选项,选择jjc文件。 图8 选择jjc文件 单击Start,开始下载。下载完成后,请点击复位键或者重启开发板,就会看见固化的程序了。 友情提示:EPCS擦写次数有限(请自行查询),请尽量采用JTAG模式下载sof文件测试程序。