数字电路常用芯片应用设计

74ls138

摘要:

74LS138 为3 -8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其中LS是指采用低功耗肖特基电路.

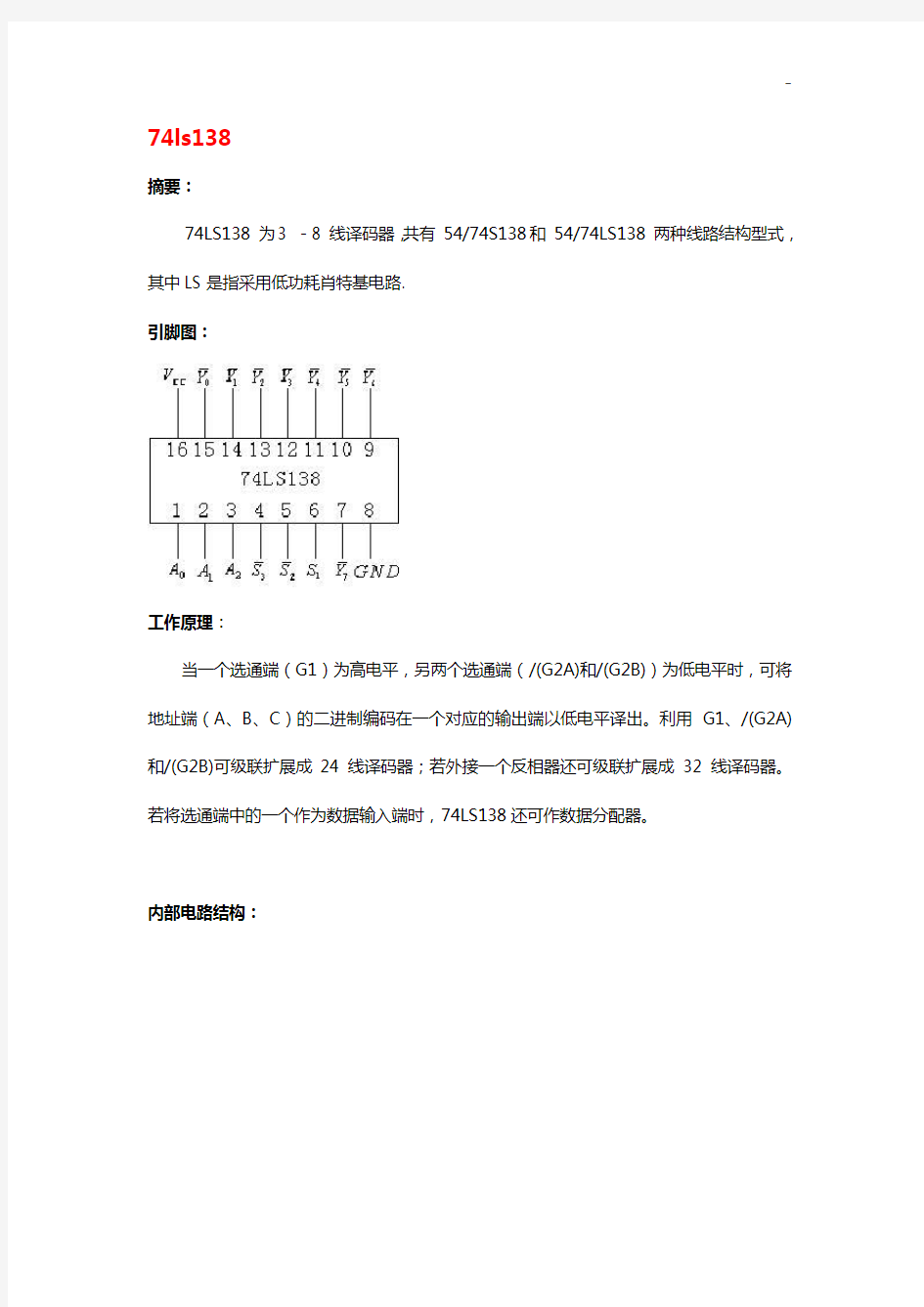

引脚图:

工作原理:

当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。

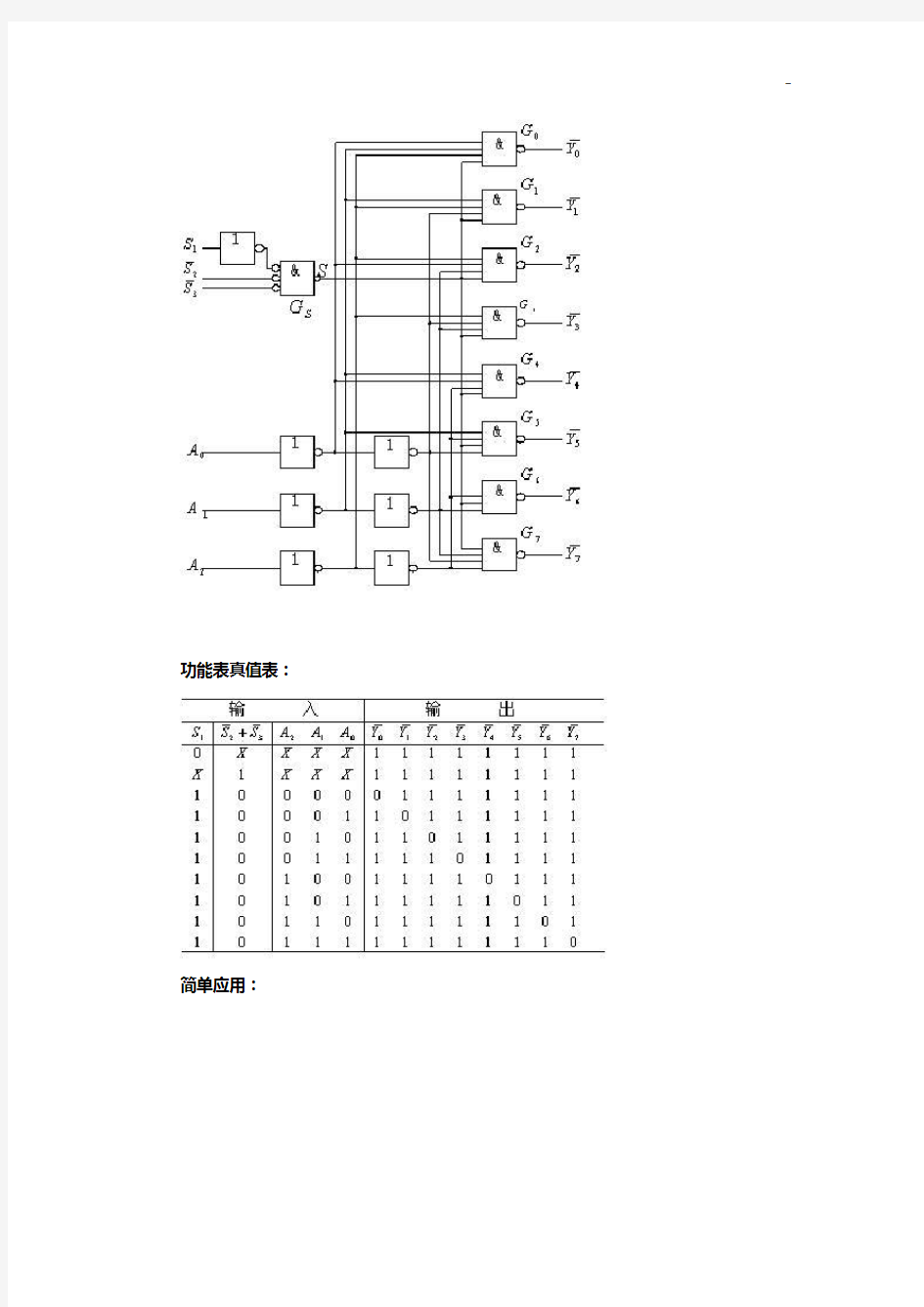

内部电路结构:

功能表真值表:

简单应用:

74ls139:

74LS139功能:

54/74LS139为2 线-4 线译码器,也可作数据分配器。其主要电特性的典型值如下:型号54LS139/74LS139 传递延迟时间22ns 功耗34mW

当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。若将选通端(G1)作为数据输入端时,139 还可作数据分配器。

74ls139引脚图:

引出端符号:

A、B:译码地址输入端

G1、G2 :选通端(低电平有效)

Y0~Y3:译码输出端(低电平有效74LS139内部逻辑图:

74LS139真值表:

74ls164:

164 为8 位移位寄存器,其主要电特性的典型值如下:54/74164 185mW 54/74LS164 80mW当清除端(CLEAR)为低电平时,输出端(QA -QH)均为低电平。串行数据输入端(A,B)可控制数据。当A、B任意一个为低电平,则禁止新数据输入,在时钟端(CLOCK)脉冲上升沿作用下Q0 为低电平。当A、B 有一个为高电平,则另一个就允许输入数据,并在CLOCK 上升沿作用下决定Q0 的状态。

引脚功能:

CLOCK :时钟输入端CLEAR:同步清除输入端(低电平有效)A,B :串行数据输入端QA-QH:输出端

(图1 74LS164封装图)

(图2 74LS164 内部逻辑图)

极限值电源电压7V 输入电压………5.5V

工作环境温度

54164…………-55~125℃

74164…………-0~70℃

储存温度……-65℃~150℃

(图3 真值表)

H-高电平L-低电平X-任意电平↑-低到高电平跳变QA0,QB0,QH0 -规定的稳态条件建立前的电平QAn,QGn -时钟最近的↑前的电平

(图4 时序图)

应用实例:

如图所示的电原理图,利用74LS164串行输入并行输出芯片作一个简单的电子钟,要求四个数码管显示时钟;其中LED1显示小时的十位,LED2显示小时的个位,LED3显示分钟的十位,LED4显示分钟的个位。

解:采用单片机的串行口输出字形码,用74LS164和74LS139作为扩展芯片。

74LS164的功能是将80C51串行通信口输出的串行数据译码并在其并口线上输出,从而驱动LED 数码管。74LS139是一个双2-4线译码器,它将单片机输出的地址信号译码后动态驱动相应的LED。因74LS139电流驱动能力较小,故用末级驱动三极管9013作为地址驱动。将4只LED的字段位都连在一起,它们的公共端则由74LS139分时选通,这样任何一

个时刻,都只有一位LED在点亮,也即动态扫描显示方式,其优点使用串行口进行LED通信程序编写相当简单,用户只需将需显示的数据直接送串口发送缓冲器,等待串行发送完毕标志位即可。

串行动态LED扫描电路

参考程序:

org 0100h

mov scon,#00h

main:mov r3,#00h

loop:mov r4,#0e8h

delay:acall display

dinz r4,delay

inc r3

cjne r3,#oah,loop

ajmp main display:clr p3.2

clr p3.3

acall disp

acall delay1

setb p3.3

acall disp

acall delay1

setb p3.3

clr p3.2

acall disp

acall delay1

setb p3.2

setb p3.3

acall disp

acall delay1

ret

disp: mov a,r3

mov dptr,#table

movc a,@a+dptr

mov buff,a

wait: jnb ti,wait

clr ti

ret

delay1:mov r6,#10h

loop1:mov r7,#38h

loop2:djnz r7,loop2

djnz r6,loop1

ret

table :db 0c0h,0f9h,oa4h,0b0h,99h

db 92h,82h,0f8h,80h,90h

end

74ls373:

简要说明:

74LS373是八D锁存器(3S,锁存允许输入有回环特性),常应用在地址锁存及输出口的扩展中。

SN74LS373, SN74LS374 常用的8d锁存器,常用作地址锁存和i/o输出. 可以用74hc373代换. 74LS373是低功耗肖特基TTL8D锁存器,74H373是高速CMOS器件,功能与74LS373相同,两者可以互换。

74LS373内有8个相同的D型(三态同相)锁存器,由两个控制端(11脚G或EN;1脚OUT、CONT、OE)控制。当OE接地时,若G为高电平,74LS373接收由PPU输出的地址信号;如果G为低电平,则将地址信号锁存。

工作原理:

74LS373的输出端O0~O7可直接与总线相连。当三态允许控制端OE为低电平时,O0~O7为正常逻辑状态,可用来驱动负载或总线。当OE为高电平时,O0~O7呈高阻态,即不驱动总线,也不为总线的负载,但锁存器内部的逻辑操作不受影响。当锁存允许端LE为高电平时,O随数据D而变。当LE为低电平时,O被锁存在已建立的数据电平。

74LS373引脚(管脚)图:

74LS373内部逻辑图:

74LS373真值表:

利用74LS373设计的一个超实用型抢答器:

利用74LS373设计的抢答器电路它由一片8D锁存器74LS373。8只组别按键开关S1-S8,8组别抢答有效的状态显示发光二极管L1-L8,一个复位按键FW等组成。

该8路竞赛抢答器,每组受控于一个抢答按键开关,高电平表示抢答有效。

设置主持人控制键FW用于控制整个系统清0和抢答有效开始控制的启动。每按下一次复位键FW时,使8D锁存器的控制端G为高电平,若组别按键开关S1~S8中任何一个都没按下,即对应8D锁存器的输入端D均为低电平,则此时8个输出端均为低电平,对应的发光二极管均不点亮,表示抢答者正在准备抢答状态。按下复位键FW时,8D锁存器的控制端G为高电平,若组别按键开关S1-S8中存在一个或几个处于按下状态,即与之对应的8D 锁存器的输入端D为高电平,此时与之对应的8D锁存器的输出端立即为高电平,对应的

发光二极管被点亮,表示抢答者违规了。只有每按下一次复位键FW,并在复位键FW抬起后,抢答才是有效的。

系统具有第一抢答信号鉴别和锁存功能。在主持人将系统复位并使抢答有效开始后,第一抢答者按下抢答按钮。对应的输入引脚接高电位1,8D锁存器的对应输出端立即为高电平1。二极管VD1-VD8组成了或门电路。使三极管VT1基极得到高电位而饱和导通使锁存器的G为低电平,将8D锁存器的输入信号锁存在了输出端,输入端的信号变化将不在影响输出端。对应点亮的发光二极管指示出第一抢答者的组别。在显示有效的组别的同时,也可同时采用蜂鸣器警示。

设计特点:8D锁存器74LS373的允许端G的控制信号不是周期固定的脉冲信号,而是将取自锁存器输出端的信号处理后得到的,保证电路结构最简洁、处理时间最快捷,同时减少了脉冲源存在可能带来的干扰,使电路性能更可靠。

74ls151:

简要说明:

8选1数据选择器(有选通输入端,互补输出)

151为互补输出的8选1数据选择器,共有54/74151、54/74S151、74LS151三种线路结构形式,其主要电特性的典型值如下:

数据选择端(ABC)按二进制译码,以从8个数据(D0-D7)中选取1个所需的数据。只有在选通端STROBE为低电平时才可选择数据。

151有互补输出端(Y、W),Y输出原码,W输出反码。

管脚图:

引出端符号:

A、B、C 选择输入端

D0-D7 数据输入端

STROBE 选通输入端(低电平有效)W 反码数据输出端

Y 数据输出端

功能表:

逻辑图:

极限值:

电源电压 ------------------------------------------7V

输入电压

54/74151、54/74S151---------------------------------5.5V 54/74LS151 ------------------------------------7V

CD4532:

图为CD4532编码芯片引脚仿真分布图(GND 为第8脚,VCC为16脚省略未画出)EI引脚为高电平的时候,D0~D7输入相应的电平信号时Q0~Q2可以输出不同的二进制数据,同时EO输出低电平,GS输出高电平,D0~D7与Q0~Q2的关系如下:

D0 为高电平Q2Q1Q0 输出000

D1 为高电平Q2Q1Q0 输出001

D2 为高电平Q2Q1Q0 输出010

D3 为高电平Q2Q1Q0 输出011

D4 为高电平Q2Q1Q0 输出100

D5 为高电平Q2Q1Q0 输出101

D6 为高电平Q2Q1Q0 输出110

D7 为高电平Q2Q1Q0 输出111。

以下电路可以印证这种状态,在D6按键按下输入高电平时,GS EO Q2 Q1 Q0分别输出10110。

图为测试CD4532引脚的状态

我们都非常熟悉7LS138这个芯片把3个引脚的输出状态扩展为8个引脚输出的状态。使用CD4532你就可以将8个输入引脚的状态转化为3个引脚的输入状态。在单片机项目开发过程中,如果单片机引脚作为接收外界信号不够用时,实用CD4532是非常实用的。

555:

555时基电路的特点:

555集成电路开始是作定时器应用的,所以叫做555定时器或555时基电路。但后来经过开发,它除了作定时延时控制外,还可用于调光、调温、调压、调速等多种控制及计量检测。此外,还可以组成脉冲振荡、单稳、双稳和脉冲调制电路,用于交流信号源、电源变换、频率变换、脉冲调制等。由于它工作可靠、使用方便、价格低廉,目前被广泛用于各种电子产品中,555集成电路内部有几十个元器件,有分压器、比较器、基本R-S触发器、放电管以及缓冲器等,电路比较复杂,是模拟电路和数字电路的混合体.

图为555集成电路内部结构图:

555集成电路是8脚封装,双列直插型,如图所示:

555时基集成电路各引脚功能描述:

脚①是公共地端为负极;

脚②为低触发端TR,低于1/3电源电压以下时即导通;

脚③是输出端V,电流可达2000mA;

脚④是强制复位端MR,不用可与电源正极相连或悬空;

脚⑤是用来调节比较器的基准电压,简称控制端VC,不用时可悬空,或通过0.01μF电容器接地;

脚⑥为高触发端TH,也称阈值端,高于2/3电源电压发上时即截止;