哈工大Verilog课程设计-状态机

可编程逻辑器件大作业(二)

2012年12月

一、题目

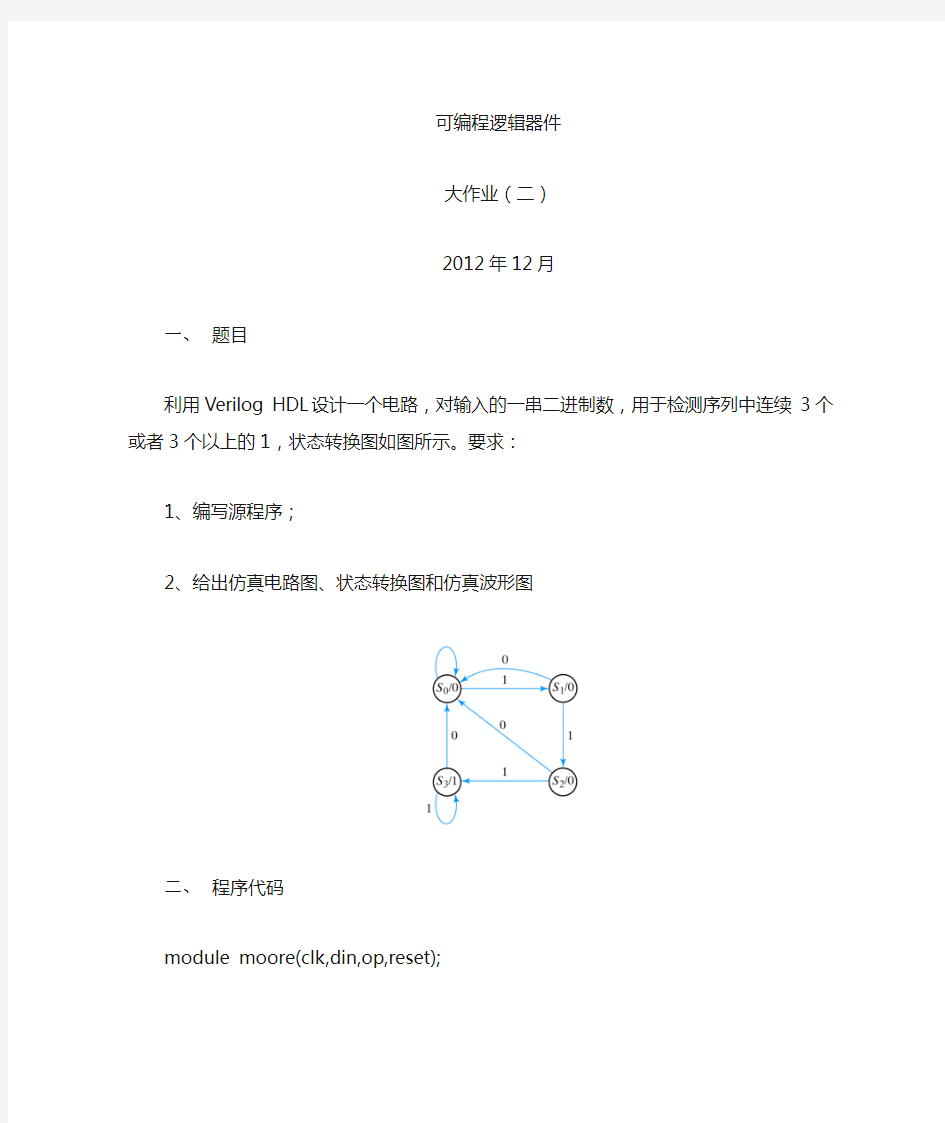

利用Verilog HDL设计一个电路,对输入的一串二进制数,用于检测序列中连续3个或者3个以上的1,状态转换图如图所示。要求:

1、编写源程序;

2、给出仿真电路图、状态转换图和仿真波形图

二、程序代码

module moore(clk,din,op,reset);

input clk,din,reset;

output op;

reg[1:0] current_state,next_state;

reg op;

parameter S0=2'b00,S1=2'b01,S2=2'b10,S3=2'b11;

always @ (posedge clk)

begin

if(!reset) current_state = S0;

else current_state <= next_state;

end

always @ (din or current_state)

begin

case( current_state )

S0: begin

op = 0;

if(din == 0)

next_state = S0;

else

next_state = S1;

end

S1: begin

op = 0;

if(din == 0)

next_state = S0;

else

next_state = S2;

end

S2: begin

op = 0;

if(din == 0)

next_state = S0;

else

next_state = S3;

end

S3: begin

op = 1;

if(din == 0)

next_state = S0;

else

next_state = S3;

end

default:begin

next_state = S0;

op = 0;

end

endcase

end

endmodule

三、仿真波形图

可知仿真波形图与状态转换图的相符四、仿真电路图

五、状态转换图

六、心得体会

通过设计过程对状态机的概念有了更深的理解,认识到了其在现实生活中的重要应用。更熟练地掌握了Verilog HDL硬件描述语言,提高了编程能力;对利用quartus软件设计过程有了大致的了解。