FPGA开发板实验手册2017

FPGA开发板实验指导书(2017)

第一章注意事项

工程未使用到的IO请设置为三态

所有程序请一定将未定义的引脚设为三态输入(As input tri-stated),一定不能将未使用的引脚设置为输出(As outputs driving ground),否则可能会造成核心板主芯片及存储芯片冲突损坏!或是造成其它意想不到的损坏!

如何设置未使用的引脚为三态?

答:Quartus--菜单Assignments--Device---Device and Pin Options---Unused Pins---Reserve all unused pins==改为As input tri-stated

每个例程下载前都养成习惯,先查下设置对不对,不对的话,改好,要重新编译一下。

如果程序下载进去,数码管、LED灯都乱亮了,那肯定是没设置好,请严格遵照上面的修改好,重新编译。

1.1JTAG及AS的插拔安全

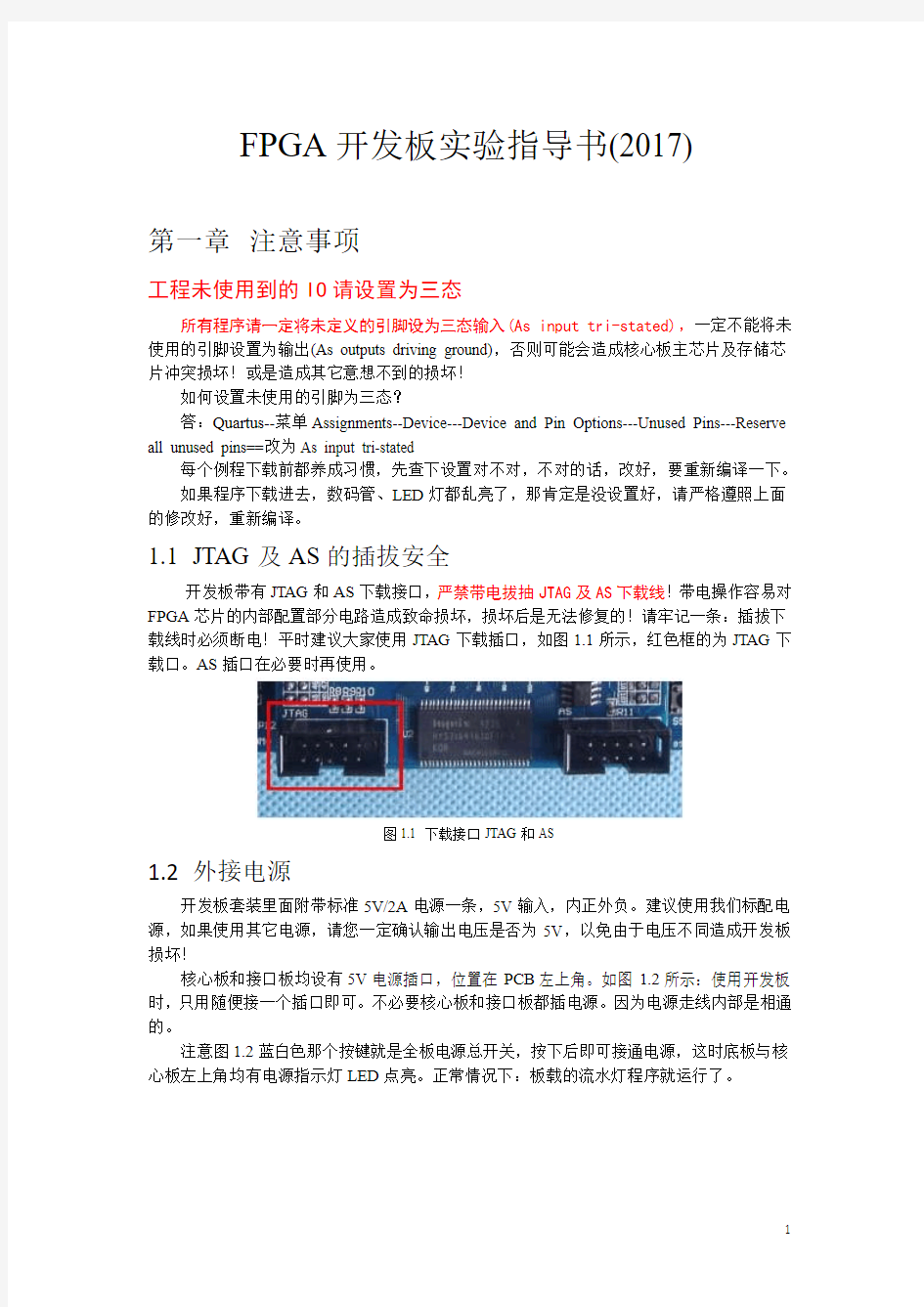

开发板带有JTAG和AS下载接口,严禁带电拔抽JTAG及AS下载线!带电操作容易对FPGA芯片的内部配置部分电路造成致命损坏,损坏后是无法修复的!请牢记一条:插拔下载线时必须断电!平时建议大家使用JTAG下载插口,如图1.1所示,红色框的为JTAG下载口。AS插口在必要时再使用。

图1.1 下载接口JTAG和AS

1.2外接电源

开发板套装里面附带标准5V/2A电源一条,5V输入,内正外负。建议使用我们标配电源,如果使用其它电源,请您一定确认输出电压是否为5V,以免由于电压不同造成开发板损坏!

核心板和接口板均设有5V电源插口,位置在PCB左上角。如图1.2所示:使用开发板时,只用随便接一个插口即可。不必要核心板和接口板都插电源。因为电源走线内部是相通的。

注意图1.2蓝白色那个按键就是全板电源总开关,按下后即可接通电源,这时底板与核心板左上角均有电源指示灯LED点亮。正常情况下:板载的流水灯程序就运行了。

图1.2 两个5V电源接口

第二章硬件资源描述

2.1 PFGA开发板硬件介绍

2.1.1 硬件资源图示

图2.1 开发板硬件资源图示

2.1.2 核心板资源

FPGA主芯片采用Altera公司高性价比FPGA:Cyclonell系列EP2C8Q208C8N;

采用64Mbit的SDRAM,足够胜任NIOSII设计;

板载50Mhz有源晶振,提供系统工作主时钟;

采用大功率LDO电源管理芯片1085-3.3V,最大支持3A的3.3V电压输出;

采用1117-1.2V稳压芯片,提供FPGA内核电压。

JTAG下载接口,对应下载的文件是SOF文件,速度快,JTAG将程序直接下载到FPGA 中,但是掉电程序丢失,平时学习推荐使用JTAG方式,最后固化程序的时候再通过AS方式将程序下载到配置芯片中即可;

AS下载接口,对应下载的是POF文件,速度相对较慢,需要重新上电并且拔掉下载线,才能工作,操作相对麻烦,不推荐学习的时候使用。

2.2 核心板电路分析

2.2.1FPGA主芯片

图2.2 EP2C5Q208C8N

EP2C5Q208和EP2C8Q208除了图 2.2的区别外,封装上是差不多的,开发板上EP2C8Q208的32、120脚是接VCCINT,36、119脚接GND。

图2.3 EP2C8Q208C8N的4个BANK图

2.2.2 存储器SDRAM电路

核心板选用的SDRAM芯片是HY57V641620FTP为64Mbit容量,地址为AO~A11,SDRAM的电源部分使用多个104电容进行了滤波处理,保证了芯片工作的电源稳定性。SDRAM部分原理图如图2.4所示:

图2.4 SDRAM原理图

2.2.3 电源电路

电源是保证整个开发系统正常工作最重要的部分。核心板外部输入5V电源,经过1085-3.3V稳压后输出3.3V,3.3V主要用于给FPGA所有IO口,核心板存储器电路、串行配置器件、复位电路和LED等供电。然后3.3V送给1117-1.2V稳压,提供FPGA的内部核工作,以及锁相环部分电源工作。D1为电源工作指示灯,在核心板的左上角,D0为1N5819,高速肖特基二极管,防止电源接反;同时各电源输入及输出部分设计了高质量钽电容用作电源滤波处理,提高系统电源稳定性。电源部分的原理图如图2.5所示。

图2.5 电源电路

2.2.4 时钟和复位电路

开发板采用50M有源贴片晶体为系统提供运行时钟,时钟部分电路电源经过π形滤波处理,工作更加稳定可靠。时钟和复位电路电路如图2.6所示。

图2.6 时钟和复位电路

2.3 接口板电路分析

2.3.1 按键及LED

接口板上具有8个独立按键和8个独立LED,电路如图2.7所示,对于按键电路部分,如果输出低电平,则表示按键按下。电路中电阻RP3,RP4均为保护作用,以防止FPGA芯片IO设为输出且为高电平时,在按键按下时直接对地短路。

图2.7 独立按键和LED 电路

2.3.2 拨码开关电路

4位拨码开关电路如图2.8所示:

图2.8 拨码开关电路

2.3.3 蜂鸣器电路

蜂鸣器使用PNP三极管驱动控制,如果在BEEP输入一定频率脉冲时,蜂鸣器会响,改变输入频率可以改变蜂鸣器的响声。

图2.9 蜂鸣器电路

2.3.4 七段数码管显示电路

七段数码管显示电路如图2.10所示,数码管是共阳极的,当位码驱动信号为0时,对应的数码管即操作;当段码驱动信号为0时,对应的段码点亮。位码由于电流较大,采用了三极管驱动。

图2.10 七段数码管显示电路

2.3.5RS232串口电路

RS232串口电路如图2.11示,由于是3.3V系统,所以使用了max3232进行RS232电平转换,同时,还有两个LED用于指示串口的工作状态。

图2.11 RS232串口电路

2.3.6VGA接口电路

VGA的接口电路如图2.12示,本电路采用的是电阻网络的方法来产生VGA所需要的不同电压信号,输入端共用了8个信号线,可以产生256色。

图2.12 VGA接口电路

2.3.7PS/2键盘、鼠标接口

PS左键盘鼠标接口电路原理如图2.13所示,使用5V电源供电,接口的数据线和时钟线均要接上拉电阻。

图2.13 PS/2键盘、鼠标接口电路

2.3.8 串行DA、AD电路

DAC电路使用一片串行接口的4通道8位DA转换器TLC5620,TLC5620具有半缓冲输出功能,可编程输出量程功能。它的每一路DA通道均需要参考电源,由REFA、REFB、REFC和REFD引脚输入。

串行A。电路采用单通道8位AD转换器TLC549C,转换所需的电压基准由REF+输入,电压基准定为2.5V,AD、DA电路如图2.14所示。电压基准电路由图2.15所示。

图2.14 DA、AD电路图

图2.15 电压基准电路

2.3.9 温度传感器电路

接口板上设有经典DS18B20温度传感器电路,原理图如图2.16所示,板载未焊DS18B20元件,为选配件。

图2.16 温度传感器电路

第三章例程说明及使用、下载方法

3.1 打开一个例程

打开一个已有的FPGA工程很简单:将工程注意请放在英文目录下,并且不要有空格。

打开QuartusII 11.0软件,在菜单File里选择“Open Project”

找到实例工程包,打开01 _ledl。

打开工程文件后,如下图所示:

3.2 用JTAG下载SOF文件

SOF文件是用JTAG口下载的,下载后掉电丢失的,主要用于程序调试过程,平时学习,使用这种模式。下载也很简单,点击工具栏上的编程选择,如下图红色框所示:

点击下图示的“H ardware Setup”,然后再选择下载硬件为:“USB blaster”。

关闭后,回到编程窗口,注意下图中各个红色框选择,

上图重点地方打了红框,并编号1,2,3,4,5,依次如下:

1.选择下载器硬件设备,前面已经设好;

2.选择下载模式JTAG,同时usb blaster下载线接在开发板的JTAG口上;

3.选择下载文件,点击Add File,把.sof的文件加进来;

4.Program configure打√;

5.点START下载;

点“start”下载,开发板上配置指示灯会闪一下,然后程序就开运行了,8个LED灯同时点亮了。

3.3 用AS下载配置EPCS芯片

AS下载是固化程序的,代码调好,想固化在电路里面时,就用这种模式,掉电后是不丢失的,睿智FPGA开发板出厂前都严格测试过,最后测试一步一般烧写一个流水灯程序

到EPCS芯片里,所以收到开发板上电后,会看流水灯效果。您可以烧写自己的程序,或擦除。

具体下载方法如下图所示:

上图重点地方打了红框,并编号1,2,3,4,5,依次如下:

1.选择下载器硬件设备;

2.选择下载模式AS,同时usb blaster下载线接在开发板的AS口上;

3.选择下载文件,点击Add File,把.pof的文件加进来;

4.Program configure打√;

5.点START下载。

3.4 新建工程操作说明

FPGA开发板底板上共有8个发光二极管LED1-LED8,完成这样一个任务:要间隔点亮这8个发光二极管。硬件原理图如下:

如果要点亮这些LED,只需要把与其相连接FPGA管脚输出低电平“0”就可以实现这个功能了。若利用连续赋值语句assign实现的话,写程序代码如下:

module led_light(led);

output[7:0] led;

assign led=8’b10101010;

endmodule

启动Quartus II中任何一项设计都是一项工程,在工程设计过程中,会产生许多仅扩展名不同的同名文件,放在同一个文件夹下,便于统一管理。所以,不同的设计项目最好放在不同的文件夹中。在本例中,建立文件夹D:\FPGA_study作为工作库,以便将设计过程中的相关文件存储于此。

启动Quartus II:

双击桌面上的Quartus II图标或单击开始按扭,在程序菜单中选择Quartus II,可以启动Quartus II。其初始界面如图所示:

在图中,在File标签下点击左键,可打开如下图所示的菜单,新建工程向导点击

File->New project wizard..新建工程项目led_light:

点击Next,进入下步,进入基本设置对话框;

在第一栏的输入框中输入工作库文件夹的地址。第二栏的输入框要求输入该工程的名称,一般可以用顶层文件的名称作为工程名称,这里我们写led_light。第三栏的输入框要求输入顶层设计文件实体的名称,实际上,您会发现,您在写第二栏时,第三栏已经由系统自动完成了,也是led_light。完成后,直接点击Finish。

因为还没有创建文件夹,Quartus II弹出一个对话框,询问是否新建所需文件夹,如下

图所示。

点“是”单击Yes,将会引出下图所示的窗口:

因为现在还没具体的设计verilog文件,我们先点[next];

下面选择所用的FPGA器件以及进行一些必要配置。开发板使用的是EP2C8Q208C8,

这时候在Available device列表已经列出了符介以上条件的器件,这时我们选择

EP2C8Q208C8,点OK确定。

点击File->New..在该项目下新建Verilog HDL 源程序文件led_light. v(或者直接点快捷图标,下图部分),输入源程序代码并保存。会弹出另存的对话框,我们发现保存的文件目录已经在led_light 下了,文件名也默认为led_light. v ,不用更改,保存即可。

点保存后,出现下图对话框:

然后点编译,过一会儿,会提示编译成功:

FPGA入门及Quartus II使用教程(内部资料)

FPGA入门及Quartus II使用教程FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列,它是在可编程阵列逻辑PAL(Programmable Array Logic)、门阵列逻辑GAL(Gate Array Logic)等可编程器件的基础上上进一步发展的产物。 可以这样讲,ASIC(Application Specific Integrated Circuit )内部的所有资源,是用积木堆积起来的小房子,可以是一个欧美风情的房子,还可以是一个北京四合院…….而FPGA内部就可以说是一个个小积木,也就是内部有大量的资源提供给我们,根据我们的需求进行内部的设计。并且可以通过软件仿真,我们可以事先验证设计的正确性。 第一章FPGA的基本开发流程 下面我们基于Altera 公司的QuantusII 软件来说明FPGA 的开发流程。 下图是一个典型的基于Quartus II的FPGA开发整体流程框图。

1、建立工程师每个开发过程的开始,Quartus II以工程为单位对设计过程进行管 理。 2、建立顶层图。可以这样理解,顶层图是一个容器,将整个工程的各个模块包 容在里边,编译的时候就将这些模块整合在一起。也可以理解为它是一个大元件,比如一个单片机,内部包含各个模块,编译的时候就是生成一个这样的大元件。 3、采用ALTERA公司提供的LPM功能模块。Quartus软件环境包含了大量的常 用功能模块,比如计数器、累加器、比较器等等。 4、自己建立模块。由于有些设计中现有的模块功能不能满足具体设计的要求, 那就只能自己设计。使用硬件描述语言,当然也可以用原理图的输入方法,可以独立的把它们当成一个工程来设计,并且生成一个模块符号(Symbol),类似于那些LPM功能模块。这里可以理解为,如果我们需求的滤波器,没有现成的合适的,那我们可以通过LC自己来搭建一个滤波器。 5、将顶层图的各个功能模块连线起来。这个过程类似电路图设计,把各个芯片 连起来,组成电路系统。 6、系统的功能原理图至此已经基本出炉了,下一步就是选择芯片字载体,分配 引脚,设置编译选项等等。 7、编译。这个过程类似软件开发里德编译,但是实际上这个过程比软件的编译 复杂的多,因为它最终要实现硬件里边的物理结构,包含了优化逻辑的组合,综合逻辑以及布线等步骤。 8、编译后会生成2个文件,一个是*.sof文件,一个是*.pof文件,前者可以通过 JTAG方式下载到FPGA内部,可以进行调试,但断电后数据丢失;后者通过AS或者PS方式下载到FPGA的配置芯片里边(EEPROM或者FLASH),重新上电后FPGA会通过配置将数据读出。 9、对于复杂的设计,工程编译好了,我们可以通过Quartus软件或者其他仿真 软件来对设计进行反复仿真和验证,直到满足要求。(主要是时序仿真)。 第二章基于Quartus II的实例 一、建立工程 首先,打开Quartus II软件。

金龙STM32F207开发板用户手册

1.概述 金龙STM32开发板用户手册芯片描述 -ARM32-bit Cortex-M3CPU -120MHz maximum frequency,150DMIPS/1.25DMIPS/MHz -Memory protection unit Memories -Up to1Mbyte of Flash memory -Up to128+4Kbytes of SRAM -Flexible static memory controller (supports Compact Flash,SRAM,PSRAM,NOR,NAND memories) -LCD parallel interface,8080/6800modes Clock,reset and supply management -1.8to3.6V application supply and I/Os -POR,PDR,PVD and BOR -4to25MHz crystal oscillator -Internal16MHz factory-trimmed RC -32kHz oscillator for RTC with calibration -Internal32kHz RC with calibration Low power -Sleep,Stop and Standby modes -VBAT supply for RTC, C32bit backup registers 20 optional4KB backup SRAM C12-bit,0.5us A/D converters 3 -up to24channels -up to6MSPS in triple interleaved mode C12-bit D/A converters 2 General-purpose DMA -16-stream DMA controller centralized FIFOs and burst support Up to17timers -Up to twelve16-bit and two32-bit timers Debug mode -Serial wire debug(SWD)&JTAG interfaces -Cortex-M3Embedded Trace Macrocell Up to140fast I/O ports with interrupt capability -51/82/114/140I/Os,all5V-tolerant Up to15communication interfaces C I2C interfaces(SMBus/PMBus) -Up to3 -Up to6USARTs(7.5Mbit/s,ISO7816interface,LIN,IrDA,modem control)

使用QUARTUS II做FPGA开发全流程,傻瓜式详细教程

My First FPGA Design Tutorial 101 Innovation Drive San Jose, CA 95134 (408) 544-7000 https://www.360docs.net/doc/2c13844870.html, TU-01002-1.0

Copyright ? 2007 Altera Corporation. All rights reserved. Altera, The Programmable Solutions Company, the stylized Altera logo, specific device des-ignations, and all other words and logos that are identified as trademarks and/or service marks are, unless noted otherwise, the trademarks and service marks of Altera Corporation in the U.S. and other countries. All other product or service names are the property of their respective holders. Al-tera products are protected under numerous U.S. and foreign patents and pending applications, maskwork rights, and copyrights. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the ap- plication or use of any information, product, or service described herein except as expressly agreed to in writing by Altera Corporation. Altera customers are advised to obtain the latest version of device specifications before relying on any published in- formation and before placing orders for products or services. Printed on recycled paper

路虎开发板用户手册

路虎NXP LPC1768开发板 用户手册

1、概述 路虎开发板采用 NXP公司 LPC1768 ARM是一款基于第二代 ARM Cortex-M3内核的微控制器,是为嵌入式系统应用而设计的高性能、低功耗的 32位微处理器,适用于仪器仪表、工业通讯、电机控制、灯光控制、报警系统等领域。路虎开发板板载 USB仿真器,支持 USB2.0 Device,具有双 CAN接口、RS-485接口等功能。路虎开发板配套丰富的例程和详尽的资料,方便用户快速进行项目开发。 功能特点: 强大的 MCU内核:Cortex-M3 ●处理速率高达 100MHz,并包含一个支持 8个区的存储器保护单元(MPU) ●内置嵌套向量中断控制器(NVIC) ● 512KB片上 Flash程序存储器,支持在系统编程(ISP)和在应用编程(IAP) ● 64KB SRAM可供高性能 CPU通过指令总线、系统总线、数据总线访问 ● AHB多层矩阵上具有 8通道的通用 DMA控制器(GPDMA) ●支持SSP、UART、AD/DA、定时器、GPIO等,并可用于存储器到存储器的传输 ●标准 JTAG测试/调试接口以及串行线调试和串行线跟踪端口选项 ●仿真跟踪模块支持实时跟踪 ● 4个低功率模式:睡眠、深度睡眠、掉电、深度掉电

●单个 3.3V电源(2.4V – 3.6V) ●工作温度:-40 °C - 85°C ●不可屏蔽中断(NMI)输入 ●片内集成上电复位电路 ●内置系统节拍定时器(SysTick),方便操作系统移植。 丰富的板载资源: 1、2路 RS232串行接口(使用直通串口线、其中一路串口支持 ISP下载程序) 2、2路 CAN总线通信接口(CAN收发器:SN65VHD230) 3、RS485通信接口(485收发器:SP3485) 4、RJ45-10/100M Ethernet网络接口(以太网 PHY:DP83848) 5、DA输出接口(可做 USB声卡实验、板载扬声器和扬声器输出驱动) 6、AD输入接口(可调电位器输入) 7、彩色液晶显示接口(可接 2.8寸或 3.2寸 TFT 320X240彩屏) 8、USB2.0接口,USB host及 USB Device接口。 9、SD/MMC卡(SPI)接口(提供带 FAT12、FAT16、FAT32文件系统)

FPGA开发入门教程

Altera FPGA开发入门教程

目录 目录 第一章 Altera FPGA 开发流程概述 (1) 1.1 你需要准备的 (1) 1.2 Altera FPGA 基本开发流程 (1) 第二章 QuartusII 软件安装教程 (4) 第三章 完成第一个FPGA设计 (20) 3.1 启动和建立QuartusII工程 (20) 3.2 编辑我们的设计文件 (27) 3.3 综合、布局布线 (30) 3.4 引脚约束 (34) 3.5 再次综合、布局布线 (37) 第四章 配置FPGA (38) 4.1 JTAG配置 (38) 4.2 JIC烧写 (42)

第一章Altera FPGA 开发流程概述 本章介绍Altera FPGA的最基本最简单的开发流程,目的在于让您更直观了解FPGA开发设计过程,最快上手FPGA开发,最快找到感觉:-) 1.1你需要准备的 ●兴趣 无需多言,兴趣是最好的老师! ●基本电路知识 学习FPGA最好能懂一些模拟电路和数字电路的基础知识,比如知道什么是高电平、低电平、逻辑门、触发器、电阻电容、发光二极管等。只需基本概念即可,不要求你是专家。当然,如果你有单片机之类的开发经验,那会更好! ●Verilog语言 是的,我们用Verilog进行FPGA设计。因为近年来,Verilog的使用率已经远远超过VHDL。你不需要太精通Verilog的语法,但是你需要用硬件的思维来学习和使用Verilog。在接下来的FPGA学习中,我们会反复强调这一点,以便带给你更深的体会。 ●硬件平台 纸上得来终觉浅。一块优秀而又易用的入门级FPGA开发板,会祝您一臂之力! 1.2A ltera FPGA 基本开发流程 图1- 1展示了Altera FPGA的基本开发流程。 1

RK3188开发板使用手册v1.0

RK3188开发板使用手册v1.0 一.安装RockUsb驱动 (2) 二.查看串口输出信息 (5) 三.烧写/下载固件 (8) 四.Kernel开发 (11) 五.Android开发 (12) 六.制作固件升级包update.img (13) 七.Recovery系统 (14) 八.Android系统USB操作 (17)

一.安装RockUsb驱动 Rockusb驱动放在RK3188\tools\RockusbDriver文件夹中 当你第一次使用RK3188SDK开发板时,接好USB线,按住“VOL+(RECOVERY)”按键上电,会要求安装驱动,按下面的图示步骤进行安装: 图1 选择“否,暂时不(T)”,点击“下一步”进入图2所示界面

图2 选择“从列表或指定位置安装(高级)”,点击下一步,进入图3界面 图3 选择你的驱动所存放的目录,点击“下一步”开始安装驱动,如图4所示

图4 完成以后可以在设备管理器看到设备已经安装成功 图5

二.查看串口输出信息 RK3188SDK开发板没有使用普通的串口,而是使用USB口来输出串口信息,你可以用一根特殊的USB调试线将开发板上的USB口连接到你的电脑中来查看串口信息。 1、在连接USB口之前,请先安装PL-2303USB转串口驱动 2、驱动安装完成后,再使用USB线将开发板上名为“UART0”的USB口连接到PC 中,然后你应该可以在设备管理器中看到一个新设备,如下所示: 3、使用串口工具查看开发板的输出信息。 在这边我以Windows自带的超级终端为例说明串口的配置: a、点击开始->所有程序->附件->通讯->超级终端 点击确定 b、选择正确的COM口:

FPGA学习指南

PS:笔者强烈建议诸位注册一个EETOP的账号,每天签到或者发贴、回贴就有积分了,里面的资源非常丰富,各种软件、资料都能找到。 一、入门首先要掌握HDL(HDL=verilog+VHDL)。 第一句话是:还没学数电的先学数电。然后你可以选择verilog或者VHDL,有C语言基础的,建议选择VHDL。因为verilog太像C了,很容易混淆,最后你会发现,你花了大量时间去区分这两种语言,而不是在学习如何使用它。当然,你思维能转得过来,也可以选verilog,毕竟在国内verilog用得比较多。 接下来,首先找本实例抄代码。抄代码的意义在于熟悉语法规则和编译器(这里的编译器是硅编译器又叫综合器,常用的编译器有:Quartus、ISE、Vivado、Design Compiler、Synopsys的VCS、iverilog、Lattice的Diamond、Microsemi/Actel的Libero、Synplify pro),然后再模仿着写,最后不看书也能写出来。编译完代码,就打开RTL图,看一下综合出来是什么样的电路。 HDL是硬件描述语言,突出硬件这一特点,所以要用数电的思维去思考HDL,而不是用C语言或者其它高级语言,如果不能理解这句话的,可以看《什么是硬件以及什么是软件》。在这一阶段,推荐的教材是《Verilog传奇》、《Verilog HDL高级数字设计》或者是《用于逻辑综合的VHDL》。不看书也能写出个三段式状态机就可以进入下一阶段了。 此外,你手上必须准备Verilog或者VHDL的官方文档,《verilog_IEEE官方标准手册-2005_IEEE_P1364》、《IEEE Standard VHDL Language_2008》,以便遇到一些语法问题的时候能查一下。 二、独立完成中小规模的数字电路设计。 现在,你可以设计一些数字电路了,像交通灯、电子琴、DDS等等,推荐的教材是《Verilog HDL应用程序设计实例精讲》。在这一阶段,你要做到的是:给你一个指标要求或者时序图,你能用HDL设计电路去实现它。这里你需要一块开发板,可以选Altera的cyclone IV系列,或者Xilinx的Spantan 6。还没掌握HDL之前千万不要买开发板,因为你买回来也没用。这里你没必要每次编译通过就下载代码,咱们用modelsim仿真(此外还有QuestaSim、NC verilog、Diamond的Active-HDL、VCS、Debussy/Verdi等仿真工具),如果仿真都不能通过那就不用下载了,肯定不行的。在这里先掌握简单的testbench就可以了。推荐的教材是《WRITING TESTBENCHES Functional Verification of HDL Models》。 三、掌握设计方法和设计原则。 你可能发现你综合出来的电路尽管没错,但有很多警告。这个时候,你得学会同步设计原则、优化电路,是速度优先还是面积优先,时钟树应该怎样设计,怎样同步两个异频时钟 《Altera FPGA/CPLD 等等。推荐的教材是《FPGA权威指南》、《IP核芯志-数字逻辑设计思想》、 设计》第二版的基础篇和高级篇两本。学会加快编译速度(增量式编译、LogicLock),静态时序分析(timequest),嵌入式逻辑分析仪(signaltap)就算是通关了。如果有不懂的地方可以暂时跳过,因为这部分还需要足量的实践,才能有较深刻的理解。 四、学会提高开发效率。 因为Quartus和ISE的编辑器功能太弱,影响了开发效率。所以建议使用Sublime text 编辑器中代码片段的功能,以减少重复性劳动。Modelsim也是常用的仿真工具,学会TCL/TK 以编写适合自己的DO文件,使得仿真变得自动化,推荐的教材是《TCL/TK入门经典》。你可能会手动备份代码,但是专业人士都是用版本控制器的,所以,为了提高工作效率,必须掌握GIT。文件比较器Beyond Compare也是个比较常用的工具。此外,你也可以使用System Verilog来替代testbench,这样效率会更高一些。如果你是做IC验证的,就必须掌

STM32F429开发板用户手册

STM32F429开发板用户手册 介绍 STM32F429(32F429IDISCOVERY)开发板可以帮助你去学习高性能STM32F4系列,并去开发你自己的应用。它包含了一个STM32F429ZIT6和一个嵌入ST-LINK/V2调试接口,2.4吋TFTLCD,64MbitsSDRAM,ST微机电陀螺仪,按键和USB OTG接口。

1约定 下表提供了一些约定惯例,目前的文档可能会用到。

2快速入门 STM32F429开发板是一种廉价且易于上手的开发套件,可以让使用者快速评估和开始STM32F4的开发工作。 在安装和使用产品以前,请接收评估产品许可协议。 2.1启动 跟随以下顺序来设置STM32F429开发板并开始开发应用: 1、确认跳线JP3和CN4被设置为“on”(开发模式) 2、连接STM32F429Discovery开发板CN1到PC,使用USB电缆(type A/mini-B),开发板上电。 3、屏幕上以下应用可用: 时钟日历和游戏 视频播放器和图片浏览器(播放浏览USB大容量存储器上的视频和图片)性能显示器(观察CPU负载和图形测试) 系统信息 4、演示软件,也像其他软件例程,运行你用来开发STM32F4。 5、从例程开始开发你自己的应用吧。 2.2系统要求 ?Windows PC(XP,Vista,7) ?USB type A to mini-B cable 2.3支持STM32F429开发板的开发工具 ?Altium:TASKING?VX-Toolset ?Atollic:TrueSTUDIO ?IAR:EWARM ?Keil?:MDK-ARM 2.4订购码 要订购STM32F429Discovery kit,请使用STM32F429I-DISCO订购码。 3特性 STM32F429Discovery开发板提供一下特性: ?S TM32F429ZIT6具有2MB闪存,256KB的RAM,LQFP144封装。 ?板载ST-LINK/V2,带有选择模式跳线,可以作为独立的ST-LINK/V2使用。 ?板电源:通过USB总线或外部3V或5V电源。 ?L3GD20:ST微机电动作传感器,3轴数字输出陀螺仪 ?TFT LCD,2.4寸,262K色RGB,240*230分辨率 ?SDRAM64Mbits(1Mbit x16-bit x4-bank),包含自动刷新模式和节能模式 ?六个LED: LD1(红绿):USB通信 LD2(红):3.3V电源 两个用户LED LD3(绿),LD4红 两个USBOTG LED:LD5(绿)VBUS和LD6OC(过流) ?两个按键(user and reset)

FPGA入门系列实验教程——LED跑马灯

艾米电子工作室FPGA入门系列实验教程 FPGA入门系列实验教程V1.0 前言 目前市场销售FPGA开发板的厂商很多,但大多只提供些简单的代码,没有详尽的文档和教程提供给初学者。经验表明,很多学生在学习FPGA设计技术的过程中,虽然刚开始学习热情很高,但真正坚持下来一直到“学会”的却寥寥无几,除了学生个人毅力的因素外,另外一个更主要的原因就是所选的开发板缺少配套的说明文档和手把手系列的入门教程。原本FPGA的学习门槛相对于单片机来说就高了不少,再加上缺少手把手系列教程资料,这就给初学者学习FPGA增添了更多的困难,很多初学者因为找不到入门的方法而渐渐失去了学习FPGA的兴趣和信心。 作者从接著到系统学习FPGA有两年多的时间了,学习FPGA的时间不长,期间因为没有专业的老师指导,自己摸索学习FPGA走了很多的弯路。有过问题迎刃而解的快乐,也有过苦苦寻求结果和答案的痛苦历程,回想起自己学习FPGA的历程,从开始的茫然,到后来的疯狂看书,购买开发板,在开发板上练习各种FPGA实例,到最后能独立完成项目,一路走来,感受颇多。发觉学习FPGA只要选择正确的方法是有捷径可走的,有很多人学习FPGA很长时间,因为没有找到正确的方法还是停留在入门阶段。 针对现状,作者从初学者的角度出发,结合作者学习FPGA的经验和亲身体会,遵循“宁可啰嗦一点,也不放过细节”的原则编写了详尽的实验教程作为艾米电子工作室开发套件的配套教程使用,主要面向FPGA初学者。FPGA的学习只有通过大量的操作与实践才能很好并快速的掌握。为此本实验教程从点亮LED 灯写起,深入浅出,以图文并茂的方式由易到难地列举了很多实例,采用手把手、Step by Step的方式让初学者以最快的方式掌握FPGA技术的开发流程以及Quartus II软件的使用,从而激起初学者学习FPGA的兴趣。在教程中作者采用“授人以渔”的方式,努力做到不仅讲述怎样进行试验,而且分析为什么这样做,以便初学者深刻理解并快速掌握FPGA的学习方法。 本实验教程的所有实例均在艾米电子工作室开发套件上验证通过,本教程虽然简单但编写也花费了作者大量的时间和精力,对于转载需要注明出处:https://www.360docs.net/doc/2c13844870.html,(艾米电子工作室作者:静水流深),并未经艾米电子工作室同意不得用于其他商业用途。 FPGA技术是不断发展变化的,要掌握FPGA技术的精髓,需要设计者在实践中不懈地摸索与积累,逐步提高自己的设计水平,本实验教程试图对初学者起到快速入门的作用。但由于作者学习FPGA时间不长,水平有限,错漏和不严谨之处在所难免,欢迎大家批评指正。并请您将阅读中发现的错误或建议发送到作者Email:zhoujie9220@https://www.360docs.net/doc/2c13844870.html,,以使本教程不断地完善。

STM32F0-DISCOVERY用户手册

1/30 文档ID 022910第1版2012年3 月 STM32F0DISCOVERY STM32F0探索套件 UM1525 前言 STM32F0DISCOVERY 是意法半导体STM32F0系列微控制器的探索套件,用于帮助你探索STM32F0 Cortex-M0微控制器的功能,轻松开发应用设计。STM32F0探索套件基于1颗STM32F051R8T6微控制器,组件包括ST-LINK/V2嵌入式调试工具、LED 指示灯、按键和1个原型板。 图1: STM32F0 探索套件 用户手册

2/30UM1525 文档ID 022910第1版 目录目录 1. 约定....................................................................................................................................52. 快速入门 (6) 2.1 开始使用........................................................................................................ 62.2 系统要求..........................................................................................................62.3 支持STM32F0探索套件的开发工具链 .......................................................62.4 订货代码. (6) 3. 特性....................................................................................................................................74. 硬件与原理图.. (8) 4.1 STM32F051R8T6 微控制器 ..........................................................................114.2 嵌入式ST-LINK/V2编程器/调试器 . (13) 4.2.1 使用ST-LINK/V2向板载STM32F0烧录和调试代码 ............................14 4.2.2 使用ST-LINK/V2向外部STM32应用板烧录和调试代码. (15) 4.3电源和电源选择............................................ 164.4 LED 指示灯 ...................................................................................................164.5 按键................................................................................................................164.6 JP2(Idd ) ﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍﹍ 16 4.7 OSC 时钟 -----------------------------------------------------------------------------174.7.1 OSC 时钟电源 .............................................................................................174.7.2 OSC 32kHz 时钟电源 17 4.8 焊桥.................................................................................................................184.9 扩展连接器.. (19) 5. 尺寸图..............................................................................................................................266. 原理图..............................................................................................................................277. 修改历史记录 (30)

AX301用户手册REV1.0

FPGA黑金开发平台 用户手册 AX301 REV 1.0 芯驿电子科技(上海)有限公司 黑金动力社区 https://www.360docs.net/doc/2c13844870.html,

目录 一、简介 (3) 二、电源 (6) 三、FPGA (7) 1)JTAG接口 (8) 2)配置芯片:M25P16 (8) 3)FPGA供电引脚 (9) 4)FPGA时钟输入引脚 (10) 四、50M有源晶振 (11) 五、SDRAM (11) 六、EEPROM 24LC04 (14) 七、PS/2接口 (15) 八、实时时钟DS1302 (16) 九、数码管 (17) 十、USB转串口 (19) 十一、VGA接口 (20) 十二、蜂鸣器 (23) 十三、SD卡槽 (24) 十四、扩展口 (25) 十五、LED (27) 十六、按键 (28) 十七、摄像头接口 (29) 十八、7寸TFT接口 (30)

FPGA黑金开发平台学生版2014款正式发布了,此款开发平台是在前两款学生版的基础上升级而来,型号为:AX301。虽然是一款入门级的FPGA开发平台,但是我们不管是在PCB设计上,还是在整个构造上都花费了很多的心思,真可谓“简约而不简单”。 一、简介 在这里,对这款FPGA开发平台进行简单的功能介绍。 此款开发板使用的是ALERA公司的CYCLONE IV系列FPGA,型号为EP4CE6F17C8,256个引脚的FBGA封装。根据ALTERA官方的数据,CYCLONE IV相对CYCLONE III来说,功耗减少25%,如下图所示 此款FPGA的资源如下图所示:

其中,主要的参数, 逻辑单元LE:6272; 乘法器LAB:392; RAM:276480bit; IO数量:179个; 内核电压:1.15V-1.25V(推荐1.2V); 工作温度:0-85℃ 图为整个系统的结构示意图:

Xilinx_FPGA中文教程

Spartan-3E Starter Kit Board User Guide

Chapter 1: Introduction and Overview Chapter 2: Switches, Buttons, and Knob Chapter 3: Clock Sources Chapter 4: FPGA Configuration Options Chapter 5: Character LCD Screen Chapter 6: VGA Display Port Chapter 7: RS-232 Serial Ports Chapter 8: PS/2 Mouse/Keyboard Port Chapter 9: Digital to Analog Converter (DAC) Chapter 10: Analog Capture Circuit Chapter 11: Intel StrataFlash Parallel NOR Flash PROM Chapter 12: SPI Serial Flash Chapter 13: DDR SDRAM Chapter 14: 10/100 Ethernet Physical Layer Interface Chapter 15: Expansion Connectors Chapter 16: XC2C64A CoolRunner-II CPLD Chapter 17: DS2432 1-Wire SHA-1 EEPROM

Chapter 1:Introduction and Overview Spartan-3E 入门实验板使设计人员能够即时利用Spartan-3E 系列的完整平台性能。 设备支持设备支持::Spartan-3E 、CoolRunner-II 关键特性关键特性::Xilinx 器件: Spartan-3E (50万门,XC3S500E-4FG320C), CoolRunner?-II (XC2C64A-5VQ44C)与Platform Flash (XCF04S-VO20C) 时钟时钟::50 MHz 晶体时钟振荡器 存储器: 128 Mbit 并行Flash, 16 Mbit SPI Flash, 64 MByte DDR SDRAM 连接器与接口: 以太网10/100 Phy, JTAG USB 下载,两个9管脚RS-232串行端口, PS/2类型鼠标/键盘端口, 带按钮的旋转编码器, 四个滑动开关,八个单独的LED 输出, 四个瞬时接触按钮, 100管脚hirose 扩展连接端口与三个6管脚扩展连接器 显示器: VGA 显示端口,16 字符- 2 线式 LCD 电源电源::Linear Technologies 电源供电,TPS75003三路电源管理IC 市场: 消费类, 电信/数据通信, 服务器, 存储器 应用: 可支持32位的RISC 处理器,可以采用Xilinx 的MicroBlaze 以及PicoBlaze 嵌入式开发系统;支持DDR 接口的应用;支持基于Ethernet 网络的应用;支持大容量I/O 扩展的应用。 Choose the Starter Kit Board for Your Needs Spartan-3E FPGA Features and Embedded Processing Functions Spartan3-E FPGA 入门实验板具有Spartan3-E FPGA 系列突出独特的特点和为嵌入式处理发展与应用提供了很大的方便。该板的特点如下: Spartan3-E 特有的特征:并行NOR Flash 配置;通过并行NOR Flash PROM 实现FPGA 的多种配置方式 嵌入式系统:MicroBlaze? 32-bit 嵌入RISC 处理器;PicoBlaze? 8-bit 嵌入控制器;DDR 存储器接口 Learning Xilinx FPGA, CPLD, and ISE Development Software Basics Spartan3-E FPGA 入门实验板比其他的入门实验板先进、复杂。它是学习FPGA 或CPLD 设计和怎样运用ISE 软件的基础。 Advanced Spartan-3 Generation Development Boards 入门实验板示范了MicroBlaze? 32-bit 嵌入式处理器和EDK 的基本运用。其更先进的地方

单片机开发板操作手册.

单片机开发板操作手册 一、概述 1,多功能单片机开发板,板载资源非常丰富,仅是包括的功能(芯片)有:步进电机驱动芯片ULN2003、 八路并行AD转换芯片ADC0804、 八路并行DA转换芯片DAC0832、 光电耦合(转换)芯片MOC3063、 八路锁存器芯片74HC573、 实时时钟芯片DS1302及备用电池、 IIC总线芯片A T24C02、 串行下载芯片MAX232CPE, 双向可控硅BTA06-600B、 4*4矩阵键盘、 4位独立按键、 DC5V SONGLE继电器、 5V蜂鸣器、 八位八段共阴数码管 5V稳压集成块78M05 八路发光二极管显示 另还有功能接口(标准配置没有芯片但留有接口,可直接连接使用):单总线温度传感器DS18B2接口、 红外线遥控接收头SM003接口8、 蓝屏超亮字符型液晶1602接口、 蓝屏超亮点阵图形带中文字库液晶12864接口、 2(4)相五线制小功率步进电机接口、 外接交流(7V-15V)电源接口 USB直接取电接口 镀金MCU晶振座 40DIP锁紧座 外接电源和5V稳压电源的外接扩展接口及MCU所有IO口扩展2,可以完成的单片机实验: 1、LED显示实验(点亮某一个指示灯、流水灯), 2、八位八段数码管显示实验(你可以任意显示段字符和数字以及开发板所有功能芯 片的显示), 3、液晶显示(1602液晶显示、12864点阵中文图形液晶显示、可以显示出开发板所 有功能芯片的操作), 4、继电器的操作 5、蜂鸣器的操作(你可以编写程序让它发出美妙动听的歌声) 6、可控硅的操作(胆大的朋友就利用这一独有的功能吧,你见过实验室温度实验箱 没有,它的驱动就是这样的;聪明的朋友就可以自己写个程序把把加热温度温 度恒定在(X±0.5)度的范围内了 7、步进电机的操作(这个是迈向自动化控制的第一步,现在的数控机床、机器人呀

FPGA入门实验教程 适合初学者

艾米电子工作室—让开发变得更简单https://www.360docs.net/doc/2c13844870.html, FPGA 入门系列实验教程——点亮LED 1. 实验任务 点亮发光二极管。通过这个实验,熟悉并掌握CPLD/FPGA 开发软件Quartus II 的使用方法和开发流程以及Verilog HDL的编程方法。 2. 实验环境 硬件实验环境为艾米电子工作室型号EP2C5T144 开发套件。 软件实验环境为Quartus II 8.1 开发软件。 3. 实验原理 FPGA 器件同单片机一样,为用户提供了许多灵活的独立的输入/输出I/O 口 (单元)。FPGA 每个I/O 口可以配置为输入、输出、双向、集电极开路和三态门等各种组态。作为输出口时,FPGA 的I/O 口可以吸收最大为24mA 的电流, 可以直接驱动发光二极管LED 等器件。图1. 1 为8 个发光二极管硬件原理图, 本原理图对应艾米电子工作室型号为EP2C5T144 FPGA 开发板及接口板。通过 原理图可知如果要点亮这八个LED,所以只要正确分配并锁定引脚后,在相应 的引脚上输出相应高电平“1”,就可实现点亮该发光二极管的功能。本工作室开 发板均采用输出“1”点亮LED 的模式,以后就不再另作说明。 图1. 1 发光二极管LED 硬件原理图 艾米电子工作室—让开发变得更简单https://www.360docs.net/doc/2c13844870.html, FPGA 入门系列实验教程——LED 闪烁灯 1. 实验任务 让实验板上的8 个LED 周期性的闪烁。通过这个实验,熟悉并掌握采用计数 与判断的方式来实现分频的Verilog HDL 的编程方法以及Quartus II 软件的使 用方法和开发流程。 2. 实验环境 硬件实验环境为艾米电子工作室型号EP2C8Q208 增强版开发套件。 软件实验环境为Quartus II 8.1 开发软件。 3. 实验原理 艾米电子工作室开发套件板载50MHz 的时钟源,假如我们直接把它输入到发光二极管LED,由于人眼的延迟性,我们将无法看到LED 闪烁,认为 它一直亮着。如果我们期望看到闪烁灯,就需要将时钟源的频率降低后再输

CPLD入门教程

目录 前言 (2) 第一章 MAX+plusII 软件和license的获得 (6) 第二章 MAX+plusII 软件的安装和license及驱动的设置 2.1 MAX+plusII 软件的安装 (7) 2.2 MAX+plusII 软件的license设置 (8) 2.3 MAX+plusII 软件的驱动设置 (12) 第三章用VHDL语言设计三人表决器 3.1打开MAX+plusII (22) 3.2新建VHDL文档 (23) 3.3输入设计文件 (24) 3.4保存文件 (25) 3.5检查编译 (27) 3.6创建symbol (32) 3.7波形防真 (33) 3.8下载验证 (40) 第四章用原理图输入的方式设计三人表决器 (47) 第五章用verilog-HDL语言设计三人表决器 (51)

前言 编写本入门教程(V1.2)的目点是为了让FPGA/CPLD初学者快速地入门。该教程的特点是通过基本概念讲解和实际的例子来让初学者迅速了解FPGA/CPLD。该教程是共享文件,可以复制、下载、转载,如果转载该文章请注明出处:https://www.360docs.net/doc/2c13844870.html,;该教程未经许可,不得用于商业用途。 FPGA/CPLD是电子设计领域中最具活力和发展前途的一项技术,它的影响丝毫不亚于70年代单片机的发明和使用。 FPGA/CPLD的基本知识: 1.什么是FPGA/CPLD FPGA (Field Programmable Gate Array)是现场可编程门阵列,CPLD是复杂的可编程逻辑器件(Complex Programmable Logic Device)的简称,不同厂家有不同的称呼,Xilinx把SRAM工艺,要外挂配置用的EEPROM的PLD叫FPGA,把Flash工艺(类似EEPROM工艺),乘积项结构的PLD叫CPLD; Altera把自己的PLD产品MAX系列(EEPROM工艺),FLEX/ACEX/APEX系列(SRAM工艺)都叫作CPLD,即复杂PLD(Complex PLD),由于FLEX/ACEX/APEX系列也是SRAM工艺,要外挂配置用的EPROM,用法和Xilinx的FPGA一样,所以很多人把Altera的FELX/ACEX/APEX系列产品也叫做FPGA. 但由于FPGA和CPLD功能基本相同,只是工艺和实现形式不同,所以初学者可以不要详细区分,我们可以统称为FPGA/CPLD。 2.FPGA/CPLD的用途:

Xilinx 开发板用户手册

SP605 Hardware User Guide UG526 (v1.6) July 18, 2011

? Copyright 2009–2011 Xilinx, Inc. Xilinx, the Xilinx logo, Artix, ISE, Kintex, Spartan, Virtex, Zynq, and other designated brands included herein are trademarks of Xilinx in the United States and other countries. All other trademarks are the property of their respective owners. DISCLAIMER The information disclosed to you hereunder (the “Materials”) is provided solely for the selection and use of Xilinx products. To the maximum extent permitted by applicable law: (1) Materials are made available "AS IS" and with all faults, Xilinx hereby DISCLAIMS ALL WARRANTIES AND CONDITIONS, EXPRESS, IMPLIED, OR ST ATUTORY, INCLUDING BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON-INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and (2) Xilinx shall not be liable (whether in contract or tort, including negligence, or under any other theory of liability) for any loss or damage of any kind or nature related to, arising under, or in connection with, the Materials (including your use of the Materials), including for any direct, indirect, special, incidental, or consequential loss or damage (including loss of data, profits, goodwill, or any type of loss or damage suffered as a result of any action brought by a third party) even if such damage or loss was reasonably foreseeable or Xilinx had been advised of the possibility of the same. Xilinx assumes no obligation to correct any errors contained in the Materials, or to advise you of any corrections or update. Y ou may not reproduce, modify, distribute, or publicly display the Materials without prior written consent. Certain products are subject to the terms and conditions of the Limited Warranties which can be viewed at https://www.360docs.net/doc/2c13844870.html,/warranty.htm; IP cores may be subject to warranty and support terms contained in a license issued to you by Xilinx. Xilinx products are not designed or intended to be fail-safe or for use in any application requiring fail-safe performance; you assume sole risk and liability for use of Xilinx products in Critical Applications: https://www.360docs.net/doc/2c13844870.html,/warranty.htm#critapps. Revision History The following table shows the revision history for this document. Date Version Revision 10/07/09 1.0Initial Xilinx release. 11/09/09 1.1?Updated Figure1-17 and Figure1-23. ?Changed speed grade from -2 to -3. ?Miscellaneous typographical edits. 02/01/10 1.1.1Minor typographical edits to Table1-24 and Table1-25. 05/18/10 1.2Updated Figure1-2. Added Note 6 to Table1-11. Updated board connections for SFP_TX_DISABLE in Table1-12. Added note about FMC LPC J63 connector in 18. VITA 57.1 FMC LPC Connector. Updated U1 FPGA Pin column for FMC_LA00_CC_P/N in Table1-28. Updated description of PMBus Pod and TI Fusion Digital Power Software GUI in Onboard Power Regulation. Updated Appendix B, VITA 57.1 FMC LPC Connector Pinout, and Appendix C, SP605 Master UCF. 06/16/10 1.3Updated 2. 128 MB DDR3 Component Memory. Added note 1 to Table1-30. 09/24/10 1.4Updated description of Fusion Digital Power Software in Onboard Power Regulation. 02/16/11 1.5Revised oscillator manufacturer information from Epson to SiTime in Table1-1. Revised oscillator manufacturer information from Epson to SiTime on page page23. Deleted note on page 44 referring to J55: “Note: This header is not installed on the SP605 as built.” Revised values for R50 and R216 in Figure1-12. Revised oscillator manufacturer information from Epson to SiTime on page page69. 07/18/11 1.6Corrected “jitter” to “stability” in section Oscillator (Differential), page23. Revised the feature and notes descriptions for reference numbers 6 and 12 in Table1-1, page10. Revised FPGA pin numbers for ZIO and RZQ in Table1-4, page14. Added Table1-29, page52, Table1-31, page55, and table notes in Table1-30. SP605 Hardware User Guide https://www.360docs.net/doc/2c13844870.html, UG526 (v1.6) July 18, 2011