循环冗余(CRC)模块设计说明

附表1:

大学学生实验报告

开课学院及实验室:物理与电子工程学院-电子楼317室2016年 5 月 26 日

.学习帮手.

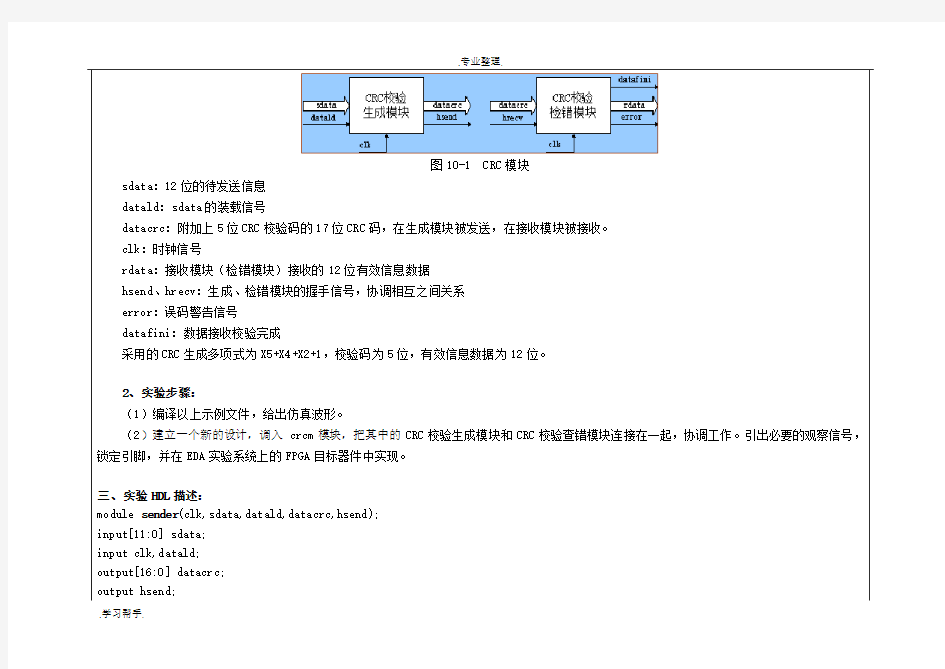

.学习帮手. 图10-1 CRC模块

sdata:12位的待发送信息

datald:sdata的装载信号

datacrc:附加上5位CRC校验码的17位CRC码,在生成模块被发送,在接收模块被接收。

clk:时钟信号

rdata:接收模块(检错模块)接收的12位有效信息数据

hsend、hrecv:生成、检错模块的握手信号,协调相互之间关系

error:误码警告信号

datafini:数据接收校验完成

采用的CRC生成多项式为X5+X4+X2+1,校验码为5位,有效信息数据为12位。

2、实验步骤:

(1)编译以上示例文件,给出仿真波形。

(2)建立一个新的设计,调入crcm模块,把其中的CRC校验生成模块和CRC校验查错模块连接在一起,协调工作。引出必要的观察信号,锁定引脚,并在EDA实验系统上的FPGA目标器件中实现。

三、实验HDL描述:

module sender(clk,sdata,datald,datacrc,hsend);

input[11:0] sdata;

input clk,datald;

output[16:0] datacrc;

output hsend;

.学习帮手.

.学习帮手.

.学习帮手.

.学习帮手.

相关主题