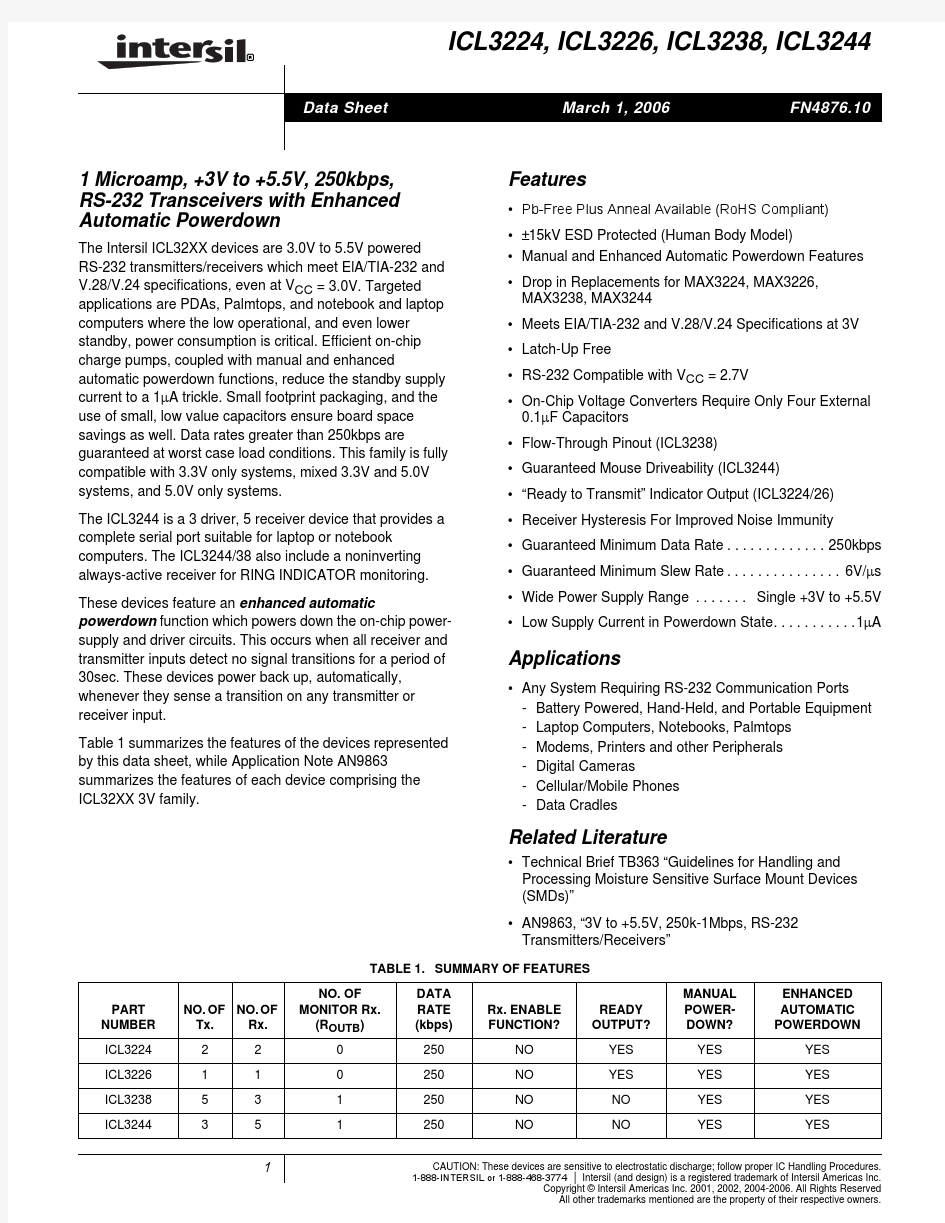

ICL3238 RS232电平转TTL电平转换芯片datesheet

详解电平种类与电平转换

详解电平种类与电平转换 1. 常用的电平转换方案 (1) 晶体管+上拉电阻法 就是一个双极型三极管或 MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 (2) OC/OD 器件+上拉电阻法 跟 1) 类似。适用于器件输出刚好为 OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与 5V TTL 电平兼容的 5V CMOS 器件都可以用作3.3V→5V电平转换。 ——这是由于 3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而 CMOS 的输出电平总是接近电源电平的。 廉价的选择如 74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列 (那个字母 T 就表 示 TTL 兼容)。 (4) 超限输入降压法(5V→3.3V,3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制 (改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其 datasheets 明确注明"输入电压范围为0~5.5V",如果采 用 3.3V 供电,就可以实现5V→3.3V电平转换。 (5) 专用电平转换芯片 最著名的就是 164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的 (俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。 (6) 电阻分压法 最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。 (7) 限流电阻法 如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如 74HC 系列为 20mA),仍然是安全的。 (8) 无为而无不为法 只要掌握了电平兼容的规律。某些场合,根本就不需要特别的转换。例如,电路中用到了某种 5V 逻辑器件,其输入是 3.3V 电平,只要在选择器件时选择输入为 TTL 兼容的,就不需要任何转换,这相当于隐含适用了方法3)。

常见TTL电平转换电路

常见TTL电平转换电路 ------设计参考 1.二、三级管组成的TTL/CMOS电平转换电路,优点是价格非常低,缺点是要求使用在 信号频率较低的条件下。 建议上拉电阻为10K时,可使用在信号频率为几百Khz以下的环境中,曾经在960Khz 的串口通信中做过测试。上拉电阻越小,速率越高,但是电路的功耗也越高,在低功耗要求高的电路中需要慎重考虑。在选择二、三极管时,尽量选用结电容小,开关速率高的。 A ) 图1所示电路,仅能使用在输入信号电平大于输出信号电平的转换上,例如3.3V转2.8V。二极管选用高速肖特基二极管,并且V F尽量小,例如RB521S。 图1 B ) 图2电路,仅能使用在输入信号电平大于输出信号电平的转换上,例如3.3V转2.8V,否则PNP管可能关不断。如果对输出低电平电压幅度有较严格的要求,PNP管则选用饱和压降小些的管子。PNP管也不如NPN的通用。VCC_OUT是输出信号的电源电压。 图2

C ) 图3是NPN管组成的转换电路,对输入和输出电平的谁高谁低没有要求,适用性很好。其中VCC_IN是输入信号的电源电压,VCC_OUT是输出信号的电源电压。转换后输出的低电平VOL=Vin_Lmax+Vsat,Vin_Lmax为输入信号低电平的最高幅值,Vsat为NPN管的饱和压降,如果对输出低电平电压幅度有较严格的要求,NPN管则选用饱和压降小些的管子,以满足一般电路中VOL<0.8V的要求。 图3 2.OC/OD输出的反相器组成的电平转换电路。 图4,由2级反相器组成,反相器必须是OC/OD输出的。反相器的电源与输入信号的电平相同或者相匹配,最后的输出电平由上拉电阻上拉到输出信号的目标电平上。上拉电阻的取值直接影响功耗和可适用的信号频率。 图4

电平转换方法

5V-3.3V电平转换方法 在实际电路设计中,一个电路中会有不同的电平信号。 方案一:使用光耦进行电平转换 首先要根据要处理的信号的频率来选择合适的光耦。高频(20K~1MHz)可以用高速带放大整形的光藕,如6N137/TLP113/TLP2630/4N25等。如果是20KHz以下可用TLP521。然后搭建转换电路。如将3.3V信号转换为5V信号。电路如下图: CP是3.3V的高速信号,通过高速光耦6N137转换成5V信号。如果CP接入的是5V 的信号VCC=3.3V,则该电路是将5V信号转换成3.3V信号。优点:电路搭建简单,可以调制出良好的波形,另外光耦还有隔离作用。缺点:对输入信号的频率有一定的限制。 方案二:使用三极管搭建转换电路 三极管的开关频率很高,一般都是几百兆赫兹,但是与方案一相比,电路搭建相对麻烦,而且输出的波形也没有方案一的好。 电路如下图: 其中C1为加速电容,R1为基极限流电阻,R2为集电极上拉电阻,R3将输入端下拉到地,保证在没有输入的情况下,输出端能稳定输出高电平。同时在三极管截止时给基区过量的电荷提供泄放回路缩短三极管的退饱和时间。 优点:开关频率高,在不要求隔离,考虑性价比的情况下,此电路是很好的选择。 缺点:输出波形不是很良好。 方案三:电阻分压 这里分析TTL电平和COMS电平的转换。首先看一下TTL电平和CMOS电平的区别。 TTL电平:输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2。最小输入高电平>=2.0V,输入低电平<=0.8,噪声容限是0.4V。 CMOS电平:1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且有很宽的噪声容限。 下面的电路是将5V的TTL电平转换成3V的TTL电平

串口电平转换芯片数据手册SP3222_3232E

DESCRIPTION s Meets true EIA/TIA-232-F Standards from a +3.0V to +5.5V power supply s 235KBps Transmission Rate Under Load s 1μA Low-Power Shutdown with Receivers Active (SP3222E ) s Interoperable with RS-232 down to +2.7V power source s Enhanced ESD Specifications: ±15kV Human Body Model ±15kV IEC1000-4-2 Air Discharge ±8kV IEC1000-4-2 Contact Discharge The SP3222E/3232E series is an RS-232 transceiver solution intended for portable or hand-held applications such as notebook or palmtop computers. The SP3222E/3232E series has a high-efficiency, charge-pump power supply that requires only 0.1μF capacitors in 3.3V operation. This charge pump allows the SP3222E/3232E series to deliver true RS-232performance from a single power supply ranging from +3.3V to +5.0V. The SP3222E/3232E are 2-driver/2-receiver devices. This series is ideal for portable or hand-held applications such as notebook or palmtop computers. The ESD tolerance of the SP3222E/3232E devices are over ±15kV for both Human Body Model and IEC1000-4-2 Air discharge test methods. The SP3222E device has a low-power shutdown mode where the devices' driver outputs and charge pumps are disabled. During shutdown, the supply current falls to less than 1μA. SELECTION TABLE L E D O M s e i l p p u S r e w o P 232-S R s r D e v i r 232-S R s r e v i e c e R l a n r e t x E s t n e n o p m o C n w o d t u h S L T T a S -3e t t f o .o N s n i P 2223P S V 5.5+o t V 0.3+224s e Y s e Y 02,812 323P S V 5.5+o t V 0.3+2 2 4 o N o N 6 1

在各个领域中常用芯片汇总(2)(精)

在各个领域中常用芯片汇总 1. 音频pcm编码DA转换芯片cirrus logic的cs4344,cs4334,4334是老封装,据说已经停产,4344封装比较小,非常好用。还有菲利谱的8211等。 2. 音频放大芯片4558,833,此二芯片都是双运放。为什么不用324等运放个人觉得应该是对音频的频率响应比较好。 3. 74HC244和245,由于244是单向a=b的所以只是单向驱动。而245是用于数据总线等双向驱动选择。同时245的封装走线非常适合数据总线,它按照顺序d7-d0。 4. 373和374,地址锁存器,一个电平触发,一个沿触发。373用在单片机p0地址锁存,当然是扩展外部ram的时候用到62256。374有时候也用在锁数码管内容显示。 5. max232和max202,有些为了节约成本就用max202,主要是驱动能力的限制。 6. 网络接口变压器。需要注意差分信号的等长和尽量短的规则。 7. amd29系列的flash,有bottom型和top型,主要区别是loader区域设置在哪里?bottom型的在开始地址空间,top型号的在末尾地址空间,我感觉有点反,但实际就是这么命名的。 8. 164,它是一个串并转换芯片,可以把串行信号变为并行信号,控制数码管显示可以用到。 9. sdram,ddrram,在设计时候通常会在数据地址总线上加22,33的电阻,据说是为了阻抗匹配,对于这点我理论基础学到过,但实际上没什么深刻理解。 10. 网卡控制芯片ax88796,rtl8019as,dm9000ae当然这些都是用在isa总线上的。 11. 24位AD:CS5532,LPC2413效果还可以 12. 仪表运放:ITL114,不过据说功耗有点大 13. 音频功放:一般用LM368 14. 音量控制IC. PT2257/9. 15. PCM双向解/编码ADC/DAC CW6691.

5V到3V3的电平转换-串口通信

5V到3V3的电平转换-串口通信 一、电平转换电路 下面来分析一下电路的设计思路: https://www.360docs.net/doc/2d9954159.html,/BLOG_ARTICLE_244240.HTM 首先声明一下:这个电路是从3V3的角度考虑的! 1、接收通道 我们首先来明确一下数据流向(其实就是电平驱动方向),接收通道是由5V方驱动的(Source),3V3方只是取电平(Sink),因此TXD5V作为此通道的输入方,RXD3V3作为通道的输出方。 我们知道,三极管(开关型)集电极输出驱动能力不错,我们就设计为集电极输出;但是,只有一个三极管是不行的,因为集电极输出的时候,基极电平和集电极逻辑是相反的;那么,加一个反相器?没必要,那是另外一种电平转换的方法了,我们只需要再使用一个三极管,基极接前级输出就可以了。这样,逻辑转换就完成了,当输入低电平时,Q1截止,集电极输出高电平,Q2导通,集电极输出低电平。同理,高电平分析是一样的。 逻辑转换完成了,那么就是电平的问题了。这很好解决,输入方为5V逻辑,那么就给它一个VCC5,3V3逻辑高电平需要一个3V3,那么就给一个VCC3V3;OK! 2、发送通道 分析完接收通道,发送通道的原理其实也是一样的,就不详细介绍了。 3、结论 其实如果稍微熟悉电子电路知识的人看来,这个电路实在太简单,正因为如此,我才要强调,基础很重要!否则,一个系统的设计会在这些小地方卡住。 二、电平问题: 单片机手册————电气特性 常用逻辑电平:12V,5V,3.3V; 1.TTL电平: 输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。

常用的电平转换方案

常用的电平转换方案 TTL、CMOS、ECL等电路的高低电平阀值不同,他们之间逻辑连接需要电平转换;还有,就是接口与接口之间的,如RS232与485之间,USB与串口之间等等,由于这些接口协议里面定义的电平不同,所以也需要电平转换。 1. 常用的电平转换方案 (1) 晶体管+上拉电阻法 就是一个双极型三极管或MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 图1. 电阻-二极管拓扑,是在同一根信号线上实现双向转换的可选技术之一

图2. 分立/数字晶体管是实现双向转换的另外一种选择 (数据入和数据出也被称为主入从出(MISO)和主出从入(MOSI)。SPI能够使用超过20Mbp的时钟信号,使用CMOS推挽逻辑。由于SPI是单向的,没有必要在同一根信号线上实现双向转换。这使电平转换变得简单一些,因为 可以采用电阻与二极管(图1)或分立/数字晶体管(图2)等简单方案。I2C、SMBusTM和1-Wire 接口为双向、漏极开路拓?扑。I2C有3个速度范围:≤ 100kbps的标准模式,≤ 400kbps的快速模式,≤ 3.4Mbps的高速模式。双向总线的电平转换更加困难,因为必须在同一根数据线上进行双向转换。基于电阻-二极管或集电极/漏极开路的单级晶体管转换器的简单拓扑由于固有的单向性,无法满足要求。 ) (2) OC/OD 器件+上拉电阻法 跟1) 类似。适用于器件输出刚好为OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与5V TTL 电平兼容的5V CMOS 器件都可以用作 3.3V→5V 电平转换。 ——这是由于3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而CMOS 的输出电平总是接近电源电平的。 廉价的选择如74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列(那个字母T 就表示TTL 兼容)。 (4) 超限输入降压法(5V→3.3V, 3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制(改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其datasheets 明确注明"输入电压范围为0~5.5V",如果采用 3.3V 供电,就可以实现5V→3.3V 电平转换。 (5) 专用电平转换芯片 最著名的就是164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的(俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。

CMOS电平转换电路详解

CMOS电平转换电路详解 COMS集成电路是互补对称金属氧化物半导体(Compiementary symmetry metal oxide semicoductor)集成电路的英文缩写,电路的许多基本逻辑单元都是用增强型PMOS晶体管和增强型NMOS管按照互补对称形式连接的,静态功耗很小。 COMS电路的供电电压VDD范围比较广在+5~+15V均能正常工作,电压波动允许10,当输出电压高于VDD-0.5V时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0。CMOS电路输出高电平约为0.9Vcc,而输出低电平约为0.1Vcc.当输入电压高于VDD-1.5V时为逻辑1,输入电压低于VSS+1.5V(VSS为数字地)为逻辑0。 TTL电平信号被利用的最多是因为通常数据表示采用二进制规定,+5V等价于逻辑1,0V 等价于逻辑0,这被称做TTL(晶体管-晶体管逻辑电平)信号系统,这是计算机处理器控制的设备内部各部分之间通信的标准技术。 标准TTL输入高电平最小2V,输出高电平最小2.4V,典型值3.4V,输入低电平最大0.8V,输出低电平最大0.4V,典型值0.2V(输入H》2V,输入L《0.8V;输出H 》2.4V(3.4V),输出L《0.4V(0.2V)。 CMOS电平是数字信号还是模拟信号?CMOS电平是数字信号,COMS电路的供电电压VDD范围比较广在+5--+15V均能正常工作,电压波动允许10,当输出电压高于VDD-0.5V 时为逻辑1,输出电压低于VSS+0.5V(VSS为数字地)为逻辑0,一般数字信号才是0和1 。 cmos电平转换电路1、TTL电路和CMOS电路的逻辑电平 VOH:逻辑电平1 的输出电压 VOL:逻辑电平0 的输出电压 VIH :逻辑电平1 的输入电压 VIH :逻辑电平0 的输入电压 TTL电路临界值:

电平转换资料

74AVC1T145 1、概述 74AVC1T145是一款具有双向电压转换和3态输出的单位双电源收发器。它的功能端口有1位输入输出端口(A和B),一个方向控制输入(DIR)和双电源引脚(V CC(A)和V CC(B))。同时V CC(A)和V CC(B)可以输入介于0.8 V 到3.6 V的电压实现器件在任意低电压节点之间的转换(0.8 V, 1.2 V, 1.5 V, 1.8 V, 2.5 V 和3.3 V)。引脚A和DIR由V CC(A)供电,引脚B由V CC(B)供电。在DIR上的高电平允许从A传输到B,也允许在DIR上的低电平从B传输到A。 该器件明确规定在局部省电模式时使用I OFF。I OFF将使输出失能,防止在电源关闭时破坏性的回路电流通过器件。当VCC(A)或VCC(B)处于地电平电压时处于挂起模式,同时A和B 将处于高阻态。 2、功能与优点 ?电源电压范围宽: ◆ ◆ ?噪声抑制能力强 ?符合JEDEC标准: ◆-12 (0.8 V to 1.3 V) ◆-11 (0.9 V to 1.65 V) ◆-7 (1.2 V to 1.95 V) ◆-5 (1.8 V to 2.7 V) ◆-B (2.7 V to 3.6 V) ?静电保护: ◆HBM JESD22-A114E类3 b超过8000 V ◆MM JESD22-A115-A超过200 V ◆CDM JESD22-C101C超过1000 V ?最大数据速率: ◆500 Mbit / s(1.8 V至3.3 V的转换) ◆320 Mbit / s(< 1.8 V至3.3 V转换) ◆320 Mbit / s(转换为2.5 V和2.5 V) ◆280 Mbit / s(转换到1.5 V) ◆240 Mbit / s(转换到1.2 V) 挂起模式或睡眠模式; ?锁存性能超过100 mA / JESD 100 II级 ?输入接受电压最高达3.6 V ?低噪声时过冲和欠冲小于VCC的10% ?I OFF电流提供部分省电模式操作 ?多种封装选择 ?指定使用温度范围从-40°C到+ 85°C和?40°C到+ 125°C 3、订购信息(略) 4、标记(略) 5、逻辑图

各种电平总结

TTL和CMOS电平总结 TTL和CMOS电平总结 TTL——Transistor-Transistor Logic HTTL——High-speed TTL LTTL——Low-power TTL STTL——Schottky TTL LSTTL——Low-power Schottky TTL ASTTL——Advanced Schottky TTL ALSTTL——Advanced Low-power Schottky TTL FAST(F)——Fairchild Advanced schottky TTL CMOS——Complementary metal-oxide-semiconductor HC/HCT——High-speed CMOS Logic(HCT与TTL电平兼容) AC/ACT——Advanced CMOS Logic(ACT与TTL电平兼容)(亦称ACL) AHC/AHCT——Advanced High-speed CMOS Logic(AHCT与TTL电平兼容) FCT——FACT扩展系列,与TTL电平兼容 FACT——Fairchild Advanced CMOS Technology 1,TTL电平: 输出高电平>2.4V,输出低电平<0.4V。在室温下,一般输出高电平是3.5V,输出低电平 是0.2V。最小输入高电平和低电平:输入高电平>=2.0V,输入低电平<=0.8V,噪声容限是0.4V。 2,CMOS电平: 1逻辑电平电压接近于电源电压,0逻辑电平接近于0V。而且具有很宽的噪声容限。 3,电平转换电路: 因为TTL和COMS的高低电平的值不一样(ttl 5v<==>cmos 3.3v),所以互相连接时需 要电平的转换:就是用两个电阻对电平分压,没有什么高深的东西。哈哈 4,OC门,即集电极开路门电路,OD门,即漏极开路门电路,必须外界上拉电阻和电源才能将开关电平作为高低电平用。否则它一般只作为开关大电压和大电流负载,所以又叫做驱 动门电路。 5,TTL和COMS电路比较: 1)TTL电路是电流控制器件,而coms电路是电压控制器件。 2)TTL电路的速度快,传输延迟时间短(5-10ns),但是功耗大。 COMS电路的速度慢,传输延迟时间长(25-50ns),但功耗低。 COMS电路本身的功耗与输入信号的脉冲频率有关,频率越高,芯片集越热,这是正常

电平转换电路

3.1 应用举例-应用SN74LVC2G07实行电平转换 图6显示了SN74LVC2G07一个Buffer作1.8V到5V的转换,另一Buffer 作3.3V到1.8V的转换。 器件的电源电压为1.8V。它可以保证器件将输入最低的VIH识别为有效的高电平。输出上拉电阻的最小值取决于器件开漏脚的最大灌电流能力(maximum current-sinking capability Iol max)。而最大灌电流能力是受限于输出信号的最大允许的上升时间的。 Rpu(min)=(Vpu-Vol)/ Iol(max) 对于图6中的SN74LVC2G07,假设Vpu1=5V±0.5V,Vpu2=1.8V±0.15V,而且电阻的精度为5% Rpu1(min)=((5.5V-0.45V)/4mA)×(1/0.95)=1.33kΩ 最接近的标称值为1.5kΩ。 Rpu2(min)=((1.8V-0.45V)/4mA)×(1/0.95)=394.73Ω 最接近的标称值为430Ω。 图7显示了在不同上拉电阻值的情况下具有10pF容性负载情况下的输出波形。当上拉电阻值增大后,输出信号的上升时间也增加了。

3.2 不要在CMOS 驱动的输出端加上拉电阻

在电平转换时,系统设计者不能在CMOS器件的输出端加上拉电阻。这种作法有很多弊端,应该避免使用。一个问题是在输出为低时增加了功耗。当CMOS 驱动输出为高是也会产生另一个危害。高电平的电源会通过上拉电阻对低电平电源灌电流。此时,下部的N沟道晶体管是关闭的,上部的P沟道晶体管是导通的。电流灌入低电平的电源会产生无法预料的后果。 4 FET开关 TI的CB3T,CBT,CBTD和TVC系列的总线开关可以用作Level-shifter。FET开关非常适用于不需要电流驱动并有很短传播时延的电平转换应用。 FET开关的好处: ●很短的传播时延 ●TVC器件(或者将CBT 器件配置为TVC)不用方向控制就可以实现双向电平转换 TI的CB3T系列器件可以用于5V到3.3V转换。图9显示了CB3T器件用作双向电平转换的一些应用。

电平转换电路

7.10 电平转换电路 在数字电路系统中,一般情况下,不同种类器件(如TTL、CMOS、HCMOS等)不能直接相连;电源电压不同的CMOS、HCMOS器件因输出电平不同也不能直接相连,这就涉及到电平转换问题。所幸的是目前单片机应用系统中的MCU、存储器、μP监控芯片、I/O扩展与接口电路芯片等多采用HCMOS工艺;另一方面74LS系列数字电路芯片已普遍被74HC系列芯片所取代。即数字电路系统中的门电路、触发器、驱动器尽可能采用74HC系列(或高速的74AHC系列)芯片、CD40系列或 CD45系列的CMOS器件(速度较HCMOS系列慢,但功耗比HC系列芯片低、电源电压范围宽。当电源电压大于5.5V时,CMOS数字逻辑器件就成了唯一可选的数字IC芯片),尽量不用74LS系列芯片(速度与74HC系列相同,但电源范围限制为5.0V±5%、功耗大、价格甚至比74HC系列高)与74系列(在74系列中,只有输出级可承受高压的7406、7407 OC门电路芯片仍在使用)。 根据CMOS、HCMOS芯片输出高低电平特征、输入高低电平范围,在电源电压相同,且不大于5.5V情况下,这些芯片能直接相连。因此,在现代数字电子电路中只需解决不同电源电压CMOS、HCMOS器件之间的连接问题。 7.10.1 高压器件驱动低压器件接口电路 高压器件驱动低压器件(如5V驱动3V或9V驱动5V、3V)时,一般不能直接相连,应根据高压器件输出口结构(漏极开路的OD门、准双向或CMOS互补推挽输出)选择相应的接口电路。 对于OD输出引脚,可采用图7-42(a)所示电路,上拉电阻R一般取 10K~510K之间,具体数值与前级输出信号频率有关:输出信号频率高,如1MHz以上方波信号,R取小一些;输出信号频率低,R可取大一些,以减小输出低电平时上拉电阻R的功耗。 对于CMOS互补推挽输出、准双向(如MCS-51的P1、P2、P3口)输出,须在两者之间加隔离二极管,如图7-42(b)所示,其中电阻R选择与图(a)相同,二极管D可采用小功率开关二极管,如1N4148。前级输出高电平时,二极管D截止,后级输入高电平电压接近电源电压。当前级输出低电平时,二极管D导通,后级输入低电平电压=+(二极管导通压降)。显然<1.0V,当后级电路为HCMOS、CMOS器件时,只要输入级N沟

3.3V转5V的双向电平转换电路

3.3V转5V的双向电平转换电路 说说所有的电平转换方法,你自己参考~ (1) 晶体管+上拉电阻法 就是一个双极型三极管或MOSFET,C/D极接一个上拉电阻到正电源,输入电平很灵活,输出电平大致就是正电源电平。 (2) OC/OD 器件+上拉电阻法 跟1) 类似。适用于器件输出刚好为OC/OD 的场合。 (3) 74xHCT系列芯片升压(3.3V→5V) 凡是输入与5V TTL 电平兼容的5V CMOS 器件都可以用作3.3V→5V 电平转换。 ——这是由于3.3V CMOS 的电平刚好和5V TTL电平兼容(巧合),而CMOS 的输出电平总是接近电源电平的。 廉价的选择如74xHCT(HCT/AHCT/VHCT/AHCT1G/VHCT1G/...) 系列(那个字母 T 就表示TTL 兼容)。 (4) 超限输入降压法(5V→3.3V, 3.3V→1.8V, ...) 凡是允许输入电平超过电源的逻辑器件,都可以用作降低电平。 这里的"超限"是指超过电源,许多较古老的器件都不允许输入电压超过电源,但越来越多的新器件取消了这个限制(改变了输入级保护电路)。 例如,74AHC/VHC 系列芯片,其datasheets 明确注明"输入电压范围为0~5.5V",如果采用3.3V 供电,就可以实现5V→3.3V 电平转换。 (5) 专用电平转换芯片 最著名的就是164245,不仅可以用作升压/降压,而且允许两边电源不同步。这是最通用的电平转换方案,但是也是很昂贵的(俺前不久买还是¥45/片,虽是零售,也贵的吓人),因此若非必要,最好用前两个方案。 (6) 电阻分压法 最简单的降低电平的方法。5V电平,经1.6k+3.3k电阻分压,就是3.3V。 (7) 限流电阻法 如果嫌上面的两个电阻太多,有时还可以只串联一个限流电阻。某些芯片虽然原则上不允许输入电平超过电源,但只要串联一个限流电阻,保证输入保护电流不超过极限(如74HC 系列为20mA),仍然是安全的。 (8) 无为而无不为法 只要掌握了电平兼容的规律。某些场合,根本就不需要特别的转换。例如,电路中用到了某种5V 逻辑器件,其输入是3.3V 电平,只要在选择器件时选择输入为TTL 兼容的,就不需要任何转换,这相当于隐含适用了方法3)。 (9) 比较器法 算是凑数,有人提出用这个而已,还有什么运放法就太恶搞了。 那位说的可以~但我分析你也不是非要芯片不可吧?尽量节约成本啊~ 3.3V转5V 电平转换方法参考 电平转换

常用数字芯片大全

产品 型号规格性能说明型号规格性能说明 名称 74LS SN74LSOO四2输入与非门SN74LSO1四2输入与非门 SN74LSO2四2输入与非门SN74LS03四2输入与非门 SN74LS04六反相器SN74LS05六反相器 SN74LS06六反相缓冲器/驱动器SN74LS07六缓冲器/驱动器 SN74LS08四2输入与非门SN74LS09四2输入与非门 SN74LS10三3输入与非门SN74LS11三3输入与非门 SN74LS12三3输入与非门SN74LS13三3输入与非门 SN74LS14六反相器.斯密特触发SN74LS15三3输入与非门 SN74LS16六反相缓冲器/驱动器SN74LS17六反相缓冲器/驱动器 SN74LS20双4输入与门SN74LS21双4输入与门 SN74LS22双4输入与门SN74LS25双4输入与门 SN74LS26四2输入与非门SN74LS27三3输入与非门 SN74LS28四输入端或非缓冲器SN74LS30八输入端与非门 SN74LS32四2输入或门SN74LS33四2输入或门 SN74LS37四输入端与非缓冲器SN74LS38双2输入与非缓冲器 SN74LS40四输入端与非缓冲器SN74LS42BCD-十进制译码器 SN74LS47BCD-七段译码驱动器SN74LS48BCD-七段译码驱动器SN74LS49BCD-七段译码驱动器SN74LS51三3输入双与或非门 SN74LS54四输入与或非门SN74LS55四4输入与或非门 SN74LS63六电流读出接口门SN74LS73双J-K触发器 SN74LS74双D触发器SN74LS754位双稳锁存器 SN74LS76双J-K触发器SN74LS78双J-K触发器 SN74LS83双J-K触发器SN74LS854位幅度比较器 SN74LS86四2输入异或门SN74LS884位全加器 SN74LS904位十进制波动计数器SN74LS918位移位寄存器 SN74LS9212分频计数器SN74LS93二进制计数器 SN74LS965位移位寄存器SN74LS954位并入并出寄存器 SN74LS109正沿触发双J-K触发器SN74LS107双J-K触发器 SN74LS113双J-K负沿触发器SN74LS112双J-K负沿触发器 SN74LS121单稳态多谐振荡器SN74LS114双J-K负沿触发器 SN74LS123双稳态多谐振荡器SN74LS122单稳态多谐振荡器 SN74LS125三态缓冲器SN74LS124双压控振荡器 SN74LS1313-8线译码器SN74LS126四3态总线缓冲器 SN74LS13313输入与非门SN74LS132二输入与非触发器 SN74LS137地址锁存3-8线译码器SN74LS136四异或门 SN74LS139双2-4线译码-转换器SN74LS1383-8线译码/转换器 SN74LS14710-4线优先编码器SN74LS145BCD十进制译码/驱动器SN74LS153双4选1数据选择器SN74LS1488-3线优先编码器 SN74LS155双2-4线多路分配器SN74LS1518选1数据选择器 SN74LS157四2选1数据选择器SN74LS1544-16线多路分配器 SN74LS160同步BDC十进制计数器SN74LS156双2-4线多路分配器

3.3v和5v双向电平转换芯片

3.3v和5v双向电平转换芯片 74LVC4245,8位电平转换 74LVC4245A,8位双向 NLSX4373,2位电平转换 NLSX4014,4位电平转换 NLSX4378,4位电平转换 NLSX3018,8位电平转换 max3002,8路双向 TXB0104?(她好像有一个系列?0102?0104?0106?0108), ADG3308 74HCT245:三态输出的八路总线收发器 SN74AVCH2T45 SN74AVC16T245:具有可配置电压转换和3 态输出的16 位双电源总线收发器 SN74LVC2T45DCT:双位双电源总线收发器可配置电压转换和三态输出 SN74LVC4245A:8位 德州仪器宣布推出SN74LVC1T45、SN74LVC2T45、SN74AVC8T245及SN74AVC20T245四款新型双电源电平转换收发器。该新品能够在 1.5V、1.8V、2.5V、3.3V 与5V 电压节点之间进行灵活的双向电平转换,而且可提供全面的可配置性。如果采用AVC 技术,则每条轨可从 1.4V 配置为 3.6V;而采用LVC 技术时则可从1.65V 配置为5.5V。适用于便携式消费类电子产品、网络、数据通信以及计算应用领域。 日前,德州仪器(TI)宣布推出四款新型的双电源电平转换器--AVC1T45、AVC2T45、AVC16T245及AVC32T245,从而进一步扩展其电平转换产品系列。这些转换器能够在互不兼容的I/O之间进行通信。这四款器件均支持1.2V、1.5V、1.8V、2.5V与3.3V节点之间的双向电平转换。在混合信号环境中,可以使用这些电压电平的任意组合,从而提高这些器件的灵活性。 1位AVC1T45与2位AVC2T45可根据需要在电路板上集成单或双转换器功能,而不是通过较高位宽的器件进行路由,这有助于简化电路板布线作业(board routing),可适用于便携式手持应用的转换要求。AVC16T245与AVC32T245是TI当前16位与32位双电源转换功能的改进版本。这些器件能够提供较低的功耗(AVC16T245的功耗为25μA,而AVCA164245的功耗则为40μA)。该类器件的总线控制选件无需外部上拉/下拉电阻器。TI还提供全面的IBIS模型支持。 SN74AVC1T45与SN74AVC2T45以及总线控制版本SN74AVCH1T45与SN74AVCH2T45均采用NanoStar 与NanoFree芯片级封装。这些器件现已推出,并可提供样片。批量为千套时,预计1T45器件的最低零售单价为0.24美元,而2T45器件的最低零售单价为0.35美元。 SN74AVC16T245和总线控制版本SN74AVCH16T245采用56球栅VFBGA封装。该器件现已推出,并可提

txs0102 电平转换芯片

FEATURES DCT OR DCU PACKAGE (TOP VIEW)1B1827V CCB 36OE 45B2GND V CCA A2A1YZP PACKAGE (BOTTOM VIEW)A254A136OE V CCA 27V CCB GND 8B1 1B2A1B1C1D1A2B2C2D2DESCRIPTION/ORDERING INFORMATION https://www.360docs.net/doc/2d9954159.html, .......................................................................................................................................................SCES640A–JANUARY 2007–REVISED MAY 2008 2-BIT BIDIRECTIONAL VOLTAGE-LEVEL TRANSLATOR FOR OPEN-DRAIN AND PUSH-PULL APPLICATIONS ?No Direction-Control Signal Needed ?ESD Protection Exceeds JESD 22 ?Max Data Rates –A Port –24Mbps (Push Pull)–2500-V Human-Body Model (A114-B) –2Mbps (Open Drain)–250-V Machine Model (A115-A) ?Available in the Texas Instruments NanoFree?–1500-V Charged-Device Model (C101) Package –B Port ? 1.65V to 3.6V on A port and 2.3V to 5.5V on –8-kV Human-Body Model (A114-B) B port (V CCA ≤V CCB )–250-V Machine Model (A115-A) ?V CC Isolation Feature –If Either V CC Input Is at –1500-V Charged-Device Model (C101) GND,Both Ports Are in the High-Impedance State ?No Power-Supply Sequencing Required – Either V CCA or V CCB Can Be Ramped First ?I off Supports Partial-Power-Down Mode Operation ?Latch-Up Performance Exceeds 100mA Per JESD 78,Class II This two-bit noninverting translator uses two separate configurable power-supply rails.The A port is designed to track V CCA .V CCA accepts any supply voltage from 1.65V to 3.6V.The B port is designed to track V CCB .V CCA must be less than or equal to V CCB .V CCB accepts any supply voltage from 2.3V to 5.5V.This allows for low-voltage bidirectional translation between any of the 1.8-V,2.5-V,3.3-V,and 5-V voltage nodes. When the output-enable (OE)input is low,all outputs are placed in the high-impedance state. To ensure the high-impedance state during power up or power down,OE should be tied to GND through a pulldown resistor;the minimum value of the resistor is determined by the current-sourcing capability of the driver. ORDERING INFORMATION T A PACKAGE (1)(2) ORDERABLE PART NUMBER TOP-SIDE MARKING (3)NanoStar?–WCSP (DSBGA) Reel of 3000TXS0102YZPR 2H_0.23-mm Large Bump –YZP Reel of 3000TXS0102DCTR NFEZ___–40°C to 85°C SSOP –DCT Tube of 250TXS0102DCTT NFEZ ___VSSOP –DCU Reel of 3000TXS0102DCUR NFE_(1) Package drawings,thermal data,and symbolization are available at https://www.360docs.net/doc/2d9954159.html,/packaging .(2) For the most current package and ordering information,see the at the end of this document,or see the TI website at https://www.360docs.net/doc/2d9954159.html, .(3)DCT:The marking has three additional characters that designate the year,month,and assembly/test site. DCU:The actual top-side marking has one additional character that designates the assembly/test site. YZP:The actual top-side marking has three preceding characters to denote year,month,and sequence code,and one following character to designate the assembly/test site.Pin 1identifier indicates solder-bump composition (1=SnPb,?=Pb-free). Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.