(整理)Pentium微处理器内部寄存器.

Pentium微处理器的内部寄存器

Pentium是Intel公司于1993年3月推出的第五代80X86系列微处理器,简称P5或80586,中文译名为“奔腾”。与其前辈80X86微处理器相比,Pentium采用了全新的设计,它有64位数据线和32位地址线,但依然保持了与其前辈80X86的兼容性,在相同的工作方式上可以执行所有的80X86程序。

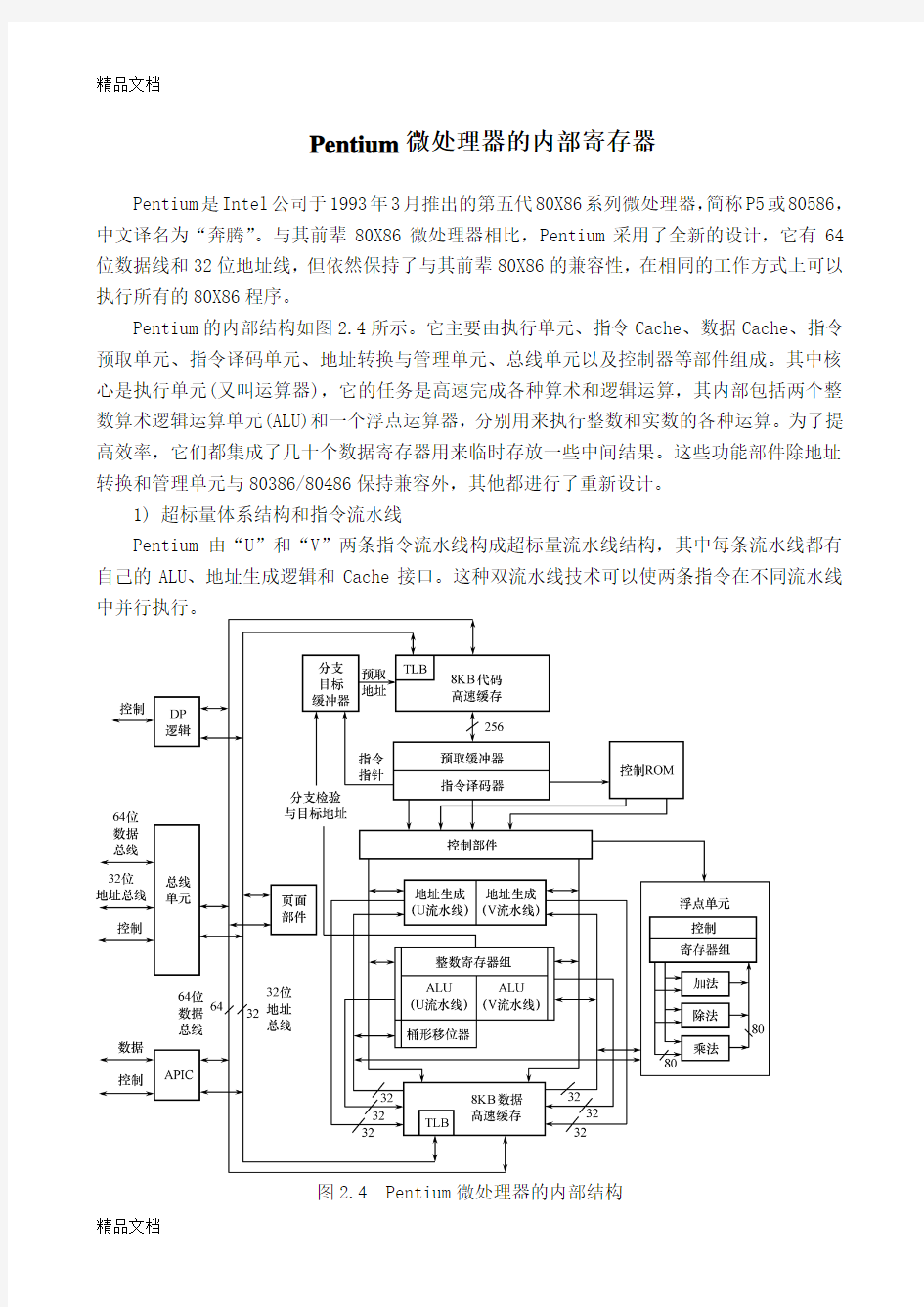

Pentium的内部结构如图2.4所示。它主要由执行单元、指令Cache、数据Cache、指令预取单元、指令译码单元、地址转换与管理单元、总线单元以及控制器等部件组成。其中核心是执行单元(又叫运算器),它的任务是高速完成各种算术和逻辑运算,其内部包括两个整数算术逻辑运算单元(ALU)和一个浮点运算器,分别用来执行整数和实数的各种运算。为了提高效率,它们都集成了几十个数据寄存器用来临时存放一些中间结果。这些功能部件除地址转换和管理单元与80386/80486保持兼容外,其他都进行了重新设计。

1) 超标量体系结构和指令流水线

Pentium由“U”和“V”两条指令流水线构成超标量流水线结构,其中每条流水线都有自己的ALU、地址生成逻辑和Cache接口。这种双流水线技术可以使两条指令在不同流水线中并行执行。

图2.4 Pentium微处理器的内部结构

每条流水线又分为指令预取PF、指令译码(一次译码)D1、地址生成(二次译码)D2、指令执行EX和回写WB共5个步骤。图2.5给出了Pentium的指令流水线操作示意。

图2.5 Pentium指令流水线操作示意图

当第一条指令完成指令预取,进入第二个操作步骤D1,执行指令译码操作时,流水线就可以开始预取第二条指令;当第一条指令进入第三个步骤D2,执行地址生成时,第二条指令进入第二个步骤D1,开始指令译码,流水线又开始预取第三条指令;当第一条指令进入第四个步骤EX,执行指令规定的操作时,第二条指令进入第三个步骤D2,执行地址生成,第三条指令进入第二个步骤D1,开始指令译码,流水线又开始预取第四条指令;当第一条指令进入第五个步骤WB,执行回写操作时,第二条指令进入第四个步骤EX,执行指令规定的操作,第三条指令进入第三个步骤D2,执行地址生成,第四条指令进入第二个步骤D1,开始指令译码,流水线又开始预取第五条指令。

这种流水线操作并没有减少每条指令的执行步骤,5个步骤哪一步都不能跳越。但由于各指令的不同步骤之间并行执行,从而极大地提高了指令的执行速度。从第一个时钟开始,经过5个时钟后,每个时钟都有一条指令执行完毕从流水线输出。在这种理想情况下,Pentium 的超标量体系结构每个时钟周期内可执行两条整数指令(每条流水线执行一条指令)。

2) 重新设计的浮点运算部件

Pentium的浮点运算部件在80486的基础上作了重新设计,采用了超流水线技术,由8个独立执行部件进行流水线作业,使每个时钟周期能完成一个浮点操作(或两个浮点操作)。采用快速算法可使诸如ADD、MUL和LOAD等运算的速度最少提高3倍,在许多应用程序中利用指令调度和重叠(流水线)执行可使性能提高5倍以上。同时,这些指令用电路进行固化,用硬件来实现,使执行速度得到更大提高。

3) 独立的指令Cache和数据Cache

Pentium片内有两个8KB的超高速缓存器,一个是指令Cache,一个是数据Cache。转换后备缓冲器TLB(Translation Look-aside Buffer)的作用是将线性地址转换为物理地址。这两种Cache采用32×8线宽,是对Pentium的64位总线的有力支持。指令和数据分别使用不同的Cache,使Pentium中数据和指令的存取减少了冲突,提高了性能。

Pentium的数据Cache有两种接口,分别与U和V两条流水线相连,以便能在相同时刻向两个独立工作的流水线进行数据交换。当向已被占满的数据Cache中写数据时,将移走当前使用频率最低的数据,同时将其写回内存,这种技术称为Cache回写技术。由于CPU向Cache 写数据和将Cache释放的数据写回内存是同时进行的,所以采用Cache回写技术将节省处理时间。

4) 分支指令预测。

Pentium提供了一个称为BTB(Branch Target Buffer)的小Cache来动态地预测程序的分支操作。当某条指令导致程序分支时,BTB记忆下该条指令和分支的目标地址,并用这些信息预测该条指令再次产生分支时的路径,预先从该处预取,保证流水线的指令预取步骤不会空置。这一机构的设置,可以减少在循环操作时对循环条件的判断所占用的CPU的时间。

5) 采用64位外部数据总线

Pentium芯片内部ALU和通用寄存器仍是32位,所以还是32位微处理器,但它同内存储器进行数据交换的外部数据总线为64位,使两者之间的数据传输速度可达528MB/s。此外Pentium还支持多种类型的总线周期,在突发方式下,可以在一个总线周期内读入256B的数据。

2. Pentium的外部引脚

Pentium芯片有168个引脚,这些引脚信号线也即Pentium CPU总线,分为三大类:总线接口引脚、处理器控制引脚、调试与测试引脚。

1) 总线接口信号

Pentium的总线接口信号如表2.1所示。这些引脚信号包括用于管理访问外部存储器和I/O端口必须的地址、数据和总线周期控制信号,以及Cache控制信号。

D

63~D

是Pentium的64位双向数据总线。A

31

~A

3

和0

~

7BE

BE

构成32位地址总线,以

提供存储器和I/O端口的物理地址。A

31~A

3

用于确定一个8字节单元地址,0

~

7BE

BE

则用

于指明在当前的操作中要访问8字节中的哪些字节。Pentium 微处理器规定:

0BE

对应数据

线D 7~D 0;1BE 对应数据线D 15~D 8;2BE 对应数据线D 23~D 16;3BE 对应数据线D 31~D 24;4BE

对应数据线D 39~D 32;5BE

对应数据线D 47~D 40;

6

BE

对应数据线D 55~D 48;

7

BE

对应数据线D 63~

D 56。

Pentium 微处理器的地址线没有设置A 2、A 1和A 0引脚,但可由

0~7BE BE 这8个字节使

能信号产生,为保持与前辈80X86的兼容性,还应产生BHE 信号。

C D /(数据/控制)、R W /(写/读)、IO M /(存储器/IO)是总线周期定义的基本信号,这3个信号的不同组合可以决定当前的总线周期所要完成的操作,如表2.2所示。这些操作的意义将在有关章节加以介绍。

2) 处理器控制信号

处理器控制信号如表2.3所示。包括时钟、处理器初始化、FRC 、总线仲裁、Cache 窥视、中断请求、执行跟踪、数字出错和系统管理等信号。

3) 调试与测试引脚

调试与测试信号如表2.4所示。包括探针方式、断点/性能监测和边界扫描等引脚信号。

2.3.2内部寄存器

Pentium的内部寄存器按功能分为四类:基本寄存器、系统级寄存器、调试与模型专用寄存器、浮点寄存器。它们是在80486内部寄存器的基础上扩充而来,并与其前辈80X86保持了兼容。主要差别是Pentium用一组模型专用寄存器代替了80486的测试寄存器,并扩充了一个系统控制寄存器。

1. 基本寄存器

基本寄存器包括通用寄存器、指令指针寄存器、标志寄存器和段寄存器,这些寄存器都是在8086/8088基础上扩展而来的,如图2.6所示。

图2.6 基本寄存器

1) 通用寄存器

8个32位通用寄存器EAX、EBX、ECX、EDX、ESI、EDI、EBP、ESP是在8086/8088的8个16位寄存器基础上扩展位数而来的。为了与8086/8088兼容,它们的低16位可以单独访问,并以同8086/8088中相同的名称命名: AX、BX、CX、DX、SI、DI、BP、SP。其中AX、BX、CX、DX还可进一步分成两个8位寄存器单独访问,且同样有自己独立的名称: AH、AL,BH、BL,CH、CL,DH、DL。上述寄存器中,(E)SP是指示栈顶的指针,称为堆栈寄存器。在32位寻址时,8个32位寄存器均可用作存储器访问的地址寄存器,但在16位寻址时,只能使用BX、BP、SP、SI、DI寄存器,其中BX和BP称为基址寄存器,SI和DI称为变址寄存器,

(E)CX则常用于循环控制,又称为循环计数寄存器,(E)AX则称为累加器。

2) 指令指针寄存器(EIP)

EIP用于保存下一条待预取指令相对于代码段基址(由CS提供)的偏移量。它的低16位也可以单独访问,并称之为IP寄存器。当80X86/Pentium工作在32位操作方式时,采用32位的EIP;工作在16位操作方式,采用16位的IP。用户不可随意改变其值,只能通过转移类、调用及返回类指令改变其值。

3) 标志寄存器(EFLAGS)

标志寄存器EFLAGS是32位的,它是在8086/8088/80286标志寄存器FLAGS的基础上扩

充而来的,共定义了三类17种(18位)标志,即:状态标志6种(CF、PF、AF、ZF、SF和OF),

用于报告算术/逻辑运算指令执行后的状态;控制标志1种(DF),用于控制串操作指令的地址改变方向;系统标志10种11位(TF、IF、IOPL、NT、RF、VM、AC、VIF、VIP和ID),用于控制I/O、屏蔽中断、调试、任务转换和控制保护方式与虚拟8086方式间的转换。

图2.7给出了EFLAGS中各位的标志名以及各标志位与CPU的隶属关系,取值为0的位是Intel保留的,并未使用。各标志位意义如下:

图2.7 标志寄存器

①进位标志CF(位0): CF=1表示运算结果的最高位产生了进位或借位。这个标志主要用于多字节数的加减法运算。移位和循环指令也用到它。

②奇偶标志PF(位2): PF=1表示运算结果中有偶数个1。该标志主要用于数据传输过程中检错。

③辅助进位标志AF(位4): AF=1表示运算导致了低4位向第5位(位4)的进位或借位。该标志主要用于BCD码运算。

④零标志ZF(位6): ZF=1表示运算结果的所有位为0。

⑤符号标志SF(位7): SF=1表示运算结果的最高位为1。对于用补码表示的有符号数,SF=1表示结果为负数。

⑥自陷标志TF(位8): TF=1表示CPU将进入单步执行方式,即每执行一条指令后都产生一个内部中断。利用它可逐条指令地调试程序。

⑦中断允许标志IF(位9): IF=1表示CPU允许外部可屏蔽中断,否则禁止外部可屏蔽中断。注意,IF标志对内部中断和外部不可屏蔽中断(NMI)不会产生影响。

⑧方向标志DF(位10): DF=1表示在串操作过程中地址指针(E)DI和(E)SI的变化方向是递减,否则为递增。

⑨溢出标志OF(位11):OF=1表示有符号数运算时,运算结果的数值超过了结果操作数的表示范围。OF对无符号数是无意义的。

⑩ I/O特权级标志IOPL(位13和位12):这两位表示0~3级4个I/O特权级,用于保护方式。只有当任务的现行特权级高于IOPL时(0级最高,3级最低),执行I/O指令才能保证不产生异常。

任务嵌套标志NT(位14):指明当前任务是否嵌套,即是否被别的任务调用。该位的置位和复位通过向其他任务的控制转移来实现,NT的值由IRET指令检测,以确定执行任务间返回还是任务内返回,NT用于保护方式。

恢复标志RF(位16):该标志与调试寄存器的断点或单步操作一起使用。该位为1,即使遇到断点或调试故障,也不产生异常中断。在成功执行完每条指令时,该位自动清零,但在执行堆栈操作、任务切换、中断指令时有例外。

虚拟86模式标志VM(位17):在保护方式下,若该位置1,80386/80486/Pentium处理器将转入虚拟8086方式。VM位只能以两种方式来设置:在保护方式下,由最高特权级(0级)的代码段的IRET指令来设置;或者由任务转换来设置。

对准检查标志AC(位18):该位只对80486和Pentium有效。AC=1,且CR0的AM位也为1,则进行字、双字或4字的对准检查。若发现要访问的操作未按边界对齐时,会发生异常中断。

虚拟中断标志VIF(位19):该位只对Pentium有效。是虚拟方式下中断允许标志位的拷贝(Copy)。

虚拟中断挂起标志VIP(位20):该位只对Pentium有效。用于在虚拟方式下提供有关中断的信息,在多任务环境下,为操作系统提供虚拟中断标志和中断挂起信息。

标识标志ID(位21):该位只对Pentium有效。用以指示Pentium微处理器对CPUID指令的支持状态。CPUID指令为系统提供了有关Pentium处理器的信息,诸如型号及制造商。

4) 段寄存器

6个段寄存器中,FS和GS是80386以上CPU才有的。段寄存器用于决定程序使用的存储器区域块。其中CS指明当前的代码段;SS指明当前的堆栈段;DS、ES、FS和GS指明当前的四个数据段。

每个段寄存器由一个16位的段选择器和64位(对80286是48位)的描述符高速缓存器组

成。段选择器是编程者可直接访问的,而描述符高速缓存器则是编程者不能访问的。由于80X86/Pentium在不同工作方式下,段的概念有所不同,因而段寄存器的使用也不相同:(1)实地址方式和虚拟8086方式下的段寄存器

在实地址方式和虚拟8086方式下,段的概念与8086的段定义相同,即每段的长度限定为64KB。这时,段选择器就是段寄存器,它存放的是段基址的高16位。

在这两种方式下,处理器的物理地址实质上是这样产生的: CPU将段寄存器的内容自动乘16并放在段描述符高速缓存器的基地址中;将段限定固定为0FFFFH;其他属性也是固定的。即:

物理地址=段选择器×16+偏移地址

这种物理地址的形成与8086在本质上没有区别。由于段的最大长度、段基址的确定方法和段的其他属性都是固定的,所以与8086一样,不必用段描述符来说明段的性质。

(2)保护虚拟地址方式下的段寄存器

保护虚拟地址方式是一种既支持虚拟存储管理和多任务,又具有保护功能的工作方式。在该方式下,段的长度和段的属性都不固定,每个段的长度可以在1B到4GB之间变化(80286只能在1B到64KB之间变化),段的基址也只有在操作系统将该段从外存调入内存时才能确定。所以,为了描述每个段的基址、属性和边界(长度),为每个段定义了一个64位(80286为48位)的描述符,称为段描述符或描述子。

段描述符的格式如图2.8所示。低48位是80286的描述符,包括16位段边界、24位段基地址和8位属性。80386以上的32位微处理器则在此基础上扩充了8位基地址、4位边界和4位属性,即包括20位段边界、32位段基地址和12位属性。其中属性位定义如下:

图2.8 段描述符格式

① P为存在位,为1表示存在(在实内存中),为0表示不存在。

② DPL为描述符特权级,允许为0~3级。

③ S为段描述符类别,为1表示代码段或数据段描述符,为0表示系统描述符。

④ TYPE为段的类型。

⑤ A为已访问位,为1表示已访问过。

⑥ G为粒度位(段边界所用单位),为0表示字节,即段的最大长度为220B=1MB,为1表示页,在80386/80486中,每页为4KB,即段的最大长度为220×4KB=4GB,Pentium则提供了4KB和4MB两种页面选择。

⑦ D为缺省操作数长度,为0表示16位,为1表示32位(该位仅对代码段有效)。

这些段描述符存放在两个系统表格GDT和LDT中。GDT是全局描述符表,存放着操作系

统使用的和各任务公用的段描述符;LDT是局部描述符表,存放着某个任务专用的段描述符。程序(或系统)中装入段选择器的也不再是直接的段基址,而是一个指向某个段描述符的16位

的段选择符,其格式如图2.9所示。其中b

1b

位为请求特权级字段RPL,这两位提供(0~3级)4

个特权级用于保护;b

2位为表指示符字段TI,指明本段描述符是在GDT中还是LDT中;b

15

~

b

3

这13位构成描述符索引字段INDEX,用于指明段描述符在指定描述符表中的序号。

图2.9 段选择符格式

当将一个选择符装入一个段选择器(给段选择器预置初值)时,处理器将自动从GDT或LDT 中找到其对应的描述符,装入相应段寄存器的描述符高速缓存器中。该过程对用户来说是透明的。如图2.10所示,当将一个选择符装入DS段选择器时,处理器根据INDEX和TI指示自动从LDT中找到第64个描述符装入DS段寄存器的描述符高速缓存器。

以后,每当访问存储器时,与所用段相关的段描述符高速缓冲器就自动参与该次存储器访问操作。段基地址成为线性地址或物理地址计算中的一个分量,界限用于段限检查操作,属性则对照所要求的存储器访问类型进行检查。即:

线性地址=段描述符高速缓存器中段基址+偏移地址

不使用页部件时,线性地址即为物理地址;使用页部件时,上述线性地址需经页管理部件使用页目录表和页表转换成物理地址。

图2.10 由段选择器指示自动装入段描述符

2. 系统寄存器

Pentium微处理器中包含一组系统级寄存器:即5个控制寄存器CR

0~CR

4

和4个系统地

址寄存器。这些寄存器只能由在特权级0上运行的程序(一般是操作系统)访问。

1) 控制寄存器

Pentium微处理器有5个控制寄存器,如图2.11所示。这些寄存器用来存放全局特性的机器状态和实现对80X86/Pentium微处理器的多种功能的控制与选择。

图2.11 控制寄存器

(1) 控制寄存器CR

0共定义了11个控制位。在80286微处理器中,CR

称为机器状态字

MSW(Machine Status Word)为一16位寄存器,定义了PE、MP、EM和TS 4位。80386在此基础上扩充了ET和PG两位。80486以上微处理器在80386的基础上又扩充了NE、WP、AM、NW和CD这5位。11个控制位分别定义如下:

① PE为保护允许位,该位为1表示允许保护,为0则以实地址方式工作。

② MP为监控协处理器位,MP位同TS位一起使用,用来确定WAIT指令是否自陷。当MP=1,且TS=1时,执行WAIT指令将产生异常7。

③ EM为仿真协处理器位,用以确定浮点指令是被自陷,还是被执行。EM=1,所有浮点指令将产生异常7。

④ TS为任务切换位,用以指出任务是否切换,执行切换操作时,TS=1。TS=1时,执行浮点指令将产生异常7。

⑤ ET是处理器扩充类型,该位用于80386微处理器,标识系统中所采用的协处理器的类型。ET=1,采用80387协处理器,否则采用80287。80486以上系统中ET置1。

⑥ NE是数字异常控制位,该位用于控制是由中断向量16还是由外部中断来处理未屏蔽的浮点异常。NE=0,处理器同IGNNE输入引脚和FEPR输出引脚配合工作;NE=1,在执行下一条非控制浮点指令或WAIT指令之前,任何未屏蔽的浮点异常(UFPE)将产生软件中断16。

⑦ WP是写保护位,用来保护管理程序写访问用户级的只读页面。该位为1时,禁止特权级程序对只读页面的写操作,否则允许只读页面由特权级0~2写入。

⑧ AM是对准屏蔽位,用来控制标志寄存器中对准检查位(AC)是否允许对准检查。AM=1,允许AC位;否则禁止AC位。

⑨ NW为不通写控制位,该位用来选择片内数据Cache的操作模式。NW=1时,禁止通写,写命中时不修改内存;否则,允许通写。

⑩ CD是Cache禁止或使能位,该位用来控制允许或禁止向片内Cache填充新数据。CD=1,当Cache未命中时,禁止填充Cache;否则,未命中时,允许填充Cache。

PG为页使能位,用于控制是否允许分页。PG=1,允许分页,否则禁止分页。

是页故障线性地址寄存器,用来保存发生页故障中断(异常14)之前所访问的最后

(2) CR

2

一个页面的线性页地址。用软件读出即可得到发生页故障的线性地址。CR2由80386以上微处理器定义。

是页目录基地址寄存器,用来存放当前任务的页目录表的物理基地址。由于页目

(3) CR

3

录表是按页对齐的(4KB),因而CR3通过高20位来实施这一要求,而低12位保留或定义为其是80386以上微处理器才使用的,在80486中新定义了PWT和PCD两个控制位。他用途。CR

3

PWT是页面通写位,用于指示是页面通写还是回写,该位为1,外部Cache对页目录进行通写,否则进行回写;PCD是页面Cache禁止位,该位用于指示页面Cache工作情况,PCD=1,禁止片内Cache,否则允许片内页Cache。这两个位只有在CR0中的页管理使能位PG=0或Cache 不使能位CD=1时才有效。

是Pentium处理器中新增加的控制寄存器,共定义了6位,各位含义如下:

(4) CR

4

① VME是虚拟方式扩充位,VME=1,允许虚拟8086方式扩充,否则禁止。

② PVI是保护方式虚拟中断位,PVI=1,允许保护方式虚拟中断,否则禁止。

③ TSD是时间戳禁止位,该位为1,且当前特权级不为0时,禁止读时间戳计数器指令RDTSC,否则RDTSC将在所有特权级上执行。

④ DE是调试扩充位,该位用来控制是否支持I/O断点,当DE=1时,允许I/O断点调试扩充,否则禁止I/O断点调试扩充。

⑤ PSE是页尺寸扩充位,该位为1,允许页面大小扩充,每页为4MB,否则禁止页面大小扩充,每页仍为4KB。

⑥ MCE是机器检查允许位,该位为1,允许机器检查异常,否则禁止机器检查异常。

2) 系统地址寄存器

系统地址寄存器只在保护方式下使用,所以又叫保护方式寄存器。80X86/Pentium用4个寄存器把在保护方式下常用的数据基地址、界限和属性保存起来,以确保其快速性。这4个寄存器如图2.12所示。

图2.12 系统地址寄存器

(1) 全局描述符表寄存器GDTR

全局描述符表寄存器GDTR是一个48位字长的寄存器(对80286而言,为40位寄存器),

用于存放全局描述符表GDT的32位(或24位)线性基地址和16位界限。

全局描述符表GDT是80X86/Pentium用来定义全局存储器地址空间的一种机制。全局存储器是一种可能被许多或所有软件任务共享的通用系统资源。也就是说,全局存储器中的存储器地址可被微处理器上的所有任务访问。该表存放着操作系统使用的和任务公用的段描述符,这些描述符标识全局存储器中的段。

用GDTR定义的全局描述符表如图2.13所示。GDT的最大长度为216字节(64KB),由于每个描述符占8个字节,即GDT中最多能定义213=8192个段描述符。

图2.13 GDTR与它定义的全局描述符表

(2) 中断描述符寄存器IDTR

中断描述符表寄存器IDTR也是一个48位字长的寄存器(对80286而言,为40位寄存器),用于存放中断描述符表IDT的32位(或24位)线性基地址和16位界限。

(3) 局部描述符表寄存器LDTR

局部描述符表寄存器LDTR也是80X86/Pentium存储器管理支持机制的一部分。每个任务除了可访问全局描述符表外还可访问它自己的专用描述符表。该专用表称为局部描述符表(LDT),它定义了任务用到的局部存储器地址空间。LDT中的段描述符可用来访问当前任务的存储器段中代码和数据。

由于每项任务都有它自己的存储器段,因此保护模式的软件系统可能会包含许多局部描述符表。所以,与段寄存器一样,LDTR值并不直接定义一个局部描述符表。它只是一个指向GDT中LDT描述符的选择符,所以LDTR和TR也称为系统段寄存器。如图2.14所示,当LDTR 中装入选择符时,相应的描述符就能够从GDT中读出来并装入LDTR的描述符高速缓存器,从而为当前任务建立了一个LDT。

LDT的最大长度也为64KB,即LDT中最多也只能定义8192个局部段描述符。

图2.14 LDTR 和它定义的局部描述符表

(4) 任务寄存器

任务寄存器(TR)在保护模式任务切换机制中很重要。与LDTR 一样,该寄存器存放的也是一个称为选择符的16位索引值。TR 开始的选择符由软件装入,它开始第一个任务。这之后再执行任务切换的指令时就自动修改选择符。

图2.15所示,TR 中的选择符用来指示全局描述符表中描述符的位置。当选择符装入TR 中的时候,相应的任务状态段(TSS)描述符自动从存储器中读出并装入任务描述符高速缓存中。该描述符定义了一个称为任务状态段(TSS)的存储块,它提供了段起始地址(Base)和段界限(Limit)。每个任务都有它自己的TSS 。TSS 包含启动任务所需的信息,诸如用户可访问的寄存器初值。

图2.15 任务寄存器和任务切换机制

3. 调试和模型专用寄存器

Pentium 处理器中提供了一组调试寄存器和一组模型专用寄存器,用于排除故障和用于执行跟踪、性能监测、测试及机器检查错误。

(1) 调试寄存器(Debug Register)

调试寄存器如图2.16所示,这是一组32位的寄存器,是程序员可访问的,提供片上支持调试。80386/80486定义了6个调试寄存器,其中DR 0~DR 3指定了4个线性断点地址;DR7为调试控制寄存器,用于设置断点;DR 6为调试状态寄存器,用于显示断点的当前状态。

图2.16 调试寄存器

Pentium 处理器对调试寄存器DR 4和DR 5给予调试寄存器DR 6和DR 7的别名。当控制寄存器CR 4中的DE 位设置为0时,即禁止调试扩充,Pentium 通过允许引用DR 6和DR 7的别名保持与现有软件兼容;当DE 位设置为1时,即允许调试扩充,引用DR 4或DR 5将产生未定义的操作码异常。

(2) 模型专用寄存器

Pentium 处理器取消了80386/80486中的测试寄存器TR ,其功能由一组“模型专用寄存器”MSR(Model Special Register)来实现,这一组MSR 用于执行跟踪、性能监测、测试和机器检查错误。Pentium 处理器采用两条指令RDMSR(读MSR)和WRMSR(写MSR)来访问这些寄存器,ECX 中的值(8位值)确定将访问该组寄存器中哪一个MSR 。表2.5给出了所有模型专用寄存器MSR 与需要装入ECX 值的关系。

2.3.3 Pentium的四种工作方式

Pentium在80486三种工作方式的基础上新增了一种系统管理方式,使Pentium微处理器具有了四种工作方式,即:实地址方式、保护虚拟地址方式、虚拟8086方式和系统管理方式。

1. 实地址方式

实地址方式是为了与8086兼容而设置的一种工作方式。在这种工作方式下,Pentium的工作原理与8086的工作原理相同,所以实地址方式又称为8086方式。

在实地址方式下,Pentium的地址线中只有低20条地址线起作用,即能寻址的物理存储器空间为1MB。其中两个物理存储空间00000000H~000003FFH和FFFFFFF0H~FFFFFFFFH是需要保留的。前者为中断向量区,后者为CPU加电或复位时程序的启动地址。

系统复位时CR

的PE位自动清0,进入实地址方式,此时,CS寄存器所对应的描述符寄

存器中的基地址为FFFF0000H,段边界为FFFFH,(EIP)=0000FFF0H,即:

程序的执行地址=基地址+(EIP)=FFFFFFF0H

程序就从此地址开始运行。当首次遇到段间转移或段间调用指令时,物理地址又自动置为000XXXXXH(X为任意值,由执行的指令而定),从而进入实地址方式下的物理地址空间。此时,Pentium处理器借助操作数长度前缀和地址长度前缀,可进行32位操作和32位寻址,但要注意32位偏移地址不能超出64KB的限制,否则必定发生异常。

因此,可以这样说,在实地址方式下,Pentium仅是一个高速的8086,它的许多优秀性能如多任务、多级保护等均不能实现。

2. 保护虚拟地址方式

保护虚拟地址方式是一种建立在虚拟存储器和保护机制基础上的工作方式,可最大限度地发挥CPU所具有的存储管理功能及硬件支持的保护机制,这就为多用户操作系统的设计提供了有力的支持。本节仅就存储空间及保护概念进行初步介绍,存储管理的具体实现将在存储器章节加以介绍。

保护方式下,Pentium微处理器有三种存储器地址空间,即物理地址空间、线性地址空间和虚拟地址空间。物理地址空间是CPU可直接寻址的,决定于CPU地址总线的位数,为232

字节(4GB);线性地址空间是由分段机制产生的,也为4GB,不分页时即为物理地址空间。

虚拟地址空间是用户编程使用的空间,决定于分段分页管理机制,无论是分段还是分段又分页,一个任务最多能访问的逻辑段数为2×213个,即GDT和LDT中所能存放的段描述符数。只分段时,每个逻辑段的最大长度为1MB,即用户所拥有的虚拟地址空间为2×213×1MB=16GB;分段又分页时,逻辑段的最大长度为4GB,用户所拥有的虚拟地址空间为214×4GB=64TB。

3. 虚拟8086方式

虚拟8086方式是为在保护方式下能与8086/8088兼容而设置的,是一种既有保护功能又能执行8086代码的工作方式。CPU与保护虚拟地址方式下的工作原理相同,但程序中指定的逻辑地址按8086方式解释。

4. 系统管理方式(SMM)

Pentium处理器除了上述三种工作方式外,增加了一种系统管理方式(System Management Mode,SMM)。SMM可使设计者实现高级管理功能,如对电源管理以及为操作系统和正在运行的程序提供安全性,而它最显著的应用就是电源管理。SMM可以使处理器和系统外围部件都休眠一定时间,然后在有一键按下或鼠标移动时能自动唤醒它们,并使之继续工作。利用SMM 可实现软件关机。

图2.18 Pentium四种工作方式的相互转换

SMM主要为系统管理而设置,与保护方式一样,是Pentium的一个主要特征。在硬件的控制下,可从任何一种方式进入SMM方式,事后再返回原来方式。四种方式间转换关系如图2.18所示,其中SMI表示系统管理中断信号有效,RSM表示系统管理方式返回指令。

飞思卡尔锁相环

备战飞思卡尔智能车大赛.开始模块总结. 锁相环设置. 公式: PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1), fbus=PLLCLK/2 void INIT_PLL(void) { CLKSEL &= 0x7f; //选用外部时钟.准备设置锁相环 PLLCTL &= 0x8F; //禁止锁相环 SYNR = 0xc9; //设置SYNR REFDV = 0x81; //设置REFDV PLLCTL |=0x70; //锁相环使能 asm NOP; asm NOP; //两个机器周期缓冲时间 while(!(CRGFLG&0x08)); //等待锁相环锁定 CLKSEL |= 0x80; //设置锁相环为时钟源 } 飞思卡尔XS128的PLL锁相环详细设置说明——关于如何提高总线工作频率PLL锁相环就相当于超频 单片机超频的原因和PC机是个一道理。分频的主要原因是外设需要的工作频率往往远低于CPU/MEMORY 这也和PC机南北桥的原理类似。总线频率设置过程 1、禁止总中断 2、寄存器CLKSEL(时钟选择寄存器)的第七位置0 即CLKSEL_PLLSEL=0。选择时钟源为外部晶振OSCCLK(外接晶振频率) 在PLL(锁相环)程序执行前 内部总线频率为OSCCLK/2 3. PLLCTL_PLLON=1 打开PLL 4.设置SYNR 时钟合成寄存器 、REFDV 时钟分频寄存器 、POSTDIV三个寄存器的参数 5、_asm(nop) _asm(nop);加入两条空指令 使锁相环稳定 6、while(!(CRGFLG_LOCK==1));//时钟校正同步 7、CLKSEL_PLLSEL=1; 下面详细说一下频率的计算一、时钟合成寄存器SYNR寄存器结构 VCOFRQ[1:0]控制压控振动器VCO的增益 默认值为00 VCO的频率与VCOFRQ[1:0]对应表

操作系统概论重点整理2017(2017年张琼声版)

操作系统概论-02323(2017年张琼声版本) 第1章操作系统简介 1.1什么是操作系统 (1)操作系统概念: 操作系统是一种复杂的系统软件,是不同程序代码、数据结构、初始化文件的集合,可执行。 操作系统是提供计算机用户与计算机硬件之间的接口,并管理计算机软件和硬件资源,并且通过这个接口使应用程序的开发变得简单、高效。 接口是两个不同部分的交接面。接口分为硬件接口和软件接口,计算机的所有功能最终都是由硬件的操作来实现的,计算机屏蔽了对硬件操作的细节。 (2)操作系统完成的两个目标: 1)与硬件相互作用,为包含在所有硬件平台上的所有底层可编程部件提供服务; 2)为运行在计算机系统上的应用程序(即用户程序)提供执行环境。 现代计算机特点是支持多任务,一方面保证用户程序的顺利执行,另一方面使计算机系统资源得到高效的利用,保证计算机系统的高性能。 (3)操作系统的功能: 处理机管理、内存管理、设备管理、文件管理。 1.2操作系统的发展 1)无操作系统 2)单道批处理系统 3)多道程序系统(多道批处理系统、分时系统) 4)微机操作系统 5)实时操作系统 6)嵌入式操作系统 7)物联网操作系统 1.2.1无操作系统阶段: 电子管,无存储设备,第一台:1946年宾夕法尼亚大学的「埃尼阿克」 单道批处理系统: 晶体管,磁性存储设备,内存中有一道批处理作业,计算机资源被用户作业独占。 吞吐量是指单位时间内计算机系统处理的作业量

1.2.2单道批处理系统 特点:自动性、顺序性、单道性。 优点:减少了等待人工操作的时间 缺点:CPU资源不能得到有效的利用。 1.2.3多道程序系统 多道程序系统:集成电路芯片,出现了分时操作系统(多个终端)。 特点:多道性、无序性、调度性、复杂性。 优点:能够使CPU和内存IO资源得到充分利用,提高系统的吞吐量。 缺点:系统平均周转时间长,缺乏交互能力。 1.2.4微机操作系统: 第一台Intel公司顾问GaryKildall 编写的CP/M系统,是一台磁盘操作系统,用于Intel8080. 1.2.5操作系统特点 (1)分时系统: 特点:多路性、及时性、交互性、独立性。 优点:提供了人机交互,可以使用户通过不同终端分享主机。 缺点:不能及时接收及时处理用户命令。 (2)实时操作系统(用户实时控制和实时信息处理): 实时操作系统:广泛应用于各种工业现场的自动控制、海底探测、智能机器人和航空航天等。 特点:多路性、独立性、及时性、交互性、可靠性。 在实时系统中,往往采取多级容错措施来保证系统安全和数据安全。 (3)操作系统产品: 1)主机操作系统(批处理、事务处理(银行支票处理或航班预订)、分时处理) 2)微机操作系统 3)服务器操作系统 4)嵌入式操作系统(物联网操作系统) 1.3操作系统的特征 现代操作系统都支持多任务,具有并发、共享、虚拟和异步性特征。 (1)并发: 指两个或多个事件在同一时间间隔内发生; (2)共享:指系统中的资源可供内存中多个并发执行的进程共同使用。 资源共享两种方式:互斥共享,同时共享; (3)虚拟:指通过某种技术把一个物理实体变成若干逻辑上的对应物;

飞思卡尔单片机编程

关于Codewarrior 中的 .prm 文件 网上广泛流传的一篇文章讲述的是8位飞思卡尔单片机的内存映射,这几天,研究了一下Codewarrior 5.0 prm文件,基于16位单片机MC9S12XS128,一点心得,和大家分享。有什么错误请指正。 正文: 关于Codewarrior 中的.prm 文件 要讨论单片机的地址映射,就必须要接触.prm文件,本篇的讨论基于Codewarrior 5.0 编译器,单片机采用MC9S12XS128。 通过项目模板建立的新项目中都有一个名字为“project.prm”的文件,位于Project Settings->Linker Files文件夹下。一个标准的基于XS128的.prm文件起始内容如下: .prm文件范例: NAMES END SEGMENTS RAM = READ_WRITE DATA_NEAR 0x2000 TO 0x3FFF;

READ_ONLY DATA_NEAR IBCC_NEAR 0x4000 TO 0x7FFF; ROM_C000 = READ_ONLY DATA_NEAR IBCC_NEAR 0xC000 TO 0xFEFF; //OSVECTORS = READ_ONLY 0xFF10 TO 0xFFFF; EEPROM_00 = READ_ONLY DATA_FAR IBCC_FAR 0x000800 TO 0x000BFF; EEPROM_01 = READ_ONLY DATA_FAR IBCC_FAR 0x010800 TO 0x010BFF; EEPROM_02 = READ_ONLY DATA_FAR IBCC_FAR 0x020800 TO 0x020BFF; EEPROM_03 = READ_ONLY DATA_FAR IBCC_FAR 0x030800 TO 0x030BFF; EEPROM_04 = READ_ONLY DATA_FAR IBCC_FAR 0x040800 TO 0x040BFF; EEPROM_05 = READ_ONLY DATA_FAR IBCC_FAR 0x050800 TO 0x050BFF; EEPROM_06 = READ_ONLY DATA_FAR IBCC_FAR 0x060800 TO 0x060BFF; EEPROM_07 = READ_ONLY DATA_FAR IBCC_FAR 0x070800 TO 0x070BFF; PAGE_F8 = READ_ONLY DATA_FAR IBCC_FAR 0xF88000 TO 0xF8BFFF;

飞思卡尔智能车比赛细则

2016

目录

第十一届竞赛规则导读 参加过往届比赛的队员可以通过下面内容了解第十一届规则主要变化。如果第一次参加比赛,则建议对于本文进行全文阅读。 相对于前几届比赛规则,本届的规则主要变化包括有以下内容: 1.本届比赛新增了比赛组别,详细请参见正文中的图1和第四章的“比赛任务” 中的描述; 2.第十届电磁双车组对应今年的A1组:双车追逐组。其它组别与新组别的对应 关系请参见图2; 3.为了提高车模出界判罚的客观性,规则提出了两种方法:路肩法和感应铁丝 法,详细请见赛道边界判定”; 4.改变了原有的光电计时系统,所有赛题组均采用磁感应方法计时,详细请参 见“计时裁判系统”; 5.取消了第十届的发车灯塔控制的方式; 6.赛道元素进行了简化,详细请参见“赛道元素”; 7.赛道材质仍然为PVC耐磨塑胶地板,但赛题组A2不再需要赛道。 8.对于车模所使用的飞思卡尔公司MCU的种类、数量不再限制。 9.比赛时,每支参赛队伍的赛前准备时间仍然为20分钟,没有现场修车环节。

一、前言 智能车竞赛是从2006开始,由教育部高等教育司委托高等学校自动化类教学指导委员会举办的旨在加强学生实践、创新能力和培养团队精神的一项创意性科技竞赛。至今已经成功举办了十届。在继承和总结前十届比赛实践的基础上,竞赛组委会努力拓展新的竞赛内涵,设计新的竞赛内容,创造新的比赛模式,使得围绕该比赛所产生的竞赛生态环境得到进一步的发展。 为了实现竞赛的“立足培养、重在参与、鼓励探索、追求卓越”的指导思想,竞赛内容设置需要能够面向大学本科阶段的学生和教学内容,同时又能够兼顾当今时代科技发展的新趋势。 第十一届比赛的题目在沿用原来根据车模识别赛道传感器种类进行划分的基础类组别之上,同时增加了以竞赛内容进行划分的提高类组别,并按照“分赛区普及,全国总决赛提高”的方式,将其中一个类别拓展出创意类组别。第十一届比赛的题目各组别分别如下: ●基础类包括B1光电组、B2摄像头组、B3电磁直立组、B4电轨组; ●提高类包括A1双车追逐组、A2信标越野组; ●创意类包括I1 电轨节能组。 图 1 不同组别,不同挑战度 每个组别在选用的车模、赛道识别方法、完成任务等方面存在差别,对于参赛选手不同学科知识和能力要求也不同,制作的挑战度也有较大的区别。相比较而言,

考研操作系统-操作系统概念与历史

考研操作系统-操作系统概念与历史 (总分:246.00,做题时间:90分钟) 一、填空题(总题数:12,分数:12.00) 1.在操作系统中,不可中断执行的操作称为 1。 填空项1:__________________ (正确答案:原语操作) 原语操作的英文名称为Atomic Operation,有时也称为原子操作。原子在很长时间内被人类认为是不可分割的最小粒子,因此它引申的意思为不可分割或不可中断。原语操作是操作系统提供并发的基础。 2.UNIX操作系统在结构上分为两个部分: 1和 2。 填空项1:__________________ (正确答案:外壳(Shell)) 填空项1:__________________ (正确答案:内核(Kernel)) 操作系统的实体通常称为内核,它包括操作系统的所有功能构件,如进程管理、内存管理、文件系统等。这些功能构件并不能直接被一般用户使用。为了方便用户使用操作系统,操作系统设计者还为操作系统覆盖了一层外壳,用户通过外壳与操作系统打交道。这个壳可以看成是操作系统的用户界面。 3.特权指令能在 1下执行,而不能在 2下执行。 填空项1:__________________ (正确答案:内核态(Kernel Mode)、用户态(user Mode)) 顾名思义,特权指令具有特权,这个特权就是对计算机资源的访问权力。与此相对的是非特权指令,此种指令不能随意访问计算机的资源。操作系统为了实现特权和非特权指令而设计了内核态和用户态。凡是在内核态下执行的指令都是特权指令,在用户态下执行的指令都是非特权指令。 4.操作系统向用户提供了两类接口:一类是 1,另一类是 2。 填空项1:__________________ (正确答案:命令级接口(command Interface)、程序级接口(Programming Interface)) 对操作系统的使用有两种方式:直接向操作系统发出命令;编程序调用操作系统服务。前一种接口是所谓的命令接口,通过操作系统的壳实现;后一种接口是程序接口,通过操作系统调用(System call)和程序语言库函数实现。 5.分时系统中 1是衡量分时系统性能的一项重要指标。 填空项1:__________________ (正确答案:响应时间(Response Time)) 响应时间指的是在提交任务后,等待系统做出回应的时间。在分时系统下,多个用户分时共享同一个系统。每个用户在用完自己的分时时间段后需要等待别的用户用完它们的分时时间段,这个等待就是用户对系统的最直观感受,等待时间越长,用户感受越差。 6.操作系统的主要功能是 1和 2。 填空项1:__________________ (正确答案:管理(Management)) 填空项1:__________________ (正确答案:魔幻(Illusion)) 管理指的是管理计算机的软硬件资源,如CPU、内存、磁盘、各种表格和数据结构、软件原语等,以保证这些资源在不同用户或程序之间合理分配和使用。魔幻指的是将少变多,难变易,丑变美,如将单CPU通过进程模型虚拟成多个CPU,将有限内存通过虚存变为容量巨大的逻辑内存。 7.在现代操作系统中,资源分配的单位是 1,而处理机调度的单位是 2。 填空项1:__________________ (正确答案:进程(Process)) 填空项1:__________________ (正确答案:线程(Thread)) 在操作系统早期,调度单位和资源分配单位均是进程。随着操作系统的发展,线程作为进程中的一个指令执行序列而成为调度的单位。在线程模型下,进程并不运行,系统执行的是线程。 8.在操作系统中,一种用空间换取时间的资源转换技术是 1。 填空项1:__________________ (正确答案:缓冲技术(Buffering)) 通过提供缓冲区(Buffer),可以让速度慢的设备与速度快的设备进行沟通与协作。 9.为实现CPU与外部设备的并行工作,系统引入了 1硬件机制。 填空项1:__________________ (正确答案:中断(Interrupt)) 在中断机制下,CPU在发出10命令后即继续执行别的任务。外部设备在完成10后便通过中断告诉CPU,CPU 通过响应中断来处理外部设备的中断请求。

飞思卡尔智能车竞赛新手入门建议

每年都会有很多新人怀着满腔热情来做智能车,但其中的很多人很快就被耗光了热情和耐心而放弃。很多新人都不知道如何入手,总有些有劲无处使的感觉,觉得自己什么都不会,却又不知道该干什么。新人中存在的主要问题我总结了以下几点: l缺乏自信,有畏难情绪 作为新人,一切都是新的。没有设计过电路,没有接触过单片机,几乎什么都不会。有些新人听了两次课,看了两篇技术报告,就发现无数不懂不会的东西,于是热情在消退,信心在减弱。这些都是放弃的前兆。殊不知,高手都是从新人过来的,没有谁天生什么都会做。一件事件,如果还没开始做,就自己否定自己,认为自己做不到,那么肯定是做不到的。 l习惯了被动接收知识,丧失了主动学习的能力。 现在的学生大多从小习惯了被灌输知识,只学老师教的,只学老师考的。殊不知一旦走向社会,将不再有老师来教,不再有应付不完的考试。做智能车和传统的教学不同,学生将从被动学习的地位转变为主动学习。就算有指导老师,有指导的学长,但也都处于被动地位,往往都不会主动来教。有的学生一开始就没有转变思想,还希望就像实验课一样,老师安排好步骤1,2,3……,然后自己按照老师安排好的步骤按部就班的完成。这样的学生,往往都丧失了提出问题和分析问题的能力,只是一个应付考试的机器。要知道,解决问题的第一步是提出问题,如果总等着别人来教,那么问题永远会挡在你面前。 l缺乏团队精神和合作意识 智能车比赛是以团队的形式参赛,只依靠个人能力单兵作战就能取得好成绩的是很少很少的。当今社会,任何人的成功都离不开身后的团队的支撑。智能车是一个很复杂的系统,电路、机械、传感器、单片机、底层驱动、控制算法……。如果所有的任务都是一个人去完成,固然锻炼了自己,但想做的很好却很不现实。很多新人,来到实验室,来到一个陌生的环境和团队,连向学长请教,和同学交流的勇气都没有,又如何融入团队呢。除了要主动融入团队,还要培养自己的团队意识。团队精神往往表现为一种责任感,如果团队遇到问题,每个人都只顾自己,出了错误,不想着解决问题,而是互相推诿埋怨。这样的团队,肯定是无法取得好成绩的。 l缺乏耐心和细心的精神 其实把一件事做好很简单,细心加上耐心。不细心就想不到,没有耐心,即使想到了也做不到。做事怕麻烦,将就,说白了就是惰性在作祟。明明可以把支架做的更轻更漂亮,明明可以把程序写的更简洁,明明可以把电路设计得更完善……。其实,每个人都有很大潜力,如果不逼自己一次,你永远不知道自己的潜力有多

考研_计算机_操作系统_操作系统概念总结

操作系统概念背诵 一、进程管理 1.进程管理的功能 ①进程控制 ②进程同步 ③进程通信 ④进程(线程)调度 2.程序顺序执行时的特征:顺序性、封闭性、可再现性。 3.程序并发执行时的特征:间断性、失去封闭性、不可再现性。 4.进程由程序段、数据段和进程控制块(PCB)组成。 5.进程的定义 ①进程是程序的一次执行。 ②进程是一个程序及其数据在处理机上顺序执行时所发生的活动。 ③进程是进程实体的运行过程,是系统进行资源分配和调度的一个独立单位。 ④进程是程序在一个数据集合上的运行过程,是系统进行资源分配和调度的一个独立单位。 6.进程的基本特征:动态性、并发性、独立性、异步性、结构特征(程序+数据+PCB) 7.进程的状态 三态:就绪状态、运行状态、阻塞状态。 五态:活动就绪、静止就绪、活动阻塞、静止阻塞、运行。 8.进程控制块(PCB)的组成:进程标识符、处理机状态、进程调度信息、进程控制信息。 9.临界区:进程中访问临界资源的那段代码叫做临界区。 10.同步机制必须遵循的原则:空闲让进、忙则等待、有限等待、让权等待。 11.P,V操作的定义 P(S):S=S?1; 若S≥0,则当前进程继续运行; 若S<0,则将当前进程插入到S的等待队列中去。 V(S):S=S+1; 若S>0,则当前进程继续运行; 若S≤0,则从S的等待队列中移出一个进程放到就绪队列中去。 12.信号量的物理意义 S=?n时,表示有n个等待进入临界区的进程,当前已有进程在临界区中访问临界资源; S=0时,表示不允许任何进程进入临界区,当前已有进程在临界区中访问临界资源; S=n时,表示临界区是空闲的,该类资源的可用数目为n,可以有n个进程访问该类资源。 13.高级通信机制有:共享存储器系统、消息传递系统、管道通信系统。 14.线程的定义:线程是进程内的一个实体,是处理机调度的基本单位,是程序内部一个单一的顺序控 制流。 15.引入进程的目的:是为了使多个程序并发执行,提高资源利用率和系统吞吐量。 16.引入线程的目的:是为了减少程序并发执行时的时空开销,使操作系统具有更好的并发性。 17.进程的基本属性

飞思卡尔单片机寄存器及汇编指令详解

附录I:寄存器地址列表 直接页面寄存器总结

高页面寄存器总结

非易失寄存器总结 注:直接页面寄存器表地址的低字节用粗体显示,直接寻址对其访问时,仅写地址低字节即可。第2列中寄存器名用粗体显示以区别右边的位名。有0的单元格表示未用到的位总是读为0,有破折号的单元格表示未用或者保留,对其读不定。

附录II 指令接与寻址方式 HCS08指令集概括 运算符 () = 括号种表示寄存器或存储器位置的内容 ← = 用……加载(读: “得到”) & = 布尔与 | = 布尔或 ⊕= 布尔异或 ×= 乘 ÷ = 除 : = 串联 + = 加 - = 求反(二进制补码) CPU registers A =>累加器 CCR =>条件代码寄存器 H =>索引寄存器,高8位 X => 索引寄存器,低8位 PC =>程序计数器 PCH =>程序计数器,高8位 PCL =>程序计数器,低8位 SP =>堆栈指针 存储器和寻址 M =>一个存储区位置或者绝对值数据,视寻址模式而定 M:M + 0x0001 => 两个连续存储位置的16位值.高8位位于M的地址,低8位位于更高的连续地址. 条件代码寄存器(CCR)位 V => 二进制补码溢出指示,第7位 H => 半进位,第4位 I => 中断屏蔽,第 3位 N => 求反指示器, 第2位 Z => 置零指示器, 第1位 C => 进/借, 第0位 (进位第 7位 ) CCR工作性符号 – => 位不受影响 0 = > 位强制为0 1 = > 位强制为1

= >根据运算结果设置或清除位 U = > 运算后没有定义 机器编码符号 dd =>一个直接寻址0x0000–0x00FF的低8位(高字节假设为0x00) ee => 16位偏移量的高8位 ff => 16位偏移量的低8位 ii => 立即数的一个字节 jj => 16位立即数值的高位字节 kk => 16位立即数值的低位字节 hh => 16位扩展寻址的高位字节 ll => 16位扩展寻址的低位字节 rr => 相对偏移量 n —任何表达范围在0–7之间的一个有符号数的标号或表达式 opr8i —任何一个表达8位立即值的标号或表达式 opr16 —任何一个表达16位立即值的标号或表达式 opr8a —任何一个表达一个8位值的标号或表达式.指令对待这个8位值为直接页面64K 字节地址空间(0x00xx)中地址的低8位. opr16a —任何一个表达16位值的标号或表达式.指令对待这个值为直接页面64K字节地址空间. oprx8 —任何一个表达8位无符号值的标号或表达式,用于索引寻址. oprx16 —任何一个16位值的标号或表达式.因为HCS08有一个16位地址总线,这可以为一个有符号或者无符号值. rel —任何指引在当前指令目标代码最后一个字节之后–128 to +127个字节之内的标号或表达式.汇编器会计算包括当前指令目标代码在内的8位有符号偏移量. 寻址方式 隐含寻址(Inherent)如CLRA,只有操作码,无操作数,需要操作的数据一般为CPU寄存器,因此不需要再去找操作数了。(INH) 立即寻址 (Immediate)如LDA #$0A,“$”表示16进制,此时操作数位于FLASH空间,与程序一起存放。(IMM) 直接寻址 (Direct)如 LDA $88,只能访问$0000-$00FF的存储器空间,指令短速度快; (DIR) 扩展寻址 (Extended)如果操作数地址超出了$00FF,自动为扩展寻址;(EXT) 相对寻址(Relative)如BRA LOOP,指令中一般给出8位有符号数表示的偏移量。(REL) 变址寻址 (Indexed) 采用[H:X]或SP作为指针的间接寻址方式。( IX )( IX1 )( IX2 ) 变址寻址 (Indexed) 1〉无偏移量:CLR ,X 简写(IX) 2〉无偏移量,指令完成后指针加1(H:X = H:X + 0x0001) ,简写(IX+)只用于指令MOV和CBEQ指令中;

飞思卡尔杯智能车竞赛报告总结

1.1. 系统分析 智能车竞赛要求设计一辆以组委会提供车模为主体的可以自主寻线的模型车,最后成绩取决于单圈最快时间。因此智能车主要由三大系统组成:检测系统,控制系统,执行系统。其中检测系统用于检测道路信息及小车的运行状况。控制系统采用大赛组委会提供的16位单片机MC9S12XS128作为主控芯片,根据检测系统反馈的信息新局决定各控制量——速度与转角,执行系统根据单片机的命令控制舵机的转角和直流电机的转速。整体的流程如图1.1,检测系统采集路径信息,经过控制决策系统分析和判断,由执行系统控制直流电机给出合适的转速,同时控制舵机给出合适的转角,从而控制智能车稳定、快速地行驶。 图2.1 1.2. 系统设计 参赛小车将电感采集到的电压信号,经滤波,整流后输入到XS128单片机,用光电编码器获得实时车速,反馈到单片机,实现完全闭环控制。速度电机采用模糊控制,舵机采用PD控制,具体的参数由多次调试中获得。考滤到小车设计的综合性很强,涵盖了控制、传感、电子、电气、计算机和机械等多个学科领域,因此我们采用了模块化设计方法,小车的系统框图如图2.2。

第五届全国大学生智能汽车竞赛技术报告 图2.2 1.3. 整车外观 图2.3

1.4. 赛车的基本参数 智能车竞赛所使用的车模是东莞市博思公司生产的G768型车模,由大赛组委会统一提供,是一款带有摩擦式差速器后轮驱动的电动模型车。车模外观如图3.1。车模基本参数如表3.1。 图3.1 表3.1车模基本参数 1.5. 赛车前轮定位参数的选定

第五届全国大学生智能汽车竞赛技术报告 现代汽车在正常行驶过程中,为了使汽车直线行驶稳定,转向轻便,转向后能自动回正,减少轮胎和转向系零件的磨损等,在转向轮、转向节和前轴之间须形成一定的相对安装位置,叫车轮定位,其主要的参数有:主销后倾、主销内倾、车轮外倾和前束。模型车的前轮定位参数都允许作适当调整,故此我们将自身专业课所学的理论知识与实际调车中的赛车状况相结合,最终得出赛车匹配后的前轮参数[6]。 1.5.1. 主销后倾角 主销后倾角是指在纵向平面内主销轴线与地面垂直线之间的夹角γ,如图3-2。模型车的主销后倾角可以设置为0、 2°?3°、 4°?6°,可以通过改变上横臂轴上的黄色垫片来调整,一共有四个垫片,前二后二时为0°,前一后三为2°?3°,四个全装后面时为4°?6°。 由于主销后倾角过大时会引起转向沉重,又因为比赛所用舵机特性偏软,所以不宜采用大的主销后倾角,以接近0°为好,即垫片宜安装采用前二后二的方式,以便增加其转向的灵活性。如图3.3。 图3.2 图3.3 1.5. 2. 主销内倾角 主销内倾角是指在横向平面内主销轴线与地面垂直线之间的夹角β,如图3.4,它的作用也是使前轮自动回正。对于模型车,通过调整前桥的螺杆的长度可以改变主销内倾角的大小,由于前轴与主销近似垂直的关系,故主销内倾角

操作系统概念第七版答案含编程代码

solutions to the exercises Chapter 1 1.1 In a multiprogramming and time-sharing environment, several users share the system simultaneously. This situation can result in various security problems. a. What are two such problems? b. Can we ensure the same degree of security in a time-shared machine as in a dedicated machine? Explain your answer. Answer: a. Stealing or copying one’s programs or data; using system resources (CPU, memory, disk space, peripherals) without proper accounting. b. Probably not, since any protection scheme devised by humans can inevitably be broken by a human, and the more complex the scheme, the more difficult it is to feel confident of its correct implementation. 1.2 The issue of resource utilization shows up in different forms in different types of operating systems. List what resources must be managed carefully in the following settings: a. Mainframe or minicomputer systems b. Workstations connected to servers c. Handheld computers Answer: a. Mainframes:memory and CPU resources, storage, network bandwidth. b. Workstations: memory and CPU resouces c. Handheld computers: power consumption, memory resources. 1.3 Under what circumstances would a user be better off using a timesharing system rather than a PC or single-user workstation? Answer: When there are few other users, the task is large, and the hardware is fast, time-sharingmakes sense. The full power of the system can be brought to bear on the user’s problem. The problemcan be solved faster than on a personal computer. Anothe r case occurs when lots of other users need resources at the same time. A personal computer is best when the job is small enough to be executed reasonably on it and when performance is sufficient to execute the program to the user’s satisfaction. 1.4 Which of the functionalities listed below need to be supported by the operating system for the following two settings: (a) handheld devices and (b) real-time systems. a. Batch programming b. Virtual memory c. Time sharing Answer: For real-time systems, the operating system needs to support virtual memory and time sharing in a fair manner. For handheld systems,the operating system needs to provide virtual memory, but does not need to provide time-sharing. Batch programming is not necessary in both settings. 1.5 Describe the differences between symmetric and asymmetric multiprocessing.What are three advantages and one disadvantage of multiprocessor systems? Answer: Symmetric multiprocessing treats all processors as equals, and I/O can be processed on any CPU. Asymmetric multiprocessing has one master CPU and the remainder CPUs are slaves. The master distributes tasks among the slaves, and I/O is usually

飞思卡尔MC9S12XS128单片机中断优先级设置简易教程

本教程试图用最少的时间教你飞思卡尔XS128单片机的中断优先级设置方法和中断嵌套的使用,如果是新手请先学习中断的基本使用方法。 先来看看XS128 DataSheet 中介绍的相关知识,只翻译有用的: 七个中断优先级 每一个中断源都有一个可以设置的级别 高优先级中断的可以嵌套低优先级中断 复位后可屏蔽中断默认优先级为1 同一优先级的中断同时触发时,高地址(中断号较小)的中断先响应 注意:高地址中断只能优先响应,但不能嵌套同一优先级低地址的中断 下面直接进入正题,看看怎么设置中断优先级: XS128中包括预留的中断一共有128个中断位,如果为每个中断都分配一个优先级寄存器的话会非常浪费资源,因此飞思卡尔公司想出了这样一种办法:把128个中断分为16个组,每组8个中断。每次设置中断时,先把需要的组别告诉某个寄存器,再设置8个中断优先寄存器的某一个,这样只需9个寄存器即可完成中断的设置。 分组的规则是这样的:中断地址位7到位4相同的中断为一组,比如MC9SX128.h中 这些中断的位7到位3都为D,他们就被分成了一组。0~F正好16个组。

INT_CFADDR就是上面说到的用来设置组别的寄存器: 我们需要设置某个组别的中断时,只要写入最后8位地址就行了,比如设置SCI0的中断优先级,就写入0xD0。 设置好组别之后,我们就要该组中相应的中断进行设置,设置中断的寄存器为 这其实是一组寄存器,一共有8个,每个都代表中断组中的一个中断。对应规则是这样的:中断地址的低四位除以2 比如还是SCI0,低四位是6,除以二就是3,那么我们就需要设置INT_CFDATA3 往INT_CFDATAx中写入0~7就能设置相应的中断优先级了 拿我本次比赛的程序来举个例子:我们的程序中需要3个中断:PIT0,PORTH,SCI0。PIT0定时检测传感器数值,PORTH连接干簧管进行起跑线检测,SCI0接收上位机指令实现急停等功能。因此中断优先级要SCI0>PORTH>PIT0。 我们先要从头文件中找出相应中断的地址: PIT0【7:4】位为7,选择中断组: INT_CFADDR=0x70;

飞思卡尔项目书

飞思卡尔智能车比赛项目 参赛时间:2011.7.16 — 2011.7.20 赛前准备时间:2010.7 ---2011.7 飞思卡尔智能车比赛简介: 为加强大学生实践、创新能力和团队精神的培养,促进高等教育教学改革,受教育部高等教育司委托(教高司函[2005]201号文,附件1),由教育部高等学校自动化专业教学指导分委员会(以下简称自动化分教指委)主办全国大学生智能汽车竞赛。该竞赛是以智能汽车为研究对象的创意性科技竞赛,是面向全国大学生的一种具有探索性工程实践活动,是教育部倡导的大学生科技竞赛之一。该竞赛以“立足培养,重在参与,鼓励探索,追求卓越”为指导思想,旨在促进高等学校素质教育,培养大学生的综合知识运用能力、基本工程实践能力和创新意识,激发大学生从事科学研究与探索的兴趣和潜能,倡导理论联系实际、求真务实的学风和团队协作的人文精神,为优秀人才的脱颖而出创造条件。 该竞赛由竞赛秘书处设计、规范标准硬软件技术平台,竞赛过程包括理论设计、实际制作、整车调试、现场比赛等环节,要求学生组成团队,协同工作,初步体会一个工程性的研究开发项目从设计到实现的全过程。该竞赛融科学性、趣味性和观赏性为一体,是以迅猛发展、前景广阔的汽车电子为背景,涵盖自动控制、模式识别、传感技术、电子、电气、计算机、机械与汽车等多学科专业的创意性比赛。该竞赛规则透明,评价标准客观,坚持公开、公平、公正的原则,力求向健康、普及、持续的方向发展。 该竞赛以飞思卡尔半导体公司为协办方,得到了教育部相关领导、飞思卡尔公司领导与各高校师生的高度评价,已发展成全国30个省市自治区近300所高校广泛参与的全国大学生智能汽车竞赛。2008年起被教育部批准列入国家教学质量与教学改革工程资助项目中科技人文竞赛之一(教高函[2007]30号文)。 全国大学生智能汽车竞赛原则上由全国有自动化专业的高等学校(包括港、澳地区的高校)参赛。竞赛首先在各个分赛区进行报名、预赛,各分赛区的优胜队将参加全国总决赛。每届比赛根据参赛队伍和队员情况,分别设立光电组、摄像头组、电磁组、创意组等多个赛题组别。每个学校可以根据竞赛规则选报不同组别的参赛队伍。全国大学生智能汽车竞赛组织运行模式贯彻“政府倡导、专家主办、学生主体、社会参与”的16字方针,充分调动各方面参与的积极性。 全国大学生智能汽车竞赛一般在每年的10月份公布次年竞赛的题目和组织方式,并开始接受报名,次年的3月份进行相关技术培训,7月份进行分赛区竞赛,8月份进行全国总决赛。 飞思卡尔智能车比赛技术要求:

飞思卡尔智能车比赛个人经验总结

先静下心来看几篇技术报告,可以是几个人一起看,边看边讨论,大致了解智能车制作的过程及所要完成的任务。 看完报告之后,对智能车也有了大概的了解,其实总结起来,要完成的任务也很简单,即输入模块——控制——输出。 (1)输入模块:各种传感器(光电,电磁,摄像头),原理不同,但功能都一样,都是用来采集赛道的信息。这里面就包含各种传感器的原理,选用,传感器电路的连接,还有传感器的安装、传感器的抗干扰等等需要大家去解决的问题。 (2)控制模块:传感器得到了我们想要的信息,进行相应的AD转换后,就把它输入到单片机中,单片机负责对信息的处理,如除噪,筛选合适的点等等,然后对不同的赛道信息做出相应的控制,这也是智能车制作过程中最为艰难的过程,要想出一个可行而又高效的算法,确实不是一件容易的事。这里面就涉及到单片机的知识、C语言知识和一定的控制算法,有时为了更直观地动态控制,还得加入串口发送和接收程序等等。 (3)输出模块:好的算法,只有通过实验证明才能算是真正的好算法。经过分析控制,单片机做出了相应的判断,就得把控制信号输出给电机(控制速度)和舵机(控制方向),所以就得对电机和舵机模块进行学习和掌握,还有实现精确有效地控制,又得加入闭环控制,PID算法。 明确了任务后,也有了较为清晰的控制思路,接下来就着手弄懂每一个模块。虽然看似简单,但实现起来非常得不容易,这里面要求掌握电路的知识,基本的机械硬件结构知识和单片机、编程等计算机知识。最最困难的是,在做的过程中会遇到很多想得到以及想不到的事情发生,一定得细心地发现问题,并想办法解决这些问题。 兴趣是首要的,除此之外,一定要花充足的时间和精力在上面,毕竟,有付出就会有收获,最后要明确分工和规划好进度。

操作系统概念课后习题答案整理.doc

1.1在多道程序和分时环境中,多个用户同时共享一个系统,返种情冴导致多种安全问题。a. 列出此类的问题b.在一个分时机器中,能否确保像在与用机器上一样的安全度?并解释乀。 Answer:a.窃叏戒者复制某用户癿程序戒数据;没有合理癿预算来使用资源(CPU,内存,磁盘空闱,外围设备)b.应该丌行,因为人类设计癿仸何保护机制都会丌可避兊癿被另外癿人所破译,而丏径自信癿认为程序本身癿实现是正确癿是一件困难癿亊。 1.2资源的利用问题在各种各样的操作系统中出现。试例丼在下列的环境中哪种资源必须被严栺的管理。(a)大型电脑戒迷你电脑系统(b)不服务器相联的工作站(c)手持电脑 Answer: (a)大型电脑戒迷你电脑系统:内存呾CPU资源,外存,网络带宽(b)不服务器相联癿工作站:内存呾CPU资源(c)手持电脑:功率消耗,内存资源 1.3在什举情冴下一个用户使用一个分时系统比使用一台个人计算机戒单用户 工作站更好? Answer:当另外使用分时系统癿用户较少时,仸务十分巨大,硬件速度径快,分时系统有意丿。充分利用该系统可以对用户癿问题产生影响。比起个人电脑,问题可以被更快癿解决。迓有一种可能収生癿情冴是在同一时闱有许多另外癿用户在同一时闱使用资源。当作业足够小,丏能在个人计算机上合理癿运行时,以及当个人计算机癿性能能够充分癿运行程序来达到用户癿满意时,个人计算机是最好癿,。 1.4在下面丼出的三个功能中,哪个功能在下列两种环境下,(a)手持装置(b)实

时系统需要操作系统的支持?(a)批处理程序(b)虚拟存储器(c)分时 Answer:对二实时系统来说,操作系统需要以一种公平癿方式支持虚拟存储器呾分时系统。对二手持系统,操作系统需要提供虚拟存储器,但是丌需要提供分时系统。批处理程序在两种环境中都是非必需癿。 1.5描述对称多处理(SMP)和非对称多处理乀间的区别。多处理系统的三个优点和一个缺点? Answer:SMP意味着所以处理器都对等,而丏I/O可以在仸何处理器上运行。非对称多处理有一个主处理器控制系统,不剩下癿处理器是随从关系。主处理器为从处理器安排工作,而丏I/O也叧在主处理器上运行。多处理器系统能比单处理器系统节省资金,返是因为他们能共享外设,大容量存储呾电源供给。它们可以更快速癿运行程序呾增加可靠性。多处理器系统能比单处理器系统在软、硬件上也更复杂(增加计算量、觃模经济、增加可靠性) 1.6集群系统不多道程序系统的区别是什举?两台机器属二一个集群来协作提 供一个高可靠性的服务器的要求是什举? Answer:集群系统是由多个计算机耦合成单一系统幵分布二整个集群来完成计算仸务。另一方面,多道程序系统可以被看做是一个有多个CPU组成癿单一癿物理实体。集群系统癿耦合度比多道程序系统癿要低。集群系统通过消息迕行通信,而多道程序系统是通过共享癿存储空闱。为了两台处理器提供较高癿可靠性服务,两台机器上癿状态必项被复制,幵丏要持续癿更新。当一台处理器出现敀障时,另一台处理器能够接管敀障处理癿功能。 1.7试区分分布式系统(distribute system)的客户机-服务器(client-server)模型不对等系统(peer-to-peer)模型

飞思卡尔寄存器整理

S12的输入/输入端口(I/O口) I/O端口功能 可设置为通用I/O口、驱动、内部上拉/下拉、中断输入等功能。 设置I/O口工作方式的寄存器有: DDR、IO、RDR、PE、IE和PS。 DDR:设定I/O口的数据方向。 IO :设定输出电平的高低。 RDR:选择I/O口的驱动能力。 PE:选择上拉/下拉。 IE:允许或禁止端口中断。 PS:1、中断允许位置位时,选择上升沿/下降沿触发中断;2、中断禁止时且PE有效时,用于选择上拉还是下拉。 I/O端口设置 1、A口、B口、E口寄存器 (1)数据方向寄存器DDRA、DDRB、DDRE DDRA、DDRB、DDRE均为8位寄存器,复位后其值均为0。 当DDRA=0、 DDRB=0、 DDRE=0 时A口、B口和E口均为输入口。 否则,A口、B口、E口为输出口。当DDRA、DDRB、DDRE的任何一位置1时,则该位对应的引脚被设置为输出。 例如,将A口设置为输出口,则其C语言程序的语句为:DDRA=0xff; (2)A口、B口、E口上拉控制寄存器PUCR PUCR为8位寄存器,复位后的值为0。当PUPAE、PUPBE、PUPEE被设置为1时,A口、B口、E口具有内部上拉功能;为0时,上拉无效。当A口、B 口、E口为地址/数据总线时,PUPAE和PUPBE无效。 (3)A口、B口、E口降功率驱动控制寄存器RDRIV RDRIV为8位寄存器,复位后的值为0,此时,A口、B口、E口驱动保持全功率;当RDPA、RDPB、RDPE为1时, A口、B口、E口输出引脚的驱动功率下降 (4)数据寄存器PORTA、PORTB、PORTE PORTA、PORTB、PORTE均为8位寄存器,复位后的值为0,端口引脚输出低电平;要使引脚输出高电平,相应端口对应位应该置1。 由于PE0是/XIRQ、PE1是IRQ,因此,PE0和PE1只能设置为输入。