Verilog流水灯实验报告

流水灯实验报告

实验二 流水灯

一、 实验目的

学会编写一个简单的流水灯程序并掌握分频的方法。熟悉Modelsim 仿真软件的使用。

二、 实验要求

用Quartus 编写流水灯程序,在Modelsim 软件中进行仿真。

三、 实验仪器和设备

1、 硬件:计算机

2、 软件:Quartus 、Modelsim 、(UE )

四、 实验内容

1、 将时钟周期进行分频。

2、 编写Verilog 程序实现LED 等依次亮灭,用Modelsim 进行仿真,绘制波形图。

五、 实验设计

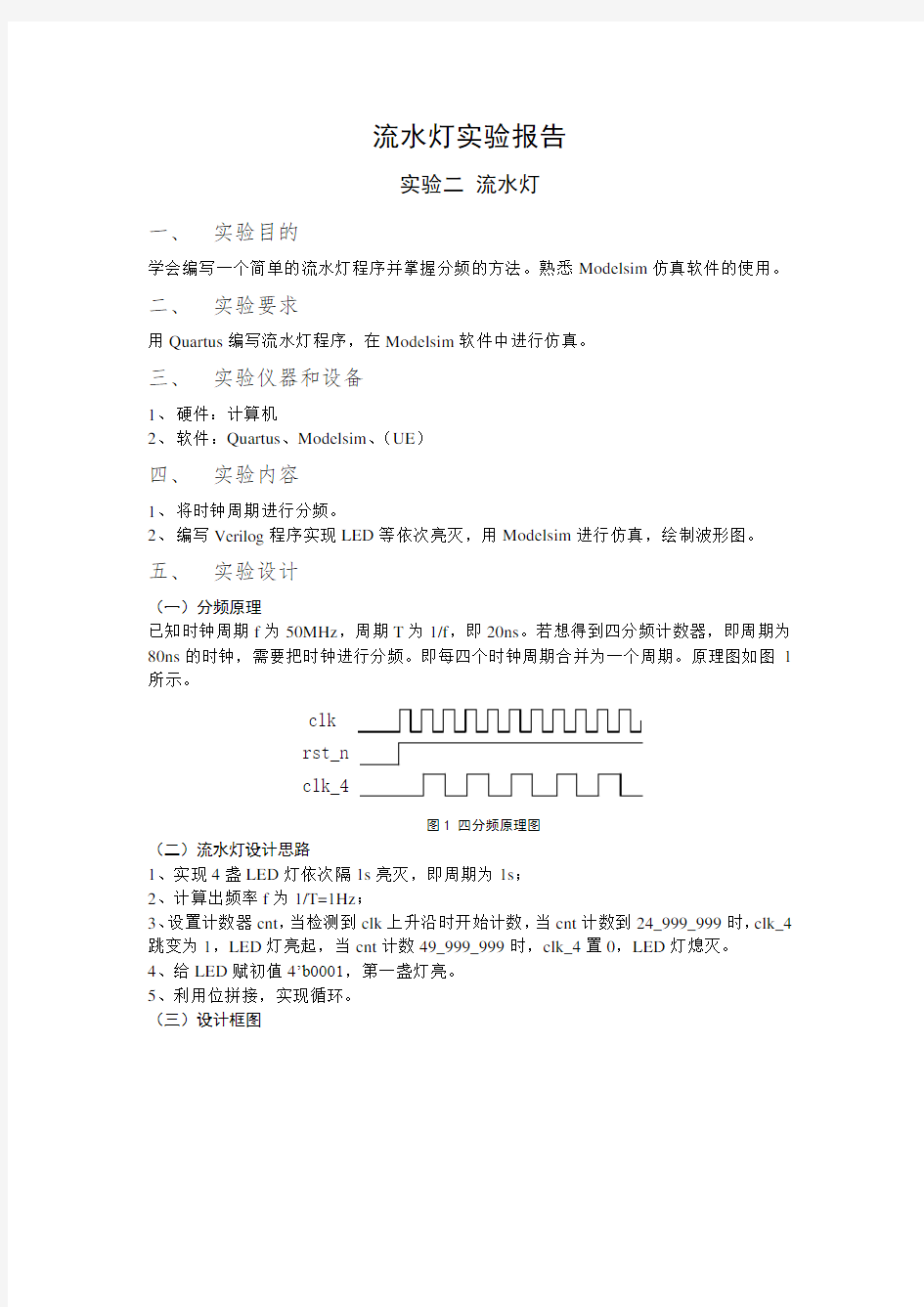

(一)分频原理

已知时钟周期f 为50MHz ,周期T 为1/f ,即20ns 。若想得到四分频计数器,即周期为80ns 的时钟,需要把时钟进行分频。即每四个时钟周期合并为一个周期。原理图如图1所示。

rst_n

clk

clk_4

图1 四分频原理图

(二)流水灯设计思路

1、实现4盏LED 灯依次隔1s 亮灭,即周期为1s ;

2、计算出频率f 为1/T=1Hz ;

3、设置计数器cnt ,当检测到clk 上升沿时开始计数,当cnt 计数到24_999_999时,clk_4跳变为1,LED 灯亮起,当cnt 计数49_999_999时,clk_4置0,LED 灯熄灭。

4、给LED 赋初值4’b0001,第一盏灯亮。

5、利用位拼接,实现循环。

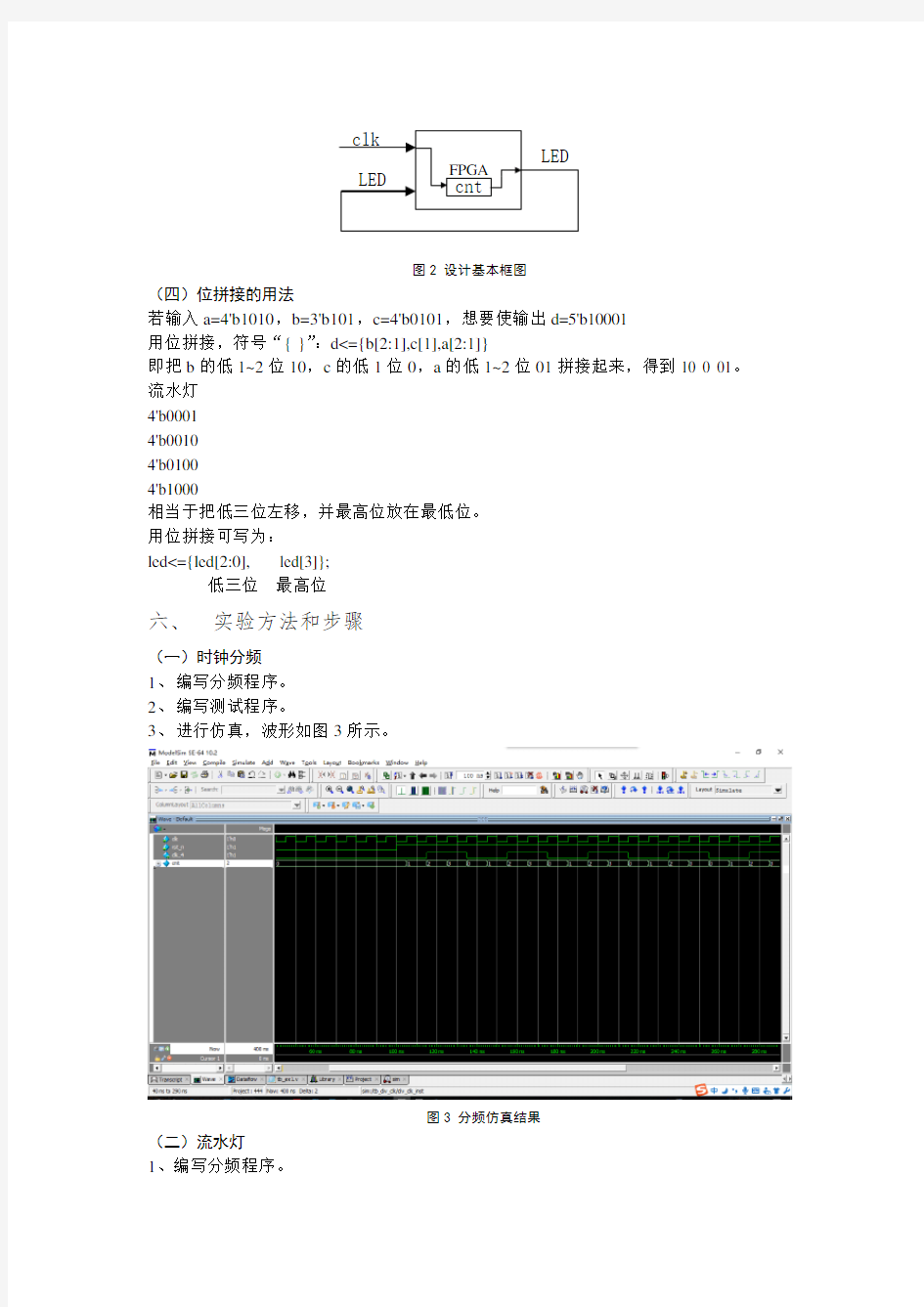

(三)设计框图

FPGA

clk

cnt

LED LED

图2 设计基本框图

(四)位拼接的用法

若输入a=4'b1010,b=3'b101,c=4'b0101,想要使输出d=5'b10001

用位拼接,符号“{ }”:d<={b[2:1],c[1],a[2:1]}

即把b 的低1~2位10,c 的低1位0,a 的低1~2位01拼接起来,得到10 0 01。 流水灯

4'b0001

4'b0010

4'b0100

4'b1000

相当于把低三位左移,并最高位放在最低位。

用位拼接可写为:

led<={led[2:0], led[3]};

低三位 最高位

六、 实验方法和步骤

(一)时钟分频

1、 编写分频程序。

2、 编写测试程序。

3、 进行仿真,波形如图3所示。

图3 分频仿真结果

(二)流水灯

1、编写分频程序。

3、编写测试程序。

3、进行仿真,为了节约时间和方便观察波形,将计数器值分别改为2

4、49跳转。波形如图4所示。

图4流水灯仿真结果

七、实验参考程序

(一)时钟分频

1、程序文件

module div_clk( lk(clk),

.rst_n(rst_n),

.clk_4(clk_4)

);

endmodule

(二)流水灯

1、程序文件

module LSD( lk(clk),

.rst_n(rst_n),

.led(led)

);

endmodule

八、实验小结

1、做实验要养成良好的习惯,每次做实验时,都要建立一个新的文件夹存放实验所需

的程序文件,为仿真时添加文件做准备,也方便以后的查找和使用。

2、写程序前要想清楚电路实现原理,根据所学数电知识对各个元器件进行控制。

3、写程序时注意排版美观整洁,同时注意添加注释。

4、注意程序中模块名要和文件名一致,否则程序报错,无法编译通过。

5、仿真时,可以选择不同的进制。在想要更改的地方右键,选择【Radix】,其中【Binary】

为二进制。如图5所示。

图5更改进制

6、在流水灯仿真时,LED灯的波形一开始是错误的,因为程序中只检测了上升沿

always@(posedge clk) ,加上下降沿检测always@(posedge clk or negedge clk) ,即可解决问题,成功绘制波形图。