Intel XScale(TM) 嵌入式微处理器简介

Intel XScale?嵌入式微处理器简介

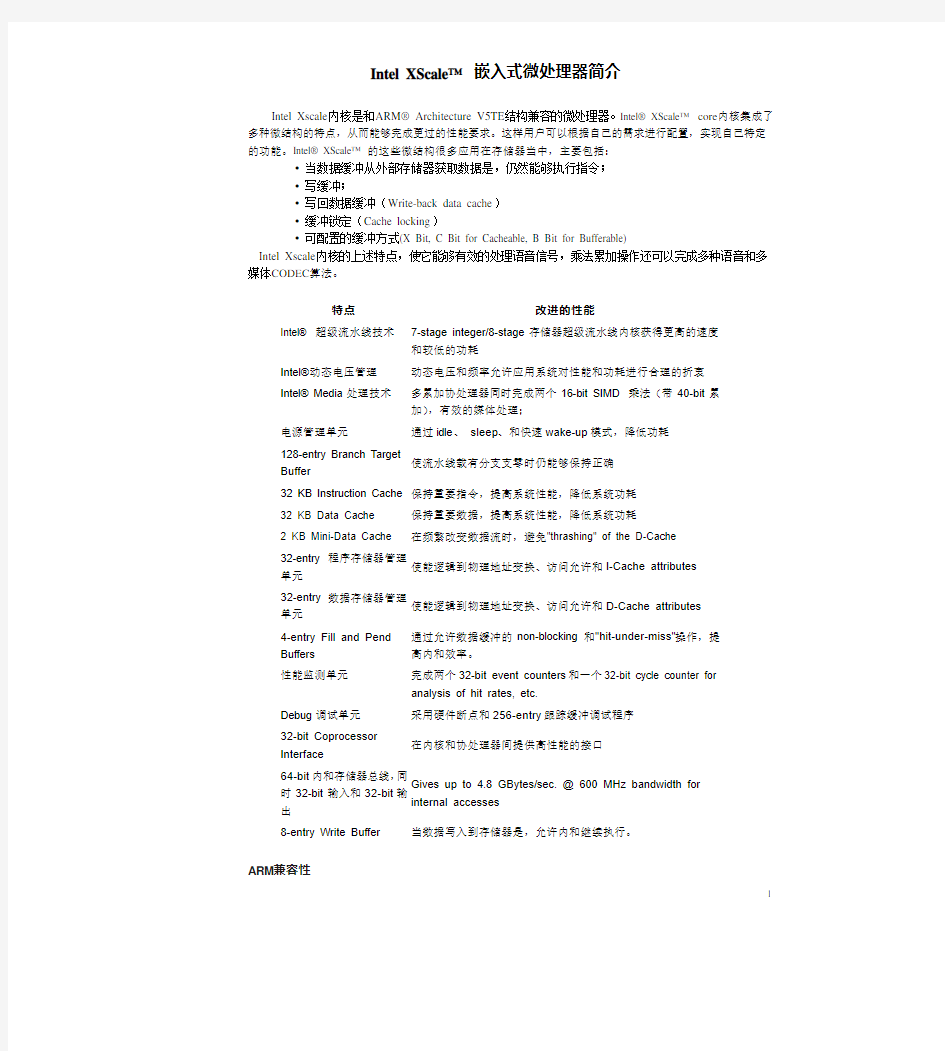

Intel Xscale内核是和ARM? Architecture V5TE结构兼容的微处理器。Intel? XScale?core内核集成了多种微结构的特点,从而能够完成更过的性能要求。这样用户可以根据自己的需求进行配置,实现自己特定的功能。Intel? XScale?的这些微结构很多应用在存储器当中,主要包括:

?当数据缓冲从外部存储器获取数据是,仍然能够执行指令;

?写缓冲;

?写回数据缓冲(Write-back data cache)

?缓冲锁定(Cache locking)

?可配置的缓冲方式(X Bit, C Bit for Cacheable, B Bit for Bufferable)

Intel Xscale内核的上述特点,使它能够有效的处理语音信号,乘法累加操作还可以完成多种语音和多媒体CODEC算法。

特点改进的性能

Intel? 超级流水线技术 7-stage integer/8-stage存储器超级流水线内核获得更高的速度

和较低的功耗

Intel?动态电压管理 动态电压和频率允许应用系统对性能和功耗进行合理的折衷

Intel? Media处理技术 多累加协处理器同时完成两个16-bit SIMD 乘法(带40-bit累

加),有效的媒体处理;

电源管理单元 通过idle、 sleep、和快速wake-up模式,降低功耗

128-entry Branch Target

Buffer

使流水线载有分支支零时仍能够保持正确

32 KB Instruction Cache 保持重要指令,提高系统性能,降低系统功耗

32 KB Data Cache 保持重要数据,提高系统性能,降低系统功耗

2 KB Mini-Data Cache 在频繁改变数据流时,避免"thrashing" of the D-Cache

32-entry 程序存储器管理

单元

使能逻辑到物理地址变换、访问允许和I-Cache attributes 32-entry数据存储器管理

单元

使能逻辑到物理地址变换、访问允许和D-Cache attributes

4-entry Fill and Pend Buffers 通过允许数据缓冲的non-blocking和"hit-under-miss"操作,提高内和效率。

性能监测单元 完成两个32-bit event counters和一个32-bit cycle counter for

analysis of hit rates, etc.

Debug调试单元 采用硬件断点和256-entry跟踪缓冲调试程序

32-bit Coprocessor

Interface

在内核和协处理器间提供高性能的接口

64-bit内和存储器总线,同时32-bit输入和32-bit输出 Gives up to 4.8 GBytes/sec. @ 600 MHz bandwidth for internal accesses

8-entry Write Buffer 当数据写入到存储器是,允许内和继续执行。

ARM兼容性

1

ARM* Version 5 (V5) Architecture在ARM* Version 4版本基础上增加了很多功能,其中包括浮点指令。Intel? XScale?内核应用ARM* V5的整型指令,但不提供浮点指令的硬件支持。Intel? XScale?内核提供ARM* V5T Thumb指令集合ARM* V5E DSP扩展。为了进一步提高多媒体处理能力, Intel? XScale?内核作为Intel? Media Processing技术的第一个应用,还增加了乘法累加功能。这些新的操作映射到ARM写处理器空间,和StrongARM兼容。为了能够满足特定硬件的需要,操作系统需要尽心适当的调整。

Intel? XScale?内核的结构框图

Figure 1给出了Intel? XScale?内核的结构框图,该内核支持:

l 7 stage integer/8 stage memory流水线操作;

l 32Kbyte指令缓冲(32 ways, lockable by line);

l 一个32Kbyte数据缓冲(32 ways,write-back or write-through);

l 一个2Kbyte mini-data cache (two ways);

l 一个分支目标缓冲 a branch target buffer (used by the processor core’s branch prediction logic);

l 性能管理单元(Performance Monitoring Unit);

l 编辑调试接口(debug port with Branch History table and hardware breakpoints);

l 电源管理控制器(Power Management Controller)和JTAG

此外,内核还有数据、存储器管理单元(MMU)、带有32传输缓冲( 32 Entry Translation look aside Buffers (TLBs))等。应用处理器特殊的结构设计提供了灵活的高性能::

下图给出了Intel? XScale?内核的主要功能框图,下面概略的介绍个功能模块:

2

Multiply/Accumulate (MAC)

MAC单元支持乘法累加操作,改进了几个硬件结构以支持语音代码算法。包括40-bit累加器和支持16-bit packed data。

Memory Management

Intel? XScale?内核采用存储器管理单元结构,具体参见ARM* Architecture Reference Manual。 MMU 提供访问保护和虚拟到物理地址的变换。MMU构架还确定指令和数据cache的分类原则。由页配置属性决定的划分方法:

?区分代码为cacheable还是non-cacheable;

?在mini-data cache或data cache中选择;

?write-back或write-through数据缓冲;

?使能数据写分配原则;

?enabling the write buffer to coalesce stores to external memory

Performance Monitoring

Intel? XScale?内核增加了两个性能监测控志气,监测在Intel? XScale?内核的各种事件的发生。该事件管理器允许软件开发人员测试cache的效率,监测系统平静并降低程序的重叠缓存等问题。

Power Management

Intel? XScale?内核集成了一个电源和时钟管理单元,能够辅助ASSP控制时钟,管理电源。

Debug

Intel? XScale?内核通过两个指令寻址断点寄存器支持软件调试。一个数据地址断点寄存器,一个数据地址屏蔽断点寄存,一个mini instruction cache和一个跟踪缓冲器。Intel? XScale?内核通过JTAG口进行调试。

Intel? XScale? Enhancements(改进)

Intel PXA250应用处理器的Intel XScale内核是在Intel StrongARM处理器Intel SA-1100和 Intel

SA-1110应用处理器基础上改进的,和Intel SA-1100和 Intel SA-1110应用处理器不同的是Intel PXA250

3

应用处理器采用Thumb代码压缩技术。RISC结构有个弱点就是代码密度问题,代码密度描述了需要存储代码(也就是软件)的空间。RISC芯片通常情况下要比CISC (Complex Instruction Set Computing) 处理器占用更大的存储空间。Thumb技术改善了这方面的性能,代码比正常的RISC密度降低30%,该压缩由Intel PXA250应用处理器自动完成。工程师或程序员不需要更多的设计考虑。

另一个改进的主要部分就是Intel Xscale内核拥有双乘法/累加(dual-MAC)指令,MAC操作对于计算机和微处理器是一个比较新的运算模式,是从数字信号处理器(DSP)中移植过来的。而MAC操作对于语音、视频和无线应用是非常重要经常用到的。一个或两个MAC指令能够完成这些多媒体的应用,因此大大的提高了微处理器的运算能力。

Intel Xscale PXA250 Architecture

Intel PXA250微处理器是下一代手持多媒体应用处理器,基于Xscale结构的高性能低功耗微处理器,广泛应用于无线、手持和Internet设备当中。Intel PXA250内核是一个32-bit的微处理器,但是在他的结

构设计中,处理器内核部分仅占了整个芯片的15%。绝大部分区域是为了提高其性能的集成程度和增强电源管理,降低芯片甚至是系统的功耗。

Intel PXA250内核是一个Intel Xscale内核微处理器。Intel Xscale本身是一个32-bit的RISC为结构。采用先进的ARM技术,是目前世界上交流行得32-bit 嵌入式CPU。在技术上ARM和Intel Xscale两者完全兼容。因此在采用Intel PXA250应用处理器进行软件开发时,原来为ARM开发的代码完全可以进行移植,或直接在基于Intel Xscale的微处理器上运行。当然新的开发工具将会更能利用发挥Intel Xscale技术。

如图所示,Intel PXA250应用处理器包括多种外设,能够完成个人客户终端构架的基本功能。它包括集成的外围存储器控制器、串行总线、并行总线、无线和有线通信接口、扩展卡接口以及LCD显示接口等。所有这些实现了一个片上系统。在具体的用户设计时,有时只需要增加一些电池、存储器、通信子系统和LCD显示屏就可以了。从而简化并降低了软硬件的设计实现难度,降低系统的成本和功耗,加快了产品推向市场

4

产品概述

移动和无线设备方便了我们的生活,使工作小冷高。几乎每天都依赖这些先进的设备来进行各种活动。为了能够满足客户随时随地能够进行通信、访问信息。生产厂商需要采用高性能、灵活方便、稳定性好、功耗比较低的技术来满足不断增长的需求。采用Intel Xscale技术的Intel Personal Internet Client Architecture (Intel PCA)应用处理器将手持设备提升到了一个新的高度。该类型处理器采用7及流水线和更高的处理速度,先进的Intel Media和CMOS技术,以及高度集成的片上系统,使系统共耗能低。

PXA250主要特点

重点技术

l 低功耗、高性能,32bitXScale内核CPU(200、300、400MHz);

l ARM结构,V.5TE兼容且与Intel的SA-100处理器兼容;

l Intel超流水线RISC技术;

l 40-bit累加器和16-bit的SIMD,改善语音/视频性能;

低功耗

l 低功耗和Turbo两种工作模式,是电池寿命达到最理想;

l 32 KB数据和32 KB指令高速缓冲存储器

l 用于数据流的2 KB mini数据缓存;

IO扩展

l 带100MHz存储总线的集成的存储器和PCMCIA/CompactFlash控制器,16-bit或32-bit ROM/Flash/SRAM 六段, 16-bit或32-bit SDRAM, SMROM四段,以及为辅助功能及扩展考虑得

PCMCIA和CompactFlash接口;

l 系统控制模块包括17的专用中断IO口、适时时钟、看门狗和定时器、电源管理控制器、终端控制器、复位控制器以及两个片上晶振;

无线通信

l 外设控制模块提供16通道可配置DMA控制器,集成LCD控制器(带单独的DMA支持快速彩屏),蓝牙Bluetooth* I/F,串口(IrDA, I2C, I2S, AC97, three UARTs, SPI and SSP),USB终端接口

和可扩展存储器和IO功能的支持MMC/ SD Card的接口;

l 17x17 256-pin PBGA

l 工作温度范围较大

主要功能描述

l 内核支持的频率:100 MHz - 400 MHz

l 系统存储器接口

— 100MHz SDRAM;

— 4 MB to 256 MB的SDRAM存储器;

—支持16, 64, 128, or 256 Mbit DRAM技术;

— 4 Banks of SDRAM, 每段支持64 MB存储器;

—时钟使能(1 CKE pin is provided to put the entire SDRAM interface into self

refresh)

—支持六种静态存储器(SRAM, Flash, or VLIO)

l PCMCIA/Compact Flash 卡控制接口;

l LCD控制器引脚;

l 全功能UART;

5

l 蓝牙Bluetooth UART;

l MMC 控制器引脚;

l SSP Pins

l USB客户端引脚;

l AC’97控制器引脚;

l 标准UART引脚;

l I2C控制器引脚;

l PWM引脚;

l 15专用GPIOs引脚;

l 集成JTAG。

流水线操作

流水线的前两步是从存储器或指令缓冲器装载一个16-bit或32-bit的Intel XScale 处理器指令,该任务需要两个流水线状态(two pipeline stages),主要因为存储器芯片相对较慢。应用处理器还需要在Branch Target Buffer (BTB)中查找branche。

下一个状态是对32-bit RISC指令进行译码,第四个状态是从板上寄存器装载数据,由于数据已经存放在处理器的寄存器当中,该过程比较快。第五个状态执行指令、第六级、保存状态。最后、将结果协会到存储器缓冲当中。从而完成一个指令操作。

在指令流水线执行过程中,也会有一些以外的情况产生。一种情况就是有分支指令,程序改变软件

6

的过程。另一种情况就是“乘法-累加”MAC指令。由于MAC指令比较复杂,在执行时要花费不止一个周期。MAC指令采用自己的流水线,一个MAC指令完成流水线的四级后,进入到自己的运算流水线。另一个例外情况就是“cache miss”—Intel PXA250处理器要求的条件在片上擦catch不能找到。

Cache Performance Tweaks

处理器的缓冲能够全面的提高执行效率,理想情况下,所有程序的数据都需要在缓存当中。然而,经常有的数据装不到缓存当中,将会因为"cache miss"导致性能下降。这就要花费一定的时间来提取外部存储器的数据。通常情况下,除了提高cache的大小以外,其他性能基本是固定的。在负担比较重的情况下cache更容易产生"cache miss"。Intel PXA250应用处理器采用“hit-under-miss”技术使数据移动尽可能的均匀,避免了"miss plenty" 的发生。

对于大多数微处理器(当cache miss时强制停止指令执行)而言,Intel PXA250应用处理器的

“hit-under-miss”功能允许当处理器处理cache miss时完成其它的任务。他的流水线似乎由其他指令填充的,并不需要停止等待。而其他的芯片就需要停止微处理器执行,直到cache miss 被处理完。

节电技术

类似于Intel PXA250的嵌入式微处理器都有良好的性能,但实际上如果他们实现高性能,就要消耗很大的能量。Intel PXA250处理器采用先进的技术,在保证高性能的同时,能功耗也相当的低。首先也是最重要的节能技术就是Intel PXA250采用0.18-micron, six-layer-metal complementary metal-oxide semiconductor CMOS 技术。该技术在其他Intel的芯片生产中已经得到了验证。另一个主要特点就是Intel PXA250处理器的电源管理模式,采用自动始终门控方式。该芯片有几百万个晶体管,但并不是完全总在工作。管理单元关闭不被”gating off”利用的单元。处理器尽可能的是整个芯片保持安静状态。芯片的主要部分完全可以一个时钟周期处于空闲状态,下一个周期全部激活。(one 400-millionth of a second)

丰富的外设扩展

即便是最快的处理企业不能独立工作,需要有存储器、外设控制器以及相应的支持电路一起协调工作。在低功耗设备中,这些辅助构建可能要占据芯片的绝大部分空间。内嵌式的外设相对而言比较简单灵活,功耗耕地。Intel PXA250应用处理器采用内嵌式外设,芯片上集成了多种外设。

USB控制器

7

Intel PXA250’s USB接口提供快速灵活的用户数据传输借口,能够方便的和PC机进行数据通信。同时两个基于Intel PXA250应用处理器的通信设备或终端可以通过USB总线进行数据传输。编程信息、网络内容、固件更新、验证码等都可以进行传输设定。

基带接口Baseband Interface, UARTs, and More

对于无线通信,Intel PXA250应用处理器为用户提供了所有可以选择的方案,使用户设计更加灵活Bluetooth*, 802.11b,infrared和其他无线接口。Intel PXA250所支持的无线标准都是异步串行通信标准,调用异步串行通信收发器(UARTs),Intel PXA250有两个高速UART,最高速度可以达到1.84 MHz,对于Bluetooth其他高级无线标准是足够了。

还有Inter-Integrated Circuit (I2C)和 Inter-Integrated Circuit Sound (I2S),提供低成本,少引脚接口的通信方式。Service Switching Point (SSP),Service Provider Interface (SPI)和mWire接口都集成在Intel PXA250应用处理器上。而且IrDA远程控制通信的红外接口也集成在该芯片上。此外, 16GPIO可以独立编程,根据用户具体的需求进行配置。

LCD显示控制器

便携设备的一个引人的特点就是他的现实功能。Intel PXA250应用处理器支持多种显示功能。在该芯片上集成了LCD控制器。从而使设计的系统可以降低芯片的数量,减小功耗。此外LCD控制器还有双通道的DMA单元,能够在不影响处理器性能的情况下,完成良好的现实功能。Intel PXA250 LCD控制器直至多种单/双(single- and dual-panel)的LCD显示,达到800 x 600像素。支持256灰度等级的单色显示屏和正负彩色平(带有65,536 color values)。参考下图的.

Memory Controller

每个处理器都有存储单元,但未必每个处理器都有自己的存储器控制器。Intel PXA250应用处理器有一个32-bit的存储器控制器,使运算与最高速。他处理同步DRAM (SDRAM),同步RAM (SRAM),Intel’s Wireless Flash memory器件等。高端的系统通常情况下采用上述器件结合。为了减小空间,节省能量Intel PXA250还可以运行在16-bit模式。

MMC/SD & PCMCIA/CF Controller

主要的存储器并不驻留在SDRAM、flash或SRAM上,当今便携设备中用户需要加入自己的存储设备或其他外设。比如PCMCIA卡。为此,Intel PXA250应用处理器有PCMCIA/SD接口,支持绝大多数标准的存储器和外设模块。 PCMCIA是一个较老的但被广泛采用的存储器接口标准,尽管在存储器上很少用,但对于Ethernet cards、802.11b wireless-networking cards、miniature digital cameras和hard disk 涌出还是比较广发。这些接口还可以用作CompactFlash? cards接口。该芯片还支持SD (secure digital) cards以及MMC (multimedia cards)等。为用户外围存储扩展提供了极大的方便。

8

Intel? SA-1110处理器

Intel? SA-1110处理器是为便携式无线多媒体设备开发的高性能、低功耗处理器。该产品的主要特点:

l 先进的技术使得该芯片具有超越的性能、较高的集成度和低功耗的特点,是和应用于便携设备、移动电话以及其他无线多媒体设备;

l 速度达到100 MHz的存储器总线和灵活的存储器控制器,支持SDRAM, SMROM以及variable-latency I/O设备,为系统设计提供了灵活性和较高的存储带宽;

l 丰富的开发环境,降低了新产品的开发难度,缩短了产品对象市场的时间。

Intel SA-1110是一个高度集成的32-bit Intel? StrongARM处理器,采用先进的设计和处理技术的ARM构架。Intel SA-1110软件和ARM v.4结构兼容,而且应用了高性能的微结构(该结构采用先进的Intel处理技术)。Intel SA-1110提供较高的性能和集成度、低的功耗、较低的价格。并有高速存储器接口、灵活的存储器控制器和处理variable-latency I/O的能力。生产厂商可以应用高性能价格比的Intel SA-1110制造出根据有竞争力的产品。

Intel SA-1110的主要构成:

l 处理器内核:处理器是带有16-Kbyte指令和数据8-Kbyte数据缓冲器、存储器管理单元、读写缓冲和512-byte mini-data cache的Intel SA-1内核;

l 存储器和PCMCIA控制模块:灵活的存储器控制器支持SDRAM、 Synchronous Mask ROM、ROM、flash、DRAM、SRAM、SRAM-like variable-latency I/O和PCMCIA控制;

l 系统控制模块:28个通用目的可中断I/O口、适时时钟、看门狗、内部定时器、电源管理控制器、中断控制器、复位控制器和两个片上晶振;

l 外设控制模块:6通道DMA控制器、LCD控制器、SDLC控制、16550兼容的UART接口、IrDA串口、同步串口、USB客户终端接口和codec接口;

l 封装形式:Intel SA-1110采用较小的256-pin mBGA封装。

Intel SA-1110系统功能框图

先进的性能和较低的功耗

当今系统设计人员面临的一个非常大的挑战,即要求系统实现较高的性能,又要维持相对较低的功耗。Intel SA-1110能够同时满足这两个方面的需求。Intel SA-1110处理器采用先进的微处理结构、先进

9

的CMOS处理技术和较大的片上存储器缓冲,从而提高了系统的性能。电源管理采用低电压处理技术,并集成了电源管理单元,降低了系统的功耗

Intel SA-1110较高的带宽允许便携设备提供快速的响应,完成诸如MP3解码、MPEG-4节马、语音处理、手写识别、软件modem和高效的Java语言解释等。从而使得基于Intel SA-1110的设备能够给用户提供更大的方便。

先进的控制提高了存储器速度、灵活多功能的I/0

Intel SA-1110先进的存储器控制器运行在100 MHz,支持4个banks的同步扩展DRAM存储器。同时还支持3个banks的静态存储器ROM、flash、SRAM和同步mask ROM (SMROM)等存储设备。存储器控制器可以采用16或32-bit总线访问存储器和数字量输入输出(SMROM只能用32-bit总线)。Intel SA-1110还支持variable-latency I/O设备,从而使它更能够满足需要其他外围兼容扩展支持的系统。例如可以和Intel? SA-1111兼容芯片或外围图像控制器借口。从而使该芯片能够满足各种便携设备的应用。

SA-1111结构框图

10

11

SA-1110/SA-1111系统结构框图

1

SA-1110/SA-1111系统结构框图2

Intel PCA

Intel PCA概要

Intel? Personal Internet Client Architecture (Intel? PCA)为下一代无线Internet设备提供优化的平台。Intel PCA特定的设计能够满足当今通信和计算环境的基本需求。并且集成了构建一个无线客户终端必要的软件和硬件。提供高度的灵活、可配置、模块化设计平台。Intel PCA使得硬件产品供应商和和服务上能够充分利用下一代无线标准的带宽,提高服务质量改善系统性能。该开放式结构支持多种操作系统和无线接口。允许集成客户的各种外设,提供一个能够增加或改变硬件和软件模块的开放式平台架构。这种开放式结构为开发者提供了开发更高性能产品和服务的机遇。

硬件构成

Intel PCA为构建无线客户终端,包括所有必要的软件和硬件部件,包括:RF、基带通信、信号处理、运算单元和多媒体处理器。他的5个主要物理构件包括:

l Intel? StrongARM处理器对于掌上设备和移动电话等设计具有很大的灵活性,它可以支持快速的存储和IO设备,以及较快的数据吞吐能力和精巧的封装形式;

l Intel? XScale?为结构以最小的功耗完成更高的性能;

l Intel? Micro Signal Architecture,一个新的DSP结构,为下一代通信设备而设计;

l Intel baseband chipsets with Intel Micro Signal Architecture支持大部分无线通信标准;

l Intel? Flash memory technology,Intel PCA利用Intel的先进的低电压,读写同时操作的flash 存储器结构,减小了开发时间。

12

主要特点

l 运算和通信子系统间开放的软硬件接口:方便第三方扩展集成和新产品的开发;

l 灵活可配置:通过增加或改变相应的模块,即可构建或设计新的系统;

l 高级的模块化设计:允许每个模块能够进行独立的测试工作,在不同系统中可以重复利用;

l 下一代标准和应用可扩展;

l 支持多种适时和应用及操作系统

l 通过可潜入的协议逻辑和软件模块,能够支持主要的cellular无线接口标准;

硬件供应商的利处:

l 缩短产品上市时间;

l 在一个平台上可以进行多种应用和标准的开发;

l 不同厂商间产品各具自己的特点;

ISV服务上的利处

l 能够更快的开发下一代无线Internet应用;

l 充分利用运算能力,提高多媒体应用的带宽;

l 提供多种标准和设备的应用服务;

l 提高服务上间的合作能力。

13

Cotulla Development Platform Introduction

无线和手持设备对于软件、硬件、固件(Firmware\middleware )的开发具有很大的挑战。软件开发者寻求设计、良好的硬件接口、优化和集成的应用软件或固件支持。该开发平台可以为开发者提供一个标准的开发框架。要想能够灵活自如的应用Intel Personal Internet Client Architecture应用处理器进行系统开发,需要有一个灵活方便的设计平台。来评估优化自己的设计。Intel?DBPXA250开发平台就是为系统设计、软件开发人员和OEMs提供一个稳定、灵活可靠的平台。该平台为开发商提供高性能、灵活的评估开发环境,包括独立应用和无线通信子系统、外设开发以及强大的操作系统支持。基于PXA250应用处理器的设备厂商开发平台,除了硬件的广泛支持外,还提供软件的优化和原有开发代码的有效移植。

该平台的主要构成:

处理器支持:

Support for Intel? PXA250 or Intel? PXA210 Applications Processors

存储器支持:

64 MB socketed Intel StrataFlash? memory

64 MB of SDRAM

1 MB SRAM

协处理器芯片:

Intel? SA-1111 companion chip

语音Codecs:

Phillips* UCB 1400 with integrated touchscreen

LCD显示:

Sharp* LM8V31 640x480 LCD panel

Third-party interface to support additional LCD panels

外设支持:

Full-Featured UART**

Pulse Width Modulation control

Bluetooth* support via dedicated serial port

I2C Controller

Two PS/2 connections (via SA-1111)

Secure Digital Memory Card and Multi-Media Card socket

One Compact-Flash Slot

One PCMCIA Slot

One SMC91C96 Ethernet Controller

调试支持的主要特点:

Mictor connectors for Agilent*and Tektronics*Logic Analyzer

Isolated Processor Core Voltage Regulator with jumper for power measurements

Eight software-writeable 7-segment LEDs for debugging

Eight software-readable event LEDs

Eight software-readable event switches

Two software-readable hex rotary dials

软件支持:

Diagnostics manager (installed)

Board Support Packages? for

14

?Microsoft Windows* CE .NET

?Microsoft PocketPC* 2002

?Symbian*OS

?PalmOS* (available from PalmSource*)

?Montavista* HardHat* Linux*

Intel? Integrated Performance Primitives??

Microsoft Windows* CE .NET Platform Builder DVD

IBM* WebSphere* Everyplace Embedded* Evalution kit, Intel? PCA edition

Intel CD containing supplementary documentation and support information

系统概述:

应用处理器和HDCDBCTA1 I/O板之间的通信全部通过GPIO来完成。系统功能框图如图:

1、电源供电和调节

HCDDBCTA1 / Cotulla系统由110 VAC to +12 VDC直流供电,系统采用TPS5102双调节器由12 VDC产生3.3 VDC和5 VDC (VCC)电源。

Green LED D16 (+5V)

15

Green LED D17 (+3.3V)

2、默认开关

开关S9 (nBAT_FAULT)和S10 (nVDD_FAULT)控制Cotulla I/O引脚状态,S11 (BAT_FAULT)控制

SA-1111 pin状态。

3、复位

硬件复位开关S27 (RESET) ,复位I/O板和Cotulla处理器板

no-dot — assert reset

dot — release reset

软件复位Miscellaneous Write Register清除适当的位来完成,然后置1恢复状态。有两种类型的软件复位:Bit PC_RST 只复位处理器卡;

Bit SYS_RST 复位处理器卡和I/O底板

4 Flash存储器和Boot ROM

四个插槽提供两块同样的Intel 28F128J3A StrataFlash存储器。每块有两片32 Mbytes的存储器。其中两片包含了出厂的POST程序。设定适当的模式,上电自动引导执行。开关S14 (nWRPT),设在no-dot position (default)位置,写保护ROM bank。另外两片标为FLASH,提供32 Mbytes的Flash存储空间供用户使用。当将S15 (nROMBT)设在dot时, FLASH bank也可上电引导。相应的片选信号分别为nCS0和nCS1

5 静态存储器(SRAM)

两片Samsung K6R4016V1C-T12 12-ns SRAM器件,组成256K by 16 bits,在nCS2的上半部分提供1 MB的通用目的存储器。

6 Cotulla通用目的I/O (GPIO)

J19, J20和J21 (GPIO)上共有9个Cotulla GPIO pins对用户来讲可以用。详细参见参考手册。GPIO 0 和1可以用S13和S12设成高/低电平。

7 底板寄存器和中断控制器

Xilinx Spartan-II—FPGA实现底板寄存器和外设的中断控制器。下列外设可以在GPIO pin GP0上产生中断::

?Burr Brown touch-screen controller

?Philips UCB 1400 CODEC

?Ethernet controller

?Cotulla Client USB

?SA-1111 companion chip

?MMC/SD card inserted

?Switch S13 (GP0)

另一种类型的中断可以由S12 (GP1)产生。

8 LCD显示和接口

I/O底板有一个Sharp LM8V31 640x480 STN LCD显示屏借口。该显示屏嵌入了触摸屏和CCFT背光。下列器件控制液晶显示:

?R3 (BRIGHT) — LCD brightness

?R1 — LCD contrast

?S2 (TDK) — backlight power on (dot position) or off (no-dot position)

9 Intel? SA-1111? Microprocessor Companion Chip

16

SA-1111占用nCS4的存储空间,它提供如下接口:

?one PCMCIA slot

?one Compact Flash connector

?one Universal Serial Bus (USB) Host port

?one PS/2 keyboard

?one PS/2 mouse.

该芯片可以产生中断,可以被使能,也可以屏蔽掉。

9.1 PCMCIA和Compact Flash

SA-1111提供PCMCIA接口逻辑控制并完成信号的缓冲,Cotulla PCMCIA和Compact Flash控制器通过专门的GPIO pins进行通信。

9.2 Universal Serial Bus Host Controller

SA-1111嵌入的主USB接口控制其,支持1.5 Mbps和12 Mbps的USB设备。

9.3 PS/2 键盘和鼠标接口

10 语音CODECs

底板上有两个CODECs,都通过Cotulla AC97控制器单元通信。AC97控制器只支持16-bit的语音处理。每一路CODEC都有独立的MIC, LINE IN和HEADPHONES接口。都有集成的输入输出信号放大电路。通过开关选择具体那一路信号:

Switch S1 (CODEC MUX) :

dot position — Cirrus Crystal CS4201*

no-dot position — Philips UCB1400* (default)

除此之外, UCB140提供两个功能:

?general-purpose I/O (GPIO)

?the default touch-screen controller

CODEC MUX使能或屏蔽UCB1400的三个功能,因此当CS4201 CODEC使能时, UCB1400的触摸屏和GPIO被屏蔽。

10.1 Philips UCB1400*

Philips UCB1400 CODEC 支持20-bit可编程采样的stereo audio接口。

10.2 Cirrus Crystal CS4201*

Crystal CS4201是一个为PC多媒体系统设计的stereo CODEC该芯片有20-bit DA变换和18-bit的AD变换。

11 Touch-Screen Controllers

11.1 UCB1400

11.2 Burr Brown ADS7846*

12 Pulse Width Modulation

13 USB Client Port

14 IrDA Infrared Transceiver

15 Serial Communications Ports

16 MultiMedia / Secure Digital Memory Card

17 Ethernet Controller

18 Expansion Card Slot

17

19 User Switches and LEDs

版权所有北京麦克泰软件技术有限公司

未经允许,请勿以任何方式转载

18

浅谈几种常见的嵌入式处理器比较分析

浅谈几种常见的嵌入式处理器比较分析 前言 随着电子科学的不断发展,人们开始逐渐对数码产品有了更高的需求,这就促使了信息技术的不断发展。嵌入式系统的核心就是嵌入式处理器,它是控制、辅助嵌入式系统运行的硬件单元,其应用范围非常的广阔,它也具有很好的发展前景。那么,面对纷繁复杂的嵌入式处理器市场,我们该如何做出适合自己的选择呢?下面小编就对市场上常见的几种嵌入式处理器进行比较分析,希望可以对大家有所帮助(嵌入式处理器类型)。 (1)嵌入式ARM微处理器(嵌入式微处理器结构) ARM微处理器的由来与发展 ARM(Advanced RISC Machines),既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。目前,采用ARM技术知识产权(IP)核的微处理器,即我们通常所说的ARM微处理器。它是一种高性能、低功耗的32位微处器,它被广泛应用于嵌入式系统中。基于ARM技术的微处理器应用约占据了32位RISC微处理器75%以上的市场份额,ARM技术正在逐步渗入到我们生活的各个方面。ARM9代表了ARM公司主流的处理器,已经在手持电话、机顶盒、数码像机、GPS、个人数字助理以及因特网设备等方面有了广泛的应用。 ARM微处理器的应用领域 ARM微处理器是目前应用领域非常广的处理器,到目前为止,ARM微处理器及技术的应用几乎已经遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,深入到各个领域。 1、工业控制领域:作为32的RISC架构,基于ARM核的微控制器芯片不但占据了高端微控制器市场的大部分市场份额,同时也逐渐向低端微控制器应用领域扩展,ARM微控制器的低功耗、高性价比,向传统的8位/16位微控制器提出了挑战。 2、无线通讯领域:目前已有超过85%的无线通讯设备采用了ARM技术,ARM以其高性能和低成本,在该领域的地位日益巩固。 3、网络应用:随着宽带技术的推广,采用ARM技术的ADSL芯片正逐步获得竞争优势。此外,ARM在语音及视频处理上行了优化,并获得广泛支持,也对DSP的应用领域提出了挑战。 4、消费类电子产品:ARM技术在目前流行的数字音频播放器、数字机顶盒和游戏机中得到广泛采用。 5、成像和安全产品:现在流行的数码相机和打印机中绝大部分采用ARM技术。手机中的32位SIM智能卡也采用了ARM技术。 基于RISC架构的ARM微处理器的特点 1、体积小、低功耗、低成本、高性能; 2、支持Thumb(16位)/ARM(32位)双指令集,能很好的兼容8位/16位器件; 3、大量使用寄存器,指令执行速度更快;

嵌入式微处理器系统读书报告

《嵌入式微处理器系统》专题读书报告 姓名:全妤

1、引言 随着医疗电子、智能家居、物流管理和电力控制等方面的不断风靡,嵌入式系统利用自身积累的底蕴经验,重视和把握这个机会,想办法在已经成熟的平台和产品基础上与应用传感单元的结合,扩展物联和感知的支持能力,发掘某种领域物联网应用。作为物联网重要技术组成的嵌入式系统,嵌入式系统的视角有助于深刻地、全面地理解物联网的本质。 2、嵌入式系统的概念 嵌入式系统被定义为以应用为中心、计算机技术为基础、软件硬件可裁剪、适应应用系统对功能、可靠性、成本、体积功耗严格要求的专用计算机系统。 2.1嵌入式系统的组成 一个嵌入式系统装置一般都由嵌入式计算机系统和执行装置组成。嵌入式计算机系统是整个嵌入式系统的核心,由硬件层、中间层、系统软件层和应用软件层组成。执行装置也称为被控对象,它可以接受嵌入式计算机系统发出的控制命令,执行所规定的操作或任务。 2.1.1 硬件层 硬件层中包含嵌入式微处理器、存储器(SDRAM、ROM、Flash等)、通用设备接口和I/O接口(A/D、D/A、I/O等)。

在一片嵌入式处理器基础上添加电源电路、时钟电路和存储器电路,就构成了一个嵌入式核心控制模块。其中操作系统和应用程序都可以固化在ROM中。 1)嵌入式微处理器 嵌入式系统硬件层的核心是嵌入式微处理器,嵌入式微处理器与通用CPU最大的不同在于嵌入式微处理器大多工作在为特定用户群所专用设计的系统中,它将通用CPU许多由板卡完成的任务集成在芯片内部,从而有利于嵌入式系统在设计时趋于小型化,同时还具有很高的效率和可靠性。 2)存储器 嵌入式系统需要存储器来存放和执行代码。嵌入式系统的存储器包含Cache、主存和辅助存储器。 3)通用设备接口和I/O接口 嵌入式系统和外界交互需要一定形式的通用设备接口,如A/D、D/A、I/O等,外设通过和片外其他设备的或传感器的连接来实现微处理器的输入/输出功能。每个外设通常都只有单一的功能,它可以在芯片外也可以内置芯片中。外设的种类很多,可从一个简单的串行通信设备到非常复杂的802.11无线设备。

微处理器系统与嵌入式系统1—7章最全答案合集

“微处理器系统原理与嵌入式系统设计”第一章习题解答 1.1 什么是程序存储式计算机? 程序存储式计算机指采用存储程序原理工作的计算机。 存储程序原理又称“·诺依曼原理”,其核心思想包括: ●程序由指令组成,并和数据一起存放在存储器中; ●计算机启动后,能自动地按照程序指令的逻辑顺序逐条把指令从存储器中 读出来,自动完成由程序所描述的处理工作。 1.2 通用计算机的几个主要部件是什么? ●主机(CPU、主板、存); ●外设(硬盘/光驱、显示器/显卡、键盘/鼠标、声卡/音箱); 1.3 以集成电路级别而言,计算机系统的三个主要组成部分是什么? 中央处理器、存储器芯片、总线接口芯片 1.4 阐述摩尔定律。 每18个月,芯片的晶体管密度提高一倍,运算性能提高一倍,而价格下降一半。 1.5 讨论:摩尔定律有什么限制,可以使用哪些方式克服这些限制?摩尔定律还会持续多久?在摩尔定律之后电路将如何演化? 摩尔定律不能逾越的四个鸿沟:基本大小的限制、散热、电流泄露、热噪。具体问题如:晶体管体积继续缩小的物理极限,高主频导致的高温…… 解决办法:采用纳米材料、变相材料等取代硅、光学互联、3D、加速器技术、多核…… (为了降低功耗与制造成本,深度集成仍是目前半导体行业努力的方向,但这不可能永无止,因为工艺再先进也不可能将半导体做的比原子更小。用作绝缘材料的二氧化硅,已逼近极限,如继续缩小将导致漏电、散热等物理瓶颈,数量集成趋势终有终结的一天。一旦芯片上线条宽度达到纳米数量级时,相当于只有几个分子的大小,这种情况下材料的物理、化学性能将发生质的变化,致使采用现行工艺的半导体器件不能正常工作,摩尔定律也就要走到它的尽头了。业界专家预计,芯片性能的增长速度将在今后几年趋缓,一般认为摩尔定律能再适用10年左右,其制约的因素一是技术,二是经济。)

嵌入式微处理器结构与应用

《嵌入式微处理器结构与应用》 实训报告 专业:电子信息工程 学生姓名: 学号 指导教师:

交通灯控制系统 1 整体设计 1.1 设计要求 利用arm9实验箱扩展口控制各个路口红绿灯及时间显示,设计一个交通灯控制系统。 1.1.1设计任务 设计一个十字路口的交通灯,它的红灯,绿灯,黄灯的闪烁必须符合交通规则,再用一个数码管来显示倒计时的时间,此时,灯的闪烁必须与数码管上的时间相对应。 1.1.2性能指标要求 (1) 按照题目要求独立设计系统所需电路,并完成电路的实际制作。 (2) 在十字交叉路口,东南西北各方向都设置红、黄、绿色信号灯,红灯亮表示禁止通行,绿灯亮表示可以通行,红灯灭之前3秒钟黄灯开始闪烁直到绿灯亮起后黄灯熄灭。其中东西方向为主干道,南北方向为次干道,设置一位数码管,用来显示红灯和绿灯倒计时间,东西方向时间一致,南北方向时间一致。 (3)开机时主干道为9秒倒计时,次干道为6秒倒计时。 (4)单独设计人行道指示灯标志,当禁止行走时为红灯,当可以横穿马路时,绿灯亮起,在通行之前3秒钟黄灯开始闪烁(以警示行人),最终红灯亮起绿灯熄灭。 (5)使用51单片机完成与arm9实验箱的连接,单片机模块只是完成通信与显示功能。所以的控制只能在arm 中实现(既断开接口连接,显示相关功能无效)。 1.2 整机实现的基本原理及框图 1.2.1 基本原理 主体电路:其分为两部分,一是由ARM9发送控制信号模块,二是由单片机完成通信与显示模块。ARM9发送控制信号模块主要由S3C2410A 的UART 专用寄存器完成串口通南 北 西 东 数码管 数码管

信,已达到发送控制信号的目的,指示单片机的交通状态是东西方向亮绿灯还是南北方向和数码管的显示。单片机完成通信与显示模块主要由AT89S52单片机的I/O 端口、定时计数器、外部中断扩展等组成,负责解读arm9试验箱发送来的数据,并把根据解读的数据控制交通灯的亮灭和数码管的显示。 1.2.2 总体框图 2 各功能电路实现原理及电路设计 2.1 交通灯显示部分 此模块是应用的16盏LED 灯,连接到51单片机的P1口,通过给P1口的管教赋值0/1,来实现16盏LED 灯的亮灭。 ARM 实验箱 发送 控制 指令 单片机系统 LED 灯显示交通状态 数码管显示倒计时时间

嵌入式微处理器未来市场趋势

嵌入式微處理器未來市場趨勢 CPU的架構大致上可分為CISC CPU & RISC CPU。 CISC CPU適用於大量資料運算的應用(INTEL、AMD、VIA的x86 CPU)。 RISC CPU所強調的是執行的效率與省電的要求(ARM、MIPS、ARC …)。 不論是CISC或是RISC CPU,都可以依據CPU內部處理資料匯流排的寬度,可區分成8位元、16位元、32位元與64位元等四種。根據In-Stat的統計,成長最快的是64位元嵌入式CPU,主要應用在STB、DTV與電視遊戲機等需要大量資料處理的產品。 8至64位元主要產品中所使用嵌入式CPU種類 全球的嵌入式CPU供應商第一大廠商是ARM,排名第二是MIPS。但兩家的產品定位並不完全相同。 ARM的CPU會強調省電應用;MIPS則主打高效能的產品。 因此在過去強調省電訴求的行動電話是嵌入式產品最大應用產品情況下,ARM 的營收皆優於MIPS。MIPS已逐漸淡出16位元CPU的市場,而專注於32位元以上的CPU。ARM與其最大競爭對手MIPS的差異處在於,以交易機制來分析,一般而言,ARM的授權金比重較高,而MIPS則收取比例較高的權利金。 早期台灣廠商CPU或MCU相關技術可區分成三類,8051架構、6502架構與自行研發等三種。INTEL的8051與Motorola的6502都是8位元的架構,初期都是由工研院所授權獲得,並推廣至國內業者。另外自行研發的也不在少數,例如凌陽、盛群、金麗或十速等公司,但都是32位元以下的架構。

嵌入式微處理(CPU)器與微控制器(MCU) 微處理器強調運算效能,而微控制器著重控制功能。 在SoC整合趨勢下,嵌入式微處理器加上記憶體、邏輯與I/O等IP將構成強大效能的微控制器;而增強位元數後的微控制器亦具有MPU的強大處理功能。 微處理器若以應用產品的軟體平台來區分,可分成特定應用型與泛用型兩種。特定應用型: 操作軟體大致是依據終端產品所需的功能加以設計,其最大特色是封閉的操作環境,終端產品的使用者大致上不需了解軟體的構造,也不能修改其操作功能,應用產品有印表機、數位相機、車用設備與遊戲機等,這類型產品通常較簡單其穩定性也要求較高。 泛用型: 如簡易的電腦一樣,有著相似而共通的作業系統,主要應用在PDA、Smart Phone、STB(視訊轉換器)、Thin Client等。此類產品因具有資訊交換的功能,其作業系統較複雜,相容性的要求也較高。 微控制器主要是負責系統產品中控制功能的IC元件。目前電子產品朝向輕薄短小、功能強大、價格低廉等目標發展,加上開發時程日益縮短,微控制器具有整合諸多功能於一身的特性,不但節省開發時間,在降低體積與成本上也有相當大的助益。 微控制器因有下列優點: 1.低價 2.較小的程式碼 3.可使用C語言編譯,開發更容易 4.耗電量較低 5.最高的效能與價格比 16位元以上的微控制器主要應用在通訊(如ISDN、USB等)、車用與工業等項目;由於需要符合工業規格,必須認證後才能出貨,技術層次較高。 隨著系統產品功能的多樣化,人機介面必須具有親和力…等,微控制器的效能亦不斷要求提升,近年來32/64位元微控制器成長率有越來越高的趨勢。

Intel XScale(TM) 嵌入式微处理器简介

Intel XScale?嵌入式微处理器简介 Intel Xscale内核是和ARM? Architecture V5TE结构兼容的微处理器。Intel? XScale?core内核集成了多种微结构的特点,从而能够完成更过的性能要求。这样用户可以根据自己的需求进行配置,实现自己特定的功能。Intel? XScale?的这些微结构很多应用在存储器当中,主要包括: ?当数据缓冲从外部存储器获取数据是,仍然能够执行指令; ?写缓冲; ?写回数据缓冲(Write-back data cache) ?缓冲锁定(Cache locking) ?可配置的缓冲方式(X Bit, C Bit for Cacheable, B Bit for Bufferable) Intel Xscale内核的上述特点,使它能够有效的处理语音信号,乘法累加操作还可以完成多种语音和多媒体CODEC算法。 特点改进的性能 Intel? 超级流水线技术 7-stage integer/8-stage存储器超级流水线内核获得更高的速度 和较低的功耗 Intel?动态电压管理 动态电压和频率允许应用系统对性能和功耗进行合理的折衷 Intel? Media处理技术 多累加协处理器同时完成两个16-bit SIMD 乘法(带40-bit累 加),有效的媒体处理; 电源管理单元 通过idle、 sleep、和快速wake-up模式,降低功耗 128-entry Branch Target Buffer 使流水线载有分支支零时仍能够保持正确 32 KB Instruction Cache 保持重要指令,提高系统性能,降低系统功耗 32 KB Data Cache 保持重要数据,提高系统性能,降低系统功耗 2 KB Mini-Data Cache 在频繁改变数据流时,避免"thrashing" of the D-Cache 32-entry 程序存储器管理 单元 使能逻辑到物理地址变换、访问允许和I-Cache attributes 32-entry数据存储器管理 单元 使能逻辑到物理地址变换、访问允许和D-Cache attributes 4-entry Fill and Pend Buffers 通过允许数据缓冲的non-blocking和"hit-under-miss"操作,提高内和效率。 性能监测单元 完成两个32-bit event counters和一个32-bit cycle counter for analysis of hit rates, etc. Debug调试单元 采用硬件断点和256-entry跟踪缓冲调试程序 32-bit Coprocessor Interface 在内核和协处理器间提供高性能的接口 64-bit内和存储器总线,同时32-bit输入和32-bit输出 Gives up to 4.8 GBytes/sec. @ 600 MHz bandwidth for internal accesses 8-entry Write Buffer 当数据写入到存储器是,允许内和继续执行。 ARM兼容性 1

嵌入式微处理器与操作系统_华中师范大学20年春季考试题库及答案

[试题分类]:嵌入式微处理器与操作系统Z_82411005 [题型]:单选 [大题名称]:单项选择题 [题目数量]:60 [分数]:2 1.Makefile文件预定定义变量$^表示()。 A.目标文件的完整名称 B.所有不重复的依赖文件,以空格隔开 C.第一个依赖文件的名称 D.第二个依赖文件的名称 [答案]:B [一级属性]: [二级属性]: [难度]: [公开度]: 2.如果生成通用计算机上(系统是Linux操作系统)能够执行的程序,则使用的C编译是()。 A.TC B.VC C.GCC D.arm-linux-gcc [答案]:C [一级属性]: [二级属性]: [难度]: [公开度]: 3.创建根文件系统映像文件使用的工具是()。 A.BusyBox B.cramfs C.make D.vi [答案]:A [一级属性]: [二级属性]: [难度]: [公开度]: 4.S3C2410X系统的存储空间分成()组(bank)。 A.2 B.4 C.8 D.16 [答案]:C

[一级属性]: [二级属性]: [难度]: [公开度]: 5.GDB软件是()。 A.调试器 B.编译器 C.文本编译器 D.连接器 [答案]:A [一级属性]: [二级属性]: [难度]: [公开度]: 6.嵌入式系统和通用计算机相比,描述不正确的是()? A.专用性强 B.实时性好 C.可裁剪性好 D.功耗高 [答案]:D [一级属性]: [二级属性]: [难度]: [公开度]: 7.ARM9使用几级流水线。 A.2 B.3 C.5 D.7 [答案]:C [一级属性]: [二级属性]: [难度]: [公开度]: 8.ARM公司主要依靠()获得利润。 A.生产芯片 B.销售芯片 C.制定标准 D.出售芯片技术授权 [答案]:D

嵌入式微处理器的分类与特点

1.2.1 嵌入式处理器的分类与特点 1.嵌入式微处理器的分类 嵌入式系统的核心部件是嵌入式处理器,一般把嵌入式处理器分成4类,即嵌入式微控制器、嵌入式微处理器、嵌入式DSP处理器和嵌入式片上系统。 (1)嵌入式微控制器(MicroController(微控制器) Unit MCU的典型代表是单片机,它将整个计算机系统集成到一块芯片中。MCU一般以某种微处理器内核为核心,根据某些典型的应用,在芯片内部集成了ROM/EPROM、RAM、总线、总线逻辑、定时/计数器、看门狗、I/O、串行口、脉宽调制输出、A/D、D/A、FLASH RAM、EEPROM等各种必要功能部件和外设。为适应不同的应用需求,对功能的设置和外设的配置进行必要的修改和裁减定制,使得一个系列的单片机具有多种衍生产品,每种衍生产品的处理器内核都相同,不同的是存储器和外设的配置及功能的设置。这样可以使单片机最大限度地和应用需求相匹配,从而减少整个系统的功耗和成本。和嵌入式微处理器相比,微控制器的单片化使应用系统的体积大大减小,从而使功耗和成本大幅度下降、可靠性提高。由于MCU目前在产品的品种和数量上是所有种类嵌入式处理器中最多的,而且上述诸多优点决定了微控制器是嵌入式系统应用的主流。微控制器的片上外设资源一般比较丰富,适合于控制,因此称为微控制器。 通常,MCU可分为通用和半通用两类,比较有代表性的通用系列包括8051、P51XA、MCS-251、MCS-96/196/296、C166/167、68300等。而比较有代表性的半通用系列,如支持USB 接口的MCU 8XC930/931、C540、C541;支持I2C、CAN总线、LCD等的众多专用MCU 和兼容系列。 (2)嵌入式微处理器(MicroProcessor Unit,MPU) MPU是由通用计算机中的CPU演变而来的。MPU采用增强型通用微处理器。由于嵌入式系统通常应用于环境比较恶劣的环境中,因而MPU在工作温度、电磁兼容性以及可靠性方面的要求较通用的标准微处理器高。但是,MPU在功能方面与标准的微处理器基本上是一样的。根据实际嵌入式应用要求,将MPU装配在专门设计的主板上,只保留和嵌入式应用有关的主板功能,这样可以大幅度减小系统的体积和功耗。 和工业控制计算机相比,MPU组成的系统具有体积小、重量轻、成本低、可靠性高的优点,但在其电路板上必须包括ROM、RAM、总线接口、各种外设等器件,从而降低了系统的可靠性,技术保密性也较差。由MPU及其存储器、总线、外设等安装在一块电路主板上构成一个通常所说的单板机系统。嵌入式处理器目前主要有AM186/88、386EX、SC-400、Power PC、68000、MPIS、ARM系列等。 (3)嵌入式数字信号处理器(Digital Signal Processor,DSP) DSP是专门用于信号处理方面的处理器,其在系统结构和指令算法方面进行了特殊设计,具有很高的编译效率和指令执行速度。 在数字信号处理应用中,各种数字信号处理算法很复杂,这些算法的复杂度可能是o (nm)的,甚至是NP的,一般结构的处理器无法实时的完成这些运算。由于DSP对系统结构和指令进行了特殊设计,使其适合于实时地进行数字信号处理。在数字滤波、fft、谱分析等方面,DSP算法正大量进入嵌入式领域,DSP应用正从在通用单片机中以普通指令实现DSP 功能,过渡到采用嵌入式DSP。 嵌入式DSP处理器有两类:(1)DSP处理器经过单片化、EMC改造、增加片上外设成为嵌入式DSP处理器,TI 的TMS320C2000/C5000 等属于此范畴。(2)在通用单片机或SOC 中增加DSP协处理器,例如Intel的MCS-296和infineon(siemens)的tricore。另外,在有关智

嵌入式微处理器特点

嵌入式微处理器特点: 嵌入式微处理器一般就具备以下4个特点: (1)对实时多任务有很强的支持能力,能完成多任务并且有较短的中 断响应时间,从而使部的代码和实时核心的执行时间减少到最低限度。 (2)具有功能很强的存储区保护功能。这是由于嵌入式系统的软件结 构已模块化,而为了避免在软件模块之间出现错误的交叉作用,需要设计强 大的存储区保护功能,同时也有利于软件诊断。 (3)可扩展的处理器结构,以能最迅速地开展出满足应用的最高性能 的嵌入式微处理器。 (4)嵌入式微处理器必须功耗很低,尤其是用于便携式的无线及移动 的计算和通信设备中靠电池供电的嵌入式系统更是如此,如需要功耗只有 mW甚至μW级。 嵌入式系统概念: 一般来说,嵌入式系统是“执行专用功能并被部计算机控制的设备或者系统。嵌入式系统不能使用通用型计算机,而且运行的是固化的软件,用术语表示就是固件(firmware),终端用户很难或者不可能改变固件。” 嵌入式系统是以应用为中心,以计算机技术为基础,并且软硬件可裁剪,适用于应用系统对功能、可靠性、成本、体积、功耗有严格要求的专用计算机系统。它一般由嵌入式微处理器、外围硬件设备、嵌入式操作系统以及用户的应用程序等四个部分组成,用于实现对其他设备的控制、监视或管理等功能。嵌入式系统一般指非PC系统,它包括硬件和软件两部分。硬件包括处理器/微处理器、存储器及外设器件和I/O端口、图形控制器等。软件部分包括操作系统软件(OS)(要时和多任务操作)和应用程序编程。有时设计人员把这两种软件组合在一起。应用程序控制着系统的运作和行为;而操作系统控制着应用程序编程与硬件的交互作用。嵌入式系统的核心是嵌入式微处理器。

DSP 、单片机以及嵌入式微处理器区别

DSP 、单片机以及嵌入式微处理器都是嵌入式家族的一员。最大区别是DSP能够高速、实时地进行数字信号处理运算。数字信号处理运算的特点是乘/加及反复相乘 求和(乘积累加)。为了能快速地进行数字信号处理的运算,(1)DSP设置了硬件乘法/累加器,(2)能在单个指令周期内完成乘/加运算。(3)为满足FFT、卷积等数字信号处理的特殊要求,目前DSP大多在指令系统中设置了“循环寻址”及“位倒序”寻址指令和其他特殊指令,使得寻址、排序的速度大大提高。DSP完成1024复点FFT的运算,所需时间仅为微秒量级。 高速数据的传输能力是DSP高速实时处理的关键之一。新型的DSP设置了单独的DMA总线及其控制器,在不影响或基本不影响DSP处理速度的情况下,作并行的数据传送,传送速率可达每秒百兆字节。DSP内部有流水线,它在指令并行、功能单元并行、多总线、时钟频率提高等方面不断创新和改进。因此,DSP与单片机、嵌入式微处理器相比,在内部功能单元并行、多DSP核并行、速度快、功耗小、完成各种DSP算法方面尤为突出。 单片机也称微控制器或嵌入式控制器,它是为中、低成本控制领域而设计和开发的。单片机的位控能力强,I/O接口种类繁多,片内外设和控制功能丰富、价格低、使用方便,但与DSP相比,处理速度较慢。DSP具有的高速并行结构及指令、多总线,单片机却没有。DSP处理的算法的复杂度和大的数据处理流量更是单片机不可企及的。嵌入式微处理器的基础是通用计算机中的CPU(微处理器)。是嵌入式系统的核心。为满足嵌入式应用的特殊要求,嵌入式微处理器虽然在功能上和标准微处理器基本是一样的,但在工作温度、抗电磁干扰、可靠性等方面一般都做了各种增强。与工业控制计算机相比,嵌入式微处理器具有体积小、质量轻、成本低、可靠性高的优点,但是在电路板上必须包括ROM、RAM、总线接口、各种外设等器件,从而降低了系统的可靠性,技术保密性也较差。在应用设计中,嵌入式微处理器及其存储器、总线、外设等安装在专门设计的一块电路板上,只保留和嵌入式应用有关的母板功能,可大幅度减小系统的体积和功耗。目前,较流行的是基于ARM7、ARM9系列内核的嵌入式微处理器。 嵌入式微处理器与DSP的一个很大区别,就是嵌入式处理器的地址线要比DSP 的数目多,所能扩展的存储器空间要比DSP的存储器空间大的多,所以可配置实时多任务操作系统(RTOS)。RTOS是针对不同处理器优化设计的高效率、可靠性和可信性很高的实时多任务内核,它将CPU时间、中断、I/O、定时器等资源都包装起来,留给用户一个标准的应用程序接口(API),并根据各个任务的优先级,合理地在不同任务之间分配CPU时间。RTOS是嵌入式应用软件的基础和开发平台。常用的RTOS:Linux(为几百KB)和VxWorks(几MB)。 由于嵌入式实时多任务操作系统具有的高度灵活性,可很容易地对它进行定制或作适当开发,来满足实际应用需要。例如,移动计算平台、信息家电(机顶盒、数字电视)、媒体手机、工业控制和商业领域(例如,智能工控设备、ATM机等)、电子商务平台,甚至军事应用,吸引力巨大。所以,目前嵌入式微处理器的应用是继单片机、DSP之后的又一大应用热门。但是,由于嵌入式微处理器通常不能高效地完成许多基本的数字处理运算,例如,乘法累加、矢量旋转、三角函数等。它的 体系结构对特殊类型的数据结构只能提供通用的寻址操作,而DSP则有专门的简捷寻址机构和辅助硬件来快速完成。所以嵌入式微处理器不适合高速、实时的数字信号处理运算。而更适合“嵌入”到系统中,完成高速的“通用”计算与复杂

浅谈几种常见的嵌入式处理器比较分析

浅谈几种常见的嵌入式处理器比较分析 The manuscript was revised on the evening of 2021

浅谈几种常见的分析 前言 随着电子科学的不断发展,人们开始逐渐对数码产品有了更高的需求,这就促使了信息技术的不断发展。嵌入式系统的核心就是嵌入式处理器,它是控制、辅助嵌入式系统运行的硬件单元,其应用范围非常的广阔,它也具有很好的发展前景。那么,面对纷繁复杂的嵌入式处理器市场,我们该如何做出适合自己的选择呢下面小编就对市场上常见的几种嵌入式处理器进行比较分析,希望可以对大家有所帮助(嵌入式处理器类型)。 (1)嵌入式ARM微处理器(嵌入式微处理器结构) ARM微处理器的由来与发展 ARM(Advanced RISC Machines),既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。目前,采用ARM技术知识产权(IP)核的微处理器,即我们通常所说的ARM微处理器。它是一种高性能、低功耗的32位微处器,它被广泛应用于嵌入式系统中。基于ARM技术的微处理器应用约占据了32位RISC微处理器75%以上的市场份额,ARM技术正在逐步渗入到我们生活的各个方面。ARM9代表了ARM公司主流的处理器,已经在手持电话、机顶盒、数码像机、GPS、个人数字助理以及因特网设备等方面有了广泛的应用。 ARM微处理器的应用领域 ARM微处理器是目前应用领域非常广的处理器,到目前为止,ARM微处理器及技术的应用几乎已经遍及工业控制、消费类电子产品、通信系统、网络系统、无线系统等各类产品市场,深入到各个领域。 1、工业控制领域:作为32的RISC架构,基于ARM核的微控制器芯片不但占据了高端微控制器市场的大部分市场份额,同时也逐渐向低端微控制器应用领域扩展,ARM微控制器的低功耗、高性价比,向传统的8位/16位微控制器提出了挑战。 2、无线通讯领域:目前已有超过85%的无线通讯设备采用了ARM技术,ARM以其高性能和低成本,在该领域的地位日益巩固。 3、网络应用:随着宽带技术的推广,采用ARM技术的ADSL芯片正逐步获得竞争优势。此外,ARM在语音及视频处理上行了优化,并获得广泛支持,也对DSP的应用领域提出了挑战。 4、消费类电子产品:ARM技术在目前流行的数字音频播放器、数字机顶盒和游戏机中得到广泛采用。 5、成像和安全产品:现在流行的数码相机和打印机中绝大部分采用ARM技术。手机中的32位SIM智能卡也采用了ARM技术。 基于RISC架构的ARM微处理器的特点 1、体积小、低功耗、低成本、高性能; 2、支持Thumb(16位)/ARM(32位)双指令集,能很好的兼容8位/16位器件;

嵌入式ARM微处理器选型指南

嵌入式ARM微处理器选型指南 要选好一款处理器,要考虑的因素很多,不单单是纯粹的硬件接口,还需要考虑相关的操作系统、配套的开发工具、仿真器,以及工程师微处理器的经验和软件支持情况等。微处理器选型是否得当,将决定项目成败。当然,并不是说选好微处理器,就意味着成功,因为项目的成败取决于许多因素;但可以肯定的一点是,微处理器选型不当,将会给项目带来无限的烦恼,甚至导致项目的流产。 1 嵌入式微处理器选型的考虑因素 在产品开发中,作为核心芯片的微处理器,其自身的功能、性能、可靠性被寄予厚望,因为它的资源越丰富、自带功能越强大,产品开发周期就越短,项目成功率就越高。但是,任何一款微处理器都不可能尽善尽美,满足每个用户的需要,所以这就涉及选型的问题。 (1)应用领域 一个产品的功能、性能一旦定制下来,其所在的应用领域也随之确定。应用领域的确定将缩小选型的范围,例如:工业控制领域产品的工作条件通常比较苛刻,因此对芯片的工作温度通常是宽温的,这样就得选择工业级的芯片,民用级的就被排除在外。目前,比较常见的应用领域分类有航天航空、通信、计算机、工业控制、医疗系统、消费电子、汽车电子等。 (2)自带资源 经常会看到或听到这样的问题:主频是多少?有无内置的以太网MAC?有多少个I/O口?自带哪些接口?支持在线仿真吗?是否支持OS,能支持哪些OS?是否有外部存储接口?……以上都涉及芯片资源的问题,微处理器自带什么样的资源是选型的一个重要考虑因素。芯片自带资源越接近产品的需求,产品开发相对就越简单。 (3)可扩展资源 硬件平台要支持OS、RAM和ROM,对资源的要求就比较高。芯片一般都有内置RAM和ROM,但其容量一般都很小,内置512 KB就算很大了,但是运行OS一般都是兆级以上。这就要求芯片可扩展存储器。 (4)功耗 单看“功耗”是一个较为抽象的名词。这里举几个形象的例子: ①夏天使用空调时,家里的电费会猛增。这是因为空调是高功耗的家用电器,这时人们会想,“要是空调能像日光灯那样省电就好了”。 ②随身的MP3、MP4都使用电池。正当听音乐看视频时,系统因为没电自动关机,谁都会抱怨“又没电了!” ③目前手机一般使用锂电池,手机的待机和通话时间成了人们选择手机的重要指标。待机及通话时间越长,电池的使用寿命就可以提高,手机的寿命也相对提高了。 以上体现了人们对低功耗的渴求。低功耗的产品即节能又节财,甚至可以减少环境污染,它有如此多的优点,因此低功耗也成了芯片选型时的一个重要指标。 (5)封装 常见的微处理器芯片封装主要有QFP、BGA两大类型。BGA类型的封装焊接比较麻烦,一般的小公司都不会焊,但BGA封装的芯片体积会小很多。如果产品对芯片体积要求不严格,选型时最好选择QFP封装。 (6)芯片的可延续性及技术的可继承性 目前,产品更新换代的速度很快,所以在选型时要考虑芯片的可升级性。如果是同一厂家同一内核系列的芯片,其技术可继承性就较好。应该考虑知名半导体公司,然后查询其相关产品,再作出判断。 (7)价格及供货保证 芯片的价格和供货也是必须考虑的因素。许多芯片目前处于试用阶段(sampling),其价格和供货就会处于不稳定状态,所以选型时尽量选择有量产的芯片。 (8)仿真器 仿真器是硬件和底层软件调试时要用到的工具,开发初期如果没有它基本上会寸步难行。选择配套适合的仿真器,将会给开发带来许多便利。对于已经有仿真器的人们,在选型过程中要考虑它是否支持所选的芯片。 (9)OS及开发工具

嵌入式微处理器结构与应用课程设计报告

《嵌入式微处理器结构与应用》 课程设计报告 题目:电子菜单 一、课程设计的目的和主要内容: 目的:《嵌入式微处理器结构与应用》课程设计是软件工程本科专业的专业实践课程,结合在课程中学到的嵌入式系统的开发和调试方法,对学生在嵌入式系统设计和应用开发的基本技能方面进行综合的检验和实践。是学生在学习完《嵌入式微处理器结构与应用》课程之后的一个重要的实践环节。要求学生在教师的指导下,综合运用已学过的嵌入式微处理器相关的各种知识和技能,以小组协作的方式完成一项较为完整、并具有一定难度的课程设计任务。使学生总结本课程的主要知识点,提高学生的实际动手能力,为学生今后进一步学习和从事嵌入式系统相关的研究与开发打下坚实的基础。 内容:基于实时操作系统,学会复杂应用程序的基本开发方法,结合课程实验学到的知识,编写一个能综合应用液晶屏、触摸屏、键盘并结合简单文件系统API函数的界面应用。要求具备基本的三个界面:初始界面、点菜界面、结束界面,基本实现点菜的全过程。 二、基本的设计思路或程序流程图描述: 基于MVC勺设计模式,将程序分成三大独立的部分:模型(逻辑)部分、视图部分、控制部分。这三大部分的关系如下:

程序总流程图:

百度文库-让每个人平等地提升自我 初始化程序, 打开启动画面线程 关闭线程 点菜结束按钮 判断消息 类型 判断操 作类型 判断单 击内容 判断控 件类型 判断该菜单条目 的 状态,进行相应的逻 辑和视图更新 本人负责: 打开线程 界面控件 翻页按钮 加载菜单数据 显示启动动 画 键盘消息 显示点菜结束 画面和总价 程序 菜单条目 进行菜单的上下 滚动 关闭按钮 单击 拉动 重置逻辑数 据,显示最初 的点菜界面 关闭启动画面线程, 显示点菜画面 显示程序结束画 面 进行菜单的翻页 等待系统消息 触摸屏消息 、视图部分:

《嵌入式微处理器结构与应用》实训报告

桂林电子科技大学信息科技学院 《嵌入式微处理器结构与应用》实训报告 学号1152100135 姓名殷浩 指导教师:韩桂明,张锟,赵志鹏 2014 年6 月20 日

实训题目:倒计时秒表 1系统设计 1.1 设计要求 1.1.1 设计任务 使用串口连接51单片机与arm9实验箱实现99秒倒计时,并通过数码管显示。当倒计时为0时,点亮LED灯,蜂鸣器报警。 1.1.2 性能指标要求 (1) 实现99秒倒计时,并通过数码管显示; (2) 四个按键:一个“运行/暂停”按键,一个“加计时”按键,一个“减计时”按键,一个“复位”按键; (3) 四个指示灯:倒计时为0时,指示灯闪烁。 (4) 扩展多位数码管,实现多位显示(动态扫描) (5) 加入蜂鸣器,可作声音报警使用。 注意:(数码管、按键和指示灯均连接到单片机I/O口) 1.2 设计思路及设计框图 1.2.1设计思路 单片机通过按键扫描,发送不同指令并通过串口发送到arm9实验箱上,arm9程序响应接收到的指令,实现相应的计算和控制功能,并向单片机传回数据,单片机接收arm9反馈回来的数据并输出显示。 1.2.2总体设计框图 串口发送 2各个模块程序的设计 2.1单片机最小系统

单片机最小系统,或者称为最小应用系统,是指用最少的元件组成的单片机可以工作的系统。对51系列单片机来说,最小系统一般应该包括:单片机、晶振电路、复位电路。 复位电路:由电容串联电阻构成,结合"电容电压不能突变"的性质,可以知道,当系统一上电,RST脚将会出现高电平,并且,这个高电平持续的时间由电路的RC值来决定。典型的51单片机当RST脚的高电平持续两个机器周期以上就将复位,所以,适当组合RC的取值就可以保证可靠的复位.一般C 取10u,R取8.2K。原则就是要让RC组合可以在RST脚上产生不少于2个机周期的高电平。 晶振电路:典型的晶振取11.0592MHz(因为可以准确地得到9600波特率和19200波特率,用于有串口通讯的场合)/12MHz(产生精确的uS级时歇,方便定时操作) 2.2数码管显示 这次实训我们使用的是四位一体共阴数码管,经过测量,分别找到了它的段选和位选。用它来显示秒表的秒值,数码管的使能端接到P2.0、P2.1、P2.2和P2.3上,其余8个引脚分别单片机P0口相连,根据单片机引脚与数码管的连接关系,可以列出显示不同数字的段选码。从而准确的输出秒表的正确秒值。

嵌入式系统开发基础——基于ARM9微处理器C语言程序设计各章习题答案

第一章习题 1。嵌入某种微处理器或单片机的测试和控制系统称为嵌入式控制系统(Embedded Control System)。 在应用上大致分为两个层次,以MCS-51为代表的8位单片机和以ARM技术为基础的32位精减指令系统单片机 2。目标机上安装某种嵌入式操作系统和不安装嵌入式操作系统, 以MCS-51为代表的8位单片机不安装嵌入式操作系统。 3。32位、16位和8位 5。32位、16位 6。在大端格式中,字数据的高字节存储在低字节单元中,而字数据的低字节则存放在高地址单元中。 在小端存储格式中,低地址单元存放的是字数据的低字节,高地址单元中,存放的是数据的高字节。 第二章习题 (略) 第三章习题 1。 (1)寄存器大约有17类,每个的定义都是寄存器名字前面加一个小写”r” (2)在56个中断源中,有32个中断源提供中断控制器,其中,外部中断EINT4~EINT7通过“或”的形式提供一个中断源送至中断控制器,EINT8~EINT23也通过“或”的形式提供一个中断源送至中断控制器。 第四章习题 1,56个中断源,有32个中断源提供中断控制器 2,两种中断模式,即FIQ模式(快速模式)和IRQ模式(通用模式)。通过中断模式控制寄存器设置。 3,常用的有5个,它们是中断模式控制寄存器,控制中断模式;中断屏蔽寄存器,控制中断允许和禁止;中断源挂起寄存器,反映哪个中断源向CPU申请了中断;中断挂起寄存器,反映CPU正在响应的中断是哪个中断源申请的;中断优先级寄存器,它和中断仲裁

器配合,决定中断优先级。 4,中断源挂起寄存器,反映哪个中断源向CPU申请了中断;中断挂起寄存器,反映CPU正在响应的中断是哪个中断源申请的。中断源向CPU申请了中断如果该中断源没被屏蔽并且没有和它同级或高级的中断源申请中断,才能被响应。系统中可以有多个中断源向CPU申请中断,但同一时刻CPU只能响应一个最高级的中断源中断请求。中断源挂起寄存器和中断挂起寄存器反映了中断系统不同时段的状态。 5,进入中断服务程序先清中断源挂起寄存器和中断挂起寄存器;中断结束,将该中断源屏蔽。 6,将该中断源屏蔽取消;将该中断源屏蔽。 第五章习题 1,S3C2410芯片上共有117个多功能的输人/输出引脚,它们是。 ?1个23位的输出端口(端口A); 。1个11位的输入/输出端口(端口B); 。1个16位输入/输出端口(端口C); ? 1个16位输入/输出端口(端口D); ? 1个16位输入/输出端口(端口E); ?1个8位输人/输出端口(端口F); ? 1个16位输入/输出端口(端口G); 。1个11位的输入/输出端口(端口H)。 2,S3C2410 I/O口的控制寄存器、数据寄存器、上拉电阻允许寄存器的作用? 端口控制寄存器定义了每个引脚的功能;与I/O口进行数据操作,不管是输入还是输出,都是通过该口的数据寄存器进行的,如果该端口定义为输出端口,那么可以向GPnDAT的相应位写数据。如果该端口定义为输人端端口,那么可以从GPnDAT的相应位读出数据。 端口上拉寄存器控制每个端口组上拉电阻的使能/禁止。如果上拉寄存器某一位为0,则相应的端口上拉电阻被使能,该位做基本输入/输出使用,即第1功能;如果上拉寄存器某一位是1,则相应的端口上拉电阻被禁止,该位做第2功能使用。 5, rGPBCON=rGPBCON& 0xFFFFFC∣1; //蜂鸣器配置,PB1口接蜂鸣器,输出delay(1000); rGPBDAT & = 0xFFFFFE; //蜂鸣器响,低电平有效 rGPBDAT∣=1; // 蜂鸣器停

DSP 单片机以及嵌入式微处理器区别

DSP 、单片机以及嵌入式微处理器都就是嵌入式家族的一员。最大区别就是DSP 能够高速、实时地进行数字信号处理运算。数字信号处理运算的特点就是乘/加及反复相乘 求与(乘积累加)。为了能快速地进行数字信号处理的运算,(1)DSP设置了硬件乘法/累加器,(2)能在单个指令周期内完成乘/加运算。(3)为满足FFT、卷积等数字信号处理的特殊要求,目前DSP大多在指令系统中设置了“循环寻址”及“位倒序”寻址指令与其她特殊指令,使得寻址、排序的速度大大提高。DSP完成1024复点FFT的运算,所需时间仅为微秒量级。 高速数据的传输能力就是DSP高速实时处理的关键之一。新型的DSP设置了单独的DMA总线及其控制器,在不影响或基本不影响DSP处理速度的情况下,作并行的数据传送,传送速率可达每秒百兆字节。DSP内部有流水线,它在指令并行、功能单元并行、多总线、时钟频率提高等方面不断创新与改进。因此,DSP与单片机、嵌入式微处理器相比,在内部功能单元并行、多DSP核并行、速度快、功耗小、完成各种DSP算法方面尤为突出。 单片机也称微控制器或嵌入式控制器,它就是为中、低成本控制领域而设计与开发的。单片机的位控能力强,I/O接口种类繁多,片内外设与控制功能丰富、价格低、使用方便,但与DSP相比,处理速度较慢。DSP具有的高速并行结构及指令、多总线,单片机却没有。DSP处理的算法的复杂度与大的数据处理流量更就是单片机不可企及的。嵌入式微处理器的基础就是通用计算机中的CPU(微处理器)。就是嵌入式系统的核心。为满足嵌入式应用的特殊要求,嵌入式微处理器虽然在功能上与标准微处理器基本就是一样的,但在工作温度、抗电磁干扰、可靠性等方面一般都做了各种增强。与工业控制计算机相比,嵌入式微处理器具有体积小、质量轻、成本低、可靠性高的优点,但就是在电路板上必须包括ROM、RAM、总线接口、各种外设等器件,从而降低了系统的可靠性,技术保密性也较差。在应用设计中,嵌入式微处理器及其存储器、总线、外设等安装在专门设计的一块电路板上,只保留与嵌入式应用有关的母板功能,可大幅度减小系统的体积与功耗。目前,较流行的就是基于ARM7、ARM9系列内核的嵌入式微处理器。 嵌入式微处理器与DSP的一个很大区别,就就是嵌入式处理器的地址线要比DSP 的数目多,所能扩展的存储器空间要比DSP的存储器空间大的多,所以可配置实时多任务操作系统(RTOS)。RTOS就是针对不同处理器优化设计的高效率、可靠性与可信性很高的实时多任务内核,它将CPU时间、中断、I/O、定时器等资源都包装起来,留给用户一个标准的应用程序接口(API),并根据各个任务的优先级,合理地在不同任务之间分配CPU时间。RTOS就是嵌入式应用软件的基础与开发平台。常用的RTOS:Linux(为几百KB)与VxWorks(几MB)。 由于嵌入式实时多任务操作系统具有的高度灵活性,可很容易地对它进行定制或作适当开发,来满足实际应用需要。例如,移动计算平台、信息家电(机顶盒、数字电视)、媒体手机、工业控制与商业领域(例如,智能工控设备、ATM机等)、电子商务平台,甚至军事应用,吸引力巨大。所以,目前嵌入式微处理器的应用就是继单片机、DSP之后的又一大应用热门。但就是,由于嵌入式微处理器通常不能高效地完成许多基本的数字处理运算,例如,乘法累加、矢量旋转、三角函数等。它的 体系结构对特殊类型的数据结构只能提供通用的寻址操作,而DSP则有专门的简捷寻址机构与辅助硬件来快速完成。所以嵌入式微处理器不适合高速、实时的数字信号处理运算。而更适合“嵌入”到系统中,完成高速的“通用”计算与复杂