测试1 抢答器PCB版图设计

版图设计

PCB版图设计

试题抢答器单面PCB

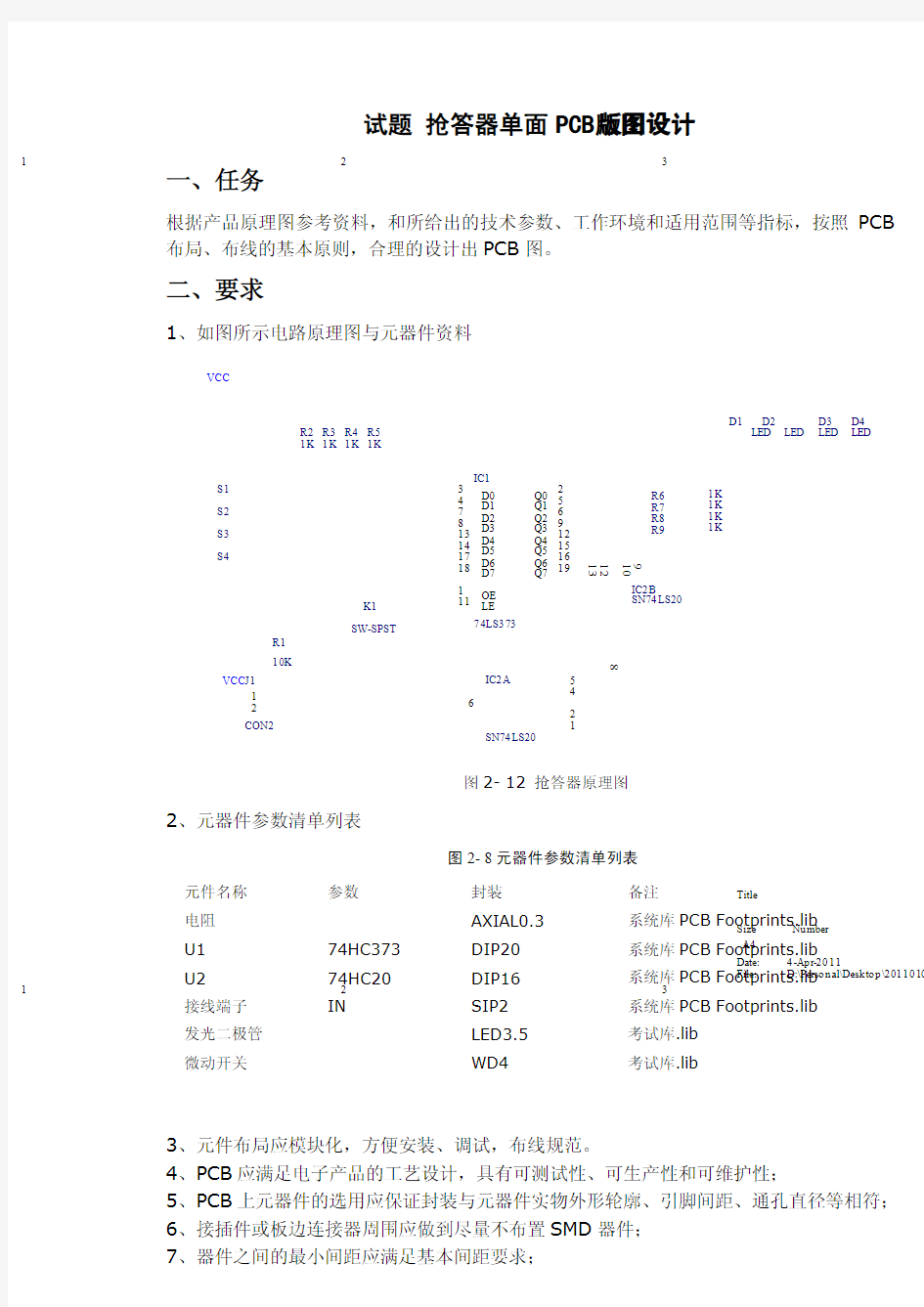

3、元件布局应模块化,方便安装、调试,布线规范。

4、PCB应满足电子产品的工艺设计,具有可测试性、可生产性和可维护性;

5、PCB上元器件的选用应保证封装与元器件实物外形轮廓、引脚间距、通孔直径等相符;

6、接插件或板边连接器周围应做到尽量不布置SMD器件;

7、器件之间的最小间距应满足基本间距要求;

10在D:\EXAM文件夹创建姓名.ddb;

11、PCB设计采用(单面板),大小为(2400*1500mil);要求:飞线小于2根,用黄色丝印线条表示飞线。

12、PCB布线宽度为10~30mil,安全间距为10mil,电源地线宽度(25mil),其它线宽(15mil);

13、安装定位孔四个

3

φmm,分别在四角,孔中心距边框5mm;

14、将考生号用文字放在顶层丝印层显眼处;

三、说明

1、本题中所用的电阻如无特殊提示均为1/4W普通电阻;

PCB测试工艺技术(DOC74)

少一些普通工艺问题 By Craig Pynn 欢迎来到工艺缺陷诊所。这里所描述的每个缺陷都将覆盖特殊的缺陷类型,将存档成为将来参考或培训新员工的一个无价的工艺缺陷指南。 大多数公司现在正在使用表面贴装技术,同时又向球栅阵列(BGA)、芯片规模包装(CSP)和甚至倒装芯片装配迈进。但是, 一些公司还在使用通孔技术。通孔技术的使用 不一定是与成本或经验有关- 可能只是由于 该产品不需要小型化。许多公司继续使用传统 的通孔元件,并将继续在混合技术产品上使用 这些零件。本文要看看一些不够普遍的工艺问 题。希望传统元件装配问题及其实际解决办法 将帮助提供对在今天的制造中什么可能还会出 错的洞察。 静电对元件的破坏 从上图,我们使用光学照片与扫描电子显 微镜(SEM, scanning electron microscopy)看到在 一个硅片表面上的静电击穿。静电放电,引入 到一个引脚,引起元件的工作状态的改变,导 致系统失效。在实验室对静电放电的模拟也能 够显示实时发生在芯片表面的失效。如上面的 照片所示,静电可能是一个问题,解决办法是 一个有效的控制政策。手腕带是最初最重要的防御。 树枝状晶体增长 树枝状结晶发生在施加的电压与潮湿和一些 可离子化的产品出现时。电压总是要在一个电路 上,但潮湿含量将取决于应用与环境。可离子化 材料可能来自印刷电路板(PCB)的表面,由于装 配期间或在空板制造阶段时的不良清洁。 如果要调查这类缺陷,不要接触板或元件。 在失效原因的所有证据毁灭之前,让缺陷拍成照 片并进行研究。污染可能经常来自焊接过程或使用的助焊剂。另一个可能性是装配期间带来的一般操作污垢。工业中最普遍的缺陷原因来自助焊剂残留物。 在上面的例子中,失效发生在元件的返修之后。这个特殊的单元是由一个第三方公司使用高活性助焊剂返修的,不象原来制造期间使用的低活性材料。 焊盘破裂 当元件或导线必须作为一个第二阶段装配安装时,通常使用 C 形焊盘。例子有,重型元件、线编织或不能满足焊接要求的元件。在某些情况中,品质人员不知道破裂的原因,以为是PCB腐蚀问题。

PCB版图设计报告

兰州交通大学电信学院课程设计实验报告 实验名称:负反馈放大电路PCB设计 无线话筒PCB设计(选作) 试验日期: 2012年6月25日 班级: 电子科学与技术092班 姓名: 刘光智 学号: 200910112

Altium designer简介 Altium Designer 提供了唯一一款统一的应用方案,其综合电子产品一体化开发所需的所有必须技术和功能。Altium Designer 在单一设计环境中集成板级和FPGA系统设计、基于FPGA和分立处理器的嵌入式软件开发以及PCB版图设计、编辑和制造。并集成了现代设计数据管理功能,使得Altium Designer成为电子产品开发的完整解决方案-一个既满足当前,也满足未来开发需求的解决方案。 一、实验目的 1.了解并学会运用Altium designer软件绘制简单PCB 2.会运用Alitum designer软件设计库元件 3.掌握印刷电路板布线流程 4.掌握印刷电路板设计的基本原则 二、设计内容 1.要求用Alitum designer软件画出电路原理图 2.按照所画原理图自动生成PCB版图 3.会自己设计元件和库 三、实验步骤(负反馈放大器PCB设计) 1、新建工程、为工程添加项目:在D盘新建一个自己的文件夹重命名为ffk,运行Alitum designer软件,然后单击文件/新建/工程/PCB工程,然后右击所建的PCB工程选择给工程添加原理图,然后添加PCB,建完PCB工程保存工程到D/ffk内,保存时三个文件都命名为ffk.扩展名 2、画原理图:在原理图窗口画出所要画的PCB原理图,本次实验所画电路图如图1: 图1 3、对所画电路图进行编译:点击工程/Compile Document mic.SchDoc,然后点击工程/Compile PCB Project PCB_mic.PrjPCB,然后打开Messages窗口查看编译结果,若有错误按照提示对错误进行改正再编译,直至没有错误结束编译

CMTBF信赖性测试评估准则

光宝科技股份有限公司 文件名称:信赖性测试评估准则 信赖性测试评估准则 ( Reliability Review Guideline ) 1 目的: 1.1 为确保产品设计的信赖性,以及加强产品在市场之竞争力,建立〝零件额定使用率〞 ( Component Stress Test ) 及〝机种预估寿命〞(MTBF Prediction) 之信赖性准则, 用以为厂内设计验证之依据。 1.2 提早介入及加速产品之成熟度。 1.3 避免上市后之风险。 2. 范围: 凡是本公司电源事业部所开发之产品均适用之。 3. 权责: 3.1 零件额定使用率 ( Component Stress Test ) 及机种预估寿命 (MTBF Prediction) 由信赖性 工程师负责测试,Component Stress De-rating 之定义由设计部及信赖性共同定义。 3.2 测试样品由设计工程师负责提供,且须经过Bench Test 测试,或有机种之验证报告。 3.3 信赖性完成之测试报告须会签设计部及其部门主管认可后,才可对外发行。 3.4 信赖性完成之测试报告文件,均须透过DOC 才能对外发行。 4. 参考标准: 4.1. 零件额定使用率参考准则 : ISO 9001 NPS-MD-P-013。 4.2. 机种预估寿命( MTBF )参考准则: MIL-STD-217F, Bellcore TR332 ISSUE 6。 5. 定义: MTBF ( Mean Time Between Failure ) :平均间隔失效时间。 MTBF = 1/p λ(p λFAILURE RATE)610* HOURS 6. 作业流程图: 6.1 信赖性测试评估作业流程图如 附件1 7. 作业内容: 7.1 新产品导入会议 ( Kickoff Meeting ): 7.1.1 新机种由业务主导之新产品会议中决定: 7.1.1.1. 决定样品 ( SAMPLE ) 及其它资料日期. 7.1.1.2. BLUE BOOK 发出之日期. 7.1.1.3. 信赖性工程师应于EVT 阶段开始执行评估, 且必须于Pilot run PCB 修改定案之前 完成零件额定使用率之测试与评估, 以符合量产及客户的需求。

电路板测试

电路板测试、检验及规范 1、Acceptability,acceptance 允收性,允收 前者是指在对半成品或成品进行检验时,所应遵守的各种作业条件及成文准则。后者是指执行允收检验的过程,如Acceptance Test。 2、Acceptable Quality Level(AQL)允收品质水准 系指被验批在抽检时,认为能满足工程要求之"不良率上限",或指百分缺点数之上限。AQL并非为保护某特别批而设,而是针对连续批品质所定的保证。 3、Air Inclusion 气泡夹杂 在板材进行液态物料涂布工程时,常会有气泡残存在涂料中,如胶片树脂中的气泡,或绿漆印膜中的气泡等,这种夹杂的气泡对板子电性或物性都很不好。 4、AOI 自动光学检验 Automatic Optical Inspection,是利用普通光线或雷射光配合计算机程序,对电路板面进行外观的视觉检验,以代替人工目检的光学设备。 5、AQL 品质允收水准

Acceptable Quality Level,在大量产品的品检项目中,抽取少量进行检验,再据以决定整批动向的品管技术。 6、ATE 自动电测设备 为保证完工的电路板其线路系统的通顺,故需在高电压(如250 V)多测点的泛用型电测母机上,采用特定接点的针盘对板子进行电测,此种泛用型的测试机谓之Automatic Testing Equipment。 7、Blister 局部性分层或起泡 在电路制程中常会发生局部板面或局部板材间之分层,或局部铜箔浮离的情形,均称为Blister。另在一般电镀过程中亦常因底材处理不洁,而发生镀层起泡的情形,尤其以镀银对象在后烘烤中最容易起泡。 8、Bow,Bowing 板弯 当板子失去其应有的平坦度(Flatness)后,以其凹面朝下放在平坦的台面上,若无法保持板角四点落在一个平面上时,则称为板弯或板翘(Warp 或Warpage),若只能三点落在平面上时,称为板扭(Twist)。不过通常这种扭翘的情况很轻微不太明显时,一律俗称为板翘(Warpage)。

PCB设计基本概念与主要流程

印制电路板的设计是以电路原理图为根据,实现电路设计者所需要的功能。印刷电路板的设计主要指版图设计,需要考虑外部连接的布局。内部电子元件的优化布局。金属连线和通孔的优化布局。电磁保护。热耗散等各种因素。优秀的版图设计可以节约生产成本,达到良好的电路性能和散热性能。简单的版图设计可以用手工实现,复杂的版图设计需要借助计算机辅助设计(CAD)实现。 目录 PCB设计简介 具体方法 PCB设计基本概念 PCB设计主要的流程 PCB设计简介 具体方法 PCB设计基本概念 PCB设计主要的流程 展开 编辑本段PCB设计简介 在高速设计中,可控阻抗板和线路的特性阻抗是最重要和最普遍的问题之一。首先了解一下传输线的定义:传输线由两个具有一定长度的导体组成,一个导体用来发送信号,另一个用来接收信号(切记“回路”取代“地”的概念)。在一个多层板中,每一条线路都是传输线的组成部分,

邻近的参考平面可作为第二条线路或回路。一条线路成为“性能良好”传输线的关键是使它的特性阻抗在整个线路中保持恒定。 线路板成为“可控阻抗板”的关键是使所有线路的特性阻抗满足一个规定值,通常在25欧姆和70欧姆之间。在多层线路板中,传输线性能良好的关键是使它的特性阻抗在整条线路中保持恒定。 但是,究竟什么是特性阻抗?理解特性阻抗最简单的方法是看信号在传输中碰到了什么。当沿着一条具有同样横截面传输线移动时,这类似图1所示的微波传输。假定把1伏特的电压阶梯波加到这条传输线中,如把1 伏特的电池连接到传输线的前端(它位于发送线路和回路之间),一旦连接,这个电压波信号沿着该线以光速传播,它的速度通常约为6英寸/纳秒。当然,这个信号确实是发送线路和回路之间的电压差,它可以从发送线路的任何一点和回路的相临点来衡量。图2是该电压信号的传输示意图。 Zen的方法是先“产生信号”,然后沿着这条传输线以6英寸/纳秒的速度传播。第一个0.01纳秒前进了0.06英寸,这时发送线路有多余的正电荷,而回路有多余的负电荷,正是这两种电荷差维持着这两个导体之间的1伏电压差,而这两个导体又组成了一个电容器。 在下一个0.01纳秒中,又要将一段0.06英寸传输线的电压从0调整到1伏特,这必须加一些正电荷到发送线路,而加一些负电荷到接收线路。每移动0.06英寸,必须把更多的正电荷加到发送线路,而把更多的负电荷加到回路。每隔0.01纳秒,必须对传输线路的另外一段进行充电,然后信号开始沿着这一段传播。电荷来自传输线前端的电池,当沿着这条线移动时,就给传输线的连续部分充电,因而在发送线路和回路之间形成了1伏特的电压差。每前进0.01纳秒,就从电池中获得一些电荷(±Q),恒定的时间间隔(±t)内从电池中流出的恒定电量(±Q)就是一种恒定电流。流入回路的负电流实际上与流出的正电流相等,而且正好在信号波的前端,交流电流通过上、下线路组成的电容,结束整个循环过程。 PCB(Printed Circuit Board)印刷电路板的缩写 编辑本段具体方法 1. 目的和作用 1.1 规范设计作业,提高生产效率和改善产品的质量。 2. 适用范围 1.1 XXX 公司开发部的VCD超级VCDDVD音响等产品。 3. 责任态度

PCB设计模拟题答案

第七届全国信息技术应用水平大赛模拟题 PCB设计 注:实际预赛题题量总计87道,其中单选题60道,每道题1分;多选题20道,每道题2分;简答题4题,每题7分,综合设计题2-3题,共计22分,试卷满分150分,完成时间180分钟。此模拟题仅供参考,具体题型、题量与分值分配以实际预赛题为准。 一、单选题(共60题,每题1分,共60分) 1.Room的主要优点是?() A.Room把功能电路集中在一个区域,布局看上去更加简洁整齐 B.Room可以智能分割元器件,自动创建元件类 C.Room可以关联多个元器件,用于功能电路布局和走线,并可以复制其格式到类似设计中 D.可以利用查询语句来选中编辑位于Room之中的元件,从而进行批量操作 2.为什么需要对PCB项目进行配置?() A.因为需要在配置中选择项目中所用到的所有派生变量,不同的变量针对不同的产品 B.因为项目配置可以发布到数据保险库的某个特定Item之中,从而进行版本更新和控制 C.因为配置代表需要在真实世界中制造的产品,定义了生产厂家制造该产品所需要的数据 D.如果不对PCB项目进行配置,则无法生成相应的Gerber等文件,无法进行裸板的生产 3.关于层次化设计,哪种说法不正确?() A.跨越不同原理图页的网络之间可以直接连接 B.使用图表符表示设计中较低等级的原理图页 C.为读者显示了工程的设计结构 D.视图上来看总是从子原理图向上追溯到父原理图 4.用来浏览与编辑封装库的面板是?() A.Library面板

B.PCB Library面板 C.SCH Library面板 D.PCB List面板 5.如何为原理图文档添加参数?() A.在项目选项(Project Option)对话框的参数(Parameter)标签页添加 B.直接在原理图上放置文本 C.在元件属性对话框中添加 D.在原理图文档选项(Document Option)对话框的参数(Parameter)标签页添加 6.*.schdot文档是什么类型的文档?() A.原理图文件 B.原理图模板文件 C.原理图库文件 D.PCB文件 7.下图是PCB 3D视图中的一部分,其中的元件的封装最可能是() A.SOT23-5; B.SOIC-5; C.QFN-5; D.TQFP-5. 8.下列哪个层是负片(绘制的图形表示切割或镂空)() A.Keep Out ; B.Power Plane;

PCB测试方法

PCB Check List 操作过程及操作要求: 一、棕化剥离强度试验: 1.1 测试目的:确定棕化之抗剥离强度 1.2 仪器用品:1OZ铜箔、基板、拉力测试机、刀片 1.3 试验方法: 1.3.1 取一张适当面积的基板,将两面铜箔蚀刻掉。 1.3.2 取一张相当大小之1OZ铜箔,固定在基板上。 1.3.3 将以上之样品按棕化→压合流程作业,压合迭合PP时,铜箔棕化面与PP接触。

1.3.4 压合后剪下适合样品,用刀片割板面铜箔为两并行线,长约10cm,宽≧3.8mm。 1.3.5 按拉力测试机操作规范测试铜箔之剥离强度。 1.4 计算: 1.5 取样方法及频率:取试验板1PCS/line/周 二、切片测试: 2.1 测试目的:压合一介电层厚度; 钻孔一测试孔壁之粗糙度; 电镀一精确掌握镀铜厚度; 防焊-绿油厚度; 2.2 仪器用品:砂纸,研磨机,金相显微镜,抛光液,微蚀液 2.3 试验方法:2.3试验方法: 2.3.1 选择试样用冲床在适当位置冲出切片。 2.3.2 将切片垂直固定于模型中。 2.3.3 按比例调和树脂与硬化剂并倒入模型中,令其自然硬化。 2.3.4 以砂纸依次由小目数粗磨至大目数细磨至接近孔中心位置 2.3.5 以抛光液抛光。 2.3.6 微蚀铜面。 2.3.7 以金相显微镜观察并记录之。 2.4 取样方法及频率: 电镀-首件,1PNL/每缸/每班,自主件2PNL/每批,测量孔铜时取9点,测量面铜时C\S面各取9点。 钻孔-首件,(1PNL/轴/4台机/班,取钻孔板底板)打板边切片位置,读最大孔壁粗糙度数值。压合-首件,(每料号1PNL及测试板厚不合格时)取压合板边任一位置。 (注:压合介电层厚度以比要求值小于或等于1mil作允收。) 防焊-首件,(1PNL/4小时)取独立线路。 三、补线焊锡/电阻值测试: 3.1测试目的:为预知产品补线处经焊锡后之品质和补线处的电阻值。 3.2仪器用品:烘箱、锡炉、秒表、助焊剂、金相显微镜、欧姆表、修补刀。 3.3试验方法: 3.3.1 选取试样置入烤箱烘150℃,1小时﹐操作时需戴粗纱手套﹐并使用长柄夹取放样品。 3.3.2 取出试样待其冷却至室温。 3.3.3 均匀涂上助焊剂直立滴流5~10秒钟,使多余之助焊剂得以滴回。 3.3.4 于288℃±5℃之锡炉中完全浸入锡液10±1秒/次,3次(补线处须完全浸入),每次浸锡后先冷却再重浸。 3.3.5 试验后将试样清洗干净检查补线有无脱落。 3.3.6 若不能判别时做补线处的切片,用金相显微镜观查补线处有无异常。 3.4 电阻值测试方法: 3.4.1 补线后用修补刀刮去补线处两端的覆盖物(防焊漆、铜面氧化层),不可伤及铜面。 3.4.2 用欧姆表测补线处两端的电阻值。 3.4.3 取样方法及频率:取成品板及半成品板各1PCS/周/每位补线操作员 四、绿油溶解测试:

PCB电路板测试 检验及规范

PCB电路板测试、检验及规范 1、Acceptability,acceptance 允收性,允收 前者是指在对半成品或成品进行检验时,所应遵守的各种作业条件及成文准则。后者是指执行允收检验的过程,如Acceptance Test。 2、Acceptable Quality Level(AQL)允收品质水准 系指被验批在抽检时,认为能满足工程要求之"不良率上限",或指百分缺点数之上限。AQL并非为保护某特别批而设,而是针对连续批品质所定的保证。 3、Air Inclusion 气泡夹杂 在板材进行液态物料涂布工程时,常会有气泡残存在涂料中,如胶片树脂中的气泡,或绿漆印膜中的气泡等,这种夹杂的气泡对板子电性或物性都很不好。 4、AOI 自动光学检验 Automatic Optical Inspection,是利用普通光线或雷射光配合计算机程序,对电路板面进行外观的视觉检验,以代替人工目检的光学设备。 5、AQL 品质允收水准 Acceptable Quality Level,在大量产品的品检项目中,抽取少量进行检验,再据以决定整批动向的品管技术。 6、ATE 自动电测设备 为保证完工的电路板其线路系统的通顺,故需在高电压(如250 V)多测点的泛用型电测母机上,采用特定接点的针盘对板子进行电测,此种泛用型的测试机谓之Automatic Testing Equipment。 7、Blister 局部性分层或起泡 在电路制程中常会发生局部板面或局部板材间之分层,或局部铜箔浮离的情形,均称为Blister。另在一般电镀过程中亦常因底材处理不洁,而发生镀层起泡的情形,尤其以镀银对象在后烘烤中最容易起泡。 8、Bow,Bowing 板弯 当板子失去其应有的平坦度(Flatness)后,以其凹面朝下放在平坦的台面上,若无法保持板角四点落在一个平面上时,则称为板弯或板翘(Warp 或Warpage),若只能三点落在平面上时,称为板扭(Twist)。不过通常这种扭翘的情况很轻微不太明显时,一律俗称为板翘(Warpage)。 9、Break-Out 破出 是指所钻的孔已自配圆(Pad)范畴内破出形成断环情形;即孔位与待钻孔的配圆(Pad)二者之间并未对准,使得两个圆心并未落在一点上。当然钻孔及影像转移二者都有可能是对不准或破出的原因。但板子上好几千个孔,不可能每个都能对准,只要未发生"破出",而所形成的孔环其最窄处尚未低于规格(一般是2 mil 以上),则可允收。 10、Bridging 搭桥、桥接 指两条原本应相互隔绝的线路之间,所发生的不当短路而言。 11、Certificate证明文书 当一特定的"人员训练"或"品质试验"执行完毕,且符合某一专业标准时,特以书面文字记载以兹证明的文件,谓之Certificate。 12、Check List 检查清单 广义是指在各种操作前,为了安全考虑所应逐一检查的项目。狭义指的是在PBC 业中,客户到现场却对品质进行了解,而逐一稽查的各种项目。 13、Continuity 连通性 指电路中(Circuits)电流之流通是否顺畅的情形。另有Continuity Testing是指对各线路通电情况所进行的测试,即在各线路的两端各找出两点,分别以弹性探针与之做紧迫接触(全板以针床实施之),然后施加指定的电压(通常为实用电压的两倍),对其进行"连通性试验",也就是俗称的Open/Short Testing (断短路试验)。 14、Coupon,Test Coupon 板边试样 电路板欲了解其细部品质,尤其是多层板的通孔结构,不能只靠外观检查及电性测试,还须对其结构做进一步的微切片(Microsectioning)显微检查。因此需在板边一处或多处,设置额外的"通孔及线路"图样,做为监视该片板子结构完整性(Structure

PCB可靠性测试方法则要

PCB可靠性测试方法择要 操作过程及操作要求: 一、棕化剥离强度试验: 1.1 测试目的:确定棕化之抗剥离强度 1.2 仪器用品:1OZ铜箔、基板、拉力测试机、刀片 1.3 试验方法: 1.3.1 取一张适当面积的基板,将两面铜箔蚀刻掉。 1.3.2 取一张相当大小之1OZ铜箔,固定在基板上。 1.3.3 将以上之样品按棕化→压合流程作业,压合迭合PP时,铜箔棕化面与PP接触。

1.3.4 压合后剪下适合样品,用刀片割板面铜箔为两并行线,长约10cm,宽≧3.8mm。 1.3.5 按拉力测试机操作规范测试铜箔之剥离强度。 1.4 计算: 1.5 取样方法及频率:取试验板1PCS/line/周 二、切片测试: 2.1 测试目的:压合一介电层厚度; 钻孔一测试孔壁之粗糙度; 电镀一精确掌握镀铜厚度; 防焊-绿油厚度; 2.2 仪器用品:砂纸,研磨机,金相显微镜,抛光液,微蚀液 2.3 试验方法:2.3试验方法: 2.3.1 选择试样用冲床在适当位置冲出切片。 2.3.2 将切片垂直固定于模型中。 2.3.3 按比例调和树脂与硬化剂并倒入模型中,令其自然硬化。 2.3.4 以砂纸依次由小目数粗磨至大目数细磨至接近孔中心位置 2.3.5 以抛光液抛光。 2.3.6 微蚀铜面。 2.3.7 以金相显微镜观察并记录之。 2.4 取样方法及频率: 电镀-首件,1PNL/每缸/每班,自主件2PNL/每批,测量孔铜时取9点,测量面铜时C\S面各取9点。 钻孔-首件,(1PNL/轴/4台机/班,取钻孔板底板)打板边切片位置,读最大孔壁粗糙度数值。压合-首件,(每料号1PNL及测试板厚不合格时)取压合板边任一位置。 (注:压合介电层厚度以比要求值小于或等于1mil作允收。) 防焊-首件,(1PNL/4小时)取独立线路。 三、补线焊锡/电阻值测试: 3.1测试目的:为预知产品补线处经焊锡后之品质和补线处的电阻值。 3.2仪器用品:烘箱、锡炉、秒表、助焊剂、金相显微镜、欧姆表、修补刀。 3.3试验方法: 3.3.1 选取试样置入烤箱烘150℃,1小时﹐操作时需戴粗纱手套﹐并使用长柄夹取放样品。 3.3.2 取出试样待其冷却至室温。 3.3.3 均匀涂上助焊剂直立滴流5~10秒钟,使多余之助焊剂得以滴回。 3.3.4 于288℃±5℃之锡炉中完全浸入锡液10±1秒/次,3次(补线处须完全浸入),每次浸锡后先冷却再重浸。 3.3.5 试验后将试样清洗干净检查补线有无脱落。 3.3.6 若不能判别时做补线处的切片,用金相显微镜观查补线处有无异常。 3.4 电阻值测试方法: 3.4.1 补线后用修补刀刮去补线处两端的覆盖物(防焊漆、铜面氧化层),不可伤及铜面。 3.4.2 用欧姆表测补线处两端的电阻值。 3.4.3 取样方法及频率:取成品板及半成品板各1PCS/周/每位补线操作员 四、绿油溶解测试: 4.1测试目的:测试样本表面的防焊漆是否已经完成硬化,及足以应付在焊接时所产生热力。 4.2仪器用品:三氯甲烷、秒表、碎布 4.3测试方法:

《电路板测试手册》

仅供内部使用文档模板编号:M-G08730.5D-V4.0 XXX电路板测试手册 项目名称: 文档编号: 电路板版本号: 发布部门: 生效日期: 西安大唐电信有限公司 XI’AN DATANG TELEPHONE CORP

技术文档修改记录表

目录 1. 引言 (1) 1.1 目的和范围 (1) 1.2 输入文档 (1) 1.3 参考资料 (1) 1.4 术语约定 (1) 2. 测试范围 (1) 2.1.测试的内容 (1) 2.2,不测试的内容 (1) 3. 环境配置 (1) 4. 测试工具 (1) 5. 测试说明 (1) 6. 测试内容 (2)

1.引言 【提示文字:引言提出了对本文档的纵览,帮助读者理解该文档的编写目的,适用的读者,参考资料,术语解释等等。】 1.1 目的和范围 编写此电路板测试手册的目的是,在设计之时,测试之前明确测试要求,用以指导电路板设计人员进行设计之后的自测,同时在设计完成后作为项目测评和测试验证的参考。【建议直接引用】此文档的针对的读者是,评审的专家组成员、单板设计者、测试验证人员。【建议直接引用】 1.2 输入文档 【提示文字:拟制该文档时依据的任务书和上层技术文档,如XXX总体方案或XXX概要设计说明书、XXX详细设计说明书。】 1.3 参考资料 【提示文字:本文件中各处引用的文件、资料,包括所要用到的硬件开发标准,并列出这些文件的标题、文件编号、发表日期、出版单位、说明能够得到这些文件的来源。】 1.4 术语约定 【提示文字:提供正确理解该文档所包含的全部术语的定义、首字母缩写词和缩略语。】 2.测试范围 【提示文字:从总体上说明该版本测试范围,包括测试内容,不被测试内容。】 2.1 测试的内容 2.2 不测试的内容 3.环境配置 【提示文字:验证测试环境的系统图,必要时可包括环境配置图,基本数据配置说明(如果需说明的配置内容较多,可以设置为附录)。】 4.测试工具 对于验证测试中使用的仪表和工具(包括软件工具)进行介绍和说明。【此段文字保留,具体内容换行后描述】 5.测试说明 【提示文字:需要在测试前说明的注意事项、部分关键字的说明、执行原则,如,步骤的说明、部

PCB测试点

PCB测试点制作的一般要求 PCB测试点制作的一般要求 关键性元件需要在PCB上预设测试点。用于焊接外貌组装元件的焊盘不容许兼作检测点,必须另外预设专用的测试焊盘,以保证焊点检测和生产调试的没事了进行。用于测试的焊盘尽可能的安排于PCB的统一侧面上,即便于检测,又利于减低检测所花的费用。 1.工艺预设要求 (1) 测试点间隔PCB边缘需大于5mm; (2) 测试点不可被阻焊药或文字油墨笼罩; (3) 测试点最佳镀焊料或选用质地较软、易贯串、不易氧化的金属,以保证靠患上住接 地,延长探针施用寿命 (4) 测试点需放置在元件周围1mm之外,制止探针和元件撞击; (5) 测试点需放置在定位孔(配合测试点用来精确定位,最佳用非金属化孔,定位孔误 差应在±0.05mm内)环状周围3.2mm之外; (6) 测试点的直径不小于0.4mm,相邻测试点的间距最幸亏2.54mm以上,但不要小于 1.27mm; (7) 测试面不能放置高度超过6.4mm的元器件,过高的元器件将导致在线测试夹具探针 对测试点的接触不良; ⑻ 测试点中间至片式元件端边的间隔C与SMD高度H有如下关系:SMD高度H≤3mm, C≥2mm;SMD高度H≥3mm,C≥4mm。 (9) 测试点焊盘的巨细、间距及其布局还应与所采用的测试设备有关要求相匹配。 2.电气预设要求 (1) 尽量将元件面的SMC/SMD测试点通过过孔引到焊接面,过孔直径 大于1mm,可用单面针床来测试,减低测试成本;

(2) 每个电气接点都需有一个测试点,每个IC需有电源和接地测试点,且尽可能接近 元件,最幸亏2.54mm之内; (3) 电路走线上设置测试点时,可将其宽度放大到1mm; (4) 测试点应均匀分布在PCB上,削减探针压应力集中; (5) PCB上供电线路应分区域设置测试断点,以便电源去耦合或妨碍点查询。设置断点 时应考虑恢复测试断点后的功率承载能力。 --------------- 问:PCB板如何留测试点? 答:今日电子产品越趋轻薄短小,PCB之预设布线也越趋复杂坚苦,除需统筹功能性与安全性外,更需可生产及可测试。兹就可测性之需求,提供法则供预设布线工程师参考。如能注重为之,将可为贵公司省下可观之治具制作费用并促进测试之靠患上住性与治具之施 用寿命。 LAYOUT法则 1.虽然有双面治具,但最佳将被测点放在统一面。以能做成单面测试为考虑重点。 若有坚苦则TOP SIZE针点要少于BOTTON SIZE。 2. 测点优先级:Ⅰ. 测试点(Test pad) Ⅱ. 零件脚(Component lead) Ⅲ. 贯串孔(Via hole)-->但不可Mask. 3. 二被测点或被测点与预钻孔之中间距不患上小于1.27mm(50mil)。以大于 2.54mm(100mil)为佳。其次是1.905mm(75mil)。 4. 被测点应离其附近零件(位于统一面者)至少2.54mm。如为高于3mm零件,则应至少 间距3.05mm。 5. 被测点应平均分布于PCB外貌,制止局部密渡过高。

电路版图设计的常见问题

Pcb板电路版图设计的常见问题 问题1:什么是零件封装,它和零件有什么区别? 答:(1)零件封装是指实际零件焊接到电路板时所指示的外观和焊点位置。 (2)零件封装只是零件的外观和焊点位置,纯粹的零件封装仅仅是空间的概念,因此不同的零件可以共用同一个零件封装;另一方面,同种零件也可以有不同的封装,如RES2代表电阻,它的封装形式有AXAIL0.4 、AXAIL0.3 、AXAIL0.6等等,所以在取用焊接零件时,不仅要知道零件名称还要知道零件的封装。 (3) 零件的封装可以在设计电路图时指定,也可以在引进网络表时指定。设计电路图时,可以在零件属性对话框中的Footprint设置项内指定,也可以在引进网络表时也可以指定零件封装。 问题2:导线、飞线和网络有什么区别? 答:导线也称铜膜走线,简称导线,用于连接各个焊点,是印刷电路板最重要的部分,印刷电路板设计都是围绕如何布置导线来进行的。 与导线有关的另外一种线,常称之为飞线也称预拉线。飞线是在引入网络表后,系统根据规则生成的,用来指引布线的一种连线。 飞线与导线是有本质的区别的。飞线只是一种形式上的连线,它只是形式上表示出各个焊点间的连接关系,没有电气的连接意义。导线则是根据飞线指示的焊点间连接关系布置的,具有电气连接意义的连接线路。 网络和导线是有所不同的,网络上还包括焊点,因此在提到网络时不仅指导线而且还包括和导线相连的焊点。 问题3:内层和中间层有什么区别? 答:中间层和内层是两个容易混淆的概念。中间层是指用于布线的中间板层,该层中布的是导线;内层是指电源层或地线层,该层一般情况下不布线,它是由整片铜膜构成。 问题4:什么是内部网络表和外部网络表,两者有什么区别? 答:网络表有外部网络表和内部网络表之分。外部网络表指引入的网络表,即Sch 或者其他原理图设计软件生成的原理图网络表;内部网络表是根据引入的外部网络表,经过修改后,被PCB系统内部用于布线的网络表。严格的来说,这两种网络表是完全不同的概念,但读者可以不必严格区分。 问题5:网络表管理器有什么作用? 答:第一,引入网络表,这种网络表的引入过程实际上是将原理图设计的数据加载到印刷电路板设计系统PCB的过程。PCB设计系统中数据的所有变化,都可以通过网络宏(Netlist Macro)来完成,系统通过比较、分析网络表文件和PCB系统的内部数据,自动产生网络宏。 第二,可以利用网络表管理器直接在PCB系统中编辑电路板各个组件间的连接关

PCB可靠性及名词解释

线路板可靠性与微切片中英名词解释(一) 1、Abrasion Resistance耐磨性 在电路板工程中,常指防焊绿漆的耐磨性。其试验方法是以 1 k g 重的软性砂轮,在完成绿漆的IP-B-25样板上旋转磨擦 50 次,其梳型电路区不许磨破见铜(详见电路板信息杂志第 54 期P.70),即为绿漆的耐磨性。某些规范也对金手指的耐磨性有所要求。又,Abrasive是指磨料而言,如浮石粉即是。Accelerrated Test(Aging)加速试验,加速老化也就是加速老化试验(Aging)。如板子表面的熔锡、喷锡或滚锡制程,其对板子焊锡性到底能维持多久,可用高温高湿的加速试验,仿真当板子老化后,其焊锡性劣化的情形如何,以决定其品质的允收与否。此种人工加速老化之试验,又称为环境试验,目的在看看完工的电路板(已有绿漆)其耐候性的表现如何。新式的"电路板焊锡性规范"中(ANSI/J- STD-003,本刊 57 期有全文翻译)已有新的要求,即高可靠度级CLASS 3的电路板在焊锡性(Solderability)试验之前,还须先进行 8 小时的"蒸气老化"(Steam Aging),亦属此类试验。 2、Accuracy 准确度 指所制作的成绩与既定目标之间的差距。例如所钻成之孔位,有多少把握能达到其"真位"(True Position)的能力。 3、Adhesion 附着力 指表层对主体的附着强弱而言,如绿漆在铜面,或铜皮在基材表面,或镀层与底材间之附着力皆是。 4、Aging 老化 指经由物理或化学制程而得到的产物,会随着时间的经历而逐渐失去原有的品质,这种趋向成熟或劣化的过程即称之"Aging"。不过在别的学术领域中亦曾译为"经时反应"。 5、Arc Resistance 耐电弧性 指在高电压低电流下所产生的电弧,当此电弧在绝缘物料表面经过时,物料本身对电弧

PCB测试工艺及技术方法详解模板

PCB测试工艺及技术方法 详解模板

少一些普通工艺冋题 By Craig Pynn 欢迎来到工艺缺陷诊所。这里所描述的每个缺陷都将覆盖特 殊的缺陷类型,将存档成为将来参考或培训新员工的一个无价的工艺缺陷指南。 大多数公司现在正在使用表直贴装 技术,同时又向球栅阵列(BGA)、芯片规 模包装(CSP)和甚至倒装芯片装配迈进。 可是,一些公司还在使用通孔技术。通孔 技术的使用不一定是与成本或经验有关- 可能只杲由于该产品不需要小型化。许多公司继续使用传统的通孔元件,并将继续在混合技术产品上使用这些零件。 本文要看看一些不够普遍的工艺问题。希望传统元件装配冋题及 其实际解决办法将帮助提供对在今天的制造中什么可能还会出错的洞察。 静电对元件的破坏 从上图,我们使用光学照片与扫描电子显 微镜(SEM, scanning electron microscopy) 看到在一个硅片表⑥上的 静电击穿。静电放电,引入到一个引脚,引起元件的工作状态的改

变,导致系统失效。在实验室对静电放电的模拟也能够显示实时发生在芯片表廂的失效。如上面的照片所示,静电可能是一个问题, 解决办法是一个有效的控制政策。手腕带是最初最重要的防御。 树枝状晶体增长 树枝状结晶发生在施加的电压与潮 湿和一些可离子化的产品出现时。电压 总是要在一个电路上,但潮湿含量将取决 于应用与环境。可离子化材料可能来自印刷 电路板(PCB)的表⑥, 由于装配期间或在空板制造阶段时的不良清洁。 如果要调查这类缺陷,不要接触板或元件。在失效原因的所有证据毁灭之前,让缺陷拍成照片并进行研究。污染可能经常来自焊接过程或使用的助焊剂。另一个可能性是装配期间带来的一般操作污垢。工业中最普遍的缺陷原因来自助焊剂残留物。 在上面的例子中,失效发生在元件的返修之后。这个特殊的电话单元是由一个第三方公司使用高活性助焊剂返修的,不象原来制造期间使用的低活性材料。 焊盘破裂 当元件或导线必须作为一个第二阶段装配安装时,一般使用C 形焊盘。例子有,重型元件、线编织或不能满足焊接要求的元件。在某些情况中,品质人员不知道破裂的原因,以为是PCB腐蚀

pcb信赖性测试

PCBf言赖性测试项目的品质要求和判定标准

(2)操作过程及操作要求: 一、棕化剥离强度试验: 1.1测试目的:确定棕化之抗剥离强度 1.2仪器用品:1OZ铜箔、基板、拉力测试机、刀片 1.3试验方法: 1.3.1取一张适当面积的基板,将两面铜箔蚀刻掉。 1.3.2取一张相当大小之1OZ铜箔,固定在基板上。 1.3.3将以上之样品按棕化-压合流程作业,压合迭合PP时,铜箔棕化面与PP接触1.3.4压合后剪下适合样品,用刀片割板面铜箔为两并行线,长约10cm,宽三3.8mm。 1.3.5按拉力测试机操作规范测试铜箔之剥离强度。 1.4计算: 1.5取样方法及频率:取试验板1PCS/ line/周 二、切片测试: 2.1测试目的:压合一介电层厚度; 钻孔一测试孔壁之粗糙度; 电镀一精确掌握镀铜厚度; 防焊-绿油厚度; 2.2仪器用品:砂纸,研磨机,金相显微镜,抛光液,微蚀液 2.3试验方法: 2.3.1选择试样用冲床在适当位置冲出切片。

2.3.2将切片垂直固定于模型中。 2.3.3按比例调和树脂与硬化剂并倒入模型中,令其自然硬化。 2.3.4以砂纸依次由小目数粗磨至大目数细磨至接近孔中心位置 2.3.5 以抛光液抛光。 2.3.6微蚀铜面。 2.3.7以金相显微镜观察并记录之。 2.4取样方法及频率: 电镀—首件,1PNL/每缸/每班,自主件2PNL/每批,测量孔铜时取9点,测量面铜时C\S 面各取9 点。 钻孔-首件,(1PNL/轴/4台机/班,取钻孔板底板)打板边切片位置,读最大孔壁粗糙度数值。 压合—首件,(每料号1PNL 及测试板厚不合格时)取压合板边任一位置。 (注:压合介电层厚度以比要求值小于或等于1miI作允收。) 防焊—首件,(1PNL/4 小时)取独立线路。 三、绿油硬度测试: 6.1测试目的:试验绿油的硬度。 6.2仪器用品:标准硬度的铅笔:6H 型号铅笔 6.3测试方法: 6.3.1用削笔刀削好铅笔,用细砂纸将笔咀磨尖。 6.3.2将样本水平放置于工作台面,首先用6H铅笔以一般力度在样本表面,倾斜45度,然后将铅笔以向样本方向推,使笔尖在防焊漆表面划过约1/4" 长。 6.3.3如防焊漆面没有被划花或破坏,则代表样本的硬度>6H 。

PCB四密度通用测试技术介绍

四密度通用测试技术介绍 1 通用测试技术的起源和发展 最早的PCB通用电性测试技术可追溯至七十年代末八十年代初, 由于当时的元器件均采用标准封装(Pitch为100mil), PCB亦只有THT(通孔技术)密度层次, 所以欧美测试机厂商就设计了一款标准网格的测试机, 只要PCB上的元件和布线是按照标准距离排布的,则每个测试点均会落在标准网格点上, 因为当时所有PCB都能通用, 故称为通用测试机。由于半导体封装技术的发展, 元器件开始有了更小的封装及贴片(SMT)封装, 标准密度通用测试开始不再适用, 于是九十年代中期, 欧美的测试厂商又推出了双倍密度测试机, 并结合用一定的钢针斜率制造夹具以转换PCB测试点与机器网格连接, 随着HDI制程工艺的逐渐成熟, 双倍密度通用测试又不能完全满足测试的需求,于是在二000年左右, 欧洲测试机厂商又推出了四倍密度网格通用测试机。图一为网格规格: (图一) 网格密度 单密度双密度四密度

2 通用测试的关键技术 2·1开关元件 要满足大部份HDI PCB的测试要求, 测试面积必须要足够大, 通常有以下标准尺寸: 9.6×12.8(inch)、16 X12.8(inch)、24×19.2(inch), 在双密度满网格(Full Grid)情况下, 上述三种尺寸测试点数分别是49512、81920、184320, 电子元件的数量高达数十万, 开关元件是保证测试稳定的一个核心元件, 要求其具有耐高压(>300V)、低漏电等性能, 同时电阻值等电气性能要均衡一致,所以这类元件一定要经过严格的筛选与检测, 通常以晶体管或场效应管作为开关元件,基本线路如图二所示: 图(二):开关回路 晶体三极管的优缺点: 优点: 成本低,抗静电击穿能力强, 稳定性高; 缺点: 电流驱动,电路比较复杂, 需隔离基流(Ib)影响, 功耗大 场效应管的优缺点: 优点: 电压驱动, 电路简单, 不受基流(Ib)影响,功耗小 缺点: 成本高, 极易发生静电击穿, 需加静电保护措施, 稳定性不高, 所以会增加维修成本。 2·2 网格点的独立性 满网格(Full Grid) 每个网格有独立的开关回路, 即每个点都占用一组开关元件及线路,整个测试面积都能按四倍密度撒针; 共享网格(Share Grid) 由于满网格的开关元件数量多且线路比较复杂, 难于实现,所以某些测试厂商使用网格共用技术,使不同区域的几个点共用一组开关元件和线路,从而减小了布线的难度和开关元件的数量,我们称之为共享网格(Share Grid)。共享网格有一个很大的缺陷,假如一个区域的点己经被完全占用了, 那么与之共享的区域的点就不能再用,以至降低了该区域的密度为单密度。所以在较大面积HDI测试仍存在密度的瓶颈。

信赖性试验标准规范

深圳市超思维电子有限公司SHENZHEN CHAOSIWEI ELECTRONIC CO.,LTD 文件修(制)订履历一览表 N0. 版 次 发布日期修(制)订说明拟制审核批准备注 1 A0 2012-5-4 信赖性试验标准规范谢金华文件发放范围及份数(“( )”填写分发范围“[ ]”填写发放份数): ( √ ) 1、总经理[ 1 ] ( √ ) 2、副总经理 [ 1 ] ( √ ) 3、总经理助理[ 1 ] ( √ ) 4、管理者代表[ 1 ] ( √ ) 5、市场部[ 1 ] ( √ ) 6、品质部[ 1 ] ( √ ) 7、工程部[ 1 ] ( √ ) 8、物控部[ 1 ] (√ ) 9、生产部[ 1 ] ( √ ) 10、行政人事部[ 1 ] ( √ ) 11、财务部[ 1 ] ( √ ) 12、采购部[ 1 ] 备注唯盖有红色的DCC正本受控章方为正式有效文件。 制作审核批准日期日期日期

一.目的 针对本公司产品制定信赖性试验规范,有利于品质保证制度之推行,促使可靠性测试标准化。 二. 适用范围 本规范适用于公司所有艾天成品信赖性测试实验时的操作作业. 三. 定义 可靠性:制品的动作或性能时间稳定性的程度或性质。 四.权责 生产部:信赖性测试用成品的提供; 品质部:信赖性计划的制定与实施 工程部:信赖性测试技术分析的支援 五.检验数量 每个项目要取12PCS做此可靠性测试实验. 六. 实验项目 高溫实验 试验目的:检验产品在高温环境条件下贮存的适用性 试验设备:恒温恒湿试验箱 实验条件:在85℃存放96小时后,在正常温度(25℃)下放置30分钟,然后测试其功能 实验方法:取功能及外观合格的成品,放置于恒温恒湿箱內,机器通电运行96H后,取出在正常温度(25℃)下放置30分钟检查无性能不良. 低温实验 试验目的:检验产品在低温环境条件下贮存的适用性 试验设备:恒温恒湿试验箱 实验条件:在-25℃存放96小时后,在正常温度(25℃)下放置30分钟,然后测试其功能。

PCB电路版图设计的常见问题

PCB电路版图设计的常见问题 问题1:什么是零件封装,它和零件有什么区别? 答:(1)零件封装是指实际零件焊接到电路板时所指示的外观和焊点位置。 (2)零件封装只是零件的外观和焊点位置,纯粹的零件封装仅仅是空间的概念,因此不同的零件可以共用同一个零件封装;另一方面,同种零件也可以有不同的封装,如RES2代表电阻,它的封装形式有AXAIL0.4 、AXAIL0.3 、AXAIL0.6等等,所以在取用焊接零件时,不仅要知道零件名称还要知道零件的封装。 (3) 零件的封装可以在设计电路图时指定,也可以在引进网络表时指定。设计电路图时,可以在零件属性对话框中的Footprint设置项内指定,也可以在引进网络表时也可以指定零件封装。 问题2:导线、飞线和网络有什么区别? 答:导线也称铜膜走线,简称导线,用于连接各个焊点,是印刷电路板最重要的部分,印刷电路板设计都是围绕如何布置导线来进行的。 与导线有关的另外一种线,常称之为飞线也称预拉线。飞线是在引入网络表后,系统根据规则生成的,用来指引布线的一种连线。 飞线与导线是有本质的区别的。飞线只是一种形式上的连线,它只是形式上表示出各个焊点间的连接关系,没有电气的连接意义。导线则是根据飞线指示的焊点间连接关系布置的,具有电气连接意义的连接线路。 网络和导线是有所不同的,网络上还包括焊点,因此在提到网络时不仅指导线而且还包括和导线相连的焊点。 问题3:内层和中间层有什么区别? 答:中间层和内层是两个容易混淆的概念。中间层是指用于布线的中间板层,该层中布的是导线;内层是指电源层或地线层,该层一般情况下不布线,它是由整片铜膜构成。 问题4:什么是内部网络表和外部网络表,两者有什么区别? 答:网络表有外部网络表和内部网络表之分。外部网络表指引入的网络表,即Sch或者其他原理图设计软件生成的原理图网络表;内部网络表是根据引入的外部网络表,经过修改后,被PCB系统内部用于布线的网络表。严格的来说,这两种网络表是完全不同的概念,但读者可以不必严格区分。 问题5:网络表管理器有什么作用? 答:第一,引入网络表,这种网络表的引入过程实际上是将原理图设计的数据加载到印刷电路板设计系统PCB的过程。PCB设计系统中数据的所有变化,都可以通过网络宏(Netlist Macro)来完成,系统通过比较、分析网络表文件和PCB系统的内部数据,自动产生网络宏。 第二,可以利用网络表管理器直接在PCB系统中编辑电路板各个组件间的连接关系,