实验一 二输入端与非门的设计EPM7128-bdf_百度文库.

实验一二输入端与非门的设计

利用EDA-V+板,使用Quartus II 9.0软件,完成实验内容。

二输入端与非门有2个输入端,1个输出端。在

EPM7128SLC84-15芯片内实现功能,选择合适的引脚。1. 实验目的

掌握Quartus II 9.0软件的使用;

学会实验箱EDA-V+资源的使用。

2. 实验原理

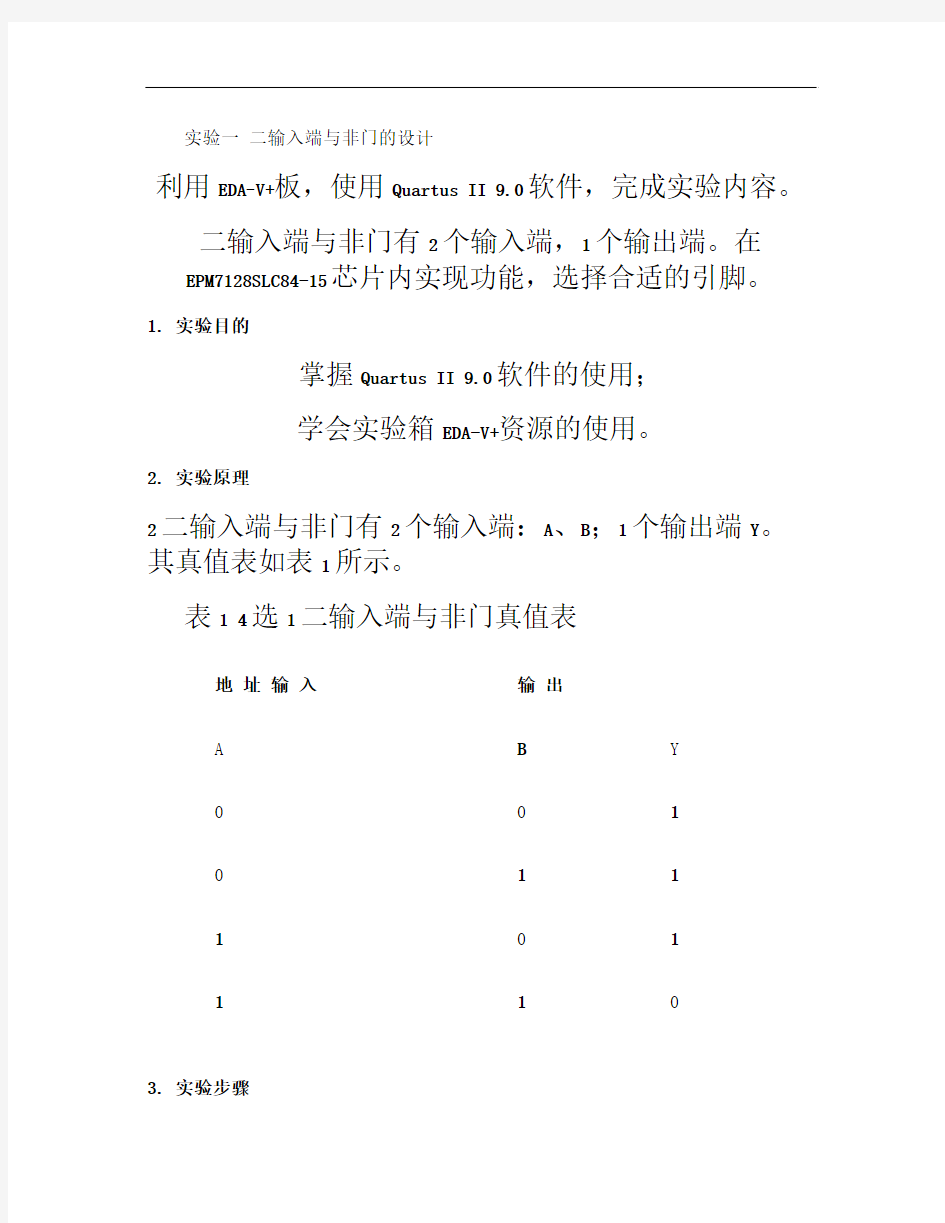

2二输入端与非门有2个输入端:A、B;1个输出端Y。其真值表如表1所示。

表1 4选1二输入端与非门真值表

地址输入输出

A B Y

0 0 1

0 11

10 1

110

3. 实验步骤

(1 建立工程项目:

确定具有合法的密码文件后,安装进入如下提示:

图1

点击NEXT进入建立工程对话窗口:

图2

或者,从主菜单选取File→New Project Wizard,同样出现图

2。来创建工程。

图3 从主下拉菜单主选择路径新建工程项目

出现对话框如图4所示。

图4 新建工程

更改工程保存的路径为D:\EDA_test\2nand,工程名称为2nand,文件名称为2nand,点击Next,提示是否创建“D:\EDA_test\2nand”?

选择“是”,出现:

在上图中的File name对话框内输入2nand.bdf,

然后,点击右侧的Add。

图3 添加文件到工程中

接着点击Next,在下图中选择所使用的器件。在

Family“系列”下拉窗口中选择MAX7000S,在Available devices 下选择EPM7128SLC84-15具体器件。

图4 选择器件

在图4中,点击Next进入图5。

图5 选择第三方工具

在图5中取默认值,直接点击Next进入图6。

图6 工程信息

点击Finish完成工程设置,这时在Project Navigator下的实体Entity下出现multi_4v的工程,见图7所示。

图7 全局窗口

综上,建立了一个名称为“2nand”的工程,接下来需要在工程下建立需要的文件。

(2建立文件:选取窗口菜单File→New,

图8 建立文件

出现对话框,如图9。选Block Diagram/Schematic File选项,建立原理图文件。单击OK按钮,进入文本编辑画面。

图9 建立文件对话框

输入原理图文件内容到编辑窗口。方法是:在编辑的栅格处,双击鼠标左键,在弹出的对话框中的Name处输入“nand2”元件名,可以看到,NAND2元件的样图显示出来了。然后,点击“OK”。一个NAND2元件元件就被放置到了原理图编辑对话框

中了。

图10A 原理图文件输入和编辑对话框

接下来,用同样的方法安放输入和输出引脚。在编辑栅格的空白处,双击鼠标左键,在弹出的对话框中的Name处键入“INPUT”元件名。然后,点击“OK”。一个INPUT元件就被放置到了原理图编辑对话框中了。同样,再安放“OUTPUT”元件。

图10B 原理图文件输入和编辑对话框

接下来,进行连线。鼠标移动到元件的引脚旁时,会出现连线的标志,此时按住鼠标左键,在目标处放开鼠标左键,一条连线就画成功了。完成下图的连线。

图10 原理图

编辑引脚的名称。如双击一条“INPUT”引脚,如下图。在“Pin name(s”处输入“A”。

另一输入引脚,和一个输出引脚,同样编辑。最后形成下图所示的电路。

(3 保存:选取窗口菜单File→Save as,出现对话框,键入文件名2nand.bdf,

图11 文件保存

单击“保存”按钮保存文件。

(4编译:选取窗口菜单Processing→Start Compila tion,或点击快捷按钮进行编译。

图12 编译工程选项

编译工程需要一段时间,见图13的编译过程进程显示。

图13 编译工程进程

图14 编译结束

需要排除编译中产生的所有错误,某些警告可以忽略。点击“确定”。

(5 引入输入/输出脚:选取窗口菜单Assignments → Pins,图13对话框。

图15 引入输入/输出脚对话框

图16 编辑引入输入/输出脚对话框

在图14中,拖动A、B、Y引脚到图中的引脚。在此选:

A→9→D1

B→10→D2

Y→11→LED1

将Node Name下的名称(如A一个一个地拖动到Pin Planner对应的引脚标号处(如15)。

图17 引脚分布

此步骤不用保存,将上面的对话框关到最小即可。这时,再查看原理图,已经

有了对应的引脚。

在主菜单Assignments→Pins或Assignments→Pin Planner均可打开图20,

用以观察引脚分布。

或

图18 引脚分布图观察操作

(6 编辑输入/输出脚之后,再执行项目编译:选取窗口菜单

Processing→Start Compilation,或点击快捷按钮进行编译。这样,可以形成对应编辑好引脚的对应文件,包括烧写文件等。

编译之后,就可以将程序代码烧写到CPLD或FPGA中,这一步我们放到第(8)步进行。

(7建立波形仿真文件:选取窗口菜单File→New,出现对话框,如图19。选Vector Waveform File选项,单击OK按钮,进入波形图编辑画面。

图19 建立波形仿真文件窗口

图20 建立波形仿真文件窗口

在引脚输入的“Name”区,点击鼠标右键,如图21在波形窗口中插入引脚。

图21 在波形窗口中插入引脚

可以在图22的“Name”区,输入引脚的名称,然后点击“OK”。这种方式一次只能输入一个引脚。下图是输入引脚“A”的示例,在此引脚的书写不分大小

写。逐一输入即可。

图22 一次输入一个引脚

或者在上图中,点击“Node Finder”,出现图23。

图23 批量一次性输入所有引脚到波形编辑窗口

在图23中,点击“List”。

图24 引入引脚

点击“≥”,将左侧发现的引脚选择有用的逐一添加到右侧窗口中,或者点击“》”,将左侧发现的引脚全部一次性地添加到右侧窗口中,在此点击“》”。见

图25。

图25 引入引脚对话框

点击OK,进入图26。

图26 引入引脚对话框

点击OK,进入图27。

图27 引入引脚

选中引脚图标,见图28,信号源图标变成实体。

图28 将各个引脚引入信号源信号源可以选择图标,如图29、30。

图29 引脚引入信号源设置

图30 引脚引入信号源设置

点击“确定”。同样,输入B引脚的波形。

或者选择图标,自编各个引脚的波形。引脚波形的构造要与系统的功能状态相吻合,便于验证系统功能。