教学设计 数字电子技术 实验报告.doc

实验一组合逻辑电路设计与分析

1.实验目的

(1)学会组合逻辑电路的特点;

(2)利用逻辑转换仪对组合逻辑电路进行分析与设计。

2.实验原理

组合逻辑电路是一种重要的数字逻辑电路:特点是任何时刻的输出仅仅取决于同一时刻输入信号的取值组合。根据电路确定功能,是分析组合逻辑电路的过程,一般按图1-1所示步骤进行分析。

图1-1 组合逻辑电路的分析步骤

根据要求求解电路,是设计组合逻辑电路的过程,一般按图1-2所示步骤进

行设计。

图1-2 组合逻辑电路的设计步骤

3.实验电路及步骤

(1)利用逻辑转换仪对已知逻辑电路进行分析。

a.按图1-3所示连接电路。

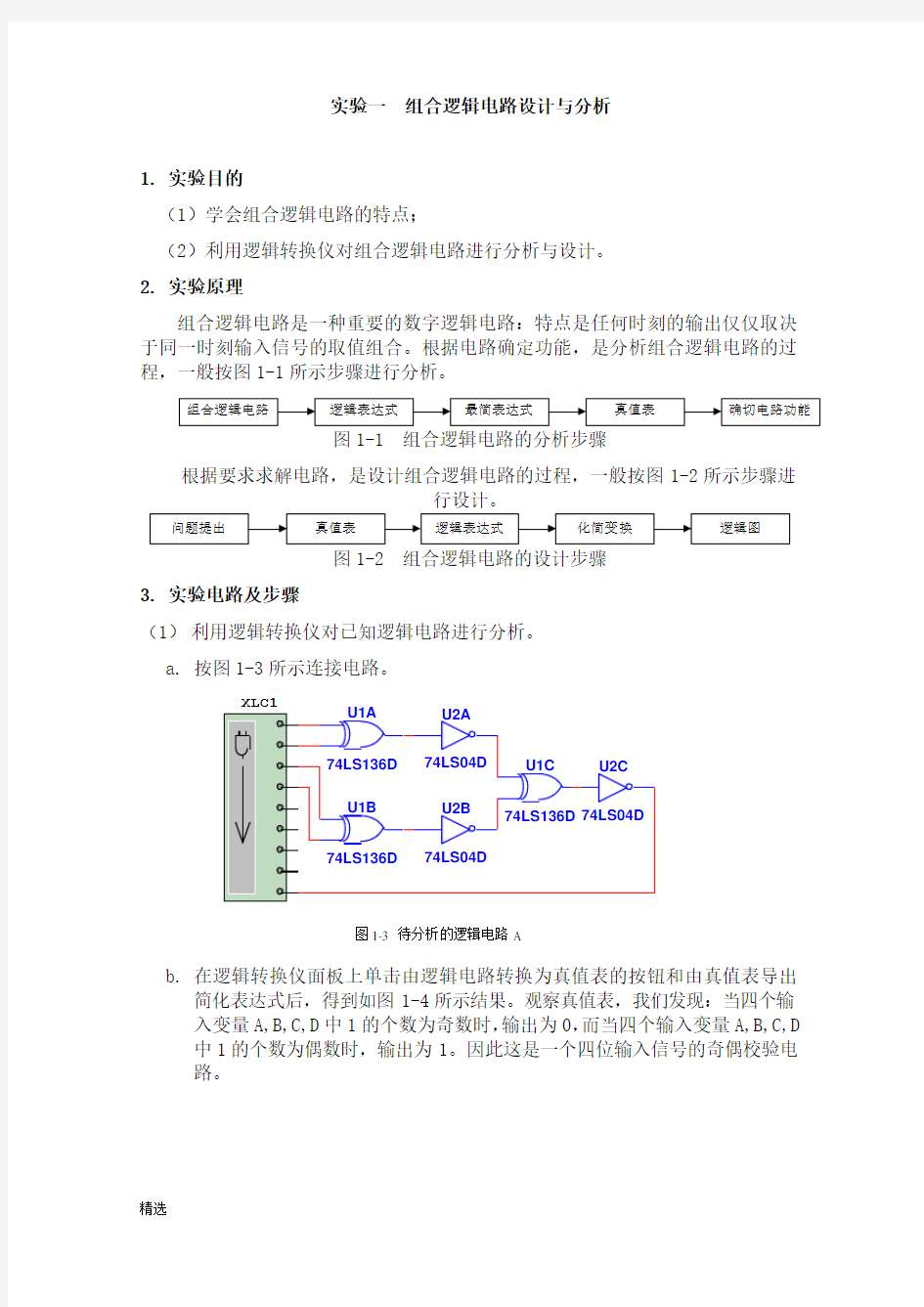

b.在逻辑转换仪面板上单击由逻辑电路转换为真值表的按钮和由真值表导出

简化表达式后,得到如图1-4所示结果。观察真值表,我们发现:当四个输入变量A,B,C,D中1的个数为奇数时,输出为0,而当四个输入变量A,B,C,D 中1的个数为偶数时,输出为1。因此这是一个四位输入信号的奇偶校验电路。

(2)

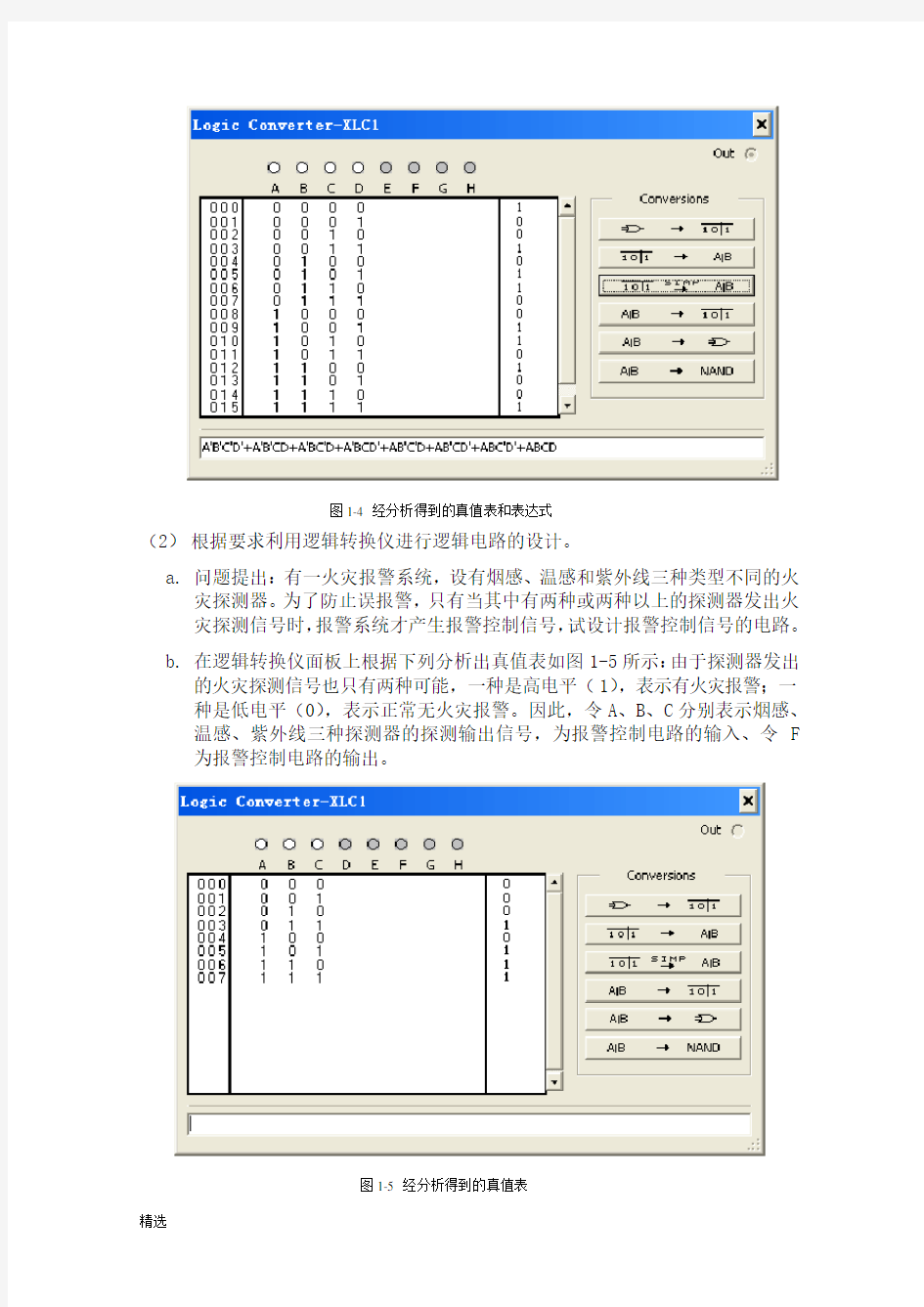

a.问题提出:有一火灾报警系统,设有烟感、温感和紫外线三种类型不同的火

灾探测器。为了防止误报警,只有当其中有两种或两种以上的探测器发出火灾探测信号时,报警系统才产生报警控制信号,试设计报警控制信号的电路。

b.在逻辑转换仪面板上根据下列分析出真值表如图1-5所示:由于探测器发出

的火灾探测信号也只有两种可能,一种是高电平(1),表示有火灾报警;一种是低电平(0),表示正常无火灾报警。因此,令A、B、C分别表示烟感、温感、紫外线三种探测器的探测输出信号,为报警控制电路的输入、令F 为报警控制电路的输出。

图1-4 经分析得到的真值表和表达式

图1-5 经分析得到的真值表

(3)在逻辑转换仪面板上单击由真值表到处简化表达式的按钮后得到最简化表达式AC+AB+BC。

4.实验心得

通过本次实验的学习,我们复习了数电课本关于组合逻辑电路分析与设计的相关知识,掌握了逻辑转换仪的功能及其使用方法。初步掌握了软件multisim的用法。

实验二编码器、译码器电路仿真实验

1.实验目的

(1)掌握编码器、译码器的工作原理。

(2)常见编码器、译码器的应用。

2.实验原理

所谓编码是指在选定的一系列二进制数数码中,赋予每个二进制数码以某一固定含义。例如,用二进制数码表示十六进制数叫做二—十六进制编码。能完成编码功能的电路统称为编码器。74LS148D是常用8线—3线优先编码器。在8个输入线上可以同时出现几个有效输入信号,但只对其中优先权最高的一个有效输入信号进行编码。其中7端优先权最高,0端优先权最低,其他端的优先权按端脚号的递减顺序排列。~E1为选通输入端,低电平有效,只有~E1=0时,编码器正常工作,而在~E1=1时,所以的输出端均被封锁。E0为选通输出端,GS为优先标志端。该编码器输入、输出均为低电平有效。

译码器是编码的逆过程,将输入的每个二进制代码赋予的含义“翻译”过来,给出相应的输出信号。能够完成译码功能的电路焦作译码器。74LS138D属于3线—8线译码器。该译码器输入高电平有效,输出低电平有效。

3.实验电路及步骤

3.1电路

(1)8—3线优先编码器具体电路如图2-1所示,说明如下:

利用9个单刀双掷开关(J0—J8)切换8位信号输入端和选通输入端(~E1)输入的高低电平状态。利用5个探测器(X1—X5)观察3位信号输出端、选通输出端、优先标志段输出信号的高低电平状态(探测器亮表示输出高电平“1”,灭表示输出低电平“0”)。

(2)3—8线译码器具体电路如图2-2所示,说明如下:

利用3个单刀双掷开关(J1—J3)切换二路输入端输入的高低电平状态。利用8个探测器(X0—X7)观察8路输出端输以信号的高低电平状态(探测器亮表示输出高电平“1”,灭表示输出低电平“0”)。使能端G1接高电平,G2A接低电平,G2B接低电平。

3.2 步骤

(1)8—3线优先编码器实验步骤:

a. 按图2-1所示连接电路。

b. 切换9个单刀双掷开关(J0—J8)进行仿真实验,将结果填入表2.1中。输入端中的“1”表示接高电平,“0”表示接低电平,“×”表示接高、低电平都可以。输出端中的“1”表示探测器亮,“0”表示探测器灭。该编码器输入、输出均为低电平有效。

A1

A0

E0

A2

GS

(2)3-8a. 按图2-2所示连接电路。

b. 切换3个单刀双掷开关(J1—J3)进行仿真实验,得到表2.2所示结果。输入端中的“1”表示接高电平,“0”表示接低电平。输出端中的“1”表示探测器亮,“0”表示探测器灭。该译码器输入高电平有效,输出低电平有效。

4.实验心得

本次实验主要掌握编码器、译码器的工作原理,并掌握了如何利用基础编码器设计位数更高的编码器。知道了各个管脚的功能与连接方式,进一步学习了multisim软件的使用。

实验三 触发器电路仿真实验

1. 实验目的

(1) 掌握边沿触发器的逻辑功能。

(2) 逻辑不同边沿触发器逻辑功能之间的相互切换。 2. 实验原理

触发器是构成时序电路的基本逻辑单元,具有记忆、存储二进制信息的功能。从逻辑功能上将触发器分为RS 、D 、JK 、T 、T ’等几种类型,对于逻辑功能的描述有真值表、波形图、特征方程等几种方法。功能不同的触发器之间可以相互转换。边沿触发器是指只在CP 上升沿或下降沿到来时接受此刻的输入信号,进行状态转换,而其他时刻输入信号状态的变化对其没有影响的电路。

集成触发器通常具有异步置位、复位功能。74LS74D 是在一片芯片上包含两个完全独立边沿D 触发器的集成电路。对它的分析可分为以下三种情况:

(1) 无论CP 、D 为何值,只要1~CLR=0,~1PR=1,触发器置0;只要~1CLR=1,~1PR=0,

触发器置1。(“~”表示非) (2) 当~1CLR=~1PR=0时为不允许状态、

(3) 当~1CLR=~1PR=1且CP 处于上升沿时,10n Q D +=

74LS112D 是在一芯片上饱和两个完全独立边沿JK 触发器的集成电路。对他的分析可分为以下三种情况。

(1) 无论CP 、J 、K 为何值,只要~1CLR=0,~1PR=1,触发器置0;只要~1CLR=1,~1PR=0,触发器置1。(“~”表示非) (2) 当~1CLR=~1PR=0时为不允许状态。

(3) 当~1CLR=~1PR=1且CP 处于下降沿时,1n n n Q JQ KQ +=+。

U1A

74LS74D

1D

2

1Q

5

~1Q

6

~1CLR

1

1CLK

3

~1PR

4异步置位端

信号输入端时钟信号

异步清零端

两个互补信号输出端

图4-1 74LS74D 逻辑符号和引脚注解

U2A

74LS112D

1Q

5

~1Q

6

~1PR

41K

2

~1CLR

15

1J 3

1CLK 1异步置位端

信号输入端时钟信号

K 信号输入端异步清零端

两个互补信号输入端

图4-2 74LS112D 逻辑符号和引脚注解

3. 实验电路及步骤 3.1电路

(1) D 触发器仿真电路如图4-3所示,说明如下:

利用单刀双掷开关J1、J2、J3、J4切换输入管脚的信号电平状态,利用探测器X1观察输出管脚的信号电平状态。用示波器查看输出管脚的信号波形。

表4.1 边沿D触发器74LS74D真值表

图4-3 D触发仿真电路

3.2步骤

D触发器仿真电路实验步骤。

a.按图4-3所示连接电路。

b.进行仿真电路实验,利用开关来改变~1PR、1D、~1CP、CP的状态,观察输出

端1Q的变化,将结果填入表4.1并验证结果。输入端的“1”表示接高电平,“0”表示接低电平,“x”表示接高、低电平都可以。输出端的“1”表示探测器亮,“0”表示探测器灭。

实验四计数器电路仿真实验

1.实验目的

(1)了解计数器的日常应用和分类。

(2)熟悉集成计数器逻辑功能和其各控制端作用。

(3)掌握计数器使用方法。

2.实验原理

统计输入脉冲个数的过程叫计数。能够完成计数工作的电路称作计数器。计数器的基本功能是统计叫钟脉冲的个数,即实现计数操作,也可用于分频、定时、产生节拍脉冲等。计数器的种类很多,根据计数脉冲引入方式的不同,将计数器分为同步计数器和异步计数器;根据计数过程中计数变化趋势,将计数器分为加法计数器、减法计数器、可逆计数器;根据计数器中计数长度的不同,可以将计数器分为二进制计数器和非二进制计数器(例如十进制、N进制)。

二进制计数器是构成其他各种计数器的基础。按照计数器中计数值的编码方法,用n表示二进制代表,N表示状态位,满足2n

N 的计数器称作二进制计数器。74LS161D是常见的二进制加法同步计数器,其功能如表5.1所示。

表5.1 74LS161D功能表(~表示“非”)

3.1电路

74LS161D构成的二进制加法同步计数器。具体电路如图5-1所示,说明如下:

a.该电路采用总线方式进行连接。

b.利用J2、J2、J3、J4四个单刀双掷开关可以切换74LS161D第7、10、9、1脚输入的高低电平状态。74LS161D第3、4、5、6(4位二进制输入端)同时接高电平。74LS161D第15脚(进位输出端)接探测器X1。V1为时钟信号。利用逻辑分析仪观察四位二进制输出端(第11、12、13、14脚)、进位输出端(第15脚)和时钟信号端(第2脚)的波形。利用数码管U2显示计数器的计数情况。

图5-1 74LS161D构成的二进制加法同步计数器

3.2步骤

74LS161D构成的二进制加法同步计数器仿真实验步骤。

a.按图5-1所示连接电路。

b.利用J1、J2、J3、J4四个单刀双掷开关切换74LS161D第1、7、9、10脚输入的高低电平状态,同时观察数码管U2的输出信号,验证表5.1给定的74LS161D 功能是否与实验结果相吻合。

c.观测探测器X1发现当该计数器计满(计到数码管U2显示“F”时),探测器X1亮,表明进位输出端有进位输出且高电平有效。

d.逻辑分析仪观察的结果如图5-2所示,验证其结果是否与表 5.1给定的74LS161D功能相吻合。改变时钟信号V1的幅度和频率,观察数码管和逻辑分析仪显示结果有何变化。

图5-2 逻辑分析仪观察结果

5.实验心得

通过本次实验了解计数器的日常应用和分类,熟悉集成计数器逻辑功能和其各控制端作用,掌握计数器使用方法。