组合逻辑电路的设计及半加器、全加器

实验四组合逻辑电路的设计及半加器、全加器

一、实验目的

1.掌握组合逻辑电路的设计与测试方法

2.掌握半加器、全加器的工作原理。

二、实验原理和电路

1、组合逻辑电路的设计

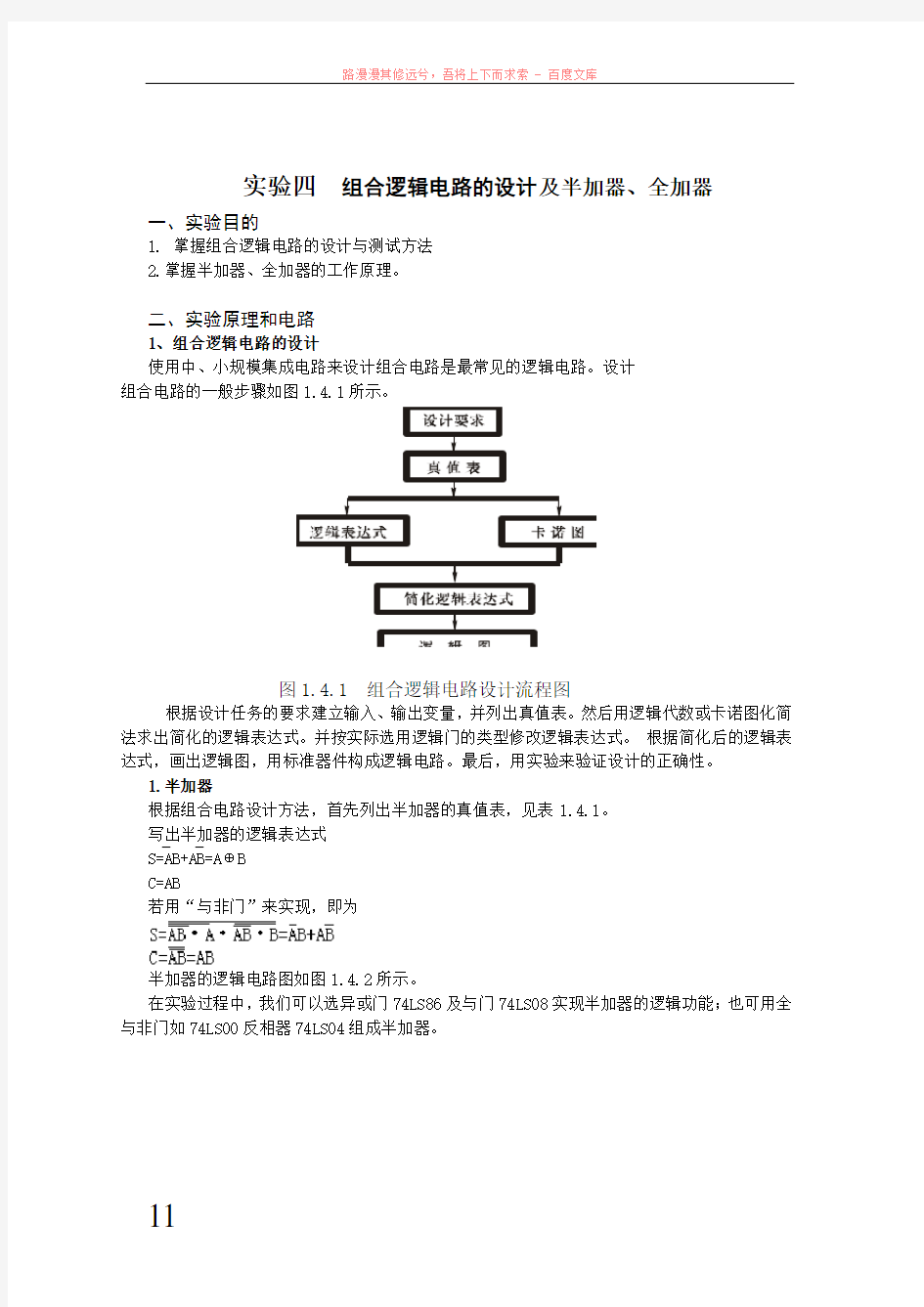

使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计

组合电路的一般步骤如图1.4.1所示。

图1.4.1 组合逻辑电路设计流程图

根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。根据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。最后,用实验来验证设计的正确性。

1.半加器

根据组合电路设计方法,首先列出半加器的真值表,见表1.4.1。

写出半加器的逻辑表达式

S=AB+AB=A⊕B

C=AB

若用“与非门”来实现,即为

半加器的逻辑电路图如图1.4.2所示。

在实验过程中,我们可以选异或门74LS86及与门74LS08实现半加器的逻辑功能;也可用全与非门如74LS00反相器74LS04组成半加器。

(a)用异或门组成的半加器(b)用与非门组成的半加器

图1.4.2 半加器逻辑电路图

2.全加器

用上述两个半加器可组成全加器,原理如图1.4.3所示。

图1.4.3由二个半加器组成的全加器表1.4.2 全加器逻辑功能表

表1.4.1 半加器逻辑功能

三、实验内容及步骤

1.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。

根据半加器的逻辑表达式可知,相加的和Y是A、B的异或,而进位Z是A、B相与,故半加器可用一个集成异或门和二个与非门组成如图1.4.4。

图1.4.4 用一个集成异或门和二个与非门组成半加器

⑴在实验仪上用异或门和与门接成以上电路。A、B接逻辑开关,Y、Z接发光二极管显示。

⑵按表1.4.3要求改变A、B状态,将相加的和Y和进位Z的状态填入下表中。

输入端 A 0 1 0 1

输入输出

C1-1 B A S i C i

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

00

10

1 0

0 1

10

0 1

0 1

1 1

输入和进位

A B S C

0 0

0 1

1 0

1 1

1

1

1

B 0 0 1 1

输出端Y Z

⑴写出图1.4.5电路的逻辑表达式。S

i = C

i

=

⑵根据逻辑表达式列真值表,并完成表1.4.4,实验证之。

⑶根据真值表画逻辑函数SiCi的卡诺图。完成图1.4.6

图 1.4.5

图 1.4.6

表1.4.4

Ai Bi Ci-1 Y Z X1 X2 X3 Si Ci

0 0 0

0 1 0

1 0 0

1 1 0

0 0 1

0 1 1

1 0 1

1 1 1

⑸试设计用异或门、与门、或门组成的全加器的逻辑功能并接线进行测试,将测试结果记入表1.4.5中,与上表进行比较看逻辑功能是否一致。

设计要求按组合逻辑电路设计流程图所述的设计步骤进行,直到测试电路逻辑功能符合设计要求为止。

Ai Bi Ci-1 Ci Si

0 0 0

0 1 0

1 0 0

1 1 0

0 0 1

0 1 1

1 0 1

1 1 1

四、实验器材

1.数字电子技术实验系统1台

2.直流稳压电源1台

3.集成电路:74L S00 3片74LS86,74LS32, 74LS08 各1片五、预习要求

1. 根据实验任务要求设计组合电路,并根据所给的标准器件画出逻辑图。

2. 复习半加器、全加器工作原理和特点。

3. 了解本实验中所用集成电路的逻辑功能和使用方法。

六、实验报告要求

1.列写实验任务的设计过程,画出设计的逻辑电路图。

2.对所设计的电路进行实验测试,记录测试结果。

3.组合电路设计体会。