基于FPGA的低密度奇偶校验码编码器设计

第45卷第9期2011年9月

浙 江 大 学 学 报(工学版)

Jo urnal of Zhejiang U niv ersity (Engineer ing Science)

Vol.45No.9Sep.2011

收稿日期:2010-05-05.

浙江大学学报(工学版)网址:w w w.jou https://www.360docs.net/doc/499144744.html, /eng

基金项目:国家质检总局科技计划资助项目(2009QK027);浙江省科技计划优先主题重点工业资助项目(2010C11024);杭州经济开发区

产学研合作资助项目(201002).

作者简介:张洋(1984-),男,硕士生,主要从事信道编译码技术与超大规模集成电路设计的研究.E -m ail:yangz hang999@gm https://www.360docs.net/doc/499144744.html,

通信联系人:王秀敏,女,教授.E -mail:w xm6341@https://www.360docs.net/doc/499144744.html,

DO I:10.3785/j.issn.1008-973X.2011.09.012

基于FPGA 的低密度奇偶校验码编码器设计

张 洋,王秀敏,陈豪威

(中国计量学院信息工程学院,浙江杭州310018)

摘 要:为提高准循环低密度奇偶校验码(LD PC)编码过程中矩阵与向量乘法运算的运算速度,提高编码器的吞吐率,提出采用对数循环移位器实现这一运算的方案.设计了WIM AX 标准中码率为1/2,码长为2304的L DPC 码的编码器.利用该码的校验基矩阵经过重组后可得到一个相邻的奇数行与偶数行非负元素所在的列号互不相同的矩阵的特点,在编码器的设计中充分利用了资源共享,采用6个对数循环移位器完成该码编码过程中的12组矩阵与向量乘法的并行运算.时序仿真和实际硬件测试的结果表明:与其他方法相比,该方案有效地降低了系统资源消耗,提高了吞吐率.

关键词:低密度奇偶校验码;编码器;现场可编程逻辑门阵列;对数循环移位寄存器;资源共享中图分类号:T N 47 文献标志码:A 文章编号:1008-973X(2011)09-1582-05

FPGA based design of LDPC encoder

ZH ANG Yang,WA NG Xiu -min,CH EN Hao -w ei

(College of I nf ormation Engineer ing ,China J iliang Univers ity ,H angz hou 310018,China )

Abstract:A logarithm ic cyclic shifter based schem e w as proposed to im pr ove the operation speed o f m atrix -vecto r m ultiplication in the quas-i cyclic low density parity -check co de (QC LDPC)encoding process and then im pro ve the throughput of the encoder.An enco der w as designed for an LDPC co de defined in the WIM AX standar d w ith a code rate of 1/2and a code length of 2304.The advantage of resource sharing w as fully taken accor ding to the char acteristics o f the base par ity -check m atrix w hich could be co nverted to a m atrix w ith no tw o no nnegativ e elements in the same column in any tw o adjacent row s by row per muta -tion.Six log ar ithmic cyclic shifters w ere used fo r the par allel calculation of tw elve matrix -vector multipl-i cations in the encoding process.T iming simulation and hardw are test results show that the proposed so lu -tion reduces the resource consumed and improv es the thro ug hput effectiv ely compared to other methods.Key words:LDPC;encoder;field -pro gramm able gate array (FPGA);lo garithm ic cyclic shifter;resource sharing

低密度奇偶校验码(lo w density parity -check code,LDPC),即在高斯白噪声信道条件下,采用BP (belief -propagatio n)译码算法时,该码与Turbo 码一样具有接近香农容限的误码率性能[1]

.目前LD -PC 码已广泛地应用于二次高斯Wyner -Ziv 编码[2]、

GM D -TH P M IMO 系统

[3]

、全息数据存储系统

[4]

以

及正交频分复用(OFDM )系统[5],并被DVB -S2,WIM AX 等通信标准所采用[6-7].

矩阵与向量的乘法运算是LDPC 码编码过程中的一种主要运算.赵明等

[8]

设计了一种类CPU

结构的编码器,通过设计专用的指令集实现这一运算.Kopparthy等[9]利用循环移位寄存器实现这一运算.对于子矩阵大小为z的LDPC码,完成一次信息比特向量的移位运算需要z/2个周期.Lee 等[10]将校验矩阵每行中的1所在的列号预先存储在一块ROM中,根据从该ROM中读出的值选择信息向量的比特位进行模2加运算,需要z个周期才能完成一次乘法运算.针对该不足,笔者提出了采用对数循环移位寄存器实现准循环LDPC码编码过程中的矩阵与向量的乘法运算,能在lo g2N个时钟周期内将最多N个比特一组的序列循环移位0到N-1之间的任意值,其中N为2的幂次.在此基础上设计了WIM AX标准中规定的码率为1/2,码长为2304的LDPC码的编码器.根据该码校验矩阵的特点,充分利用了资源共享,有效地降低了系统资源消耗,提高了其吞吐率.

1LDPC码的编码算法[1]

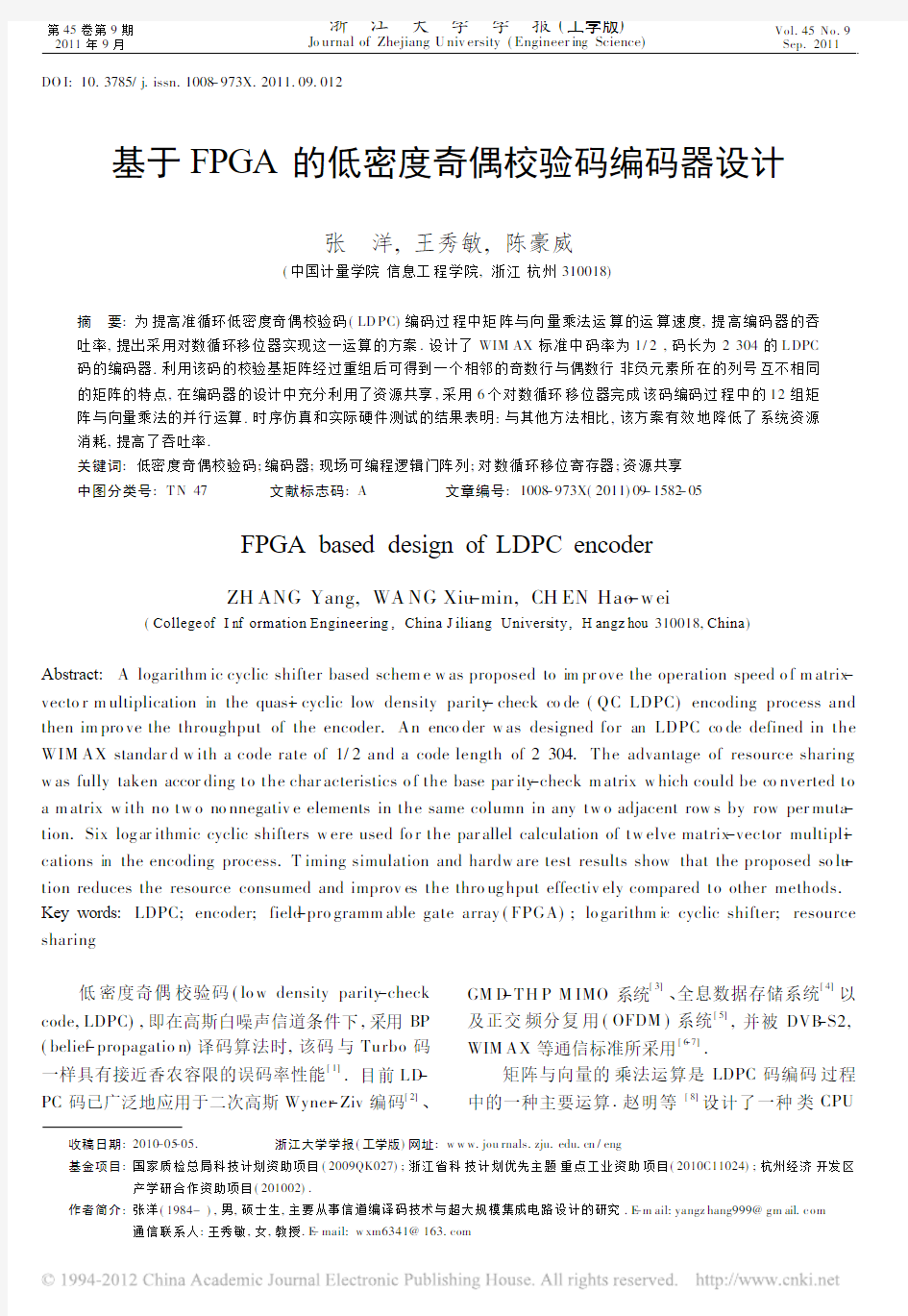

LDPC码的编码通常采用基于近似下三角的编码方法.该方法首先对校验矩阵的行和列重排,得到一个近似下三角的矩阵H,再将该矩阵分解为A、B、T、C、D、E等6个子矩阵,即

H=A B T C D E

.

如图1所示[1].其中T为一下三角矩阵,g

为与该

算法编码复杂度有关的一个常量,其值越小,则编码

图1校验矩阵的分块

Fig.1Blo cking of parit y check matr ix

复杂度与码长越接近线性关系.根据该分块方法,将整个码字cw T分解为(s T,p0T,p T1)三部分,其中:s T 为信息比特序列,其长度为N-M;p T0、p T1分别为校验比特序列的第1和第2部分,其长度分别为g和M-g.根据校验矩阵H与码字比特序列cw T的关系Hcw=0得

As+Bp0+Tp1=0,(1)

Cs+Dp0+Ep1=0.(2)在二进制下求解该方程组有

p0=(D+ET-1B)-1(C+ET-1A)s,(3)

p1=T-1(As+Bp0).(4)将s、p0、p1合并即得到编码后的码字序列.

2编码器的实现

WIM AX标准中定义的码率为1/2,扩展因子为96的LDPC码的校验基矩阵如下[11]:

H b=-19473-1-1-1-1-15583-1-170-1-1-1-1-1-1-1-1-1-

1

-127-1-1-122799-1-1-112-100-1-1-1-1-1-1-1-1-1

-1-1-1242281-133-1-1-10-1-100-1-1-1-1-1-1-1-1

61-147-1-1-1-1-16525-1-1-1-1-100-1-1-1-1-1-1-1

-1-139-1-1-184-1-14172-1-1-1-1-100-1-1-1-1-1-1

-1-1-1-14640-182-1-1-1790-1-1-1-100-1-1-1-1-1

-1-19553-1-1-1-1-11418-1-1-1-1-1-1-100-1-1-1-1

-11173-1-1-12-1-147-1-1-1-1-1-1-1-1-100-1-1-1

12-1-1-18324-143-1-1-151-1-1-1-1-1-1-1-100-1-1

-1-1-1-1-194-159-1-17072-1-1-1-1-1-1-1-1-100-1

-1-1765-1-1-1-13949-1-1-1-1-1-1-1-1-1-1-1-100

43-1-1-1-166-141-1-1-1267-1-1-1-1-1-1-1-1-1-10

(5)

将该矩阵中的每个-1扩展为一个96阶的零矩阵,每个0扩展为一个96阶的单位矩阵,每个大于0的数x扩展为一个96阶的单位阵循环右移x 后所得到的置换矩阵,即得到本文所实现的码长为2304,码率为1/2的LDPC码的校验矩阵.

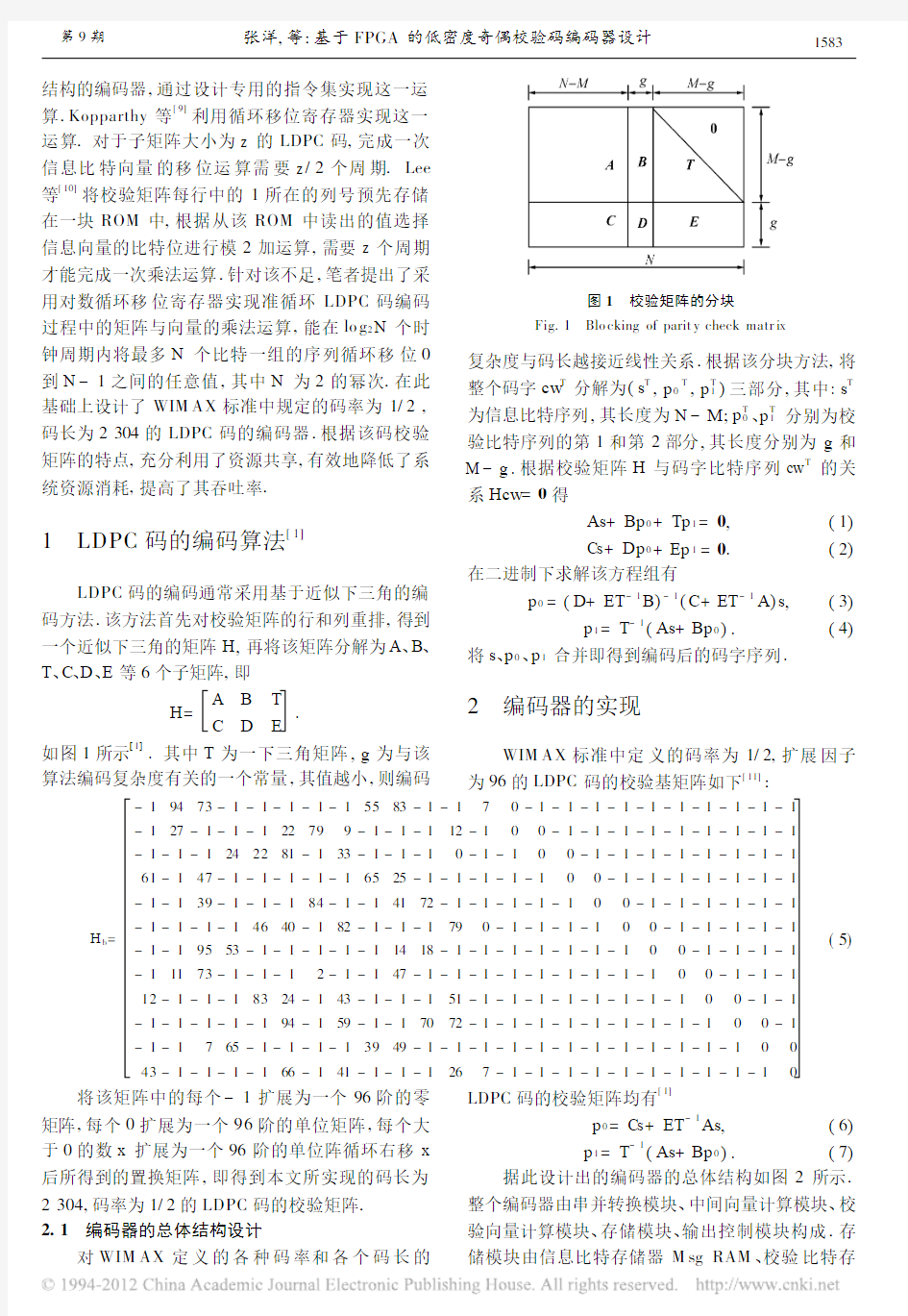

2.1编码器的总体结构设计

对WIM AX定义的各种码率和各个码长的LDPC码的校验矩阵均有[1]

p0=Cs+ET-1As,(6)

p1=T-1(As+Bp0).(7)据此设计出的编码器的总体结构如图2所示.整个编码器由串并转换模块、中间向量计算模块、校验向量计算模块、存储模块、输出控制模块构成.存储模块由信息比特存储器M sg RAM、校验比特存

1583

第9期张洋,等:基于FPGA的低密度奇偶校验码编码器设计

储器Chk RAM ,及中间结果As 存储器As RAM 构成.所有存储器数据位宽均为96比特.串并转换模块将并行输入的4比特数据转转成并行输出的96比特数据,该数据一路传给后续模块进行处理,一路传给信息比特存储器存储.中间向量计算模块完成

As 和Cs 的计算,校验向量计算模块完成p T 0和p T

1的计算,并将运算结果存入相应的存储器.输出控制模块控制码字比特的连续输出

.

图2 编码器总体结构框图

F ig.2 O ver all structur e diagr am of the encoder

212 中间向量计算模块

中间向量计算模块接收串并转换模块输出的96比特信息比特,将其分别与校验矩阵中的A 和C 相乘得到As 和Cs .该模块涉及到大量的矩阵与向量的乘法运算以及向量的累加运算,是整个编码器中耗用资源最多的部分.本文根据所实现的LDPC 码的校验矩阵的特点,对该部分进行了一系列优化设计,有效地降低了整个编码器耗用的资源,提高了其吞吐率.

2.211 采用对数移位寄存器实现矩阵与向量的乘法运算 对数循环移位寄存器[12]能在lo g 2N 个时钟周期内,将最多N 个比特一组的序列循环移位1到N -1之间的任意值,其中N 为2的某一整数次幂.其工作原理为:在log 2N 个连续的时钟周期内依次判断循环移位值sftcnt 的各个比特位上的值是否为1,若是,则将i -1个周期后循环移位的结果再循环移位2i

位,否则保持不变,其中i 为大于0小于lo g 2N 的整数.由于本文实现的LDPC 码的扩展因子为96,为此本文设计的是一个输入数据序列为96比特,循环移位数位宽为7比特的对数循环移位寄存器.

2.212 结合校验矩阵的特点,充分利用资源共享,降低硬件资源消耗 通过观察WIM AX 标准中码率为1/2的校验基矩阵(式(5))发现:该矩阵的第1行和第3行、第2行和第11行、第4行和第6行、第5行和第12行、第7行和第9行、第8行和第10行同一列上的值不同时为非负数.根据这一特点,本文在设计As 和Cs 计算模块时,充分利用了资源共享的优势,在不降低系统吞吐率的条件下,有效降低了

硬件资源消耗.采用6个循环移位寄存器实现As 和Cs 的12组96比特序列并行计算所需的对信息比

特序列的循环移位运算.2.3 校验向量计算模块

该模块由p T 0计算模块和p T

1计算模块构成.根

据校验基矩阵H b ,校验比特序列p T 0就是As 的11组96比特序列与Cs 的模2累加和.因此,p T 0计算模块主要由96个异或门构成,在12连续的周期内完成p T

0的计算.p T

1的计算由两级流水线完成,第一级流水线计算As +Bp 0的值V ,第二级流水线根据

V 计算p T 1.根据校验基矩阵H b ,p T

1的第i 个96比

特序列就是V T 的前i 个96比特序列的模2累加和,i =1,2,,,11;计算Bp 0所需的循环移位操作由

一个移位数固定为7的对数循环移位器完成.2.4 码字存储及输出模块

为实现编码过程的流水线处理,本设计将信息比特和校验比特分别存储在2个字数为12,数据位宽为96比特的双口RAM 中,每12个周期读一次信息比特存储器.当其存储的信息比特数据全部读出之后,开始以同样的方式读校验比特存储器,读完之后接着再读信息比特存储器.如此循环,从信息比特存储器和校验比特存储器读出的96比特数据通过串并转换模块在12个连续的时钟周期内输出,形成连续的8比特位宽码字流.

3 编码器仿真、测试及分析

3.1 时序仿真

为测试所设计的编码器的工作性能,首先建立该编码器的测试平台.整个测试平台由信源产生模块、编码模块、码字模块、比较模块等4个模块构成,如图3所示

.

图3 编码器测试平台结构图

Fig.3 Str ucture diag ram of encoder testing platfor m

信源产生模块在576个连续的时钟周期内输出576个4比特位宽的数据(2帧信息比特数据);编码模块对这2帧数据进行编码,并在576个连续的时钟周期内输出全部576个8比特位宽的码字序列;比较模块将该码字序列逐个与码字模块输出的预先存储在码字ROM 中的正确码字进行对比,只要有一个码字不同,则比较结果输出低电平,否则输出高

1584

浙 江 大 学 学 报(工学版) 第45卷

电平.选择EP2C70F896C6芯片作为目标器件,将整个测试系统用Quar tus2811自带的综合工具进行综合,之后进行时序仿真,所得局部放大波形如图4所示.图中dout0为编码模块的输出,do ut1为码字模块的输出.从波形图可看到在码字模块输出正确码字的同时,比较结果信号comp _r esult 一直为

高电平,说明编码器输出的码字正确.由于仅输入了2帧信息比特,编码器输出完第1帧数据的码字后,开始循环输出存储在信息比特存储器和校验比特存储器中的第2帧数据的信息位和校验位,而码字ROM 输出完576个码字后,不再输出,因此,比较完毕后dout1变为

0.

图4 时序仿真局部放大波形2

F ig.4 P artial enlar ged wav eform 2of t iming simulation

3.2 硬件测试

硬件测试在DE2-70开发板上进行.该开发板上的FPGA 芯片型号为EP2C70F896C6,将测试模块的dotu0,dout1输出分别映射到开发板上的16个红色的LED,将com p_r esult 映射到开发板上的一个绿色的LED,将编译后生成的.sof 文件下载到开发板上的FPGA 芯片中.结果LED 绿灯点亮,与dotu0对应的8个红色的LED 一直点亮,硬件测试结果正确.

3.3 编码器的性能分析

采用EP2C70F896C6芯片作为目标器件,综合结果显示:本文设计的LDPC 码编码器共消耗7641个逻辑单元,3157个寄存器和3936bits 的RAM.编码器最高工作频率可达188MH z,因此,其最高编码吞吐率可达188@4=752M bps .而文献[9]中介绍的编码器全部采用逻辑单元设计,共消耗了12727个逻辑单元,编码吞吐率仅可达到422Mbps,因此,本文提出的方案用较少的硬件资源消耗就换得了编码吞吐率极大的提高.

本文所提出的利用对数循环移位器实现置换矩阵与向量的乘法运算,适用于所有准循环LDPC 码编码器的设计.利用资源共享降低硬件资源消耗的方案适用于所有具有如下特点的LDPC 码编码器的设计:该码的校验基矩阵经过重组后可得到一个相邻的奇数行与偶数行非负元素所在的列号互不相同的矩阵.

4 结 语

针对准循环LDPC 码编码过程中存在的大量的置换矩阵与向量的乘法运算,本文提出了一种专用的实现结构对数循环移位寄存器.基于该结构,设计实现了WIM AX 标准中码率为1/2、码长为2304的LDPC 码的编码器.利用该码校验基矩阵的特点,在编码器的中间向量As 和Cs 计算模块的设计中充分利用了资源共享.与其他设计相比,本文所提方案有效降低了编码器的资源消耗,提高了吞吐率.该方案还可应用于其他基校验矩阵具有类似特点的准循环LDPC 码的编码器设计.

参考文献(References):

[1]袁东风,张海刚.L DPC 码理论与应用[M ].北京:人民

邮电出版社,2008:9-11,38.

[2]Y AN G Y ,CH EN G S,XI ON G Z,et a l.Wy ner -Ziv cod -ing based on T CQ and L DPCs[J].IEEE Transactions on C ommunications ,2009,57(2):376-387.

[3]P ET H E C Y ,L IA N G Y C.P ow er and modulo lo ss

tr adeo ff w ith ex panded so ft demapper for L DPC coded G M D -T H P M I M O systems [J ].IEEE Transactions on Wireless C ommunications ,2009,8(2):714-724.[4]K IM J,L EE J.T w o -dimensional SO V A and L DPC

co des fo r holo gr aphic dat a sto rage system [J].IEEE Transactions on Magnetics ,2009,45(5):2260-2263.

1585

第9期

张洋,等:基于FPGA 的低密度奇偶校验码编码器设计

[5]L I X H,CAO Y Q,LI Z S,et al.Perfo rmance of de-

g ree distributio n based HA RQ scheme for L DP C-co ded

O FD M system[J].The Journal of C hina Universities of Posts and Telecommunications,2009,16(1):47-50. [6]郗丽萍,赵小祥,王匡.基于循环矩阵的低密度校验码的

V L SI译码设计[J].浙江大学学报:工学版,2009,43

(2):261-265.

X I L-i ping,Z HA O Xiao-x iang,W A NG K uang.V L SI decoding design of lo w-density par ity-check codes based o n circulant mat rices[J].Journal of Zhejiang University: Engineering Science,2009,43(2):261-265.

[7]郗丽萍,赵小祥,王匡.改进的低密度校验码的定点译码

实现[J].浙江大学学报:工学版,2008,42(3):471-476, 516.

X I L-i ping,ZHA O Xiao-xiang,W A NG K uang.Im-pro ved decoding appro ach of low-density par ity-check co des with finite precisio n[J].Journal of Zhejiang Un-i versity:Engineering Science,2008,42(3):471-476,516. [8]赵明,李亮.在线可编程QC-L DPC码高速编码器结构

[J].清华大学学报:自然科学版,2009,49(7):1025-1028.

ZH A O M ing,L I L iang.P rog rammable quas-i cy clic LD-PC enco der a rchitectur e[J].Journal of Tsinghua Univer-sity:Sci&Tech,2009,49(7):1025-1028.

[9]KO PP A RT H Y S,GRU EN BA CH ER D M.Implemen-

tat ion of a flex ible encoder for st ruct ur ed lo w-density par ity-check codes[C]M IEEE Pacific Rim C onference on

C ommunications,Computers and Signal Processing2007.

PacRim:IEEE,2007:438-441.

[10]LEE D U,LU K W,W AN G C,et al.A flexible hardw ar e

encoder for low-density parity-check co des[C]M12th An-nual IEEE Symposium o n F ield-Prog ra mm able C ustom C om-puting M achines.N apa:IEEE,2004:13-19.

[11]ZH ANG K ai,HU AN G Xin-ming,W A NG Zhong-feng.

H igh-throug hput layered decoder implementation fo r qua-

s-i cyclic LDPC codes[J].IEEE J ournal on Selected Areas in C omm unications,2009,27(6):985-994.

[12]G U N NA M K K,CH OI G S,Y EAR Y M B,et al.V L-

SI architectur es fo r lay ered deco ding fo r ir regular LD-PCs of W iM ax[C]M IEEE International C onference on Communications2007.G lasgo w:I EEE,2007:4542-4547.

下期论文摘要预登

喷墨印花纹理图像的单元分解光流场配准算法

冯志林1,尹建伟2

(1.浙江工业大学之江学院信息工程学系,浙江杭州310024;

2.浙江大学计算机科学与技术学院,浙江杭州310027)

摘要:为了解决喷墨印花纹理图像在噪声环境下配准精确度低、局部区域存在大的配准偏差问题,提出一种新的基于单元分解光流场的图像配准算法.利用单元分解技术对光流场图像配准问题进行建模,采用阶谱分层策略和基函数自适应调整,对单元分解过程中生成的局部和全局网格实施灵活度控制.通过引入一个新的能够对纹理结构的光滑效果实施约束的特征能量项,使网格单元取得令人满意的纹理表征效果,并且能够提高光流场模型在定位精细纹理边缘时的配准精度.对含噪喷墨印花纹理图像的配准实验结果表明了该算法的可行性.

关键词:喷墨印花纹理;光流场;单元分解;图像配准

1586浙江大学学报(工学版)第45卷

编码器四倍频细分电路(含波形图)

四倍频细分电路(含波形图) 时间:2010-06-12 05:00:19 来源:作者: 1.光电编码器原理 光电编码器,是一种通过光电转换将输出轴上的机械几何位移量转换成脉冲或数字量的传感器。这是目前应用最多的传感器,光电编码器是由光栅盘和光电检测装置组成。光栅盘是在一定直径的圆板上等分地开通若干个长方形孔。由于光电码盘与电动机同轴,电动机旋转时,光栅盘与电动机同速旋转,经发光二极管等电子元件组成的检测装置检测输出若干脉冲信号,其原理示意图如图1所示;通过计算每秒光电编码器输出脉冲的个数就能反映当前电动机的转速。此外,为判断旋转方向,码盘还可提供相位相差90旱牧铰仿龀逍藕拧 根据检测原理,编码器可分为光学式、磁式、感应式和电容式。根据其刻度方法及信号输出形式,可分为增量式、绝对式以及混合式三种。 1.1增量式编码器 增量式编码器是直接利用光电转换原理输出三组方波脉冲A、B和Z相;A、B两组脉冲相位差90海佣煞奖愕嘏卸铣鲂较颍鳽相为每转一个脉冲,用于基准点定位。它的优点是原理构造简单,机械平均寿命可在几万小时以上,抗干扰能力强,可靠性高,适合于长距离传输。其缺点是无法输出轴转动的绝对位置信息。 1.2绝对式编码器 绝对编码器是直接输出数字量的传感器,在它的圆形码盘上沿径向有若干同心码道,每条道上由透光和不透光的扇形区相间组成,相邻码道的扇区数目是双倍关系,码盘上的码道数就是它的二进制数码的位数,在码盘的一侧是光源,另一侧对应每一码道有一光敏元件;当码盘处于不同位置时,各光敏元件根据受光照与否转换出相应的电平信号,形成二进制数。这种编码器的特点是不要计数器,在转轴的任意位置都可读出一个固定的与位置相对应的数字码。显然,码道越多,分辨率就越高,对于一个具有N位二进制分辨率的编码器,其码盘必须有N条码道。目前国内已有16位的绝对编码器产品。 绝对式编码器是利用自然二进制或循环二进制(葛莱码)方式进行光电转换的。绝对式编码器与增量式编码器不同之处在于圆盘上透光、不透光的线条图形,绝对编码器可有若干编码,根据读出码盘上的编码,检测绝对位置。编码的设计可采用二进制码、循环码、二进制补码等。它的特点是: 1.2.1可以直接读出角度坐标的绝对值; 1.2.2没有累积误差; 1.2.3电源切除后位置信息不会丢失。但是分辨率是由二进制的位数来决定的,也就是说精度取决于位数,目前有10位、14位等多种。 1.3混合式绝对值编码器

奇偶校验

为了系统的可靠性,对于位数较少,电路较简单的应用,可以采用奇偶校验的方法。奇校验是通过增加一位校验位的逻辑取值,在源端将原数据代码中为1的位数形成奇数,然后在宿端使用该代码时,连同校验位一起检查为1的位数是否是奇数,做出进一步操作的决定。奇偶校验只能检查一位错误,且没有纠错的能力。偶校验道理与奇校验相同,只是将校验位连同原数据代码中为1的位数形成偶数。奇偶校验器多设计成九位二进制数,以适应一个字节,一个ASCII代码的应用要求。奇偶校验是一种荣誉编码校验,在存储器中是按存储单元为单位进行的,是依靠硬件实现的,因而适时性强,但这种校验方法只能发现奇数个错,如果数据发生偶数位个错,由于不影响码子的奇偶性质,因而不能发现。 奇偶校验是一种校验代码传输正确性的方法。根据被传输的一组二进制代码的数位中“1”的个数是奇数或偶数来进行校验。采用奇数的称为奇校验,反之,称为偶校验。采用何种校验是事先规定好的。通常专门设置一个奇偶校验位,用它使这组代码中“1”的个数为奇数或偶数。若用奇校验,则当接收端收到这组代码时,校验“1”的个数是否为奇数,从而确定传输代码的正确性。 与一段信息关联的冗余信息。在WindowsNTServer中,带奇偶校验的带区集意味着每行有一个附加的奇偶校验带区。因此,必须使用至少三个(而不是两个)磁盘才能考虑该附加的奇偶校验信息。奇偶校验带区包含该带区内数据的XOR(称为排它性“或”的布尔操作)。重新生成失败的磁盘时,WindowsNTServer将使用这些带区中与完好磁盘上数据关联的奇偶校验信 息重新在失败盘上创建数据。请参阅容错;带区集;带奇偶校验的带区集奇偶校验能够检测出信息传输过程中的部分误码(1位误码能检出,2位及2位以上误码不能检出),同时,它不能纠错。在发现错误后,只能要求重发。但由于其实现简单,仍得到了广泛使用。 为了能检测和纠正内存软错误,首先出现的是内存“奇偶校验”。内存中最小的单位是比特,也称为“位”,位只有两种状态分别以1和0来标示,每8个连续的比特叫做一个字节(byte)。不带奇偶校验的内存每个字节只有8位,如果其某一位存储了错误的值,就会导致其存储的相应数据发生变化,进而导致应用程序发生错误。而奇偶校验就是在每一字节(8位)之外又增加了一位作为错误检测位。在某字节中存储数据之后,在其8个位上存储的数据是固定的,因为位只能有两种状态1或0,假设存储的数据用位标示为1、1、1、0、0、1、0、1,那么把每个位相加(1+1+1+0+0+1+0+1=5),结果是奇数。对于偶校验,校验位就定义为1,反之则为0;对于奇校验,则相反。当CPU读取存储的数据时,它会再次把前8位中存储的数据相加,计算结果是否与校验位相一致。从而一定程度上能检测出内存错误,奇偶校验只能检测出错误而无法对其进行修正,同时虽然双位同时发生错误的概率相当低,但奇偶校验却无法检测出双位错误。

光电编码器原理及应用实例介绍

光电编码器原理及应用实例介绍 1.光电编码器原理 根据检测原理,编码器可分为光学式、磁式、感应式和电容式。根据其刻度方法及信号输出形式,可分为增量式、绝对式以及混合式三种。1.1 增量式编码器增量式编码器是直接利用光电转换原理输出三组方波脉冲A、B 和Z 相; A、B 两组脉冲相位差90 海佣煞奖愕嘏卸铣鲂较颍Z 相为每转一个脉冲,用于基准点定位。它的优点是原理构造简单,机械平均寿命可在几万小时以上,抗干扰能力强,可靠性高,适合于长距离传输。其缺点是无法输出轴转动的绝对位置信息。1.2 绝对式编码器绝对编码器是直接输出数字量的传感器,在它的圆形码盘上沿径向有若干同心码道,每条道上由透光和不透光的扇形区相间组成,相邻码道的扇区数目是双倍关系,码盘上的码道数就是它的二进制数码的位数,在码盘的一侧是光源,另一侧对应每一码道有一光敏元件;当码盘处于不同位置时,各光敏元件根据受光照与否转换出相应的电平信号,形成二进制数。这种编码器的特点是不要计数器,在转轴的任意位置都可读出一个固定的与位置相对应的数字码。显然,码道越多,分辨率就越高,对于一个具有N 位二进制分辨率的编码器,其码盘必须有N 条码道。目前国内已有16 位的绝对编码器产品。绝对式编码器是利用自然二进制或循环二进制(葛莱码)方式进行光电转换的。绝对式编码器与增量式编码器不同之处在于圆盘上透光、不透光的线条图形,绝对编码器可有若干编码,根据读出码盘上的编码,检测绝对位置。编码的设计可采用二进制码、循环码、二进制补码等。它的特点是:1.2.1 可以直接读出角度坐标的绝对值;1.2.2 没有累积误差;1.2.3 电源切除后位置信息不会丢失。但是分辨率是由二进制的位数来决定的,也就是说精度取决于位数,目前有10 位、14 位等多种。1.3 混合式绝对值编码器混合式绝对值

基于FPGA的低密度奇偶校验码编码器设计

第45卷第9期2011年9月 浙 江 大 学 学 报(工学版) Jo urnal of Zhejiang U niv ersity (Engineer ing Science) Vol.45No.9Sep.2011 收稿日期:2010-05-05. 浙江大学学报(工学版)网址:w w w.jou https://www.360docs.net/doc/499144744.html, /eng 基金项目:国家质检总局科技计划资助项目(2009QK027);浙江省科技计划优先主题重点工业资助项目(2010C11024);杭州经济开发区 产学研合作资助项目(201002). 作者简介:张洋(1984-),男,硕士生,主要从事信道编译码技术与超大规模集成电路设计的研究.E -m ail:yangz hang999@gm https://www.360docs.net/doc/499144744.html, 通信联系人:王秀敏,女,教授.E -mail:w xm6341@https://www.360docs.net/doc/499144744.html, DO I:10.3785/j.issn.1008-973X.2011.09.012 基于FPGA 的低密度奇偶校验码编码器设计 张 洋,王秀敏,陈豪威 (中国计量学院信息工程学院,浙江杭州310018) 摘 要:为提高准循环低密度奇偶校验码(LD PC)编码过程中矩阵与向量乘法运算的运算速度,提高编码器的吞吐率,提出采用对数循环移位器实现这一运算的方案.设计了WIM AX 标准中码率为1/2,码长为2304的L DPC 码的编码器.利用该码的校验基矩阵经过重组后可得到一个相邻的奇数行与偶数行非负元素所在的列号互不相同的矩阵的特点,在编码器的设计中充分利用了资源共享,采用6个对数循环移位器完成该码编码过程中的12组矩阵与向量乘法的并行运算.时序仿真和实际硬件测试的结果表明:与其他方法相比,该方案有效地降低了系统资源消耗,提高了吞吐率. 关键词:低密度奇偶校验码;编码器;现场可编程逻辑门阵列;对数循环移位寄存器;资源共享中图分类号:T N 47 文献标志码:A 文章编号:1008-973X(2011)09-1582-05 FPGA based design of LDPC encoder ZH ANG Yang,WA NG Xiu -min,CH EN Hao -w ei (College of I nf ormation Engineer ing ,China J iliang Univers ity ,H angz hou 310018,China ) Abstract:A logarithm ic cyclic shifter based schem e w as proposed to im pr ove the operation speed o f m atrix -vecto r m ultiplication in the quas-i cyclic low density parity -check co de (QC LDPC)encoding process and then im pro ve the throughput of the encoder.An enco der w as designed for an LDPC co de defined in the WIM AX standar d w ith a code rate of 1/2and a code length of 2304.The advantage of resource sharing w as fully taken accor ding to the char acteristics o f the base par ity -check m atrix w hich could be co nverted to a m atrix w ith no tw o no nnegativ e elements in the same column in any tw o adjacent row s by row per muta -tion.Six log ar ithmic cyclic shifters w ere used fo r the par allel calculation of tw elve matrix -vector multipl-i cations in the encoding process.T iming simulation and hardw are test results show that the proposed so lu -tion reduces the resource consumed and improv es the thro ug hput effectiv ely compared to other methods.Key words:LDPC;encoder;field -pro gramm able gate array (FPGA);lo garithm ic cyclic shifter;resource sharing 低密度奇偶校验码(lo w density parity -check code,LDPC),即在高斯白噪声信道条件下,采用BP (belief -propagatio n)译码算法时,该码与Turbo 码一样具有接近香农容限的误码率性能[1] .目前LD -PC 码已广泛地应用于二次高斯Wyner -Ziv 编码[2]、 GM D -TH P M IMO 系统 [3] 、全息数据存储系统 [4] 以 及正交频分复用(OFDM )系统[5],并被DVB -S2,WIM AX 等通信标准所采用[6-7]. 矩阵与向量的乘法运算是LDPC 码编码过程中的一种主要运算.赵明等 [8] 设计了一种类CPU

常用的检错码 - 奇偶校验码

3.2差错控制 3.2.2常用的检错码- 奇偶校验码 奇偶校验码是一种简单的检错码,奇偶校验码分为奇校验码和偶校验码,两者原理相同。它通过增加冗余位来使得码字中“1”的个数保持奇数或偶数。 ?无论是奇校验码还是偶校验码,其监督位只有一位; ?假设信息为为I1, I2, …, I n,对于偶校验码,校验位R可以表示为: R =I 1 ⊕I 2 ⊕Λ⊕I n ?假设信息为为I1, I2, …, I n,对于奇校验码,校验位R可以表示为: R =I 1 ⊕I 2 ⊕Λ⊕I n ⊕1 ?无论是奇校验码还是偶校验码,都只能检测出奇数个错码,而 不能检测偶数个错码。 4 4

讨论: 从检错能力、编码效率和代价等方面来评价垂直奇偶校验、水平奇偶校验和水平垂直奇偶校验 3.2 差错控制 3.2.2 常用的检错码 - 奇偶校验码 奇偶校验在实际使用时又可分为垂直奇偶校验、水平奇偶校验和水平垂直奇偶校验等几种。 5

3.2.2常用的检错码–定比码 所谓定比码,即每个码字中“1”的个数与“0”的个数之比保持恒定, 故又名等比码或恒比码。 ?当码字长一定,每个码字所含“1”的数目都相同,“0”的数目也 都相同。 ?由于若n位码字中“1”的个数恒定为m,还可称为“n中取m”码 定比码(n中取m)的编码效率为: log C m R = ?2 n n 定比码能检测出全部奇数位错以及部分偶数位错。实际上,除了码 字中“1”变成“0”和“0”变成“1”成对出现的差错外,所有其它差 错都能被检测出来 6 4

代码“1011011”对应的多项式为x 6 + x 4 + x 3 +1 多项式“x 5 + x 4 + x 2 + x”所对应的代码为“110110” 3.2.2 常用的检错码 – 循环冗余检验 循环冗余码(Cyclic Redundancy Code ,简称CRC )是无线通信中用得最广泛的检错码,又被称为多项式码。 二进制序列多项式:任何一个由m 个二进制位组成的代码序列都可以和一个只含有0和1两个系数的m-1阶多项式建立一一对应的关系。 CRC 有关的多项式: ? 信息位多项式、冗余位多项式、码字多项式、和生成多项式 信息位1010001:K (x ) = x 6 + x 4 + 1 冗余位1101:R (x ) = x 3 + x 2 + 1; 码字10100011101: T (x ) = x 10 + x 8 + x 4 + x 3 + x 2 + 1 7

旋转编码器电路 课程设计

XX大学 课程设计说明书 学生姓名:学号: 学院:信息与通信工程学院 专业:电子信息科学与技术 题目:旋转编码器电路 指导教师:职称: 年月日

XX大学 课程设计任务书 2008/2009 学年第一学期 学院: 专业: 学生姓名:学号: 课程设计题目:旋转编码器电路 起迄日期:12月29日~1月9日 课程设计地点: 指导教师: 系主任: 下达任务书日期: 年月日

课程设计任务书 1.设计目的: 通过本课程设计, 主要训练和培养学生综合应用所学过的电路、低频、数字、高频等课程的相关知识,设计实用的电子电路方面的实际电路,包括:查阅资料、合理性的设计、分析和解决实际问题的能力,电路设计工具PROTEL的学习与应用,应用计算机的能力,用简洁的文字,清晰的图表来表达自己设计思想的能力。 2.设计内容和要求(包括原始数据、技术参数、条件、设计要求等): (1)学习和练习电路设计PROTEL软件, (2)把旋转编码器输出的信号,经整形后送给计数器,使计数器开始计数。 (3)在旋转编码器时有两种方式,顺时针和逆时针,此时方式控制端的触发沿是不一样的。 3.设计工作任务及工作量的要求〔包括课程设计计算说明书(论文)、图纸、实物样品等〕: 画出电路图,并进行原理图的详细叙述, (1)尽量给出元器件的型号和数值, (2)尽量画出PCB图, (3)写出符合格式要求的设计报告。

课程设计任务书 4.主要参考文献: 5.设计成果形式及要求: 设计说明书及相关电路图 6.工作计划及进度: 2008年12 月29 日~ 12月31 日了解设计题目及熟悉资料; 2009年1月1日~ 1月2 日确定各题目要求计算相关参数; 2009年1月2日~ 1月3 日结合各题目确定具体设计方案; 2009年1月3日~ 1月8 日结合要求具体设计并仿真、整理报告; 2009年1月9日答辩。 系主任审查意见: 签字: 年月日

低复杂度准循环低密度奇偶校验码

低复杂度准循环低密度奇偶校验码 摘要 本文主要对低复杂度准循环低密度奇偶校验码结构的研究。结果表明,这种编码坦纳图代表与周长不能大于12,代码周长的充分条件有一个6,8,10或12的周长推导。这些结果表明这样周长群的LDPC码的相对容易获得,因此,额外的参数,如最小距离或多余的数量检查总结应予以考虑。为此,为必要条件规范调查,以达到其最大可能的最小汉明距离建议。 正文: 近年来, 已有多种LDPC 码构造方案被陆续提出, 按照构造方法的不同LDPC 码可以分为两大类, 随机和伪随机码. 对于第一类随机码和伪随机码.尽管分组长度足够长的随机码具有接近Shannon 限的性能, 但不具有线性的编码复杂度. 针对随机码编码复杂度高的问题, 学术界提出了另一类LDPC 码. 这类LDPC 码通常具有循环或者准循环的结构, 从而可以利用线性反馈移位寄存器实现线性编码, 其在串行编码时的复杂度正比于校验比特的个数, 而并行编码时正比于码长, 根据构造时所采用代数方法的不同, 这类LDPC 码可细分为 3 个子类. 第 1 类是基于有限几何的LDPC 码, 该算法将有限几何中的点和线映射为LDPC 码的变量节点和校验节点. 第 2 类是基于组合设计,特别是基于平衡不完全组合设计的LDPC 码这两类码均为循环或者准循环LDPC 码, 并且不含长度为 4 的环路, 但是其分组长度受限. 第 3 类是基于循环置换矩阵的准循环LDPC 码, 虽然这类码的分组长度的范围远远大于基于有限几何的LDPC 码, 但是如果随机选取每个循环置换矩阵, 将不能避免长度为 4 的环路的出现. 对于给定的期望最小环长g, 我们可以用列重为J, 行重为L 的准循环LDPC 码的随机构造法. 该算法从所有jl p个矩阵中搜索一个期望矩阵(p 代表每个循环置换矩阵的阶数). 准循环LDPC 码的随机构造法中,待搜索的矩阵个数是乘积JL 的指数函数, 对于大的行重J 和列重L, 构造复杂度高. 为了降低构造复杂度, 本文首先给出了长度为2i 环路的几何描述, 并且基于该几何描述提出了一种改进的最小

多媒体技术与应用案例教程习题答案

模块1习题参考答案 一、选择题 1-6 ADCCB B 二、问答题 1.简述多媒体系统的组成 多媒体系统由多媒体硬件系统和多媒体软件系统组成。多媒体硬件系统主要由多媒体计算机、多媒体存储设备、多媒体输入/输出设备和多媒体接口设备组成;多媒体软件系统主要由多媒体操作系统、多媒体驱动程序、多媒体数据处理软件、多媒体开发工具和多媒体系统组成。 2. 简述多媒体系统的分类 多媒体系统从基于功能和基于应用的角度不同可以分为两大类。从基于功能来分可以分为多媒体开发系统、多媒体演示系统、多媒体教育/培训系统;从基于应用来分可以分为多媒体出版系统、多媒体娱乐系统、多媒体通信系统、多媒体信息咨询系统、多媒体数据库系统。 3. 常用的压缩编码方法可分为哪两类?常用的数据压缩标准有哪些? 常用的压缩编码方法可分为无损压缩和有损压缩两种。所谓无损压缩,就是毫无损失地将数据信息进行压缩,解压缩后能够完全还原原始信号的一种压缩算法;有损压缩,是以牺牲原始数据中的部门信息为前提进行压缩,这种压缩算法在还原后可能会丢失部分的信息。

常用的数据压缩标准有JPEG标准、MEPG标准、H.261标准和JBIG标准。 4.简述数据压缩的可行性 首先,数据中存在着大量的冗余,如空间冗余、时间冗余和感觉冗余,这就为数据压缩提供了可能性;其次,就是利用了人耳、人眼对信号的时间变化和幅度变化的感受能力都有一定的极限这一特点,为数据压缩提供了可能性。 模块2习题参考答案 一、选择题 1.C 2.B 3.D 4.D 5.C 6.A 7.B 8.B 二、问答题 1.获取文本数据通常有哪些方法? 答:主要有键盘输入、手写输入、语音输入和扫描仪输入等。键盘输入是主要的输入方法,通过键盘,英文信息可直接输入,中文信息则通过不同的中文输入编码来完成;手写输入是一种非常人性化的中英文输入法,适合于不习惯键盘操作的人群和没有标准英文键盘的场合;语音输入是通过计算机中的音频处理系统(主要包括声卡和麦克风),采集处理人的语音信息,再经过语音识别处理,将说话内容转换成对应的文字完成输入;扫描仪输入是指用扫描仪将印刷文字以图像的方式扫描到计算机中,再用OCR文字识别软件将图像中的文字识别出来,并转换为文本格式的文件,完成文本信息的输入。 2.超文本和超媒体的联系和区别有哪些?

卷积码编码器的设计 (1)剖析

湖南文理学院 课程设计报告 课程名称:通信系统课程设计 专业班级:通信工程11102班09 学生姓名:朱涛 指导教师:侯清莲 完成时间:2014-11-18 报告成绩:

目录 一、设计要求 (1) 二、设计作用与目的 (1) 三、所用设备及软件 (1) 四、卷积码编码的概念 (1) 4.1卷积码的编码描述方法 (1) 4.2 卷积编码 (2) 4.3 卷积码的树状图 (3) 4.4 卷积码的网格图 (3) 五、 EDA设计方法及工具软件QUARTUSⅡ (4) 六、改变卷积编码器的参数仿真以及结论 (4) 6.1 不同回溯长度对卷积编码器性能的影响 (4) 6.2 不同码率对卷积编码器误码性能的影响 (5) 6.3 不同约束长度对卷积编码器的误码性能影响 (6) 七、卷积码编码器的VHDL设计与仿真 (8) 7.1 VHDL设计的优点与设计方法 (8) 7.2 卷积码编码器的VHDL实现 (10) 八、心得体会 (10) 九、参考文献 (11)

卷积编码器的设计 一、设计要求 (1)画出卷积码的原理框图,说明系统中各主要组成部分的功能。 (2)使用EDA技术及VHDL语言对卷积编码器进行设计与仿真并对结果分析。 二、设计作用与目的 (1)巩固加深对通信基本知识分析以及卷积码的掌握,提高综合运用通信知识的能力。(2)掌握采用仿真软件对系统进行仿真分析。 (3)培养学生查阅参考文献,独立思考,设计,钻研电子技术相关问题的能力。 (4)掌握相关电子线路工程技术规范以及常规电子元器件的性能技术指标。 (5)培养严肃认真的工作作风与科学态度,建立严谨的工程技术观念。 (6)了解电气图国家标准,并利用电子CAD等正确绘制电路图。 (7)培养工程实践能力,创新能力与综合设计能力。 三、所用设备及软件 (1)QUARTUSⅡ (2)PC机 四、卷积码编码的概念 4.1卷积码的编码描述方法 编码描述方法有5种:冲激响应描述法、生成矩阵描述法、多项式乘积描述法、状态图描述法和网格图描述法。卷积码的纠错能力随着N的增加而增大,而差错率随着N的增加而指数下降。在编码器复杂性相同的情况下,卷积码的性能优于分组码。分组码有严格的代数结构,但卷积码至今尚未找到如此严密的数学手段。分组码的译码算法可以由其代数特性得到。卷积码虽然可以采用适用于分组码的门限译码(即大数逻辑译码),但性能不如维特比译码和序列译码[2]。 以二元码为例,输入信息序列为u=(u0,u1,…),其多项式表示为u(x)=u0+u1x+…+…。编码器的连接可用多项式表示为g (1,1) (x)=1+x+x2和g(1,2)(x)=1+x2,称为码的子生 成多项式。它们的系数矢量g (1,1)=(111)和g (1,2) =(101)称作码的子生成元。以子生成多项式 为阵元构成的多项式矩阵G(x)=[g (1,1)(x),g (1,2) (x)],称为码的生成多项式矩阵。由生成 元构成的半无限矩阵。

奇偶校验通信原理课程设计

西南科技大学通信原理设计报告 课程名称:通信原理课程设计 设计名称:奇偶校验编码仿真 姓名:王雷 学号: 班级:通信1004 指导教师:秦明伟 起止日期:2013年7月5日星期五 西南科技大学信息工程学院制

方向设计任务书 学生班级:通信1004 学生姓名:王雷学号:20105615 设计名称:奇偶校验编码仿真 起止日期:2013年7月5日星期五指导教师:秦明伟 方向设计学生日志

奇偶校验编码仿真 一、摘要(150-250字) 奇偶校验是一种校验代码传输正确性的方法。根据被传输的一组二进制代码的数位中“1”的个数是奇数或偶数来进行校验。采用奇数的称为奇校验,反之,称为偶校验。采用何种校验是事先规定好的。通常专门设置一个奇偶校验位,用它使这组代码中“1”的个数为奇数或偶数。若用奇校验,则当接收端收到这组代码时,校验“1”的个数是否为奇数,从而确定传输代码的正确性。 二、设计目的和意义 认识matlab软件,学习掌握matlab的基本操作方法,熟悉M文件和simulink的具体实现方法,了解数据奇偶校验的原理和在matlab中的基本仿真,通过对简单的通信实验设计,提高了动手能力和对matlab操作,巩固了课程知识。 三、设计原理 在数据传输前附加一位奇校验位,用来表示传输的数据中"1"的个数是奇数还是偶数,为奇数时,校验位置为"0",否则置为"1",用以保持数据的奇偶性不变。例如,需要传输"11001110",数据中含5个"1",所以其奇校验位为"0",同时把"110011100"传输给接收方,接收方收到数据后再一次计算奇偶性,"110011100"中仍然含有5个"1",所以接收方计算出的奇校验位还是"0",与发送方一致,表示在此次传输过程中未发生错误。奇偶校验就是接收方用来验证发送方在传输过程中所传数据是否由于某些原因造成破坏。 奇偶校验原理是基于异或的逻辑功能。奇偶校验的编码方法是在原信号码组后面添加以为监督码元,奇偶校验分为奇校验和偶校验,奇校验是原信息码元加上监督码元后,使整个组成的数码组中,1的个数为奇数个。偶校验的工作原理则正好与奇校验相反。 对于n位二进码a1a2a3a4……a n奇校验有如下表示: a1⊕a2⊕a3⊕a4……⊕a n⊕C=1 偶校验的表达式为: a1⊕a2⊕a3⊕a4……⊕a n⊕C =1 其中,C为监督码元,在本设计中n为8,可以推出C的表达式为: C =a1⊕a2⊕a3⊕a4……⊕a8 在发送端让其监督码和信息码一起发送,在信息接收端,计算校验因子的表达式为: 、 S=a1⊕a2⊕a3⊕a4……⊕a n⊕C

EC16编码器设计应用案例

EC16编码器设计应用案例 摘要:介绍了一种基于单片机的智能仪器前面板的设计及实现方法。根据数字旋钮的特点,在硬件上设计了鉴相电路检测旋钮的正旋和反旋,巧妙地将旋钮扫描和按键扫描统一起来,以Philip低成本的Flash型单片机P89LPC922作为处理芯片,运用了定时中断、状态机、软件去抖、RS-232接口协议等方法实现软件设计,提高按键和旋钮的抗干扰能力,并介绍了用自定义的通信协议计算旋钮转动量和减少主机负担。具有良好的通用性,适用于短周期、低成本的按键和旋钮混合面板设计,并已成功地应用于数字存储大功率半导体管特性曲线图示仪。 关键词:单片机;智能仪器;面板;数字旋钮;鉴相电路 引言: 许多仪器的前面板通常是由诸多的旋钮、按键组成的混合界面。传统的仪器前面板上通常有两种旋钮,一种是电位器,用于调节连续变化的量;另一种是档位开关,用于调节间隔变化的量。它们嵌入在测量电路中,可以直接改变仪器的参数和设置。而在现代智能仪器[1]中,这两类调节均可以通过数字旋钮由微控制器将用户操作的变化量反馈给仪器的主处理器,再由主处理器改变仪器的参数和设置。所以,智能仪器上的数字旋钮和传统仪器上的旋钮在原理和处理方法上有很大不同。为了节省成本,面板处理往往采用体积小、性价比高的单片机(MCU)。运用单片机不但经济灵活,并可充分利用MCU逻辑处理的优势,大大简化外围连线,对旋钮按键混合控制系统[2]的处理尤为突出。 设计采用LPC900系列的P89LPC922Flash单片机来实现软件处理。P89LPC922采用高性能的处理器结构,6倍于标准80C51器件的速率,并自带波特率发生器。充分考虑单片机的资源和处理速度,分模块设计——按钮电路,旋钮电路,串口电路,扫描电路。用protel完成电路原理图,制作电路板,在KeilC环境下编写软件。软件和硬件相结合,协同实现整个面板。 1硬件设计及原理 1.1旋钮电路设计 1.1.1数字旋钮的工作原理 本设计选用常见的编码器EC16系列作为数字旋钮,如图1。4、5脚供固定之用,3脚接VCC(+5V),1、2脚在转动时输出连续脉冲。这种旋钮只有两种操作,即正旋和反旋。通过示波器可以观察到如图所示的旋钮转动时1、2脚的波形。

低密度奇偶检验码

低密度奇偶检验码(LDPC code) LDPC码是麻省理工学院Robert Gallager于1962年在博士论文中提出的一种具有稀疏校验矩阵的分组纠错码。几乎适用于所有的信道,因此成为编码界近年来的研究热点。它的性能逼近香农限,且描述和实现简单,易于进行理论分析和研究,译码简单且可实行并行操作,适合硬件实现。 任何一个(n,k)分组码,如果其信息元与监督元之间的关系是线性的,即能用一个线性方程来描述的,就称为线性分组码。 低密度奇偶校验码图(LDPC码)本质上是一种线形分组码,它通过一个生成矩阵G将信息序列映射成发送序列,也就是码字序列。对于生成矩阵G,完全等效地存在一个奇偶校验矩阵H,所有的码字序列C构成了H的零空间 (null space),即HCT=0。 LDPC仿真系统图 DLPC 码的奇偶校验矩阵H是一个稀疏矩阵,相对于行与列的长度,校验矩阵每行、列中非零元素的数目(我们习惯称作行重、列重)非常小,这也是LDPC码之所以称为低密度码的原因。由于校验矩阵H的稀疏性以及构造时所使用的不同规则,使得不同LDPC码的编码二分图(Taner图)具有不同的闭合环路分布。而二分图中闭合环路是影响LDPC码性能的重要因素,它使得LDPC码在类似可信度传播(Belief ProPagation)算法的一类迭代译码算法下,表现出完全不同的译码性能。

当H的行重和列重保持不变或尽可能的保持均匀时,我们称这样的LDPC码为正则LDPC码,反之如果列、行重变化差异较大时,称为非正则的LDPc码。研究结果表明正确设计的非正则LDPC码的性能要优于正则LDPC。根据校验矩阵H中的元素是属于GF(2)还是GF(q)(q=2p),我们还可以将LDPC码分为二元域或多元域的LDPC码。研究表明多元域LDPC码的性能要比二元域的好。 LDPC码 - 发展现状 LDPC码 LDPC ( Low-density Parity-check,低密度奇偶校验)码是由 Gallager 在1963 年提出的一类具有稀疏校验矩阵的线性分组码 (linear block codes),然而在接下来的 30 年来由于计算能力的不足,它一直被人们忽视。1993年,D MacKay、M Neal 等人对它重新进行了研究,发现 LDPC 码具有逼近香农限的优异性能。并且具有译码复杂度低、可并行译码以及译码错误的可检测性等特点,从而成为了信道编码理论新的研究热点。 Mckay ,Luby 提出的非正则 LDPC 码将 LDPC 码的概念推广。非正则LDPC码的性能不仅优于正则 LDPC 码,甚至还优于 Turbo 码的性能,是目前己知的最接近香农限的码。 Richardson 和 Urbank 也为 LDPC 码的发展做出了巨大的贡献。首先,他们提出了一种新的编码算法,在很大程度上减轻了随机构造的 LDPC 码在编码上的巨大运算量需求和存储量需求。其次,他们发明了密度演进理论,能够有效的分析出一大类 LDPC 译码算法的译码门限。仿真结果表明,这是一个紧致的译码门限。最后,密度演进理论还可以用于指导非正则 LDPC码的设计,以获得尽可能优秀的性能。

卷积码的设计与实现

湖南文理学院课程设计报告 课程名称:通信系统课程设计 院部:电气与信息工程学院 专业班级: 学生姓名: 指导教师: 完成时间: 2011 年 12 月 29日 报告成绩:

目录 目录 (2) 摘要 (3) Abstract (4) 一、引言 (5) 1.1设计任务及基本要求 (5) 1.2设计目的 (6) 1.3 设计所用仪器设备.................................................................................. 错误!未定义书签。 二、基本概念 (6) 2.1 卷积码的编码原理 (6) 2.2 卷积码编码描述 (6) 2.3 卷积码译码描述 (6) 三、卷积码的编译码原理 (6) 3.1卷积码的图形描述 (6) 3.1.1 树状图 (8) 3.1.2 网格图 (8) 3.1.3 状态图 (9) 3.2 卷积积码的编码算法 (9) 3.3卷积码的Viterbi译码 (10) 四、卷积码的仿真及性能分析 (12) 4.1 SIMULINK仿真模块 (12) 4.2 卷积码的参数对误码率的影响 (13) 4.2.1 码率对误码性能的影响 (13) 4.2.2 约束长度对误码性能的影响 (15) 4.2.3 回溯长度对卷积码性能的影响 (16) 4.3 仿真分析 (17) 总结 (18) 参考文献: (19)

摘要 卷积码是深度空间通信系统和无线通信系统中常用的一种差错控制编码。在编码过程中,卷积码充分利用了各码字间的相关性。在与分组码同样的码率和设备复杂性的条件下,无论从理论上还是从实践上都证明,卷积码的性能都比分组码具有优势。而且卷积码在实现最佳译码方面也较分组码容易。因此卷积码广泛应用于卫星通信,CDMA数字移动通信等通信系统,是很有前途的一种编码方式。对其进行研究有很大的现实意义。为了解决传统的维特比译码器结构复杂、译码速度慢、消耗资源大的问题,提出一种新型的适用于FPGA 特点,路径存储于译码输出并行工作,同步存储路径矢量和状态矢量的译码器设计方案。该设计方案通过在ISE.2i中仿真验证,译码结果正确,得到编码前的原始码元,速度显著提高,译码器复杂程度明显降低。并在实际的软件无线电通信系统中信道编解码部分得到应用,性能优良。 关键词:卷积码;误码性能;原理

编码器、译码器及应用电路设计

实验六编码器、译码器及应用电路设计 一、实验目的: 1、掌握中规模集成编码器、译码器的逻辑功能测试和使用方法; 1、学会编码器、译码器应用电路设计的方法; 3、熟悉译码显示电路的工作原理。 二、实验原理: 编码是用文字、符号或者数字表示特定对象的过程,在数字电路中是用二进制数进行编码的,相应的二进制数叫二进制代码。编码器就是实现编码操作的电路。本实验使用的是优先编码器74LS147,当输入端有两个或两个以上为低电平时,将对输入信号级别相对高的优先编码,其引脚排列如图6—1所示。 图6—1 74LS147引脚排列图图6—2 74LS138引脚排列图译码是编码的逆过程,是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器在数字系统有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配和组合控制信号等。不同的功能可选用不同种类的译码器。 译码器按照功能的不同,一般分为三类: 1、变量译码器(二进制译码器):用以表示输入变量的状态,如2—4线、3—8线、4—16线译码器。以3—8线译码器74LS138为例介绍: 图6—2为74LS138的引脚图,其中,A2A1A0为地址输入端,为译码器输出端,为使能端(只有当时,才能进行译码)。 图6—3 74LS42引脚排列图图6—5为CC4511引脚排列图 2、码制变换译码器:用于同一个数据的不同代码之间的相互变换。这种译码器的代表是4—10线译码器,它的功能是将8421BCD码译为十个对象,如74LS42等。它的原理与 74LS138译码器类同,只不过它有四个输入端,十个输出端。4位输入代码共有0000—1111

案例五旋转编码器的安装与应用

案例五旋转编码器的安装与应用 1.项目训练目的 掌握旋转编码器的安装与使用方法。 2.项目训练设备 旋转编码器及相应耦合器一套。 3.项目训练内容 先熟悉旋转编码器的使用说明书。 (1)旋转编码的安装步骤及注意事项 ①安装步骤: 第一步:把耦合器穿到轴上。不要用螺钉固定耦合器和轴。 第二步:固定旋转编码器。编码器的轴与耦合器连接时,插入量不能超过下列值。 E69-C04B型耦合器,插入量 5.2mm;E69-C06B型耦合器,插人量 5.5mm;E69-Cl0B型耦合器,插入量7.lmm。 第三步:固定耦合器。紧固力矩不能超过下列值。E69-C04B型耦合器,紧固力矩2.0kfg?cm;E69-C06B型耦合器,紧固力矩 2.5kgf?cm;E69B-Cl0B型耦合器,紧固力矩4.5kfg?cm。 第四步:连接电源输出线。配线时必须关断电源。 第五步:检查电源投入使用。 ②注意事项: 采用标准耦合器时,应在允许值内安装。如图5-1所示。 图5-1 标准耦合器安装 连接带及齿轮结合时,先用别的轴承支住,再将旋转编码器和耦合器结合起来。如图 5-2所示。 图5-2 旋转编码器安装 齿轮连接时,注意勿使轴受到过大荷重。 用螺钉紧固旋转编码器时,应用5kfg?cm左右的紧固力矩。 固定本体进行配线时,不要用大于3kg的力量拉线。 可逆旋转使用时,应注意本体的安装方向和加减法方向。 把设置的装置原点和编码器的Z相对准时,必须边确定Z相输出边安装耦合器。 使用时勿使本体上粘水滴和油污。如浸入内部会产生故障。 (2)配线及连接

①配线应在电源0FF状态下进行。电源接通时,若输出线接触电源线,则有时会损坏输出回路。 ②若配线错误,则有时会损坏内部回路,所以配线时应充分注意电源的极性等。 ③若和高压线、动力线并行配线,则有时会受到感应造成误动作或损坏。 ④延长电线时,应在10m以下。还由于电线的分布容量,波形的上升、下降时间会延长,所以有问题时,应采用施密特回路等对波形进行整形。 还有为了避免感应噪声等,也要尽量用最短距离配线。集成电路输人时,要特别注意。 ⑤电线延长时,因导体电阻及线间电容的影响。波形的上升、下降时间变长,容易产 生信号间的干扰(串音),因此应使用电阻小、线间电容低的电线(双绞线、屏蔽线)。

基于matlab的2-3卷积码编码译码设计与仿真

西南科技大学 方向设计报告 课程名称:通信工程方向设计 设计名称:2/3卷积码编译码器仿真与性能分析 姓名: 学号: 班级: 指导教师: 起止日期:2011.12.12-2012.1.6 西南科技大学信息工程学院制

方向设计任务书 学生班级:学生姓名:学号: 设计名称:2/3卷积码编译码器仿真与性能分析 起止日期:2011.12.12-2012.1.6指导教师: 设计要求: (1)分析2/3卷积码编码器结构; (2)分析2/3卷积码译码的Viterbi算法; (3)基于SIMULINK进行2/3卷积码的纠错性能仿真; 方向设计学生日志 时间设计内容 12.15-12.17 查看题目及设计要求。 12.18-12.23 查阅相关资料,设计方案。 12.23-12.27 编写报告及调试程序。 12.28-12.29 完善修改课程设计报告。 12.30-12.31 答辩。

方向设计考勤表 周星期一星期二星期三星期四星期五 方向设计评语表 指导教师评语: 成绩:指导教师: 年月日

2/3卷积码编译码器仿真与性能分析 摘要: 卷积码是一种性能优越的信道编码。它的编码器和译码器都比较容易实现,同时它具有较强的纠错能力。随着纠错编码理论研究的不断深入,卷积码的实际应用越来越广泛。本文简明地介绍了卷积码的编码原理和Viterbi译码原理。并在SIMULINK模块设计中,完成了对卷积码的编码和译码以及误比特统计整个过程的模块仿真。最后,通过在仿真过程中分别改变卷积码的重要参数来加深理解卷积码的这些参数对卷积码的误码性能的影响。经过仿真和实测,并对测试结果作了分析。 关键词: 卷积码编码器、viterbi译码器、SIMULINK

奇偶校验

奇偶校验 在数据传输前在数据位后附加一位奇偶校验位,用来表示传输的数据中"1"的个数是奇数还是偶数,以此判断数据传输正确性的一种校验方法。 奇偶校验的产生: 为奇数时,校验位置为"0",否则置为"1",用以保持数据的奇偶性不变。例如,需要传输"11001110",数据中含5个"1",所以其奇校验位为"0",同时把"110011100"传输给接收方,接收方收到数据后再一次计算奇偶性,"110011100"中仍然含有5个"1",所以接收方计算出的奇校验位还是"0",与发送方一致,表示在此次传输过程中未发生错误。奇偶校验就是接收方用来验证发送方在传输过程中所传数据是否由于某些原因造成破坏。 具体方法如下: 奇校验: 就是让原有数据序列中(包括你要加上的一位)1的个数为奇数 1000110(0)你必须添0这样原来有3个1已经是奇数了所以你添上0之后1的个数还是奇数个。 偶校验: 就是让原有数据序列中(包括你要加上的一位)1的个数为偶数 1000110(1)你就必须加1了这样原来有3个1要想1的个数为偶数就只能添1了。 按校验的数据量和生成校验码的方式分为三类: 1.垂直奇偶校验码:以一个字符作为校验单位纵向生成校验码位;

例如使用ASCII编码的一个字符由8bit组成,其中低7bit为信息位,最高1bit作为校验位,假设某一字符的标准ASCII编码为0011000,根据奇偶校验规则,如果采用奇校验,则校验位应为1(这样字符中1的个数才能为奇数),即00110001;如果采用偶校验,校验位应为0,即00110000垂直奇偶校验码的特点:校验处理过程简单,但如果字符中发生偶数位的错误就检测不出来,也检测不到错误发生在哪一位。 2.水平奇偶校验码:以多个字符作为校验单位横向生成校验码位; 生成方法:以若干个字符作为一个校验单位。每个字符各自生成一个垂直奇偶校验码,再为每个字符的相同位及其垂直奇偶校验码生成水平奇偶校验码,这些校验码形成一个校验字符,附加在被校验字符的后面一并传输到接收方,该校验字符即称为方阵校验码。 校验特点:一次能校验更多的数据,效率较高,系统实现也比较简单,检测可靠性有所提高,但仍然不能检测出所有的错误。 3.水平垂直冗余校验码(方阵校验码):以多个字符作为校验单位水平垂直两个方向共同生成校验字符。