浅谈状态机的设计方法及应用

浅谈状态机的设计方法及应用

刘成玉;李明;陈洁

【期刊名称】《集成电路通讯》

【年(卷),期】2007(025)001

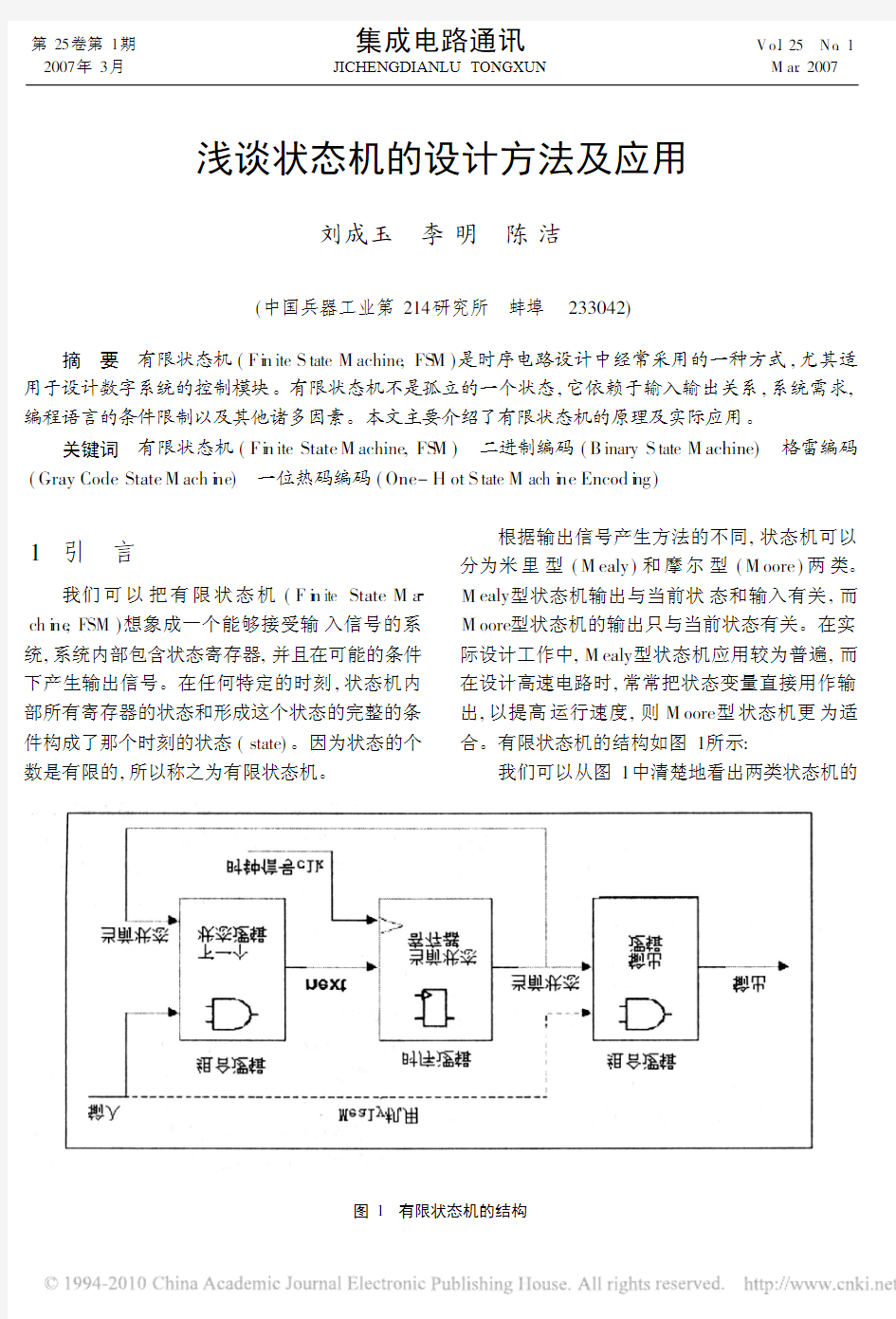

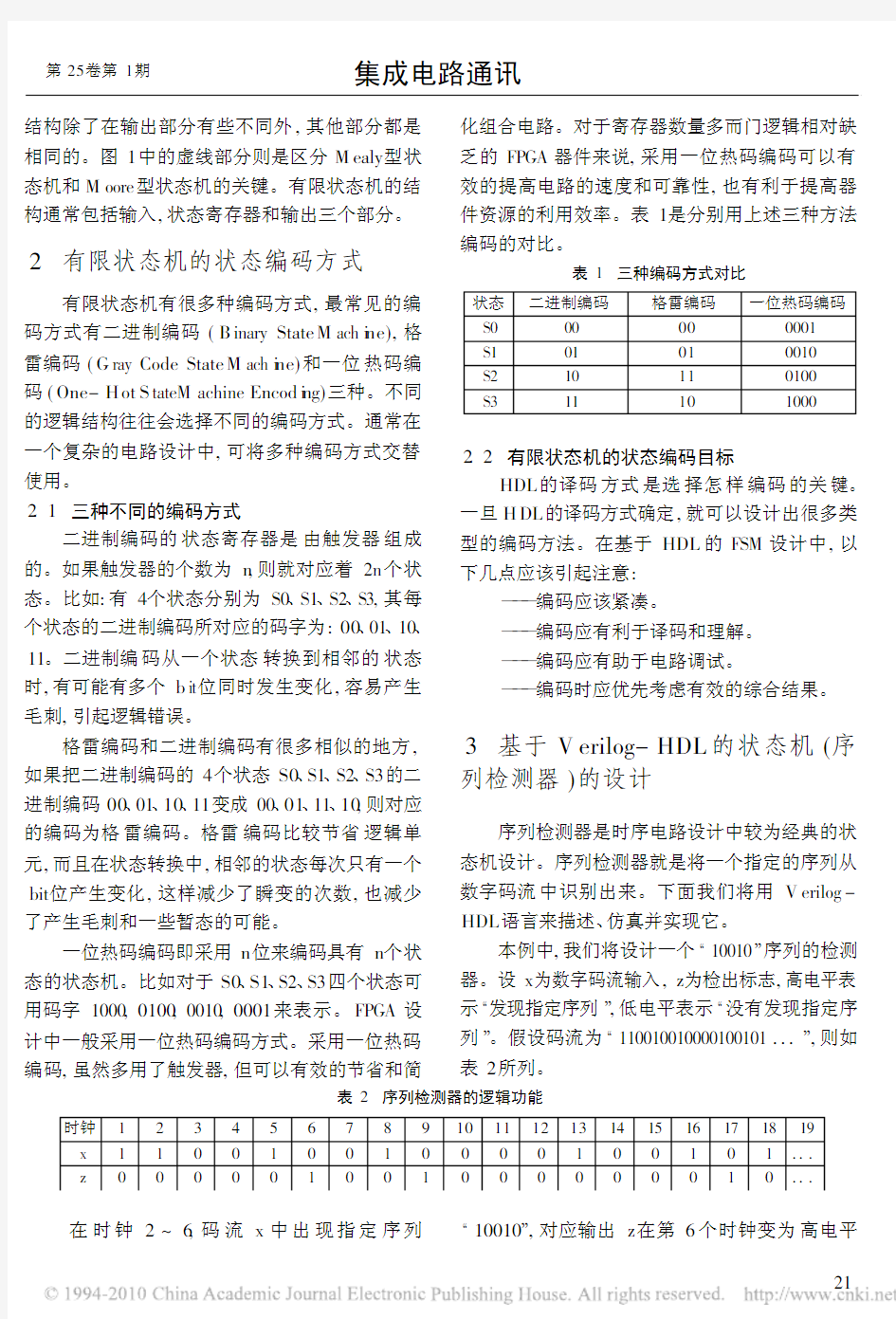

【摘要】有限状态机(Finite State Machine,FSM)是时序电路设计中经常采用的一种方式,尤其适用于设计数字系统的控制模块。有限状态机不是孤立的一个状态,它依赖于输入输出关系,系统需求,编程语言的条件限制以及其他诸多因素。本文主要介绍了有限状态机的原理及实际应用。

【总页数】5页(20-24)

【关键词】有限状态机(Finite;State;Machine,FSM);二进制编码(Binary;State;Machine);格雷编码(Gray;Code;State;Machine)一位热码编码(One-Hot;State;Machine;Encoding)

【作者】刘成玉;李明;陈洁

【作者单位】中国兵器工业第214研究所,蚌埠233042

【正文语种】英文

【中图分类】TN915.04

【相关文献】

1.应用计数器设计状态机的一种新方法 [J], 孙蕾

2.一种应用VHDL语言设计有限状态机控制器的方法 [J], 牛斌; 马利; 张玉奇

3.状态机思路在单片机程序设计中的应用 [J], 张俊

4.层次状态机及协处理状态机的Verilog HDL描述方法研究[J], 刘海成; 关旭东

相关主题