80C51单片机的上电复位POR

80C51单片机的上电复位POR(Pmver On Reset)实质上就是上电延时复位,也就是在上电延时期间把单片机锁定在复位状态上。为什么在每次单片机接通电源时,都需要加入一定的延迟时间呢?分析如下。

1 上电复位时序

在单片机及其应用电路每次上电的过程中,由于电源同路中通常存在一些容量大小不等的滤波电容,使得单片机芯片在其电源引脚VCC和VSS之间所感受到的电源电压值VDD,是从低到高逐渐上升的。该过程所持续的时间一般为1~100ms(记作 tsddrise)。上电延时taddrise的定义是电源电压从lO%VDD上升到90%VDD所需的时间,如图1所示。

在单片机电源电压上升到适合内部振荡电路运行的范围并且稳定下来之后,时钟振荡器开始了启动过程(具体包括偏置、起振、锁定和稳定几个过程)。该过程所持续的时间一般为1~50 ms(记作tOSC)。起振延时tOSC的定义是时钟振荡器输出信号的高电平达到Vih1所需的时间。从图1所示的实际测量图中也可以看得很清楚。这里的 Vih1是单片机电气特性中的一个普通参数,代表XTALl和RST引脚上的输入逻辑高电平。例如,对于常见的单片机型号AT89C5l和

AT89S5l,厂家给出的Vih1值为0.7VDD~VDD+0.5V。

从理论上讲,单片机每次上电复位所需的最短延时应该不小于treset。这里,treset等于上电延时taddrise与起振延时tOSC之和,如图1所示。从实际上讲,延迟一个treset往往还不够,不能够保障单片机有--一个良好的工作开端。

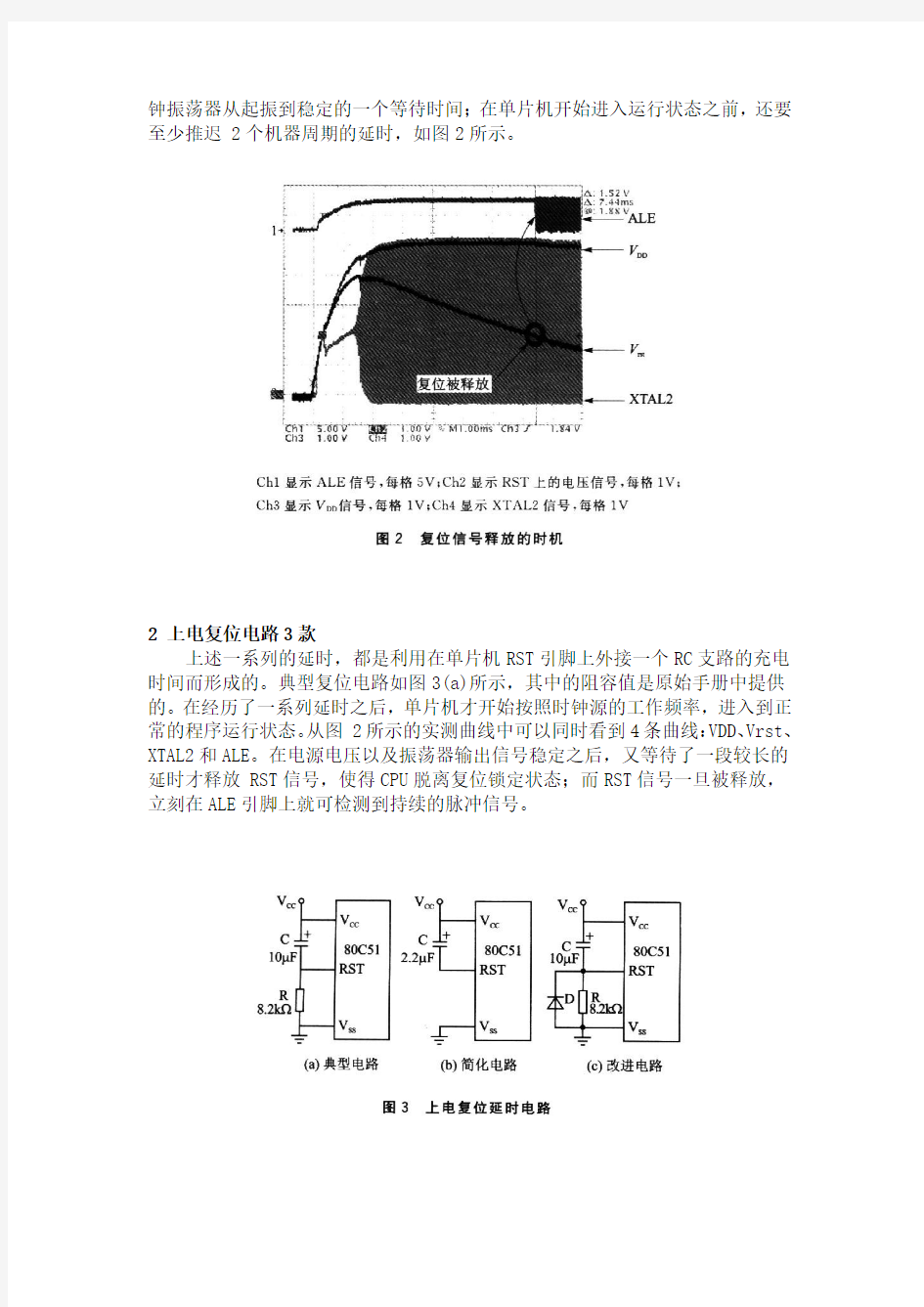

在单片机每次初始加电时,首先投入工作的功能部件是复位电路。复位电路把单片机锁定在复位状态上并且维持一个延时(记作TRST),以便给予电源电压从上升到稳定的一个等待时间;在电源电压稳定之后,再插入一个延时,给予时

钟振荡器从起振到稳定的一个等待时间;在单片机开始进入运行状态之前,还要至少推迟 2个机器周期的延时,如图2所示。

2 上电复位电路3款

上述一系列的延时,都是利用在单片机RST引脚上外接一个RC支路的充电时间而形成的。典型复位电路如图3(a)所示,其中的阻容值是原始手册中提供的。在经历了一系列延时之后,单片机才开始按照时钟源的工作频率,进入到正常的程序运行状态。从图 2所示的实测曲线中可以同时看到4条曲线:VDD、Vrst、XTAL2和ALE。在电源电压以及振荡器输出信号稳定之后,又等待了一段较长的延时才释放 RST信号,使得CPU脱离复位锁定状态;而RST信号一旦被释放,立刻在ALE引脚上就可检测到持续的脉冲信号。

由于标准80C51的复位逻辑相对简单,复位源只有RST一个(相对新型单片机来说,复位源比较单一),因此各种原因所导致的复位活动以及复位状态的进入,都要依靠在外接引脚RST上施加一定时间宽度的高电平信号来实现。

标准80C5l不仅复位源比较单一,而且还没有设计内部上电复位的延时功能,因此必须借助于外接阻容支路来增加延时环节,如图3(a)所示。其实,外接电阻R还是可以省略的,理由是一些CMOS单片机芯片内部存在一个现成的下拉电阻Rrst。例如,AT89系列的Rrst阻值约为50~200kΩ; P89V51Rx2系列的Rrst阻值约为40~225 kΩ,如图4所示。因此,在图3(a)基础上,上电复位延时电路还可以精简为图3(b)所示的简化电路(其中电容C的容量也相应减小了)。

在每次单片机断电之后,须使延时电容C上的电荷立刻放掉,以便为随后可能在很短的时间内再次加电作好准备。否则,在断电后C还没有充分放电的情况下,如果很快又加电,那么RC支路就失去了它应有的延迟功能。因此,在图3(a)的基础上添加一个放电二极管D,上电复位延时电路就变成了如图3(c)所示的改进电路。也就是说,只有RC支路的充电过程对电路是有用的,放电过程不仅无用,而且会带来潜在的危害。于是附加一个放电二极管D来大力缩短放电持续时间,以便消除隐患。二极管D只有在单片机断电的瞬间(即VCC趋近于0V,可以看作VCC对地短路)正向导通,平时一直处于反偏截止状态。

3 上电复位失败的2种案例分析

假如上电复位延迟时间不够或者根本没有延时过程,则单片机可能面临以下2种危险,从而导致CPU开始执行程序时没有一个良好的初始化,甚至陷入错乱状态。

①在时钟振荡器输出的时钟脉冲还没有稳定,甚至还没有起振之前,就因释放RST信号的锁定状态而放纵CPU开始执行程序。这将会导致程序计数器PC中首次抓取的地址码很可能是0000H之外的随机值,进而引导CPU陷入混乱状态。参考图5所示的实测信号曲线。

②在电源电压还没有上升到合适范围之前(自然也是时钟尚未稳定之前),就释放RST信号的锁定状态,将会使单片机永远感受不到复位信号、经历不到复位过程、包含PC在内的各个SFR内容没有被初始化而保留了随机值,从而导致CPU 从一个随机地址开始执行程序,进而也陷入混乱状态。参考图6所示的实测信号曲线。

4 外接监控器MAX810x

为了提高单片机应用系统的稳定性,以及保障单片机应用系统的可靠复位,许多世界著名的半导体公司,陆续推出了种类繁多、功能各异、封装微小的专用集成电路。本文仅以带有电源电压跌落复位和上电延迟复位功能的3脚芯片MAX810x为例,简单说明。

MAX810x(x=L、M、J、T、S或R)是美国Maxim公司研制的一组CMOS电源监

控电路,能够为低功耗微控制器MCU(或μC)、微处理器 MPU(或μP)或数字系统监视3~5V的电源电压。在电源上电、断电和跌落期间产生脉宽不低于140ms 的复位脉冲。与采用分立元件或通用芯片构成的欠压检测电路相比,将电压检测和复位延时等功能集成到一片3引脚封装的小芯片内,大大降低了系统电路的复杂性,减少了元器件的数量,显著提高了系统可靠性和精确度。应用电路如图7所示。

MAX810x系列产品提供高电平复位信号,并且还能提供6种固定的检测门限(4.63V、4.38V、4.OOV、3.08V、2.93V和2.63V)。例如,MAX810M的检测门限电压就是4.38V,回差电压约为O.16V。

对于MAX810,在电源上电、断电或跌落期间,只要VCC还高于1.1V,就能保证RESET引脚输出高电压。在VCC上升期问RESET维持高电平,直到电源电压升至复位门限以上。在超过此门限后,内部定时器大约再维持240 ms后释放RESET,使其返回低电平。无论何时只要电源电压降低到复位门限以下(即电源跌落),RESET引脚就会立刻变高。

c单片机上电复位和复位延时的时序分析

80C51单片机上电复位和复位延时的时序分析 80C51单片机的上电复位POR(Power On Reset)实质上就是上电延时复位,也就是在上电延时期间把单片机锁定在复位状态上.为什么在每次单片机接通电源时,都需要加入一定的延迟时间呢?分析如下. 1 上电复位时序 在单片机及其应用电路每次上电的过程中,由于电源回路中通常存在一些容量大小不等的滤波电容,使得单片机芯片在其电源引脚VCC和VSS之间所感受到的电源电压值VDD,是从低到高逐渐上升的.该过程所持续的时间一般为1~100 ms(记作taddrise).上电延时taddrise的定义是电源电压从10% VDD上升到90% VDD所需的时间,如图1所示. 图1 上电延时taddrise和起振延时tosc实测结果 在单片机电源电压上升到适合内部振荡电路运行的范围并且稳定下来之后,时钟振荡器开始了启动过程(具体包括偏置、起振、锁定和稳定几个过程).该过程所持续的时间一般为1~50 ms(记作tosc).起振延时tosc的定义是时钟振荡器输出信号的高电平达到Vih1所需的时间.从图1所示的实际测量图中也可以看得很清楚.这里的Vih1是单片机电气特性中的一个普通参数,代表XTAL1和RST引脚上的输入逻辑高电平.例如,对于常见的单片机型号AT89C51和AT89S51,厂家给出的Vih1值为0.7VDD~VDD+0.5 V. 从理论上讲,单片机每次上电复位所需的最短延时应该不小于treset.这里,treset等于上电延时taddrise与起振延时tosc之和,如图1所示.从实际上讲,延迟一个treset往往还不够,不能够保障单片机有一个良好的工作开端. 在单片机每次初始加电时,首先投入工作的功能部件是复位电路.复位电路把单片机锁定在复位状态上并且维持一个延时(记作TRST),以便给予电源电压从上升到稳定的一个等待时间;在电源电压稳定之后,再插入一个延时,给予时钟振荡器从起振到稳定的一个等待时间;在单片机开始进入运行状态之前,还要至少推迟2个机器周期的延时,如图2所示.

STC89C51单片机引脚功能介绍

C51单片机引脚功能介绍 C51单片机引脚功能介绍 单片机的40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。 ⒈电源: ⑴VCC - 芯片电源,接+5V; ⑵VSS - 接地端; ⒉时钟:XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。 ⒊控制线:控制线共有4根, ⑴ALE/PROG:地址锁存允许/片内EPROM编程脉冲 ①ALE功能:用来锁存P0口送出的低8位地址新门户 ②PROG功能:片内有EPROM的芯片,在EPROM编程期间,此引脚输入编程脉冲。 ⑵PSEN:外ROM读选通信号。

⑶RST/VPD:复位/备用电源。 ①RST(Reset)功能:复位信号输入端。 ②VPD功能:在Vcc掉电情况下,接备用电源。 ⑷EA/Vpp:内外ROM选择/片内EPROM编程电源。 ①EA功能:内外ROM选择端。 ②Vpp功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。 ⒋I/O线 89C51共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。 拿到一块芯片,想要使用它,首先必须要知道怎样连线,我们用的一块称之为89C51的芯片,下面我们就看一下如何给它连线。 1、电源:这当然是必不可少的了。单片机使用的是5V电源,其中正极接40管脚,负极(地)接20管脚。 2、振蒎电路:单片机是一种时序电路,必须供给脉冲信号才能正常工作,在单片机内部已集成了振荡器,使用晶体振荡器,接18、19脚。只要买来晶体震荡器,连上就能了,按下图1接上即可。 3、复位管脚:按下图1中画法连好。 EA管脚:EA管脚接到正电源端。至此,一个单片机就接好,通上电,单片机就开始工作了。 我们的第一个任务是要用单片机点亮一只发光二极管LED,显然,这个LED必须要和单片机的某个管脚相连,不然单片机就没法控制它了,单片机上除了刚才用掉的5个管脚,还有35个,我们将这个LED和1脚相连。(见图1,其中R1是限流电阻) 按照这个图的接法,当1脚是高电平时,LED不亮,只有1脚是低电平时,LED才发亮。因此要1脚我们要能够控制,也就是说,我们要能够让1管脚按要求变为高或低电平。即然要控制1脚,就得给它起个名字,叫它什么名字呢,设计51芯片的INTEL公司已经起好了,就叫它P1.0,这是规定。 名字有了,要计算机做事,也得要向计算机发命令,计算机能听得懂的命令称之为计算机的指令。让一个管脚输出高电平的指令是SETB,让一个管脚输出低电平的指令是CLR。因此,我们要P1.0输出高电平,只要写SETB P1.0,要P1.0输出低电平,只要写CLR P1.0就能了。但是我们怎样才能计算机执行这条指令呢?要解决这个问题,第一,计算机看不懂SETB CLR之类的指令,我们得把指令翻译成计算机能懂的方式,再让计算机去读。计算机只懂一样东西:数字。因此我们得把SETB P1.0变为(D2H,90H ),把CLR P1.0变为(C2H,90H ),至于为什么是这两个数字,这也是由51芯片的设计者--INTEL规定的,我们不去研究。第二步,在得到这两个数字后,还要借助于一个硬件工具"编程器"将这两个数字进入单片机的内部。编程器:就是把你在电脑上写出来的代码用汇编等编译器生成的一个

51单片机复位电路有关问题

想问一下单片机复位电路问题 复位过程我明白,RST接高电平复位,接低电平单片机正常工作 但电路连接不太理解什么意思, 想知道图中电解电容的作用,既然是按键高电平复位为什么要加电解电容呢不加可以吗?如果一定要加原因是什么? 另外想知道电容作用是隔直流通交流,是绝对的直流不通过还是什么充电过程无电流放电过程有电流,求指教 我认为绛红的蓝同学说的不太好。 电容确实可以起到按键去除抖动的作用,但是这里的电容还有一个更重要的作用就是上电复位,因为考虑到芯片刚刚上电时由于供电不稳定而做出错误的计算,所以增加一个上电复位以达到延时启动CPU的目的,使芯片能够正常工作。虽然现在很多芯片自带了上电延时功能,但是我们一般还是会增加额外的上电复位电路,提高可靠性。 上电复位是如此工作的,此时不用考虑按键和你图中1K电阻的作用。上电瞬间,电压VCC短时间内从0V上升到5V(比方说5V),这一瞬间相当于交流电,电容相当于导线,5V的电压全部加在10K电阻上,也就是说,这时RST的电平状态为高电平。但是从上电开始,电容自己就慢慢充电,其两端电压呈曲线上升,最终达到5V,也就是说其正端电位为5V,负端电位为0V,其负端也就正好是RST,此时RST为低电平,单片机开始正常工作。 添加按键是为了手动复位,一般那个1K电阻可以不加。当按键按下时,电容两端构成回路并放电,使RST端重新变为高电平,按键抬起时电容又充电使RST 变回低电平。 复位电路的作用 在上电或复位过程中,控制CPU的复位状态:这段时间内让CPU保持复位状态,而不是一上电或刚复位完毕就工作,防止CPU发出错误的指令、执行错误操作,也可以提高电磁兼容性能。 无论用户使用哪种类型的单片机,总要涉及到单片机复位电路的设计。而单片机复位电路设计的好坏,直接影响到整个系统工作的可靠性。许多用户在设计完单片机系统,并在实验室调试成功后,在现场却出现了“死机”、“程序走飞”等现象,这主要是单片机的复位电路设计不可靠引起的。 基本的复位方式 单片机在启动时都需要复位,以使CPU及系统各部件处于确定的初始状态,并从初态开始工作。89系列单片机的复位信号是从RST引脚输入到芯片内的施密特触发器中的。当系统处于正常工作状态时,且振荡器稳定后,如果RST引脚上有一个高电平并维持2个机器周期(24个振荡周期)以上,则CPU就可以响应并将系统复位。单片机系统的复位方式有:手动按钮复位和上电复位 1、手动按钮复位 手动按钮复位需要人为在复位输入端RST上加入高电平(图1)。一般采用的办法是在RST端和正电源Vcc之间接一个按钮。当人为按下按钮时,则Vcc的+5V电平就会直接加到RST端。手动按钮复位的电路如所示。由于人的动作再快也会使按钮保持接通达数十毫秒,所以,完全能够满足复位的时间要求。

单片机复位原理总结

题6是作者在2006年10月份全国巡回人才招聘的考题,居然60%的同学得零分,却只有一位同学得满分,这种现象值得我们彻底地反思。 题6:单片机上电复位电路如图3所示,请回答下列问题(12分): (1)该复位电路适用于高电平复位还是低电平复位? (2)试述复位原理,画出上电时Vc的波形; (3)试述二极管D的作用。 图3RC复位电路 答案:(1)低电平复位。 (2)在图3中,CPU上电时,但由于电容C两端的电压V C不能突变,因此V C保持低 不断上升,上升曲线如图4所示。只要选择合适电平。但随着电容C的充电,V C 就可以在CPU复位电压以下持续足够的时间使CPU复位。复位之后,的R和C,V C V 上升至电源电压,CPU开始正常工作。相当于在CPU上电时,自动产生了一个C 一定宽度的低电平脉冲信号,使CPU复位。 4 RC充放电曲线 图 (3)当电源电压消失时,二极管D为电容C提供一个迅速放电的回路,使/RESET端迅速回零,以便下次上电时CPU能可靠复位。 这是一个非常重要的知识点,如果CPU的复位电路设计得不合理将会导致CPU严重死机,并且影响与CPU有关的外围器件的稳定性,比如存储器上电丢失数据。因此我们在学习的过程中,一定要善于将前后的知识连贯起来。千万不要随意放过哪怕一个细小的问题,只有这样才能做到融会贯通。在管理新产品的开发过程中,作者发现出现质量事故的产品都是由一些看起来并不起眼的小问题所引起的,最终给企业带来的损失却是巨大的,甚至是毁灭性的打

击。 二、复位电路的工作原理 在书本上有介绍,51单片机要复位只需要在第9引脚接个高电平持续2US就可以实现,那这个过程是如何实现的呢? 在单片机系统中,系统上电启动的时候复位一次,当按键按下的时候系统再次复位,如果释放后再按下,系统还会复位。所以可以通过按键的断开和闭合在运行的系统中控制其复位。 开机的时候为什么为复位 在电路图中,电容的的大小是10uF,电阻的大小是10k。所以根据公式,可以算出电容充电到电源电压的0.7倍(单片机的电源是5V,所以充电到0.7倍即为3.5V),需要的时间是10K*10UF=0.1S。 也就是说在电脑启动的0.1S内,电容两端的电压时在0~3.5V增加。这个时候10K电阻两端的电压为从5~1.5V减少(串联电路各处电压之和为总电压)。所以在0.1S内,RST引脚所接收到的电压是5V~1.5V。在5V正常工作的51单片机中小于1.5V的电压信号为低电平信号,而大于1.5V的电压信号为高电平信号。所以在开机0.1S内,单片机系统自动复位(RST引脚接收到的高电平信号时间为0.1S左右)。 按键按下的时候为什么会复位 在单片机启动0.1S后,电容C两端的电压持续充电为5V,这是时候10K电阻两端的电压接近于0V,RST处于低电平所以系统正常工作。当按键按下的时候,开关导通,这个时候电容两端形成了一个回路,电容被短路,所以在按键按下的这个过程中,电容开始释放之前充的电量。随着时间的推移,电容的电压在0.1S内,从5V释放到变为了1.5V,甚至更小。根据串联电路电压为各处之和,这个时候10K电阻两端的电压为3.5V,甚至更大,所以RST引脚又接收到高电平。单片机系统自动复位。 总结: 1、复位电路的原理是单片机RST引脚接收到2US以上的电平信号,只要保证电容的充放电时间大于2US,即可实现复位,所以电路中的电容值是可以改变的。 2、按键按下系统复位,是电容处于一个短路电路中,释放了所有的电能,电阻两端的电压增加引起的。

单片机各种复位电路原理

单片机各种复位电路原理 复位电路的作用 在上电或复位过程中,控制CPU的复位状态:这段时间内让CPU保持复位状态,而不是 一上电或刚复位完毕就工作,防止CPU发出错误的指令、执行错误操作,也可以提高电磁 兼容性能。 无论用户使用哪种类型的单片机,总要涉及到单片机复位电路的设计。而单片机复位电路设 计的好坏,直接影响到整个系统工作的可靠性。许多用户在设计完单片机系统,并在实验室调试成功后,在现场却出现了“死机”、“程序走飞”等现象,这主要是单片机的复位电路设计不可 靠引起的。 基本的复位方式 单片机在启动时都需要复位,以使CPU及系统各部件处于确定的初始状态,并从初态开始 工作。89系列单片机的复位信号是从RST引脚输入到芯片内的施密特触发器中的。当系统处于正常工作状态时,且振荡器稳定后,如果RST引脚上有一个高电平并维持2个机器周期(24个振荡周期)以上,则CPU就可以响应并将系统复位。单片机系统的复位方式有:手动按钮复位和上电复位 1、手动按钮复位 手动按钮复位需要人为在复位输入端RST上加入高电平(图1)。一般采用的办法是在RST 端和正电源Vcc之间接一个按钮。当人为按下按钮时,则Vcc的+5V电平就会直接加到RST端。手动按钮复位的电路如所示。由于人的动作再快也会使按钮保持接通达数十毫秒, 所以,完全能够满足复位的时间要求。

图1 图2 2 、上电复位 AT89C51 的上电复位电路如图 2 所示,只要在RST 复位输入引脚上接一电容至Vcc 端,下接一个电阻到地即可。对于CMOS 型单片机,由于在RST 端内部有一个下拉电阻,故可将外部电阻去掉,而将外接电容减至1μF。上电复位的工作过程是在加电时,复位电路通 过电容加给RST 端一个短暂的高电平信号,此高电平信号随着Vcc 对电容的充电过程而 逐渐回落,即RST 端的高电平持续时间取决于电容的充电时间。为了保证系统能够可靠地 复位,RST 端的高电平信号必须维持足够长的时间。上电时,Vcc 的上升时间约为10ms ,而振荡器的起振时间取决于振荡频率,如晶振频率为10MHz ,起振时间为1ms ;晶振频率为1MHz ,起振时间则为10ms 。在图 2 的复位电路中,当Vcc 掉电时,必然会使RST 端电压迅速下降到0V 以下,但是,由于内部电路的限制作用,这个负电压将不会对器件产生 损害。另外,在复位期间,端口引脚处于随机状态,复位后,系统将端口置为全“l态”。如果系统在上电时得不到有效的复位,则程序计数器PC 将得不到一个合适的初值,因此,CPU 可能会从一个未被定义的位置开始执行程序。 2 、积分型上电复位 常用的上电或开关复位电路如图 3 所示。上电后,由于电容C3 的充电和反相门的作用,使RST 持续一段时间的高电平。当单片机已在运行当中时,按下复位键K 后松开,也能使RST 为一段时间的高电平,从而实现上电或开关复位的操作。 根据实际操作的经验,下面给出这种复位电路的电容、电阻参考值。 图3 中:C:=1uF ,Rl=lk ,R2=10k

80C51单片机引脚图及引脚功能介绍

80C51单片机引脚图及引脚功能介绍 首先我们来介绍一下单片机的引脚图及引脚功能(如下图所示),引脚的具体功能将在下面详细介绍 单片机的40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。 ⒈ 电源: ⑴ VCC - 芯片电源,接+5V; ⑵ VSS - 接地端; ⒉ 时钟:

XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。 ⒊ 控制线:控制线共有4根, ⑴ ALE/PROG:地址锁存允许/片内EPROM编程脉冲 ① ALE功能:用来锁存P0口送出的低8位地址 ② PROG功能:片内有EPROM的芯片,在EPROM 编程期间,此引脚输入编程脉冲。 ⑵ PSEN:外ROM读选通信号。 ⑶ RST/VPD:复位/备用电源。 ① RST(Reset)功能:复位信号输入端。 ② VPD功能:在Vcc掉电情况下,接备用电源。 ⑷ EA/Vpp:内外ROM选择/片内EPROM编程电源。 ① EA功能:内外ROM选择端。 ② Vpp功能:片内有EPROM的芯片,在EPROM 编程期间,施加编程电源Vpp。 ⒋ I/O线

80C51共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。 P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。 拿到一块单片机,想要使用它,首先必须要知道怎样去连线,我们用的一块89C51的芯片为例,我们就看一下如何给它连线。 1、电源:这当然是必不可少的了。单片机使用的是5V电源,其中正极接40管脚,负极(地)接20管脚。 2、振蒎电路:单片机是一种时序电路,必须供给脉冲信号才能正常工作,在单片机内部已集成了振荡器,使用晶体振荡器,接18、19脚。只要买来晶体震荡器,电容,连上就能了,按图1接上即可。 3、复位管脚:按图1中画法连好,至于复位是何含义及为何需要复要复位,在单片机功能中介绍。 4、 EA管脚:EA管脚接到正电源端。至此,一个单片机就接好,通上电,单片机就开始工作了。

单片机各个引脚功能概述

单片机引脚,单片机引脚是什么意思 8051单片机引脚功能介绍 首先我们来连接一下单片机的引脚图,如果,具体功能在下面都有介绍。 单片机的40个引脚大致可分为4类:电源、时钟、控制和I/O引脚。 ⒈ 电源: ⑴ VCC - 芯片电源,接+5V; ⑵ VSS - 接地端; ⒉ 时钟:XTAL1、XTAL2 - 晶体振荡电路反相输入端和输出端。 ⒊ 控制线:控制线共有4根, ⑴ ALE/PROG:地址锁存允许/片内EPROM编程脉冲 ① ALE功能:用来锁存P0口送出的低8位地址 ② PROG功能:片内有EPROM的芯片,在EPROM编程期间,此引脚输入编程脉冲。 ⑵ PSEN:外ROM读选通信号。 ⑶ RST/VPD:复位/备用电源。 ① RST(Reset)功能:复位信号输入端。 ② VPD功能:在Vcc掉电情况下,接备用电源。 ⑷ EA/Vpp:内外ROM选择/片内EPROM编程电源。 ① EA功能:内外ROM选择端。 ② Vpp功能:片内有EPROM的芯片,在EPROM编程期间,施加编程电源Vpp。 ⒋ I/O线 80C51共有4个8位并行I/O端口:P0、P1、P2、P3口,共32个引脚。P3口还具有第二功能,用于特殊信号输入输出和控制信号(属控制总线)。

〈51单片机引脚图及引脚功能〉 拿到一块芯片,想要使用它,首先必须要知道怎样连线,我们用的一块称之为89C51的芯片,下面我们就看一下如何给它连线。 1、电源:这当然是必不可少的了。单片机使用的是5V电源,其中正极接40管脚,负极(地)接20管脚。 2、振蒎电路:单片机是一种时序电路,必须供给脉冲信号才能正常工作,在单片机内部已集成了振荡器,使用晶体振荡器,接18、19脚。只要买来晶体震荡器,电容,连上就能了,按图1接上即可。 3、复位管脚:按图1中画法连好,至于复位是何含义及为何需要复要复位,在单片机功能中介绍。 4、 EA管脚:EA管脚接到正电源端。至此,一个单片机就接好,通上电,单片机就开始工作了。 我们的第一个任务是要用单片机点亮一只发光二极管LED,显然,这个LED必须要和单片机的某个管脚相连,不然单片机就没法控制它了,那么和哪个管脚相连呢?单片机上除了刚才用掉的5个管脚,还有35个,我们将这个LED和1脚相连。(见图1,其中R1是限流电阻) 按照这个图的接法,当1脚是高电平时,LED不亮,只有1脚是低电平时,LED 才发亮。因此要1脚我们要能够控制,也就是说,我们要能够让1管脚按要求变为高或低电平。即然我们要控制1脚,就得给它起个名字,总不能就叫它一脚吧?叫它什么名字呢?设计51芯片的INTEL公司已经起好了,就叫它P1.0,这是规定,不能由我们来更改。

MSP430系列单片机复位电路系统设计分析及JTAG烧录不进程序的解决方法

去掉,或者减小RST引脚上的电容。因为电容太大了编程器无法复位430。因此检测失败。如果仍未解决,可能还是你的引脚连接有问题。 没找到芯片。如果电脑---仿真器----MSP430芯片的电气连接是正确可靠,没接触不良的话, 可能的情况有: 外部复位芯片复位引脚直接连至单片机引脚; 并口仿真器中BIOS参数设置不正确; 3.3V负载大,电路板没上电烧写; 芯片引脚或电路板有短路、断路问题; USB-JTAG未能成功启动、运行; 单片机熔丝烧过了或坏了; MSP430系列单片机复位电路系统设计分 析 2010年11月04日 10:59 本站整理作者:佚名用户评论(0) 关键字:MSP430(105)复位电(1) 0 引言 TI公司的混合信号处理器MSP430系列单片机以其处理能力强大、外围器件集成度高、功率消耗低、产品系列全面、全系列工业级等特点,作为目前MCU主流市场的产品之一,在电子应用领域中得到广泛应用,被越来越多的电子设计师所青睐。由于复位电路设计问题而导致的系统出现上电后不工作或状态不正确是很多MSP430单片机电路设计者们在设计、调试和应用中曾遇到过的问题,尽管这种情况发生的几率很低,但对于可靠性要求较高的应用场合,这个现象仍需引起电子设计人员的足够重视。 为此,本文对MSP430全系列单片机的复位系统和复位机制进行了详细深入的分析,并针对性地提出了具体的外围复位电路设计方案和有关电子元器件的详细介绍,以供同行参考和交流。 1 MSP430复位机制 1.1 MSP430复位电路 MSP430的复位电路包括一个上电复位(POR)和上电清除信号(PUC)。POR是设备复位信号,它通常在以下三种事件发生时被触发:a.上电;b.复位模式下RST/NMI脚出现低电平;c.电压监控设备(Brownout)触发。 POR时序见图1(a)所示。

51单片机主要引脚功能

51单片机主要引脚功能 XTAL1(19 脚)和XTAL2(18 脚)为振荡器输入输出端口,外接12MHz 晶振。 RST/Vpd(9 脚)为复位输入端口,外接电阻电容组成的复位电路。 VCC(40 脚)和VSS(20 脚)为供电端口,分别接+5V 电源的正负端。 P0~P3 为可编程通用I/O 脚,其功能用途由软件定义 P0 口:P0 口是一组8 位漏极开路型双向I/O 口,也即地址/数据总线复用口。作为输出口用时,每位能吸收电流的方式驱动8 个TTL 逻辑门电路,对端口P0 写1 时,可作为高阻抗输入端用。在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8 位)和数据总线复用,在访问期间激活内部上拉电阻。在Flash 编程时,P0 口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。 P1 口:P1 是一个带内部上拉电阻的8 位双向I/O 口,P1 的输出缓冲级可驱动(吸收或输出电流)4 个TTL 逻辑门电路。对端口写1,通过内部的上拉电阻把端口拉到高电平,此时可作输入口。作输入口使用时,因为内部存在 上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL)。 P2 口:P2 是一个带有内部上拉电阻的8 位双向I/O 口,P2 的输出缓冲级可驱动(吸收或输出电流)4 个TTL 逻辑门电路。对端口P2 写1,通过内部的上拉电阻把端口拉到高电平,此时可作输入口,作输入口使用时,因为内 部存在上拉电阻,某个引脚被外部信号拉低时会输出一个电流(IIL)。 P3 口:P3 口是一组带有内部上拉电阻的8 位双向I/O 口。P3 口输出缓冲级可驱动(吸收或输出电流)4 个TTL 逻辑门电路。对P3 口写入1 时,它

单片机复位电路设计

单片机复位电路设计 :blog.sina.. /s/blog_4b7b591401000ai0.html 一、概述 影响单片机系统运行稳定性的因素可大体分为外因和内因两部分: 1、外因 射频干扰,它是以空间电磁场的形式传递在机器内部的导体(引线或零件引脚)感生出相应的干扰,可通过电磁屏蔽和合理的布线/器件布局衰减该类干扰; 电源线或电源内部产生的干扰,它是通过电源线或电源内的部件耦合或直接传导,可通过电源滤波、隔离等措施来衰减该类干扰。 2、内因 振荡源的稳定性,主要由起振时间频率稳定度和占空比稳定度决定起振时间可由电路参数整定稳定度受振荡器类型温度和电压等参数影响复位电路的可靠性。 二、复位电路的可靠性设计 1、基本复位电路 复位电路的基本功能是:系统上电时提供复位信号,直至系统电源稳定后,撤销复位信号。为可靠起见,电源稳定后还要经一定的延时才撤销复位信号,以防电源开关或电源插头分-合过程中引起的抖动而影响复位。图1所示的RC复位电路可以实现上述基本功能,图3为其输入-输出特性。但解决不了电源毛刺(A 点)和电源缓慢下降(电池电压不足)等问题而且调整RC 常数改变延时会令驱动

能力变差。左边的电路为高电平复位有效右边为低电平Sm为手动复位开关Ch 可避免高频谐波对电路的干扰调频FM发射话筒制作套件 图1RC复位电路 图2所示的复位电路增加了二极管,在电源电压瞬间下降时使电容迅速放电,一定宽度的电源毛刺也可令系统可靠复位。图3所示复位电路输入输出特性图的下半部分是其特性,可与上半部比较增加放电回路的效果电子元件邮购 图2增加放电回路的RC复位电路 使用比较电路,不但可以解决电源毛刺造成系统不稳定,而且电源缓慢下降也能可靠复位。图4 是一个实例当VCC x (R1/(R1+R2) ) = 0.7V时,Q1截止使系统复

80C51单片机的上电复位POR

80C51单片机的上电复位POR(Pmver On Reset)实质上就是上电延时复位,也就是在上电延时期间把单片机锁定在复位状态上。为什么在每次单片机接通电源时,都需要加入一定的延迟时间呢?分析如下。 1 上电复位时序 在单片机及其应用电路每次上电的过程中,由于电源同路中通常存在一些容量大小不等的滤波电容,使得单片机芯片在其电源引脚VCC和VSS之间所感受到的电源电压值VDD,是从低到高逐渐上升的。该过程所持续的时间一般为1~100ms(记作 tsddrise)。上电延时taddrise的定义是电源电压从lO%VDD上升到90%VDD所需的时间,如图1所示。 在单片机电源电压上升到适合内部振荡电路运行的范围并且稳定下来之后,时钟振荡器开始了启动过程(具体包括偏置、起振、锁定和稳定几个过程)。该过程所持续的时间一般为1~50 ms(记作tOSC)。起振延时tOSC的定义是时钟振荡器输出信号的高电平达到Vih1所需的时间。从图1所示的实际测量图中也可以看得很清楚。这里的 Vih1是单片机电气特性中的一个普通参数,代表XTALl和RST引脚上的输入逻辑高电平。例如,对于常见的单片机型号AT89C5l和 AT89S5l,厂家给出的Vih1值为0.7VDD~VDD+0.5V。 从理论上讲,单片机每次上电复位所需的最短延时应该不小于treset。这里,treset等于上电延时taddrise与起振延时tOSC之和,如图1所示。从实际上讲,延迟一个treset往往还不够,不能够保障单片机有--一个良好的工作开端。 在单片机每次初始加电时,首先投入工作的功能部件是复位电路。复位电路把单片机锁定在复位状态上并且维持一个延时(记作TRST),以便给予电源电压从上升到稳定的一个等待时间;在电源电压稳定之后,再插入一个延时,给予时

at89c51引脚图及功能

at89c51引脚图及功能 AT89C51是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4k bytes的可反复擦写的只读程序存储器(PEROM)和128 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。 主要性能参数: ·与MCS-51产品指令系统完全兼容·4k字节可重擦写Flash闪速存储器·1000次擦写周期 ·全静态操作:0Hz-24MHz ·三级加密程序存储器·128×8字节内部RAM ·32个可编程I/O口线·2个16位定时/计数器·6个中断源 ·可编程串行UART通道·低功耗空闲和掉电模式 功能特性概述: AT89C51提供以下标准功能:4k字节Flash闪速存储器,128字节内部RAM,32个I/O口线,两个16位定时/计数器,一个5向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。同时,AT89C51可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。 ·P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口。作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口写“1”可作为高阻抗输入端用。 在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。 在FIash编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。 ·P1口:P1是一个带内部上拉电阻的8位双向I/O口,P1的输出缓冲级可驱

单片机延时程序

实验一单片机延时程序实验 一、实验目的与要求: 在使用4MH在外部晶体振荡器的PIC16F877A上用软件设计一个20ms的软件延时子程序。另外,还要求用MPLAB的软件模拟器及其附带的软件工具窗口stopwatch观测延时程序执行的时间。 二、实验内容: 1.硬件电路设计: 本实验中用的是软件延时,利用循环来实现延时功能。电路就用了单片机的原本电路。没有用到其他的功能模块,单片机与ICD3相连接。 2.软件设计思路: 单片机软件延时的前提和基础是每条指令的执行时间是固定的,且大部分指令的执行时间是相同的。这要求对每条指令所花费的指令周期(Tcy)做到心中有数。指令集中5条无条件跳转指令GOTO,CALL.RETURN,RETLW和RETFIE,由于它们必然引起程序跳转,造成流水线中断,因此肯定将占用2个指令周期。而其他4条有可能引起程序跳转的条件跳转指令DECFSZ,INCFSZ,BTFSC和,BTFSS的执行时间,需要占用2个指令周期,当条件为假不发生跳转时,仅占用1个指令周期。其余所有指令都只用1个指令周期。

每个指令周期Tcy的时间长度,计算方法:如果采用4MHz 的外部晶体(fosc=4 MHz),则PIC中档单片机的指令周期Tcy 为1us,这是一个整数。而采用其他频率的外部晶体时,指令周期时间将反比于外部晶体频率。 至于软件延时的结构和实现方法,其实可以采用任何指令和结构,因为只是通过执行指令耗费时间。但通常情况下有两个选择延时程序结构的原则: (1)执行指令周期数计算方便。如果含有太多复杂的条件跳转循环等结构势必会造成指令周期的计算困难,甚至可 能造成执行所造成的软件延时时间不等。 (2)不能占用太多的程序空间。试想用20000个NOP指令来实现20ms的延时,显然是可以的,但是这样做浪费了 整整一个页的程序存储器,得不偿失,而通过适当的循 环结构,重复执行某些相同的程序是比较合理的方法。 因此,软件延时程序一般采用下列方法:如果延时时间 短(微妙级别),可以连续插入几条NOP指令;如果延 时时间长(几个毫秒级别),则可以使用双嵌套循环的 方法来实现。 实验的流程图:

单片机复位电路

单片机在启动运行时都需要复位,复位使CPU 和系统中的其他部件都处于一个确定的工作状态,并从这个状态开始工作。在系统中,有时也会出现显示不正常,也为了调试方便,需要设计一个复位电路,复位电路主要完成系统的上电复位和系统在运行时用户的按键复位功能。 在此系统中单片机的复位靠外部电路实现的,AT89C51单片机有一个复位引脚RST ,高电平有效。只要RST 保持高电平,单片机便保持复位状态。此时,ALE/PSEN 、P0、P1、P2、P3口都输出高电平。RST 变成低电平后,退出复位状态,CPU 开始正常工作。需要注意的是,复位操作不影响片内RAM 的内容。 复位电路的基本功能是系统上电时提供复位信号,直至系统电源稳定后,撤销复位信号。图1为基本RC 复位电路,其电路为高电平复位有效, SW1为手动复位开关,可以实现上述基本功能。 图1基本RC 复位电路 对于图1中的电阻10R 两端的电压R u (即复位信号)是一个时间的函数。上电复位时R u 和t 有以下函数关系,波形图如图2(a )所示。 ) 2.2.3(V u C R R 10a e cc t - ?= 按键复位时设t 在0~0t 之间时SW1合上,t 0t ≥ 时,SW1断开,则R u 和t 有以下函数关系,波形图如图2(b )所示。 ) 2.2.3()1(0)1(2 1 0110 11010 110b t t e e V R R R t t e V R R R u o t t CC o t CC R ????? ??≥-+<<-+=- --τττ 其中,C R //1011?=R τ,C R 102?=τ,Vcc 为电源电压(+5V )。

单片机常用复位电路

单片机复位电路设计 一、概述 影响单片机系统运行稳定性的因素可大体分为外因和内因两部分: 1、外因 射频干扰,它是以空间电磁场的形式传递在机器内部的导体(引线或零件引脚)感生出相应的干扰,可通过电磁屏蔽和合理的布线/器件布局衰减该类干扰; 电源线或电源内部产生的干扰,它是通过电源线或电源内的部件耦合或直接传导,可通过电源滤波、隔离等措施来衰减该类干扰。 2、内因 振荡源的稳定性,主要由起振时间频率稳定度和占空比稳定度决定。起振时间可由电路参数整定稳定度受振荡器类型温度和电压等参数影响复位电路的可靠性。 二、复位电路的可靠性设计 1、基本复位电路 复位电路的基本功能是:系统上电时提供复位信号,直至系统电源稳定后,撤销复位信号。为可靠起见,电源稳定后还要经一定的延时才撤销复位信号,以防电源开关或电源插头分-合过程中引起的抖动而影响复位。图1所示的RC复位电路可以实现上述基本功能,图3为其输入-输出特性。但解决不了电源毛刺(A 点)和电源缓慢下降(电池电压不足)等问题而且调整 RC 常数改变延时会令驱动能力变差。左边的电路为高电平复位有效右边为低电平 Sm为手动复位开关Ch 可避免高频谐波对电路的干扰。

图1 RC复位电路 图2所示的复位电路增加了二极管,在电源电压瞬间下降时使电容迅速放电,一定宽度的电源毛刺也可令系统可靠复位。图3所示复位电路输入输出特性图的下半部分是其特性,可与上半部比较增加放电回路的效果 图2 增加放电回路的RC复位电路 使用比较电路,不但可以解决电源毛刺造成系统不稳定,而且电源缓慢下降也能可靠复位。图4 是一个实例当 VCC x (R1/(R1+R2) ) = 0.7V时,Q1截止使系统复位。Q1的放大作用也能改善电路的负载特性,但跳变门槛电压 Vt 受 VCC 影响是该电路的突出缺点,使用稳压二极管可使 Vt 基本不受VCC影响。见图5,当VCC低于Vt(Vz+0.7V)时电路令系统复位。 图3 RC复位电路输入-输出特性

单片机上电复位

80C51单片机的上电复位POR 80C51单片机的上电复位POR(Power On Reset)实质上就是上电延时复位,也就是在上电延时期间把单片机锁定在复位状态上。为什么在每次单片机接通电源时,都需要加入一定的延迟时间呢?分析如下。 1 上电复位时序 在单片机及其应用电路每次上电的过程中,由于电源回路中通常存在一些容量大小不等的滤波电容,使得单片机芯片在其电源引脚VCC和VSS之间所感受到的电源电压值VDD,是从低到高逐渐上升的。该过程所持续的时间一般为1~100ms(记作taddrise)。上电延时taddrise的定义是电源电压从10% VDD 上升到90% VDD所需的时间,如图1所示。 图1 上电延时taddrise和起振延时tosc实测结果 在单片机电源电压上升到适合内部振荡电路运行的范围并且稳定下来之后,时钟振荡器开始了启动过程(具体包括偏置、起振、锁定和稳定几个过程)。该过程所持续的时间一般为1~50 ms(记作tosc)。起振延时tosc的定义是时钟振荡器输出信号的高电平达到Vih1所需的时间。从图1所示的实际测量图中也可以看得很清楚。这里的Vih1是单片机电气特性中的一个普通参数,代表XTAL1和RST引脚上的输入逻辑高电平。例如,对于常见的单片机型号AT89C51和AT89S51,厂家给出的Vih1值为0.7VDD~VDD+0.5 V。

从理论上讲,单片机每次上电复位所需的最短延时应该不小于treset。这里,treset等于上电延时taddrise与起振延时tosc之和,如图1所示。从实际上讲,延迟一个treset往往还不够,不能够保障单片机有一个良好的工作开端。 在单片机每次初始加电时,首先投入工作的功能部件是复位电路。复位电路把单片机锁定在复位状态上并且维持一个延时(记作TRST),以便给予电源电压从上升到稳定的一个等待时间;在电源电压稳定之后,再插入一个延时,给予时钟振荡器从起振到稳定的一个等待时间;在单片机开始进入运行状态之前,还要至少推迟2个机器周期的延时,如图2所示。 图2 复位信号释放的时机 2 上电复位电路3款 上述一系列的延时,都是利用在单片机RST引脚上外接一个RC支路的充电时间而形成的。典型复位电路如图3(a)所示,其中的阻容值是原始手册中提供的。在经历了一系列延时之后,单片机才开始按照时钟源的工作频率,进入到正常的程序运行状态。从图2所示的实测曲线中可以同时看到4条曲线:VDD、Vrst、XTAL2和ALE。在电源电压以及振荡器输出信号稳定之后,又等待了一段较长的延时才释放RST信号,使得CPU脱离复位锁定状态;而RST 信号一旦被释放,立刻在ALE引脚上就可检测到持续的脉冲信号。

AT89C51引脚全部和功能

AT89C51单片机简介 AT89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。AT89C2051是一种带2K字节闪烁可编程可擦除只读存储器的单片机。单片机的可擦除只读存储器可以反复擦除100次。该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL 的AT89C51是一种高效微控制器,AT89C2051是它的一种精简版本。AT89C单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。

1.主要特性: ·与MCS-51 兼容 ·4K字节可编程闪烁存储器 寿命:1000写/擦循环 数据保留时间:10年 ·全静态工作:0Hz-24Hz ·三级程序存储器锁定 ·128*8位内部RAM ·32可编程I/O线 ·两个16位定时器/计数器 ·5个中断源 ·可编程串行通道 ·低功耗的闲置和掉电模式 ·片内振荡器和时钟电路 2.管脚说明: VCC:供电电压。 GND:接地。 P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P1口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。

在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。 P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。 P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。 P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。 P3口也可作为AT89C51的一些特殊功能口,如下表所示:

51单片机复位电路的设计

51单片机复位电路的设计- 懵懂者的日志- 网易博客(转载) 大白菜的书馆收藏 于 2011-11-12 阅读 数:1 被转藏: 1 公众 公开 原文 来源 修改如何标记批注? 51单片机复位电路的设计 默认分类2009-10-12 10:05:16 阅读1955 评论1 字号:大中小订阅 单片机在可靠的复位之后,才会从0000H地址开始有序的执行应用程序。同时,复位电路也是容易受到外部噪声干扰的敏感部分之一。因此,复位电路应该具有两个主要的功能: 1. 必须保证系统可靠的进行复位; 2. 必须具有一定的抗干扰的能力; 一、复位电路的RC选择 复位电路应该具有上电复位和手动复位的功能。以MCS-51单片机为例,复位脉冲的高电平宽度必须大于2个机器周期,若系统选用6MHz晶振,则一个机器周期为2us,那么复位脉冲宽度最小应为4us。在实际应用系统中,考虑到电源的稳定时间,参数漂移,晶振稳定时间以及复位的可靠性等因素,必须有足够的余量。图1是利用RC充电原理实现上电复位的电路设计。实践证明,上电瞬间RC电路充电,RESET引脚出现正脉冲。只要RESET端保持10ms以上的高电平,就能使单片机有效的复位。 图1 对于图1-a中的电容C两端的电压(即复位信号)是一个时间的函数:

u(t)=VCC*[1-exp(-t/RC)] 对于图1-b中的电阻R两端的电压(即复位信号)也是一个时间的函数: u(t)=VCC*exp(-t/RC) 其中的VCC为电源电压,RC为RC电路的时间常数=1K*22uF=22ms。有了这个公式,我们可以更方便的对以上电路进行透彻的分析。 图1-a中非门的最小输入高电平UIH=2.0v,当充电时间t=0.6RC时,则充电电压u(t)=0.45VCC=0.45*5V,约等于2V,其中t即为复位时间。图a中时间常数=22ms,则t=22ms*0.6=13ms。 二、复位电路的可靠性与抗干扰性分析 单片机复位电路端口的干扰主要来自电源和按钮传输线串入的噪声。这些噪声虽然不会完全导致系统复位,但有时会破坏CPU内的程序状态字的某些位的状态,对控制产生不良影响。 1.电路结构形式与抗干扰性能 以图1为例,电源噪声干扰过程示意图如图2种分别绘出了A点和B点的电压扰动波形。 有图2可以看出,图2(a)实质上是个低通滤波环节,对于脉冲宽度小于3RC的干扰有很好的抑制作用;图2(b)实质上是个高通滤波环节,对脉冲干扰没有抑制作用。由此可见,对于图1所示的两种复位电路,a的抗干扰电源噪声的能力要优于b。 2. 复位按钮传输线的影响 复位按钮一般都是安装在操作面板上,有较长的传输线,容易引起电磁感应干扰。按钮传输线应采用双绞线(具有抑制电磁感应干扰的性能),并远离交流用电设备。在印刷电路板上,单片机复位端口处并联0.01-0.1uF的高频电容,或配置使密特电路,将提高对串入噪声的抑制能力。