加法器设计--数字逻辑电路(电子科技大学)

《课程设计—加减法器》报告

电工17班王兴2011029170010

1.分析及设计方法:

要设计4位的全加全减器,首先要设计一位的全加器。一位的全加器,需要3个输入,相加数A和B,还有进位输入Cin,2个输出,相加后的值S和进位输出Cout。考虑到有一个控制端Addsub,所以要加一个输入。然后考虑加法器转换为减法器。转化方法为:将减数B取反,然后进位输入Cin变为1,再进行加法运算。设计好1为的全加全减器后进行封装。然后用四个全加全减单元串联组成四位全加全减器。

然后关于控制端Sel ,只需用一个二选一的Mux,选择A或Z。

溢出的判断,不论是加法还是减法,在转化为加法运算后。判断依据:两相加数符号相同,运算结果符号不同,则发生溢出。

2.电路设计:

设计软件:Quartus II 8.1

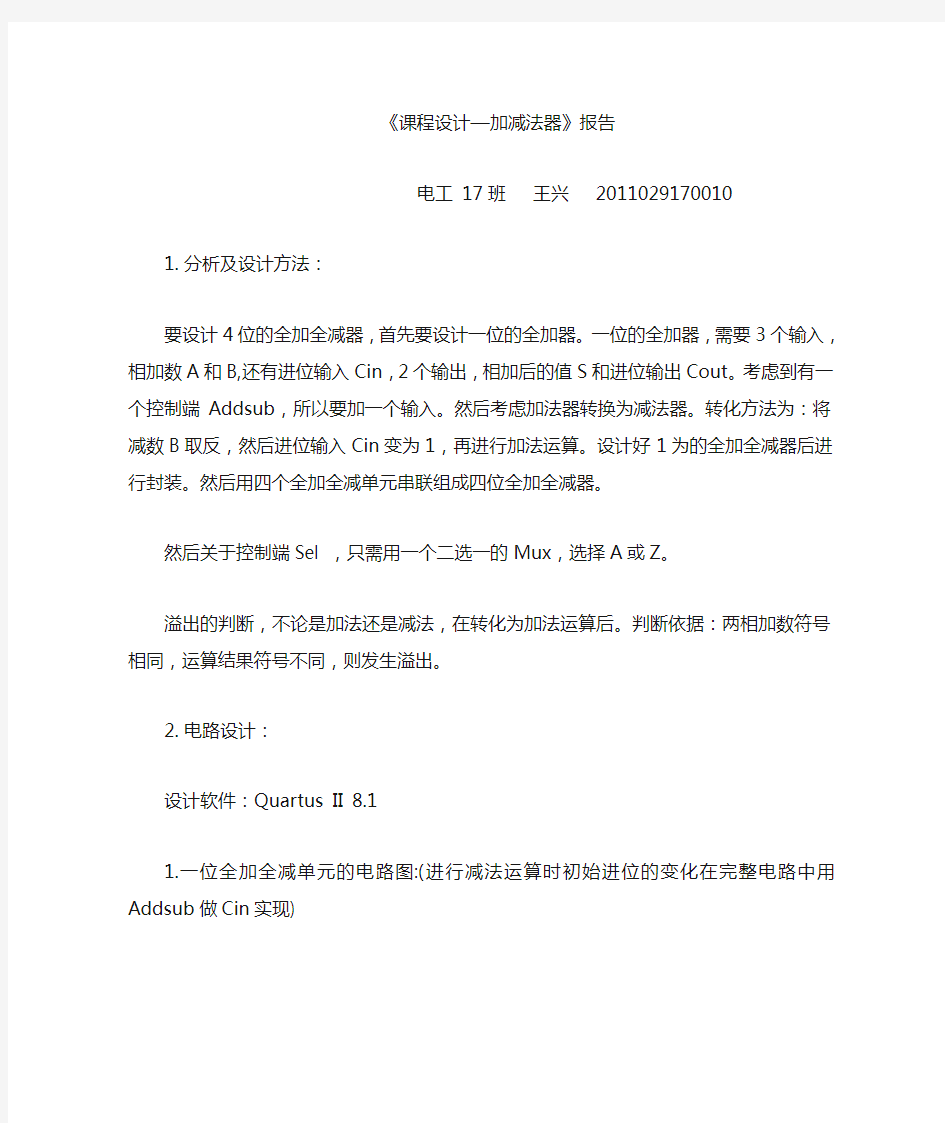

1.一位全加全减单元的电路图:(进行减法运算时初始进位的变化在完整电

路中用Addsub做Cin实现)

封装后:

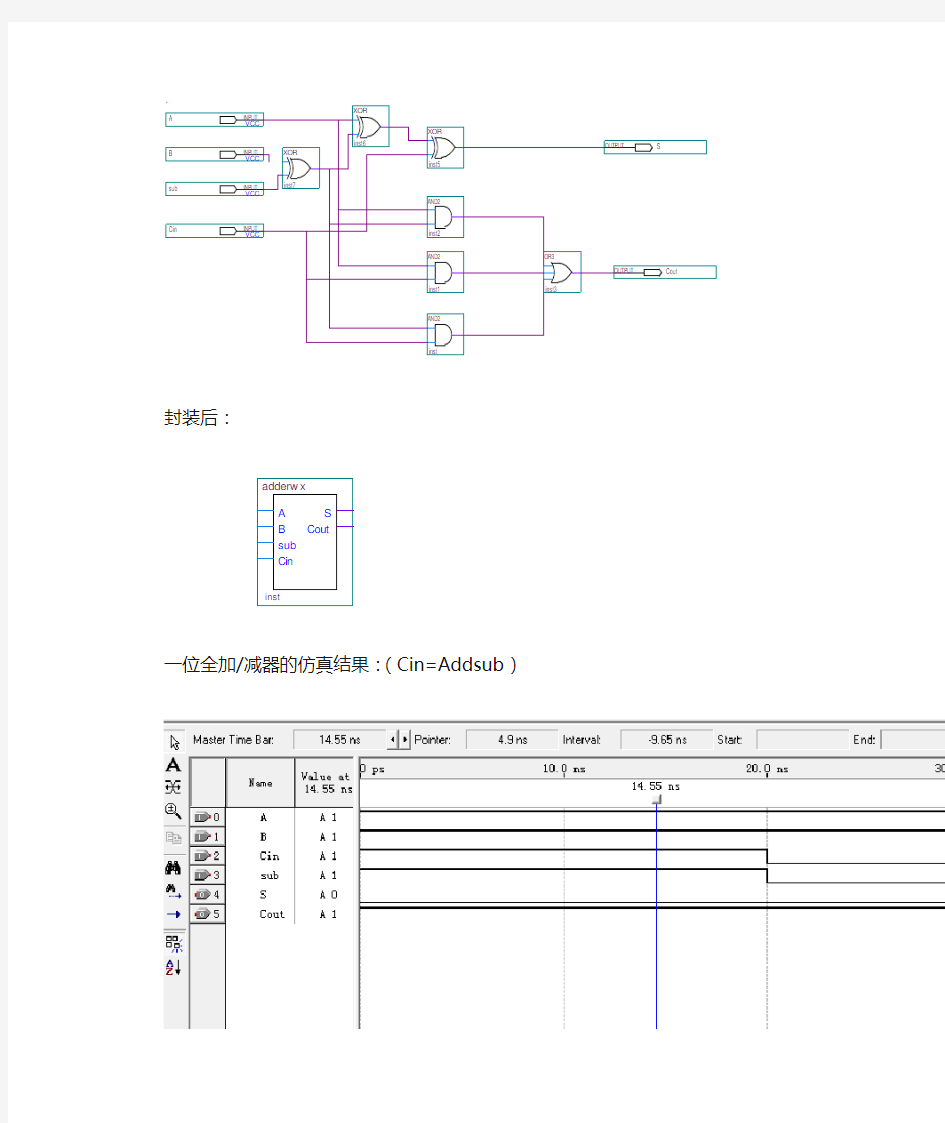

一位全加/减器的仿真结果:(Cin=Addsub)

2.Sel控制端的实现电路:

封装后:

3.判断溢出的实现电路:

封装后:

4.完整电路图:

电子科技大学期末数字电子技术考试题a卷-参考答案教学内容

电子科技大学二零零九至二零一零学年第 二 学期期 末 考试 数字逻辑设计及应用 课程考试题 A 卷(120分钟)考试形式:闭卷 考试日期2010年7月12日 课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末 60 分 一、To fill your answers in the blanks (1’×25) 1. If [X]10= - 110, then [X]two's-complement =[ 10010010 ]2, [X]one's-complement =[ 10010001 ]2. (Assumed the number system is 8-bit long) 2. Performing the following number system conversions: A. [10101100]2=[ 000111010010 ]2421 B. [1625]10=[ 0100100101011000 ]excess-3 C. [ 1010011 ]GRAY =[ 10011000 ]8421BCD 3. If ∑=C B A F ,,)6,3,2,1(, then F D ∑=C B A ,,( 1,4,5,6 )=C B A ,,∏(0,2,3,7 ). 4. If the parameters of 74LS-series are defined as follows: V OL max = 0.5 V , V OH min = 2.7 V , V IL max = 0.8 V , V IH min = 2.0 V , then the low-state DC noise margin is 0.3V ,the high-state DC noise margin is 0.7V . 5. Assigning 0 to Low and 1 to High is called positive logic. A CMOS XOR gate in positive logic is called XNOR gate in negative logic. 6. A sequential circuit whose output depends on the state alone is called a Moore machine. 7. To design a "001010" serial sequence generator by shift registers, the shift register should need 4 bit as least. 8. If we use the simplest state assignment method for 130 sates, then we need at least

组合逻辑电路的设计题目

1、在一旅游胜地,有两辆缆车可供游客上下山,请设计一个控制缆车正常运行的逻辑电路。要求:缆车A和B在同一时刻只能允许一上一下的行驶,并且必须同时把缆车的门关好后才能行使。设输入为A、B、C,输出为Y。(设缆车上行为“1”,门关上为“1”,允许行驶为“1”) (1) 列真值表;(4分) (2)写出逻辑函数式;(3分) (3)用基本门画出实现上述逻辑功能的逻辑电路图。(5分) 解:(1)列真值表:(3)逻辑电路图: A B C Y 000 001 010 011 100 101 110 111 (2)逻辑函数式: 2、某同学参加三类课程考试,规定如下:文化课程(A)及格得2分,不及格得0分;专业理论课程(B)及格得3分,不及格得0分;专业技能课程(C)及格得5分,不及格得0分。若总分大于6分则可顺利过关(Y),试根据上述内容完成: (1)列出真值表; (2)写出逻辑函数表达式,并化简成最简式; (3)用与非门画出实现上述功能的逻辑电路。 (3)逻辑电路图 A B C Y 000 001 010 011 100 101 110 111 (2)逻辑函数表达式3、中等职业学校规定机电专业的学生,至少取得钳工(A)、车工(B)、电工(C)中级技能证书的任意两种,才允许毕业(Y)。试根据上述要求:(1)列出真值表;(2)写出逻辑表达式,并化成最简的与非—与非形式;(3)用与非门画出完成上述功能的逻辑电路。 解:(1(3)逻辑电路: A B C Y 000 001 010 011 100 101 110 111 (2)逻辑表达式: 最简的与非—与非形式: 4、人的血型有A、B、AB和O型四种,假定输血规则是:相同血型者之间可输出,AB血型者可接受其他任意血型,任意血型者可接受O型血。图1是一个输血判断电路框图,其中A1A0表示供血者血型,B1B0表示受血者型,现分别用00、01、10和11表示A、B、AB和O四种血型。Y 为判断结果,Y=1表示可以输血,Y=0表示不允许输血。请写出该判断电路的真值表、最简与—或表达式,并画出用与非门组成的逻辑图。 输血判断电路框图: 解:(1)真值表:(3)逻辑图: 输入输出 A1A0B1B0Y 0000 0001 0010 0011

组合逻辑电路设计之全加器半加器

班级姓名学号 实验二组合电路设计 一、实验目的 (1)验证组合逻辑电路的功能 (2)掌握组合逻辑电路的分析方法 (3)掌握用SSI小规模集成器件设计组合逻辑电路的方法 (4)了解组合逻辑电路集中竞争冒险的分析和消除方法 二、实验设备 数字电路实验箱,数字万用表,74LS00, 74LS86 三、实验原理 1 ?组合逻辑概念 通常逻辑电路可分为组合逻辑电路和时序逻辑电路两大类。组合逻辑电路又称组合电路,组合电路的输出只决定于当时的外部输入情况,与电路的过去状态无关。因此,组合电路的 特点是无“记忆性”。在组成上组合电路的特点是由各种门电路连接而成,而且连接中没有反馈线存在。所以各种功能的门电路就是简单的组合逻辑电路。 组合电路的输入信号和输出信号往往不只一个,其功能描述方法通常有函数表达式、真值表,卡诺图和逻辑图等几种。 实验中用到的74LS00和74LS86的引脚图如图所示。 00 四2输入与非门 4B 4A 4Y 3B 3A 3Y 1A 1B 1Y 2A 2B 2Y GND 2?组合电路的分析方法。 组合逻辑电路分析的任务是:对给定的电路求其逻辑功能,即求出该电路的输出与输入之间的关系,通常是用逻辑式或真值表来描述,有时也加上必须的文字说明。分析一般分为

(1)由逻辑图写出输出端的逻辑表达式,简历输入和输出之间的关系。 (2)列出真值表。 (3)根据对真值表的分析,确定电路功能。 3?组合逻辑电路的设计方法。 组合逻辑电路设计的任务是:由给定的功能要求,设计出相应的逻辑电路。 一般设计的逻辑电路的过程如图 (1)通过对给定问题的分心,获得真值表。在分析中要特别注意实际问题如何抽象为几个输入变量和几个 输出变量直接的逻辑关系问题,其输出变量之间是否存在约束关系,从而过得真值表或简化真值表。 (2)通过卡诺图化简或逻辑代数化简得出最简与或表达式,必要时进行逻辑式的变更,最后画出逻辑图。 (3)根据最简逻辑表达式得到逻辑电路图。 四?实验内容。 1?分析,测试半加器的逻辑功能。 (1 )用74LS00组成半加器电路如图所示。写出逻辑表达式,验证逻辑关系。 (2 )用异或门74LS86和74LS00组成半加器,自己画出电路,将测试结果填入自拟表格中, 验证逻辑关系。 所以的卡诺图为:

电子科技大学模拟电路考试题及答案

电子科技大学 二零零七至二零零八学年第一学期期末考试 模拟电路基础课程考试题A卷(120分钟)考试形式:开卷 课程成绩构成:平时10分,期中30分,实验0分,期末60分 一(20分)、问答题 1.(4分)一般地,基本的BJT共射放大器、共基放大器和共集放大器的带宽哪个最大?哪个最小? 2.(4分)在集成运算放大器中,为什么输出级常用射极跟随器?为什么常用射极跟随器做缓冲级? 3.(4分)电流源的最重要的两个参数是什么?其中哪个参数决定了电流源在集成电路中常用做有源负载?在集成电路中采用有源负载有什么好处? 4.(4分)集成运算放大器为什么常采用差动放大器作为输入级? 5.(4分)在线性运算电路中,集成运算放大器为什么常连接成负反馈的形式?

二(10分)、电路如图1所示。已知电阻R S=0,r be=1kΩ,R1∥R2>>r be。 1.若要使下转折频率为10Hz,求电容C的值。 2.若R S≠0,仍保持下转折频率不变,电容C的值应该增加还是减小? 图1 三(10分)、电路如图2所示。已知差模电压增益为10。A点电压V A=-4V,硅三极管Q1和Q2的集电极电压V C1=V C2=6V,R C=10kΩ。求电阻R E和R G。 图2 四(10分)、电路如图3所示。已知三极管的β=50,r be=1.1kΩ,R1=150kΩ,R2=47k Ω,R3=10kΩ,R4=47kΩ,R5=33kΩ,R6=4.7kΩ,R7=4.7kΩ,R8=100Ω。 1.判断反馈类型; 2.画出A电路和B电路; 3.求反馈系数B; 4.若A电路的电压增益A v=835,计算A vf,R of和R if。

电子科大数字电路,期末试题0708-2半期考试

………密………封………线………以………内………答………题………无………效…… 电子科技大学二零零七至二零零八学年第二学期期中考试 “数字逻辑设计及应用”课程考试题 期中卷(120分钟)考试形式:闭卷 考试日期 2008年4月26日 课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末60 分 1-1.与十进制数 (0. 4375 )10 等值的二进制数表达是 ( A ) A. ( 0.0111 ) 2 B. ( 0.1001 ) 2 C. ( 0.0101 ) 2 D. ( 0.01101 ) 2 1-2. 与十六进制数(FD .A )16等值的八进制数是( A )8 A. ( 375.5 )8 B. ( 375.6 )8 C. ( 275.5 )8 D. ( 365.5)8 1-3.与二进制数(11010011) 2 对应的格雷码表达是 ( C ) Gray A. ( 11111010 ) Gray B. (00111010 ) Gray C. ( 10111010 )Gray D. (11111011 ) Gray 1-4.下列数字中与(34.42)8 相同 的是( B ) A.(011010.100101)2 B.(1 C.88)16 C.(27.56)10 D.(54.28)5 1-5.已知[A]补=(10010011),下列表达式中正确的是( C ) A. [–A]反=(01101100) B. [A]反=(10010100) C. [-A]原=(01101101) D. [A]原=(00010011) 1-6.一个十六路数据选择器,其选择控制输入端的数量为( A ) A .4个 B. 6个 C. 8个 D. 3个 1-7.四个逻辑相邻的最小项合并,可以消去( B )个因子。 A. ( 1 ) B. ( 2 ) C. ( 3 ) D.( 4 ) 1-8.设A 补=(1001),B 补=(1110),C 补=(0010),在下列4种补码符号数的运算中,最不可能产生溢出的是 ( D ) A. [A-C]补 B. [B-C]补 C. [A+B]补 D. [B+C]补 1-9.能够实现“线与”的CMOS 门电路叫( D ) A. ( 与门 ) B. ( 或门 ) C. (集电极开路门) D. (漏极开路门) 1-10.CMOS 三输入或非门的实现需要( C )个晶体管。 A. ( 2 ) B. ( 4 ) C. ( 6 ) D. ( 8 ) 1-11.三态门的三个输出状态分别为:逻辑“1”、逻辑“0”和( C ) A. (短路) B. ( 5V ) C. (高阻) D. ( 0.3V ) 1-12.与()x y xz ''+等价的逻辑关系为( D ) A. XYZ B. XY ’+XZ ’ C. XY ’+X ’Z ’ D. XY ’Z

电子科技大学网络教育专科C语言在线考试答案

一、单项选择题(每题2分,共30分) 1.以下描述正确的是( C ) A.goto语句只能用于退缩出多层循环。 B.switch语句中不能出现continue语句。 C.只能用continue语句中来终止本次循环。 D.在循环语句中break语句不独立出现。 2.一个C程序的执行是从( A ) A.C程序的main函数开始,到main函数结束。 B.本程序的第一个函数开始,到本程序最后一个函数结束。 C.本程序的main函数开始,到本程序文件的最后一个函数结束。 `D.本程序的第一个函数开始,到本程序main函数结束。 3.C语言中,要求运算数必须都是整数的运算符是( C )。 A.* B.- C.% D.+ 4.假定 int i=3,j=4; 执行语句: printf("%d,%d,%d\n",i+++j,i,j); 之后,其输出结果为:( C ) A.7,4,4 B. 8,4,4 C. 7,3,4 D.7,3,5 5.对break语句的正确描述。( A ) A.break语句在while语句中,立即终止执行while语句。 B.break语句不能用于循环语句之外的语句。 C.break语句与continue语句功能相同。 D.b reak语句可以带参数,也可以不带。 6.在C语言中,下面那一个不是正确的概念( A ) A. 所有循环语句都要求至少要执行一次循环体。 B. goto和if语句能构成循环语句。 C.循环过程只能包含,不能交叉。 D.循环体可以是一条语句。 7.以下对二维数组a的正确说明是( C ) A. int a[ 3 ] [ ]; B. float a( 3, 4); C. int a[ 3 ] [ 4 ] D.float a( 3, )( 4 ); 8.对函数的正确描述( C ) A.在C语言中可以嵌套定义函数。 B.自定义函数和调用函数可以不在一个源文件中。 C.函数定义都是平行的,独立的。 D.不能嵌套调用函数。 9.若用数组名作为函数调用的实参,传给形参的是( A ) A.数组的首地址 B.数组的第一个元素值 C.数组的全部元素值 D.数组中元素的个数 10.对于 int *p; int a[]; p=a; 的合法运算( C ) A. a++; B. p=a; p++; 相当于 a++; C. ++p; 相当于 a[1]; D.若p中的地址为100则p++; 运算后,则其值为100 11.假设int x[] = {1,3,5,7,9,11}, *ptr; ptr = x; 以下那些是对数组元素的正确引用 ( D )

组合逻辑电路设计心得体会

组合逻辑电路设计心得体会篇一:实验一_组合逻辑电路分析与设计 实验1 组合逻辑电路分析与设计 XX/10/2 姓名:学号: 班级:15自动化2班 ? 实验内容................................................. .. (3) 二.设计过程及讨论 (4) 1.真值表................................................. .(转载于: 小龙文档网:组合逻辑电路设计心得体会)................4 2.表达式的推导................................................. .....5 3.电路图................................................. .................7 4.实验步骤................................................. .............7 5. PROTEUS软件仿真 (9)

三测试过程及结果讨论.....................................11 1.测试数据................................................. ...........11 2.分析与讨论................................................. . (13) 四思考题................................................. (16) 实验内容: 题目: 设计一个代码转换电路,输入为4位8421码输出为4位循环码(格雷码)。 实验仪器及器件: 1.数字电路实验箱,示波器 2.器件:74LS00(简化后,无需使用,见后面) 74LS86(异或门),74LS197 实验目的: ①基本熟悉数字电路实验箱和示波器的使用 ②掌握逻辑电路的设计方法,并且掌握推导逻辑表达式的方法 ③会根据逻辑表达式来设计电路 1.真值表:

电子科技大学本科论文格式要求定稿版

电子科技大学本科论文 格式要求 HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】

电子科技大学 UNIVERSITY OF ELECTRONIC SCIENCE AND TECHNOLOGY OF CHINA 学士学位论文 BACHELOR DISSERTATION 论文题目 学生姓名 学号 学院 专业 指导教师 指导单位 年月日

电子科技大学 20 级本科毕业设计(论文)任务书 拟题单位_________________________ 审题人(签名)__________ 题目及副标题______________________________________________ 题目来源: 1.科研 2.生产 3.教学(含实验) 4.其它(选择其中一种) 主要任务: 预期成果或目标: 预期成果形式:1.硬件 2.硬件+软件 3.软件4.纯论文(选择其中一种) 指导教师签名: _____________起止时间:年月日至年月日 学生姓名_______ 专业 _________________ 学号__________ 指导单位________________________________________________ 指导教师姓名、职称______________________________________ 设计地点________________________________________________ 年月日

备注:1.此任务书应由指导教师填写,签名处须由教师亲笔签名。 2. 此任务书必须在学生毕业设计开始前....... 下达给学生。

秋专科 微机原理及应用 电子科技大学在线考试

2017年秋|微机原理及应用|专科 1. 有如下定义VAR1 DB 1,2,3,4,5 VAR2 DB '12345' NUM4 EQU VAR2–VAR1 则 NUM4=()。 (A) 5 (B) 4 (C) 3 (D) 2 分值:2 2. 下列四个寄存器中,不能用来作为间接寻址方式的寄存器是()。 (A) BP (B) BX (C) D I (D) CX 分值:2 3. 相对查询传送来说,无条件传送工作可靠。() (A) 正确 (B) 错误 分值:2 4. 指令“CMP AX,CX”和“SUB AX,CX”的实现功能完全一样,可以互相替换。() (A) 正确 (B) 错误

分值:2 5. BUFFER DB 100 DUP(?) ;表示BUFFER为()的存储空间,其内容为随机数,通常 作为程序的工作单元。 (A) 200个字节 (B) 200个字 (C) 100个字 (D) 100个字节 分值:2 6. 用来定义字节变量的伪指令是()。 (A) WORD (B) DWORD (C) B YTE (D) QWORD 分值:2 7. 乘法运算是双操作数运算,但是,在指令中却只指定一个操作数,另一个操作数是隐 含规定的,隐含操作数为()。 (A) AL/AX (B) BL/BX (C) C L/CX (D) DL/DX 分值:2

8. 指令“LOOP Lable ”与“DEC CX JNZ Lable ”的功能是等价的。() (A) 错误 (B) 正确 分值:2 9. 非循环算术移位指令在执行时,实际上是把操作数看成()符号数来进行移位。 (A) 不确定 (B) 带 (C) 都可以 (D) 无 分值:2 10. 计算机存储容量的基本单位:1 B(Byte)=(bits),1TB=GB。 (A) 8,1000G B (B) 8,1000K (C) 8,1024M (D) 8,1024G 分值:2 11. DEC 指令不能影响标志寄存器的()位。 (A) IF (B) SF

电子科技大学数字无线电课后习题答案

作业 1:FM 对讲机中接收机的设计 系统参数:射频频率: 433MHz

信号带宽:15KHz (频偏 7.5KHz ,音频带宽 3.4KHz ) 调制方式:FM 要求:1. 给出一个可实现的系统结构 2. 设计系统各级的主要参数(如滤波器、振荡器等) 3. 画出各级的频谱结构

答案: 1. 二次变频超外差式接收机系统:

f0 433MHz B 20MHz

f IF1

49.5MHz

f0 49.5MHz B 100KHz

fIF2 450KHz

f0 450KHz B 15KHz

fLO1 383.5MHz 或 482.5MHz

fLO2 48.05MHz 或 49.95MHz

2.

15KHz

433

f (MHz)

334 383.5 433 482.5 532 f (MHz)

47.5 48.05 49.5 49.95 50.4 f (MHz)

450

f (KHz)

1.根据下图所示的数字基带接收机电路和 A 点给定的信号频谱, 画出图中 B、C、D、E、F 点的信号频谱。

cos0t

e j0t

e 2

j0t

A

sin 0t

e

j0t

e 2j

j0t

cosot

LPF

LPF

-sinot

zBI(t)

zBI(n)

B

C zBQ(t)

A/D

D

DSP

E

A/D

zBQ(n)

fs=2.5Bs

zB(n)= zBI(n) +j zBQ(n)

F

A点信号频谱:

X(f)

1

Bs

0.5

f0 Bs f0

0

f0 f0 Bs f (Hz)

答案:

B点信号频谱: 经LPF滤除

2 f0

ZBI ( f ) 1 0.5

Bs 0 Bs

经LPF滤除

2 f0 f (Hz)

C点信号频谱:

j ZBQ ( f ) 1

0.5

Bs

0 Bs

f (Hz)

组合逻辑电路的设计

\ 广州大学学生实验报告 开课学院及实验室:电子信息楼410 2013年5月20日 学院 机械与电气 工程学院 年级、专 业、班 11级电气1班姓名·学号 实验课程名 称 数字电子技术实验成绩 实验项目名称; 实验二设计性实验——组合逻辑电路的设计 指导 老师 一、实验目的 1、学习组合逻辑电路的设计方法; 2、掌握使用通用逻辑器件实现逻辑电路的一般方法。 二、实验原理 使用中、小规模集成电路来设计组合电路时最常见的逻辑电路设计方法。设计的过程通常是根据 给出的实际逻辑问题,求出实现这一逻辑功能的最简单逻辑电路,这就是设计组合逻辑电路时要完成 的工作。 , 组合逻辑电路的设计工作通常可按如下步骤进行。 (1)进行逻辑抽象 (2)写出逻辑函数式 (3)选定器件的类型 (4)将逻辑函数化简或变换成适当形式 (5)根据化简或变换后的逻辑函数式画出逻辑电路的连接图 (6)工艺设计 例设计一个监视交通信号灯工作状态的逻辑电路。每一组信号灯由红、黄、绿3盏灯组成,如图 3-22所示。正常工作情况下,任何时刻必有一盏灯亮,而且只允许有一盏灯亮。而当出现其他5种 点亮状态时,电路发生故障,这是要求发出故障信号,以提醒维护人员前去修理。 { 首先进行逻辑抽象。 取红、黄、绿3盏灯的状态为输入变量,分别用R、Y、G表示,并规定灯亮时为1,不亮为0。取故 障信号为输出变量,以Z表示,并规定正常工作状态下Z=0,发生故障时Z=1。更具题意可列出表3-9 所示的逻辑真值表。 表3-9真值表 R Y G Z\ R Y G Z 000[ 1 1000 00| 1 01011 0{ 1 001101

西安电子科技大学本科生毕业设计(论文)撰写规范

西安电子科技大学本科生毕业设计(论文)撰写规范一. 毕业设计(论文)的总体要求: 撰写论文应简明扼要,一般不少于15000字(外语专业可适当减少,但不得少于10000单词,且须全部用外语书写)。 二. 毕业设计(论文)的编写格式: 每一章、节的格式和版面要求整齐划一、层次清楚。其中: 1. 论文用纸:统一用A4纸,与论文封皮,任务书,工作计划,成绩考核表一致。 2. 章的标题:如:“摘要”、“目录”、“第一章”、“附录”等,黑体,三号,居中排列。 3. 节的标题:如:“2.1认证方案”、“9.5小结”等,宋体,四号,居中排列。 4. 正文:中文为宋体,英文为“Times News Roman”,小四号。正文中的图名和表名,宋体,五号。 5. 页眉:宋体五号,居中排列。左面页眉为论文题目,右面页眉为章次和章标题。页眉底划线的宽度为0.75磅。 6. 页码:宋体小五号,排在页眉行的最外侧,不加任何修饰。 三. 毕业设计(论文)的前置部分: 毕业设计(论文)的前置部分包括封面、中英文摘要、目录等。 1.封面及打印格式 (1)学号:按照学校的统一编号,在右上角正确打印自己的学号,宋体,小四号,加粗。(2)题目:题目应和任务书的题目一致,黑体,三号。 (3)学院、专业、班级、学生姓名和导师姓名职称等内容,宋体,小三号,居中排列。 2. 中英文摘要及关键词 摘要是关于论文的内容不加注释和评论的简短陈述,具有独立性和自含性。它主要是简要说明研究工作的目的、方法、结果和结论,重点说明本论文的成果和新见解。关键词是为了文献标引工作从论文中选取出来用以表示全文主题内容信息的术语。 (1)中文摘要,宋体小四号,一般为300字;英文摘要,“Times News Roman”字体, 小四号,一般为300个实词。摘要中不宜出现公式、非公用的符号、术语等。 (2)每篇论文选取3 ~ 5个关键词,中文为黑体小四号,英文为“Times News Roman”字 体加粗,小四号。关键词排列在摘要的左下方一行,起始格式为:“关键词:”和“Keyword:”。具体的各个关键词以均匀间隔排列,之间不加任何分隔符号。 四. 目录:按照论文的章、节、附录等前后顺序,编写序号、名称和页码。目录页排在中英文摘要之后,主体部分必须另页右面开始,全文以右页为单页页码。 五. 毕业设计(论文)的主体部分: 毕业设计(论文)的主体部分包括引言(绪论)、正文、结论、结束语、致谢、参考文献。

组合逻辑电路的设计

组合逻辑电路的设计 一.实验目的 1、加深理解组合逻辑电路的工作原理。 2、掌握组合逻辑电路的设计方法。 3、掌握组合逻辑电路的功能测试方法。 二.实验器材 实验室提供的芯片:74LS00与非门、74LS86异或门,74LS54与或非门,实验室提供的实验箱。 三.实验任务及要求 1、设计要求 (1)用与非门和与或非门或者异或门设计一个半加器。 (2)用与非门和与或非门或者异或门设计一个四位奇偶位判断电路。 2、实验内容 (1)测试所用芯片的逻辑功能。 (2)组装所设计的组合逻辑电路,并验证其功能是否正确。 三.实验原理及说明 1、简述组合逻辑电路的设计方法。 (1)分析实际情况是否能用逻辑变量来表示。 (2) 确定输入、输出逻辑变量并用逻辑变量字母表示,作出逻辑规定。 (3) 根据实际情况列出逻辑真值表。 (4) 根据逻辑真值表写出逻辑表达式并化简。 (5) 画出逻辑电路图,并标明使用的集成电路和相应的引脚。 (6) 根据逻辑电路图焊接电路,调试并进一步验证逻辑关系是否与实际情况相符。 2、写出实验电路的设计过程,并画出设计电路图。 (1)半加器的设计 如果不考虑有来自低位的进位将两个1位二进制数相加。 A、B是两个加数,S是相加的和,CO是向高位的进位。 逻辑表达式 S=A’B+A’B=A⊕B CO=AB (2)设计一个四位奇偶位判断电路。 当四位数中有奇数个1时输出结果为1;否则为0。 A, B, C, D 分别为校验器的四个输入端,Y时校验器的输出端

逻辑表达式 Y=AB’C’D’+A’BC’D’+A’B’C D’+A’B’C’D+A’BCD+AB’CD+ABC’D+ABCD’ =(A⊕B)⊕(C⊕D) 四.实验结果 1、列出所设计电路的MULTISM仿真分析结果。 (1)半加器的设计,1-A被加数,2-B加数,XMMI(和数S)XMM2(进位数CO) (2)设计一个四位奇偶位判断电路。

组合逻辑电路的设计及半加器、全加器

实验四组合逻辑电路的设计及半加器、全加器 一、实验目的 1.掌握组合逻辑电路的设计与测试方法 2.掌握半加器、全加器的工作原理。 二、实验原理和电路 1、组合逻辑电路的设计 使用中、小规模集成电路来设计组合电路是最常见的逻辑电路。设计 组合电路的一般步骤如图1.4.1所示。 图1.4.1 组合逻辑电路设计流程图 根据设计任务的要求建立输入、输出变量,并列出真值表。然后用逻辑代数或卡诺图化简法求出简化的逻辑表达式。并按实际选用逻辑门的类型修改逻辑表达式。根据简化后的逻辑表达式,画出逻辑图,用标准器件构成逻辑电路。最后,用实验来验证设计的正确性。 1.半加器 根据组合电路设计方法,首先列出半加器的真值表,见表1.4.1。 写出半加器的逻辑表达式 S=AB+AB=A⊕B C=AB 若用“与非门”来实现,即为 半加器的逻辑电路图如图1.4.2所示。 在实验过程中,我们可以选异或门74LS86及与门74LS08实现半加器的逻辑功能;也可用全与非门如74LS00反相器74LS04组成半加器。

(a)用异或门组成的半加器(b)用与非门组成的半加器 图1.4.2 半加器逻辑电路图 2.全加器 用上述两个半加器可组成全加器,原理如图1.4.3所示。 图1.4.3由二个半加器组成的全加器表1.4.2 全加器逻辑功能表 表1.4.1 半加器逻辑功能 三、实验内容及步骤 1.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能。 根据半加器的逻辑表达式可知,相加的和Y是A、B的异或,而进位Z是A、B相与,故半加器可用一个集成异或门和二个与非门组成如图1.4.4。 图1.4.4 用一个集成异或门和二个与非门组成半加器 ⑴在实验仪上用异或门和与门接成以上电路。A、B接逻辑开关,Y、Z接发光二极管显示。 ⑵按表1.4.3要求改变A、B状态,将相加的和Y和进位Z的状态填入下表中。 输入端 A 0 1 0 1 输入输出 C1-1 B A S i C i 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 00 10 1 0 0 1 10 0 1 0 1 1 1 输入和进位 A B S C 0 0 0 1 1 0 1 1 1 1 1

电子科技大学模拟电路考试题及答案

………密………封………线………以………内………答………题………无………效…… 电子科技大学 二零零七至二零零八学年第一学期期末考试 模拟电路基础课程考试题A 卷(120 分钟)考试形式:开卷课程成绩构成:平时10 分,期中30 分,实验0 分,期末60 分 一(20分)、问答题 1.(4分)一般地,基本的BJT共射放大器、共基放大器和共集放大器的带宽哪个最大?哪个最小? 2.(4分)在集成运算放大器中,为什么输出级常用射极跟随器?为什么常用射极跟随器做缓冲级? 3.(4分)电流源的最重要的两个参数是什么?其中哪个参数决定了电流源在集成电路中常用做有源负载?在集成电路中采用有源负载有什么好处? 4.(4分)集成运算放大器为什么常采用差动放大器作为输入级? 5.(4分)在线性运算电路中,集成运算放大器为什么常连接成负反馈的形式?

………密………封………线………以………内………答………题………无………效…… 二(10分)、电路如图1所示。已知电阻R S=0,r be=1kΩ,R1∥R2>>r be。 1.若要使下转折频率为10Hz,求电容C的值。 2.若R S≠0,仍保持下转折频率不变,电容C的值应该增加还是减小? 图1 三(10分)、电路如图2所示。已知差模电压增益为10。A点电压V A=-4V,硅三极管Q1和Q2的集电极电压V C1=V C2=6V,R C=10 kΩ。求电阻R E和R G。 图2

………密………封………线………以………内………答………题………无………效…… 四(10分)、电路如图3所示。已知三极管的β=50,r be=1.1kΩ,R1=150kΩ,R2=47kΩ,R3=10kΩ,R4=47kΩ,R5=33kΩ,R6=4.7kΩ,R7=4.7kΩ,R8=100Ω。 1.判断反馈类型; 2.画出A电路和B电路; 3.求反馈系数B; 4.若A电路的电压增益A v=835,计算A vf,R of和R if。 图3

数字集成电路知识点整理

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统 第一章引论 1、数字IC芯片制造步骤 设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计) 制版:根据版图制作加工用的光刻版 制造:划片:将圆片切割成一个一个的管芯(划片槽) 封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连 测试:测试芯片的工作情况 2、数字IC的设计方法 分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个模块分别进行建模与验证 SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore))与设计复用Foundry(代工)、Fabless(芯片设计)、Chipless(IP设计)“三足鼎立”——SoC发展的模式 3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的) NRE (Non-Recurrent Engineering) 成本 设计时间和投入,掩膜生产,样品生产 一次性成本 Recurrent 成本 工艺制造(silicon processing),封装(packaging),测试(test) 正比于产量 一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数 功耗:emmmm自己算 4、EDA设计流程 IP设计系统设计(SystemC)模块设计(verilog) 综合 版图设计(.ICC) 电路级设计(.v 基本不可读)综合过程中用到的文件类型(都是synopsys): 可以相互转化 .db(不可读).lib(可读) 加了功耗信息

组合逻辑电路的设计实验报告

中国石油大学现代远程教育 电工电子学课程实验报告 所属教学站:青岛直属学习中心 姓名:杜广志学号: 年级专业层次:网络16秋专升本学期: 实验时间:2016-11-05实验名称:组合逻辑电路的设计 小组合作:是○否●小组成员:杜广志 1、实验目的: 学习用门电路实现组合逻辑电路的设计和调试方法。 2、实验设备及材料: 仪器:实验箱 元件:74LS00 74LS10 3、实验原理: 1.概述 组合逻辑电路又称组合电路,组合电路的输出只决定于当时的外部输入情况,与电路过去状态无关。因此,组合电路的特点是无“记忆性”。在组成上组合电路的特点是由各种门电路连接而成,而且连接中没有反馈线存在。所以各种功能的门电路就是简单的组合逻辑电路。 组合逻辑电路的输入信号和输出信号往往不止一个,其功能描述方法通常有函数表达式、真值表、卡诺图和逻辑图等几种。 组合逻辑电路的分析与设计方法,是立足于小规模集成电路分析和设计的基本方法之一。 2.组合逻辑电路的分析方法 分析的任务是:对给定的电路求解其逻辑功能,即求出该电路的输出与输入之间的逻辑关系,通常是用逻辑式或真值表来描述,有时也加上必须的文字说明。 分析的步骤: (1)逐级写出逻辑表达式,最后得到输出逻辑变量与输入逻辑变量之间的逻辑函数式。 (2)化简。 (3)列出真值表。 (4)文字说明 上述四个步骤不是一成不变的。除第一步外,其它三步根据实际情况的要求而采用。 3.组合逻辑电路的设计方法 设计的任务是:由给定的功能要求,设计出相应的逻辑电路。 设计的步骤; (1)通过对给定问题的分析,获得真值表。 在分析中要特别注意实际问题如何抽象为几个输入变量和几个输出变量之间的逻辑关系问题,其输出变量之间是否存在约束关系,从而获得真值表或简化

电子科技大学在线考试2019年春计算机应用基础专科

2019年春|计算机应用基础|专科 1. 函数Round(1 2.452,1)计算的结果是() (A) 12 (B) 12.4 (C) 12.5 (D) 12 分值:2 完全正确得分:2 2. 下列关于表格的说法错误的是() (A) 对于不需要的表格可以选中整个表格用“删除表格”命令删除 (B) 可以根据需要绘制指定行列数的表格 (C) Word文档中用空格分隔的文字可以转换成表格 (D) Word文档中只能插入固定行数的表格 分值:2 答题错误得分:0 3. 为了方便用户记忆和使用,采取域名来命名IP地址,下列域名代码表示教育机构的是() (A) GOV (B) ORG (C) EDU (D) COM 分值:2 答题错误得分:0

4. 以下编码技术属于有损压缩的是() (A) 行程编码 (B) 变换编码 (C) 算术编码 (D) 霍夫曼编码 分值:2 完全正确得分:2 5. 下列各类存储器中,断电后其息会丢失的是() (A) ROM (B) RAM (C) 光盘 (D) 硬盘 分值:2 答题错误得分:0 6. 在公式中需要计算一个单元格区域A1,B1,C1,D1,则下列表示该区域方式正确的是() (A) A1,D1 (B) A1:D1 (C) A1!D1 (D) A1+D1 分值:2 答题错误得分:0 7. 能同时显示多幻灯片缩略图的视图是()

(A) 普通视图 (B) 幻灯片浏览视图 (C) 备注页视图 (D) 幻灯片放映视图 分值:2 完全正确得分:2 8. 已知字符‘A’的ASCII码是1000001,则字符‘C’的ASCII值是() (A) 100 (B) 67 (C) 70 (D) 无法计算 分值:2 完全正确得分:2 9. 计算机的特点不包括() (A) 具有网络处理能力 (B) 具有逻辑判断能力 (C) 运算精度高 (D) 运算速度快 分值:2 完全正确得分:2 10. Word中文字格式可以利用“字体”对话框设置,以下格式不能在“字体”对话框中设置的是()

电子科大数字电路,期末试题101102半期考试试卷-答案

电子科技大学二零零九年至二零一零学年第二学期“数字逻辑设计及应用”课程考试题(半期)(120分钟)考试日期2011年4月23日 一二三四五六七八九十总分评卷教师 I. To fill the answers in the “( )” (2’ X 19=38) 1. [1776 ]8 = ( 3FE )16 = ( 1111111110 )2= ( 1000000001 ) Gray . 2. (365)10 = ( 001101100101 )8421BCD=( 001111001011 ) 2421 BCD. 3.Given an 12-bit binary number N. if the integer’s part is 9 bits and the fraction’s part is 3 bits ( N = a8 a7 a6 a5 a4 a3 a2 a1 a0 . a-1 a-2 a-3), then the maximum decimal number it can represent is ( 511.875 ); the smallest non-zero decimal number it can represent is ( 0.125 ). 4. If X’s signed-magnitude representation X SM is(110101)2, then it’s 8-bit two’s complement representation X2’s COMP is( 11101011 ) , and (–X)’s 8-bit complement representation (–X) 2’s COMP is ( 00010101 )2 . 5. If there are 2011 different states, we need at least ( 11 ) bits binary code to represent them. 6.If a positive logic function expression is F=AC’+B’C(D+E),then the negative logic function expression F = ( (A+C’)(B’+(C+DE)) ). 7. A particular Schmitt-trigger inverter has V ILmax = 0.7 V, V IHmin = 2.1 V, V T+= 1.7 V, and V T-= 1.3 V, V OLmax=0.3V, V OHmin=2.7V. Then the DC noise margin in the HIGH state is ( 0.6V ), the hysteresis is ( 0.4V ). 8.The unused CMOS NAND gate input in Fig. 1 should be tied to logic ( 1 ). Fig.1Circuit of problem I-8 9. If number [ A ] two’s-complement =11011001

常用组合逻辑电路设计

实 验 报 告 实验日期: 学 号: 姓 名: 实验名称: 常用组合逻辑电路设计 总 分: 一、实验目的 学习常用组合逻辑电路的可中和代码编写,学习并熟悉VHDL 编程思想与调试方法,掌握LPM 元件实现逻辑设计,从而完成电路设计的仿真验证和硬件验证,记录结果。 二、实验原理 VHDL 设计采用层次化的设计方法,自上向下划分系统功能并逐层细化逻辑描述。层次关系中的没一个模块可以是VHDL 描述的实体,上层VHDL 代码中实例化出各个下层子模块。 利用VHDL 语言和LPM 元件设计这两种方法方法实现两个二位数大小比较的电路,根据A 数是否大于、小于、等于B 数,相应输出端F1、F2、F3为1,设A=A2A1,B=B2B1(A2A1、B2B1表示两位二进制数),当A2A1>B2B1时,F1为1;A2A1 port(a2,a1:in STD_LOGIC; b2,b1:in STD_LOGIC; f1,f2:buffer STD_LOGIC; f3:out STD_LOGIC); end bijiao; architecture bijiao_arch of bijiao is begin f1<=(a2 and(not b2))or(a1 and (not b1)and a2)or(a1 and (not b1)and(not b2)); f2<=((not a2)and b2)or((not a2)and(not a1)and b1)or((not a1)and b1 and b2); f3<=not(f1 or f2); end bijiao_arch; (2)波形仿真 网格大小 100ns 结束时间 2μs 功能仿真:时序仿真:输入信号00, 01,10,11 输入信号00, 01,10,11 输出信号001, 010,100 信号均为二 进制表达 输入信号00, 01,10,11