1_VHDL修改Quartus自己产生的testbench

VHDL编写testbench(.vht文件)

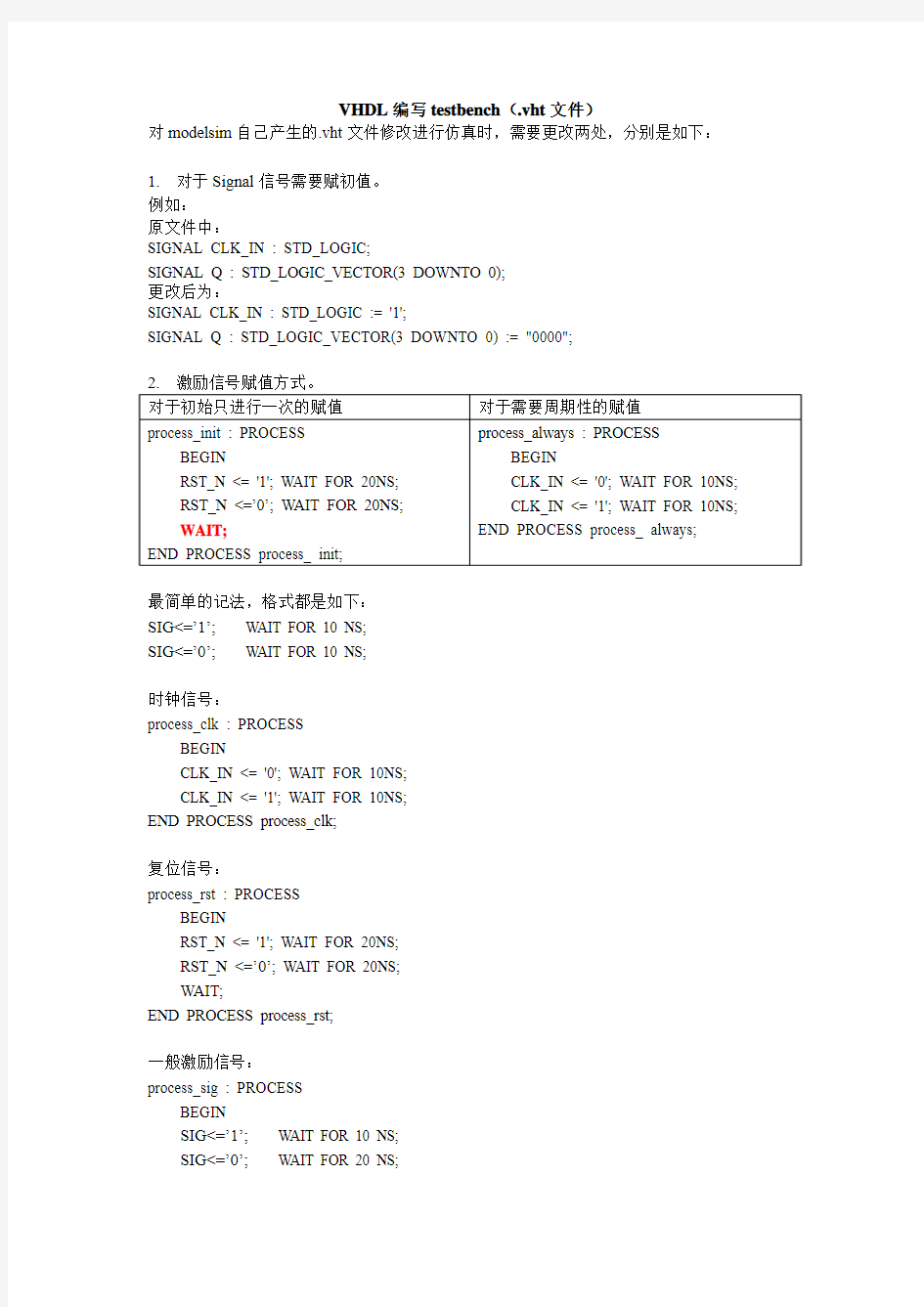

对modelsim自己产生的.vht文件修改进行仿真时,需要更改两处,分别是如下:

1.对于Signal信号需要赋初值。

例如:

原文件中:

SIGNAL CLK_IN : STD_LOGIC;

SIGNAL Q : STD_LOGIC_VECTOR(3 DOWNTO 0);

更改后为:

SIGNAL CLK_IN : STD_LOGIC := '1';

SIGNAL Q : STD_LOGIC_VECTOR(3 DOWNTO 0) := "0000";

最简单的记法,格式都是如下:

SIG<=’1’;WAIT FOR 10 NS;

SIG<=’0’;WAIT FOR 10 NS;

时钟信号:

process_clk : PROCESS

BEGIN

CLK_IN <= '0'; WAIT FOR 10NS;

CLK_IN <= '1'; WAIT FOR 10NS;

END PROCESS process_clk;

复位信号:

process_rst : PROCESS

BEGIN

RST_N <= '1'; WAIT FOR 20NS;

RST_N <=’0’; WAIT FOR 20NS;

WAIT;

END PROCESS process_rst;

一般激励信号:

process_sig : PROCESS

BEGIN

SIG<=’1’;WAIT FOR 10 NS;

SIG<=’0’;WAIT FOR 20 NS;

SIG<=’1’;WAIT FOR 20 NS;

SIG<=’0’;WAIT FOR 10 NS; END PROCESS process_ sig;

基于QuartusII的同步计数器设计

基于QuartusII的同步计数器设计 目录 一、软件及语言概述 二、实验设计 三、学习感悟 四、参考文献 一、软件及语言概述 1.1软件介绍: Quartus II是Altera公司在21 世纪初推出的FPGA/CPLD开发环境,是Altera前一代FPGA/CPLD集成开发环境MAX+PLUS II的更新换代产品,其优点是功能强大、界面友好、使用便捷。它支持原理图、VHDL、VerilogHDL以及AHDL 等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。Quartus II支持Altera的IP内核,包含了 LPM/MegaFunction宏功能模块库,使用户可以充分利用成熟的模块,简化了设计的复杂性,加快了设计速度。此外,Quartus II通过和DSP Builder工具与Matlab/Simulink的相结合,可以方便的实现各种DSP应用系统;支持Altera 的片上可编程系统开发,集系统设计、嵌入式软件开发。可编程逻辑设计于一体,是一个综合性的开发平台。 Quartus II有严格的设计流程,分为设计输入与约束、分析和综合、布局布线、仿真及编程与配置等。本次仿真设计所用到的版本为Quartus II 9.0,其用户界面如下图所示: 1.2 Verilog HDL语言概述: Verilog HDL即Verilog硬件描述语言,它主要应用于数字电路和系统设计、数字电路和系统仿真等,即利用计算机和相关软件对用Verilog HDL等硬件语言建模的复杂数字逻辑电路设计进行仿真验证,再利用综合软件将设计的数字电路自动综合,以得到符合功能需求并且在相应的硬件电路结构上可以映射实现的数字逻辑网表,然后布局布线,根据网表和选定的实现器件工艺特性自动生成具体电路,同时软件生成选定器件的延时模型,经过仿真验证确定无误后写入器件中,最终实现电路设计。Verilog HDL语言不仅定义了语法而且对每个语法结构都定义了清晰的模拟、仿真语义。因此用这种语言编写的模型能够使用Verilog仿真

数电设计数字钟基于QUARTUS

大连理工大学本科实验报告 题目:数电课设——多功能数字钟 课程名称:数字电路课程设计 学院(系):电信学部 专业:电子与通信工程 班级: 学生姓名: *************** 学号:*************** 完成日期: 成绩: 2010 年 12 月 17 日 题目:多功能数字时钟 一.设计要求 1)具有‘时’、‘分’、‘秒’的十进制数字显示(小时从00~23) 2)具有手动校时校分功能 3)具有整点报时功能,从59分50秒起,每隔2秒钟提示一次 4)具有秒表显示、计时功能(精确至百分之一秒),可一键清零 5)具有手动定时,及闹钟功能,LED灯持续提醒一分钟 6)具有倒计时功能,可手动设定倒计时范围,倒计时停止时有灯光提示,可一键清零 二.设计分析及系统方案设计 1. 数字钟的基本功能部分,包括时、分、秒的显示,手动调时,以及整点报时部分。基本模块是由振荡器、分频器、计数器、译码器、显示器等几部分组成。利用DE2硬件中提供的50MHZ晶振,经过分频得到周期为1s的时钟脉冲。将该信号送入计数器进行计算,并把累加结果以“时”“分”“秒”的形式通过译码器由数码管显示出来。 进入手动调时功能时,通过按键改变控制计数器的时钟周期,使用的时钟脉冲进行调时计数(KEY1调秒,LOAD2调分,LOAD3调时),并通过译码器由七位数码管显示。

从59分50秒开始,数字钟进入整点报时功能。每隔两秒提示一次。(本设计中以两个LED灯代替蜂鸣器,进行报时) 2. 多功能数字钟的秒表功能部分,计时范围从00分秒至59分秒。可由输入信号(RST1)异步清零,并由按键(EN1)控制计时开始与停止。 将DE2硬件中的50MHZ晶振经过分频获得周期为秒的时钟脉冲,将信号送入计数器进行计算,并把累计结果通过译码器由七位数码管显示。 3.多功能数字钟的闹钟功能部分,通过按键(KEY1,KEY2,KEY3)设定闹钟时间,当时钟进入闹钟设定的时间(判断时钟的时信号qq6,qq5与分信号qq4,qq3分别与闹钟设定的时信号r6,r5与分信号r4,43是否相等),则以LED灯连续提示一分钟。 4. 多功能数字钟的倒计时功能部分,可通过按键(LOAD7调秒,LOAD8调分,LOAD9调时)设定倒计时开始时刻。倒计时的时钟与数字钟的时钟相同,每迎到一个时钟上升沿,则计数器减一。计数器减至00时,分钟位、秒钟位恢复至59,时钟位恢复至23。倒计时结束时(即00时00分00秒),控制LED灯亮,表示倒计时结束。 本设计通过数据选择器控制译码器,使数码管独立显示,各功能之间互不影响。当LOAD4为高电平,则对秒表信号进行译码,数码管显示秒表数据;当LOAD4为低电平,LOAD5为高电平,则对闹钟信号进行译码,数码管显示闹钟数据;当LOAD4,LOAD5为低电平,LOAD6为高电平,则对倒计时信号进行译码,数码管显示倒计时信号数据;当LOAD4,LOAD5,LOAD6全为低电平,则对正常时钟信号进行译码,数码管显示时钟信号数据。 附图1:系统总体结构框图

基于Quartus_II_的FPGACPLD开发

通信工程专业实验实践课程参考系列之二(可做实验指导书或课外自学参考) 基于Quartus II 的FPGA/CPLD开发 实训手册 (未经同意不得上网传播) 通信工程系 唐庭龙夏平 2010-3

目录 1 Quartus II软件的安装 (5) 2 Quartus II软件的使用、开发板的使用 (5) 2.1 原理图方式设计3-8译码器 (5) 2.2 VHDL编程方式设计2FSK调制器 (24) 2.3 原理图结合VHDL编程方式设计流水灯 (43) 3基于QuartusII的FPGA/CPLD数字系统设计实例 (62) 3.1 数码管静态、动态显示设计(2学时) (62) 3.2 液晶接口(LCD1602/LCD12864)控制设计(4学时) (63) 3.3 矩阵键盘显示电路设计(2学时) (64) 3.4 PS2协议及PS2键盘/鼠标控制设计(2学时) (65) 3.5 VGA接口控制设计(6学时) (66) 3.6 数字频率计设计(4学时) (67) 3.7 数字钟设计(4学时) (68) 3.8 抢答器/表决器设计(2学时) (69) 3.9 出租车计费器设计(4学时) (70) 3.10 电梯控制器设计(2学时) (71) 3.11 交通灯控制电路设计(2学时) (72) 3.12 篮球计时计分器设计(8学时) (73) 3.13 DDS正弦信号发生器设计(8学时) (74) 3.14 MP3播放器设计(8学时) (75)

4 数字电路设计基础100实例(VHLD语言) 第1例带控制端口的加法器 第2例无控制端口的加法器 第3例乘法器 第4例比较器 第5例二路选择器 第6例寄存器 第7例移位寄存器 第8例综合单元库 第9例七值逻辑与基本数据类型 第10例函数 第11例七值逻辑线或分辨函数 第12例转换函数 第13例左移函数 第14例七值逻辑程序包 第15例四输入多路器 第16例目标选择器 第17例奇偶校验器 第18例映射单元库及其使用举 第19例循环边界常数化测试 第20例保护保留字 第21例进程死锁 第22例振荡与死锁 第23例振荡电路 第24例分辨信号与分辨函数 第25例信号驱动源 第26例属性TRANSACTION和分辨信号 第27例块保护及属性EVENT, 第28例形式参数属性的测试 第29例进程和并发语句 第30例信号发送与接收 第31例中断处理优先机制建模 第32例过程限定 第33例整数比较器及其测试 第34例数据总线的读写 第35例基于总线的数据通道 第36例基于多路器的数据通道 第37例四值逻辑函数 第38例四值逻辑向量按位或运算 第39例生成语句描述规则结构 第40例带类属的译码器描述 第41例带类属的测试平台 第42例行为与结构的混合描述

实验一 基于QUARTUSII图形输入电路的设计

实验一基于QUARTUSII图形输入电路的设计 一、实验目的 1、通过一个简单的3—8译码器的设计,掌握组合逻辑电路的设计方法。 2、初步了解QUARTUSII原理图输入设计的全过程。 3、掌握组合逻辑电路的静态测试方法。 二、实验原理 3-8译码器三输入,八输出。当输入信号按二进制方式的表示值为N时,输出端标号为N 的输出端输出高电平表示有信号产生,而其它则为低电平表示无信号产生。因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为高电平的情况下,能表示所有的输入组合。其真值表如表1-1所示 输入输出 A B C D7 D6 D5 D4 D3 D2 D1 D0 0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 1 1 0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0 表1-1 三-八译码器真值表 译码器不需要像编码器那样用一个输出端指示输出是否有效。但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。本例设计中没有考虑使能输入端,自己设计时可以考虑加入使能输入端时,程序如何设计。 三、实验内容 在本实验中,用三个拨动开关来表示三八译码器的三个输入(A、B、C);用八个LED来表示三八译码器的八个输出(D0-D7)。通过输入不同的值来观察输入的结果与三八译码器的真

基于quartusii时序约束

关于quartus ii时序约束(1) 2012-06-17 09:46:07| 分类:默认分类|举报|字号订阅 一直以来都只是简单地理解了一下关于时序约束的内容,而工具也有默认classic的约束,加上目前的设计对时序没有很高的要求,所以就一直都没真正地自己做过一次约束,但是我知道,这部分是不可以跳过的,这部分也算是搞 FPGA必须掌握的内容。今天下午对这部分进行了初次探究,收获有如下: 常用的约束有三种: 1.时序约束 2.区域约束 3.位置约束 时序约束的作用有: 1.提高设计的工作频率 2.获得正确的时序分析报告 需要复习前面博文《FPGA学习之时序分析基础(7)》 记住,堵塞原则是HDL语言的精髓,也就是说触发器是有延时作用的,虽然两个触发器使用的是同一个时钟,但是当第二个触发器接收第一帧数据的时候第一个触发器在发第二帧数据,而当第二个触发器接收第二帧数据的时候第一个触发器在发第三帧数据,依此类推,也就是说每一帧数据在两个触发器之间都有一个clk的时间前进,如果前进的时间太长,也即是系统给的时钟太快,就会出现无法满足第二个触发器setup的时间。setup time 就是第二个触发器在接收到由第一个触发器上一个时钟发送的数据之前应空闲的时间。 公式:CLK+TCLK2-Tsu > Tclk1 + Tcd + Tdata 所以系统CLK是和Tsu息息相关的,所以看时序报告的时候也是从Clock Setup ‘clk’看最差路径等信息。 在FPGA设计工具中包含有4种路径:从输入端口到寄存器,从寄存器到寄存器,从寄存器到输出,从输入到输出的纯组合逻辑。通常,需要对这几种路径分别进行约束,以便使设计工具能够得到最优化的结果。下面对这几种路径分别进行讨论。 1. 从输入端口到寄存器: 这种路径的约束是为了让FPGA设计工具能够尽可能的优化从输入端口到第一级寄存器之间的路径延迟,使其能够保证系统时钟可靠的采到从外部芯片到FPGA的信号。 约束名称:input delay。

基于QuartusII的数字电路仿真实验报告手册

数字电路仿真实验报告 班级通信二班姓名:孔晓悦学号:10082207 作业完成后,以班级为单位,班长或课代表收集齐电子版实验报告,统一提交. 文件命名规则如“通1_王五_学号” 一、实验目的 1. 熟悉译码器、数据选择器、计数器等中规模数字集成电路(MSI)的逻辑功能及其使 用方法。 2. 掌握用中规模继承电路构成逻辑电路的设计方法。 3. 了解EDA软件平台Quartus II的使用方法及主要功能。 二、预习要求 1. 复习数据选择器、译码器、计数器等数字集成器件的工作原理。 2. 熟悉所有器件74LS153、74LS138、74LS161的功能及外引线排列。 3.完成本实验规定的逻辑电路设计项目,并画出接线图,列出有关的真值表。 三、实验基本原理 1.译码器 译码器的逻辑功能是将每个输入的二进制代码译成对应的高、低电平信号。译码器按功能可分为两大类,即通用译码器和显示译码器。通用译码器又包括变量译码器和代码变换译码器。 变量译码器是一种完全译码器,它将一系列输入代码转换成预知一一对应的有效信号。 这种译码器可称为唯一地址译码器。如3线—8线、4线—16线译码器等。 显示译码器用来将数字或文字、符号的代码译成相应的数字、文字、符号的电路。如BCD-七段显示译码器等。 2.数据选择器 数据选择器也陈伟多路选择器或多路开关,其基本功能是:在选择输入(又称地址输入)信号的控制下,从多路输入数据中选择某一路数据作为输出。因此,数据选择器实现的是时分多路输入电路中发送端电子开关的功能,故又称为复用器。一般数据选择器有n 个地址输入端,2n错误!未找到引用源。个数据输入端,一个数据输出端或反码数据输出端,同时还有选通端。目前常用的数据选择器有2选1、4选1、8选1、16选1等多种类型。 3.计数器 计数器是一个庸医实现技术功能的时序部件,它不仅可以用来对脉冲计数,还常用作数字系统的定时、分频、执行数字运算以及其他一些特定的逻辑功能。 74LS161是4位同步二进制计数器,它除了具有二进制加法计数功能外,还具有预置数、保质和异步置零等附加功能。 四、实验内容

基于QuartusII 的多功能数字钟设计

多功能数字钟设计 院系: 专业: 指导教师: 班级: 学号: 姓名 时间:2015.3.9-3.18

摘要 多功能数字钟在我们的日常生活中有着非常广泛的应用。本实验利用QuartusII软件设计一个多功能数字计时器,并下载到SmartSOPC实验系统中。这个数字计时器,可以完成00:00:00到23:59:59的计时功能,并在控制电路的作用下具有保持、清零、快速校时、快速校分、整点报时等功能,这些功能相互独立,却又互相协调配合。在此类基础功能之上还添加了秒表功能。 关键词QuartusII软件 SmartSOPC实验系统多功能数字钟 外文摘要 Title Multi-function digital clock design dissertation Abstract Multi-function digital clock in our daily life has a very wide application. This experiment using software QuartusII design a multi-function digital timer, and download to SmartSOPC experiment system. The digital timer, can complete 00:00:00 to 23:59:59 timing functions, and under the action of control circuit has to keep fast, reset, when the school, the school points, hour, and other functions, and these features are independent of each other, and coordinate with each other. On such a basis function also added stopwatch function. Keywords QuartusII、SmartSOPC experimental system、Multi-function digital timer。

基于Quartus II的运算器的设计与实现(修改稿)

基于Quartus II的运算器的设计与实现 成耀,王礼春,顾晖 (南通大学计算机科学与技术学院,江苏南通226019) 【摘要】本文借助于Quartus II软件在计算机上仿真制作了具有简单运算功能的运算器,由此我们一方面可以了解电路仿真的主要流程,另一方面可以验证运算器的功能。 【关键词】 Q uartus II EDA 运算器仿真 0引言 电路设计对于电子信息类专业的学生而言是十分重要的,它是将理论知识运用于实践的一个重要途径。它对巩固课堂教学内容,提高学生的动手能力具有重要作用。但对于一些比较复杂的实验,学生要用大量的时间和精力进行电路连接和线路检查,常常是事倍功半,实验效果不是很理想。将计算机模拟引入到实验教学中,既可以使学生随时进行实验,又可以直接获取结果,增加学生的感性认识。而且计算机模拟仿真让设计变得更易实现,这不仅节约了经济上的开销,还节约了大量的时间与精力。这里介绍的Quartus II可以弥补原先许多数字芯片和线路连接的繁琐步骤和手工操作,使原先复杂的实现过程变得容易理解与掌握,而且还能帮助学生更快、更好地掌握课堂理论内容,加深对概念原理的理解,进一步培养学生的综合设计能力、排除故障能力和创新能力[1]。 本文借助Quartus II6.0现有的器件,设计了一个运算器,使用Quartus II6.0完成仿真,并通过仿真波形展示该运算器是如何实现运算器功能的。 1 用Quartus II做电路设计实验的优点 Quartus II6.0是由美国Altera公司开发的,是一款功能比较强的EDA工具软件,它的优势主要体现在其功能齐全,方便简单。具有可编程系统(SOPC)设计的综合性环境,也是适合SOPC的最全面的设计环境[2]。它拥有现场可编程阵列(FPGA)和复杂可编程器件(CPLD)设计的所有阶段的解决方案。它的简单易用,方便快捷,给设计者减少了难度,节约了很多时间 [3]。 为了改变延续多年的“实验内容单一,实验设备陈旧,实验时间受限,实验效果差[4]”的状况,考虑到学校机房有许多时间向学生开放,另外考虑到许多学生自己有电脑,我们选用了Quartus II。Quartus II功能强大、界面友好、易于掌握,彻底改变了传统的实验教学模式,实验具有开放性、可编程性强、设计空间大、时间灵活等特点,并具有较高的实验效率。它可以培养学生的动手能力和分析问题、解决问题的能力,增强学生对实验的浓厚兴趣,提高实践教学的质量。其显著特点如下: 开放性好:学生可以在机房的开放时间进行实验,也可以在自己宿舍里的电脑上做实验;学生可以在实验课之前预习,也可以在实验课之后进行复习;优秀学生可以进行提高训练,来不及的和不会的学生可以在课后进行补差练习;相关课程结束后,感兴趣的学生也可以在此方面继续钻研。 可操作性强:对提高学生的动手能力,加强学生对计算机整体和各组成部分的理解,增强学生计算机系统综合设计能力都有很大帮助。 实验内容安排合理:实验能够与理论教学紧密结合,实验内容由简到繁,由浅入深,循序渐进,使学生在课堂上学到的理论知识在实验中得到验证。

基于quartus的电子钟

电子线路设计Ⅱ ——基于QuartusII软件的数字钟 姓名:范征东 学号:101041305 指导老师:黄建 宇郝磊

多功能数字钟设计 一、设计内容简介 电子数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,因此得到了广泛的使用。电子数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。因此,此次设计与制做电子数字钟就是可以了解电子数字钟的原理,学会制作电子数字钟。通过电子数字钟的制作能进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法,通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。 这次电子数字钟的设计主要是利用74LS90的计数功能来实现电子钟时、分、秒的跳变,整个设计主要分为六个模块:时模块、分模块、秒模块、分频模块、校时校分模块、整点报时模块。时、分、秒模块分别用两块74LS90实现,并且分别将它们设置为60进制,60进制,24进制。秒信号的产生用石英晶体振荡器加分频器来实现,将秒信号送入秒模块,每累计60秒发出一个分脉冲信号,分模块每累计60分钟,发出一个时脉冲信号,时模块实现对24小时的累计,通过六个七段数码管显示出来。整点报时电路根据计时系统的输出状态产生一脉冲信号,然后加上一个高频或低频信号送到蜂鸣器实现报时。校时电路是直接加一个脉冲信号到时计数器或者分计数器或者秒计数器来对“时”、“分”、“秒”显示数字进行校对调整。

本数字钟以计时为基本功能,可以完成00:00:00到23:59:59,以及星期一至星期日的计时功能,并在控制电路的作用下具有保持、快速校时、快速校分的功能。在具有基本功能的基础上,增加了下列扩展功能:闹钟、整点报时功能。 数字计时器是由分频电路、计时电路、控制电路、译码显示电路等几部分组成的。其中,分频电路将试验箱提供的48Mhz的频率分成各模块电路所需要的频率;计时电路完成计时功能,并与动态显示电路相连,将时间、日期、星期等信息显示在七段数码管上;秒表电路启动后可完成最小单位为0.01秒的计时;以上各部分电路均与译码显示电路连接,将以上数据分别显示,通过按钮切换。 系统结构如下图所示

基于quartus的电子钟

基于q u a r t u s的电子钟 This model paper was revised by the Standardization Office on December 10, 2020

电子线路设计Ⅱ ——基于QuartusII软件的数字钟 姓名:范征东 5 指导老师:黄建 宇郝磊

多功能数字钟设计 一、设计内容简介 电子数字钟是一种用数字电路技术实现时、分、秒计时的装置,与机械式时钟相比具有更高的准确性和直观性,因此得到了广泛的使用。电子数字钟从原理上讲是一种典型的数字电路,其中包括了组合逻辑电路和时序电路。因此,此次设计与制做电子数字钟就是可以了解电子数字钟的原理,学会制作电子数字钟。通过电子数字钟的制作能进一步的了解各种在制作中用到的中小规模集成电路的作用及实用方法,通过它可以进一步学习与掌握各种组合逻辑电路与时序电路的原理与使用方法。 这次电子数字钟的设计主要是利用74LS90的计数功能来实现电子钟时、分、秒的跳变,整个设计主要分为六个模块:时模块、分模块、秒模块、分频模块、校时校分模块、整点报时模块。时、分、秒模块分别用两块74LS90实现,并且分别将它们设置为60进制,60进制,24进制。秒信号的产生用石英晶体振荡器加分频器来实现,将秒信号送入秒模块,每累计60秒发出一个分脉冲信号,分模块每累计60分钟,发出一个时脉冲信号,时模块实现对24小时的累计,通过六个七段数码管显示出来。整点报时电路根据计时系统的输出状态产生一脉冲信号,然后加上一个高频或低频信号送到蜂鸣器实现报时。校时电路是直接加一个脉冲信号到时计数器或者分计数器或者秒计数器来对“时”、“分”、“秒”显示数字进行校对调整。

基于QuartusⅡ的伪随机m序列发生器的设计

基于QuartusⅡ的伪随机m序列发生器的设计

————————————————————————————————作者: ————————————————————————————————日期: ?

通信系统 课程设计报告 设计题目:伪随机m序列发生器的设计班级: 13物联网1 姓名:李亚军 学号:2013313136 指导教师:程钦、任艳玲 课程地点: 60-507 江苏理工学院 电气信息工程学院 2106 年9 月8日

目录 序言………………………………………………………………………………………………1第1章QuartusⅡ软件介 绍 (2) 1.1 QuartusⅡ简 介 (2) 第2章基于QuartusⅡ的伪随机m序列发生器的设 计 (3) 2.1伪随机m序列发生器的设计要 求 (3) 2.2伪随机m序列发生器的设 计 (3) 2.3伪随机m序列发生器的实 现 (5) 2.3.1原理图输入法实现与仿真结果分 析 (5) 2.3.2 VHDL语言实现与仿真结果分 析……………………………………………………7 2.4 设计分析与总 结 (9) 2.4.1故障分 析…………………………………………………………………………………9 2.4.2功能分 析 (9) 参考文

献………………………………………………………………………………………10 体会与建议 (11) 附录………………………………………………………………………………………………12

序言 随机噪声降低了通信系统的可靠性,限制信道容量但又可以用于测试通信系统性能和提高保密通信,所以就有伪随机序列的产生。因为其具有类似于随机噪声的某些统计特性又避免了随机噪声不能重复产生和处理的缺点。 m序列是最长线性移位寄存器序列的简称,是一种伪随机序列、伪噪声(PN)码或伪随机码。可以预先确定并且可以重复实现的序列称为确定序列;既不能预先确定又不能重复实现的序列称随机序列;不能预先确定但可以重复产生的序列称伪随机序列。 m序列是目前广泛应用的一种伪随机序列,其在通信领域有着广泛的应用,如扩频通信,卫星通信的码分多址,数字数据中的加密、加扰、同步、误码率测量等领域。 在所有的伪随机序列中,m序列是最重要、最基本的一种伪随机序列。它容易产生,规律性强,有很好的自相关性和较好的互相关特性。 采用原理图输入和VHDL语言产生周期为127,码元速率为50HZ的m序列

基于Quartus_II的微程序控制简_...

基于Quartus II的微程序控制简易计算机的设计 顾晖,王礼春,成耀 (南通大学计算机科学与技术学院,江苏南通226019) 【摘要】本文借助于Quartus II软件在计算机上仿真设计了一台微程序控制的简易计算机,通过介绍电路仿真的主要流程,我们可以加深对计算机系统各模块的工作原理及相互联系的认识。 【关键词】 Q uartus II EDA 微程序控制计算机 0 引言 Quartus II是由美国Altera公司开发的,是一款功能比较强的EDA工具软件,它的优势主要体现在其功能齐全,简单易用[1]。 我们借助Quartus II6.0现有的器件,综合设计了一个简易计算机系统,并使用Quartus II6.0完成仿真[2],通过仿真波形展示该系统指令的执行流程,以及微指令的控制方法。 1 简易计算机系统的体系结构及功能模块设计 一台微程序控制的简易计算机系统包含以下几个模块[3]: 图(1)微程序控制的简易计算机系统结构示意图 a) 运算模块,由ALU (两片74181),数据寄存器DR1,DR2(两片74273)以及数据缓冲器ALU_BUF (一片74244)构成,完成DR1与DR2的各种运算; b) 存储模块,由RAM(一片lpm_ram_dp0),RAM_BUF(一片74273),AR(一片74273)构成,由AR提供地址,完成RAM 的存取数据操作;

c) 程序计数器模块,由PC(两片74161),PC_BUF(一片74244)构成,完成保存指令地址,以及提供RAM存取操作所需地址(包含存取数据与指令); d) 微程序控制模块,由IR(一片74273),微存储器(一片lpm_rom0),指令译码器(三片74273),以及一片74138(完成组合译码功能)构成,完成系统的控制功能; e) 输入模块,由IN_BUF(一片74244)构成,完成输入端IN0~IN7的数据输入功能; f) 时序电路,由集成计数器(一片74161)及三八译码器(一片74138)构成,可产生时序信号。 微程序控制的简易计算机系统结构示意图请参考图(1)。 1.1 时序电路[3] [4] 时序电路见图(1.1)。各个端口功能如下: a) R_CLK,时序电路的原始时钟,用来产生三个连续的时钟脉冲IR_CP,ROM_CP,TR_CP; b) START,启动键,低电平时有效; c) IR_CP,一个微指令周期的第一个上升沿,为指令寄存器IR的时钟信号; d) ROM_CP,一个微指令周期的第二个上升沿,为微存储器ROM及地址寄存器AR共用的时钟信号; e) TR_CP,一个微指令周期的第三个上升沿,为指令译码器,数据寄存器DR1、DR2,寄存器R0及RAM存储器共用的时钟信号。 说明:该时序电路利用集成计数器74161的计数循环特性,通过选择三八译码器74138来产生三个连续的脉冲信号,以形成一个微指令周期。因本系统只是设计简易计算机系统,所以未设计RESET键。 1.2 微程序控制器模块[3] [4] 控制器模块译码后输出的控制信号见图(1.2)。各控制端功能如下: a) 0~5号控制端,输出下一条微指令在微存储器中的地址; b) 6号控制端LDR0,R0寄存器的时钟使能信号,高电平时有效; c) 7号控制端,指示是否有下一条微指令,若有则执行下一条微指令,若无,则执行下一条指令; d) 8~10号控制端,采取组合译码方式,分别用来选择控制端PC_BUF , ALU_BUF,IN_BUF,RM_BUF,以及R0寄存器的输出使能端,均为低电平时有效,当组合译码输出为000时表示不选择任何控制端; e) 11号控制端LDRM,RAM存取操作时钟使能信号; f) 12号控制端LDAR,AR送地址操作的时钟使能信号; g) 13号控制端LDDR2,数据寄存器DR2的时钟使能信号,上升沿到来时触发; h) 14号控制端LDDR1,数据寄存器DR1的时钟使能信号,上升沿到来时触发; i) 15号控制端LDPC,程序计数器PC的时钟使能信号,上升沿到来时触发; j) 16号控制端LOAD,程序计数器PC的同步并行置数端,低电平有效,若要完成同步

基于Quartus的多功能数字钟设计

EDA设计(二) 摘要 该实验是利用QuartusII软件设计一个数字钟,进行试验设计和仿真调试,实现了计时,校时,校分,清零,保持和整点报时等多种基本功能,并下载到SmartSOPC实验系统中进行调试和验证。此外还添加了整点报时音乐功能使数字钟功能更加完善 关键字:Quartus 数字钟多功能仿真 Abstract This experiment is to design a digital clock which is based on Quartus software and in which many basic functions like time-counting,hour-correcting,minute-correcting,reset,time-hol ding and belling on the hour. And then validated the design on the experimental board.In addition,the music behing the belling on the hour make it more perfect Key words: Quartus digital-clock multi-function simulate

目录 一设计要求 (3) 二工作原理 (4) 三各模块说明 (4) 1)分频模块 (5) 2)计时模块 (8) 3)动态显示模块 (10) 4)校分与校时模块 (11) 5)清零模块 (12) 6)保持模块 (12) 7)报时模块 (12) 四扩展模块 (13) 整点报时音乐 (18) 五调试、编程下载 (19) 六实验中出现问题及解决办法 (19) 七实验收获与感受 (20) 八附录:数字钟总原理图………………………… 九参考文献 (21)

fpga 数字逻辑基于Quartus设计

示例1:基于原理图的分频器工程设计 利用原理图进行输入设计时,对设计人员的编程技术没有太高的要求,在没有掌握硬件描述语言的情况下就能进行FPGA的开发设计。学习利用软件Quartus II为原理图输入提供的原理图编辑器(Block Editor)来完成工程设计的方法。设计过程主要包括工程建立、编辑设计图形、编译综合和仿真测试。对于编程下载和硬件测试过程,这里涉及具体的硬件平台,实现的方法是相同的。 1. 建立工程文件 (1)指定工程文件名称 运行Quartus II软件,选择File→New Project Wizard打开过程生成向导。在弹出的对话框中分别输入新建工程所在的文件夹名称、工程名称和顶层实体名称。如图4.1所示。点击Next。 注意,Quartus II要求工程文件名一定要与顶层实体名称相同。 输入工程文件夹名称 输入工程名称 输入顶层实体名称 图4.1 新建工程对话框

(2)选择添加的文件和库 如果,工程文件夹不存在,则弹出提示对话框,按照提示单击Yes按钮就会自动建立。单击Next按钮,就会出现图4.2的界面。如果需要添加文件或者库,按照提示操作。否则单击Next按钮,本实验就不需要添加文件或者库。 设计文件列表 图4.2添加文件或库对话框 (3)目标器件选择 进入目标器件选择,这里在Family器件种类栏选择Cyclone系列,各项的选择如图4.3所示。点击Next就会进行第三方EDA工具的选择。 FPGA 器件选型常识。FPGA 器件的选型非常重要,不合理的选型会导致一系列的后续设计问题,有时甚至会使设计失败;合理的选型不光可以避免设计问题,而且可以提高系统的性价比,延长产品的生命周期,获得预想不到的经济效果。 FPGA 器件选型有以下7 个原则:器件的供货渠道和开发工具的支持、器件的硬件资源、器件的电气接口标准、器件的速度等级、器件的温度等级、器件的封装和器件的价格。

基于quartus II的计算机运算器设计

基于quartus II的计算机运算器设计 【摘要】随着EDA技术、CPLD/FPGA的迅猛发展以及相关软件的日益成熟,利用计算机来设计计算机成为一种行之有效且势在必行的新方式。本文基于Q uartus II 6.0的图形设计方式,辅助Verilog HDL语言,以封装的基本逻辑单元为基础设计了4位定点除法器。仿真结果表明,本文设计的除法器能够完成预期的除法运算功能。 【关键词】Q uartus;II 6.0;除法器设计;CPLD/FPGA 1 手工除法运算方法分析 计算机内部数据一般用补码表示[1],为了找出适合于计算机运算器执行的除法运算方法,下面以4位二进制数为例分析手工除法算法[2]。 正整数做除法运算时,商的数码由高到低生成,确定商之前需要比较被除数与除数位数相同的部分是否够减,不够减商位0,够减商为1[3]。由于这种试商操作是从被除数的高位开始的,为了保证位数的一致性,将被除数的最高位填写3个”0”,然后进行4位数的比较。每次得到的部分差要左移一位,最低位要由被除数没参加比较的下一位填充。当被除数的最低位数码经过试商,前次部分差和此次一位商与除数的积相减后,得到的部分差就是余数。 分析该手工除法运算方法可知:当部分积为0时,要直接将前次部分差左移一位,使之低3位的成为下一次的被减数的高3位,否则,将本次减法运算的结果左移一位,使之成为被减数的高3位。 整个除法的运算过程认定除数是不动的,那么被除数和商是每步相减之后,到要左移一位,添加下面一位,然后与一位乘积做减法。 2 正整数除法器设计 按照上述分析在Quartus II[4]中设计正整数除法电路如图1所示。主要部件为加减运算单元,保存为cfq1.bdf。用一条输入线和它的非门的或运算给减法控制线sub赋值1。正整数除法的除数和被除数的最高位均为0,因此,将补充的被除数的高3位直接同被除数的最高位连在一起,就能够得到使高位补充数码都为0的目的。