数字电子钟

数字电子钟实验报告

实验名称:数字电子钟

实验目的:掌握数字电子钟的设计、组装与调试方法;熟悉集成电路的使用方法。

实验仪器与器材:555定时器,CC4518计数器,74LS00与非门,

74LS04非门,译码驱动器74LS47,数码显示器,

电阻,电容,导线若干。

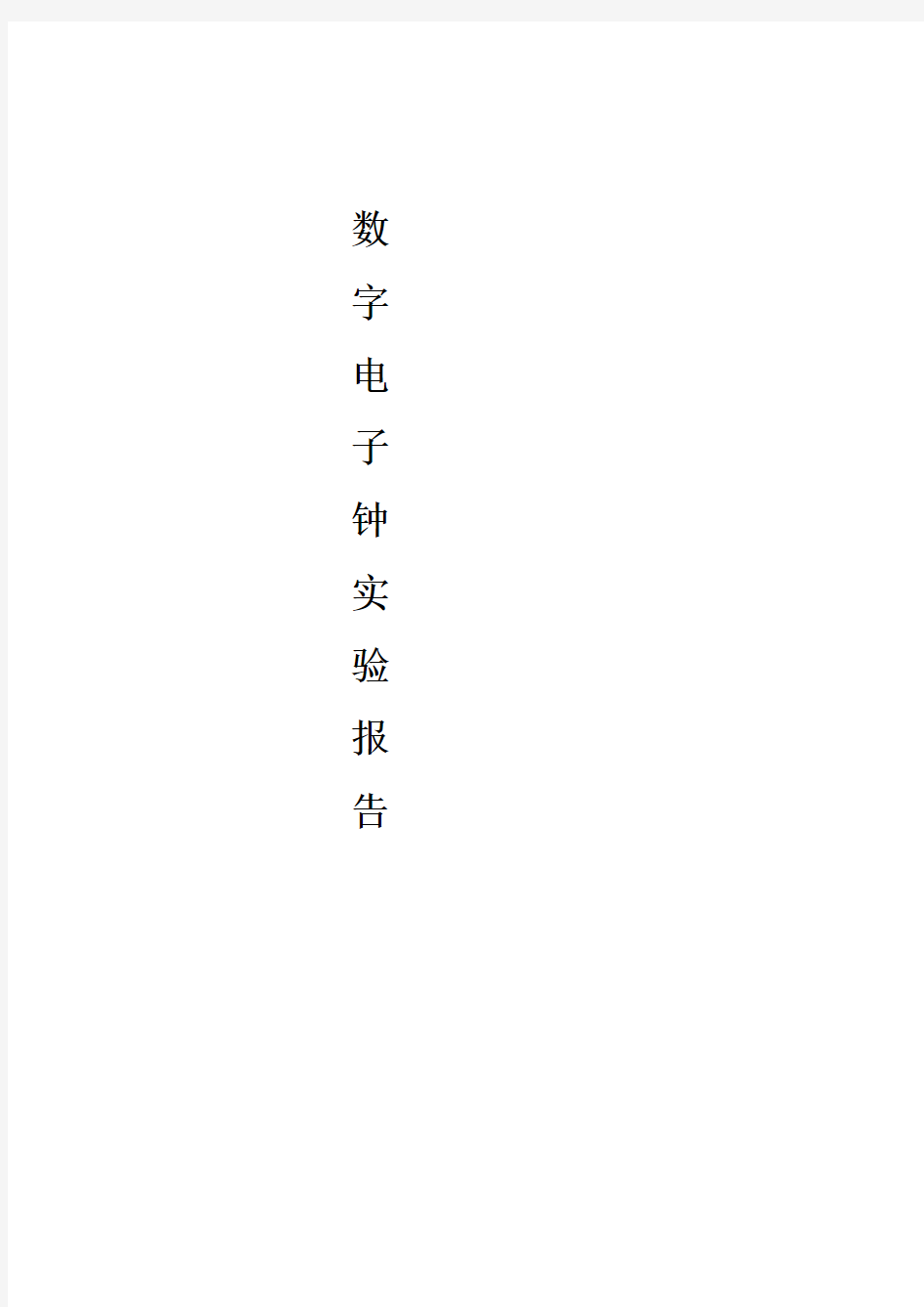

总体设计方框图:

单元电路:

(1)振荡电路:采用555定时器构成的多谐振荡器产生2000Hz脉冲。多谐振荡器的振荡频率可由式估算。

(2)分频电路:采用CC4518实现分频,产生秒脉冲

0.1uF

2.4k

2.4k

2kHz 1Hz

VCC

(3)时分秒计数器:采用CC4518设计计数器,如图,a 为六十进制

计数器,b 为二十四进制计数器

(4)译码和数码显示电路:数字钟的计数器在CP 脉冲作用下,按60秒为1分、60分为1小时,24小时为1天的计数规律计数时,就应将其状态显示成清晰的数字符号。这就需要将计数器的状态进行译码并将其显示出来。 “秒”、“分”、“时”的个位和十位的状态分别由集成片中的四个触发器的输出状态来反映的。每组(四个).输出的计数状态都按 BCD 代码以高低电平来表现。因此,需经译码电路将计数器输出的BCD 代码变成能驱动七段数码显示器的工作信号。采用译码驱动器74LS47,共阴极七段数码显示器。如图,A0、A1、A2、A3是译码器的输入端,其二进制码经译码后,从a 、b 、c 、d 、e 、f 、g 输出,分别对应的七段显示器a 、b 、c 、d 、e 、f 、g 相接 1 1 & &

74LS00与非门: 74LS04非门:

芯片CC4518: CC4518为双BCD加计数器,该器件有两个相同的同步4级计数器组成。计数器级为D触发器。具有部可交换CP和EN线,用于在时钟上升沿活下降沿加计数。在单个单元运算中,EN输入保持高电平,且在CP上升沿进位。CR线为高电平时,计数器清零。计

数器在有脉冲条件下课级联,通过将Q3连接至下一计数器的EN端可实现级联。同时后者的CP输入保持低电平。

心得体会:1、总体设计在整个设计过程中非常重要,要通过整体考虑,先画好电路图,不可看一步,做一步。在总体设计都正确后,再寻求简化的方法。

2、当设计某个单元电路无法把握整体时,可以先进行小部分功能的实现,在此基础上进行改进。

3、开始连线的时候,应该尽可能使电路连线有序,使芯片之间关系清楚,既利于自己修改,也利于与别人交流。如果电路乱的连自己都看不懂,改进和扩展都很麻烦。

4、很多难点的突破,都来自于与同学的交流,交流使自己获得更多信息,开拓了思路,因此要重视与别人的交流,多像他人请教。

5、应该有较好的理论基础,整个实验都是在理论的指导下完成了,设计过程中使用了许多平时实验课的容,如芯片的使用等。本次设计把理论应用到了实践中,同时通过设计,也加深了自己对理论知识的理解和掌握。