湖南工业大学EDA实验报告之PWM信号发生器的设计

实验三:PWM信号发生器的设计

1.实验目的

(1)熟悉Quartus Ⅱ/ISE Suite/ispLEVER软件的基本使用方法。

(2)熟悉GW48-CK或其他EDA实验开发系统的基本使用方法。

(3)学习VHDL程序中数据对象、数据类型、顺序语句和并行语句的综合使用。

2.实验内容

设计并调试好一个脉宽数控调制信号发生器,此信号发生器是由两个完全相同的可自加载加法计数器LCNT8组成的,它的输出信号的高/低电平脉宽可分别由两组8位预置数进行控制。

用GW48-CK或其他EDA实验开发系统(事先应选定拟采用的实验芯片的型号)进行硬件验证。

3.实验要求

(1)画出系统的原理图,说明系统中各主要组成部分的功能。

(2)编写各个VHDL源程序。

(3)根据系统的功能,选好测试用例,画出测试输入信号波形或编号测试程序。

(4)根据选用的EDA实验开发装置编好用于硬件验证的管脚锁定表格或文件。

(5)记录系统仿真、逻辑综合及硬件验证结果。

(6)记录实验过程中出现的问题及解决办法。

4.实验条件

(1)开发条件:Quartus Ⅱ 8.0。

(2)实验设备:GW48-CK实验开发系统。

(3)拟用芯片:EP3C55F484C8N。

5.实验设计

1)系统原理图

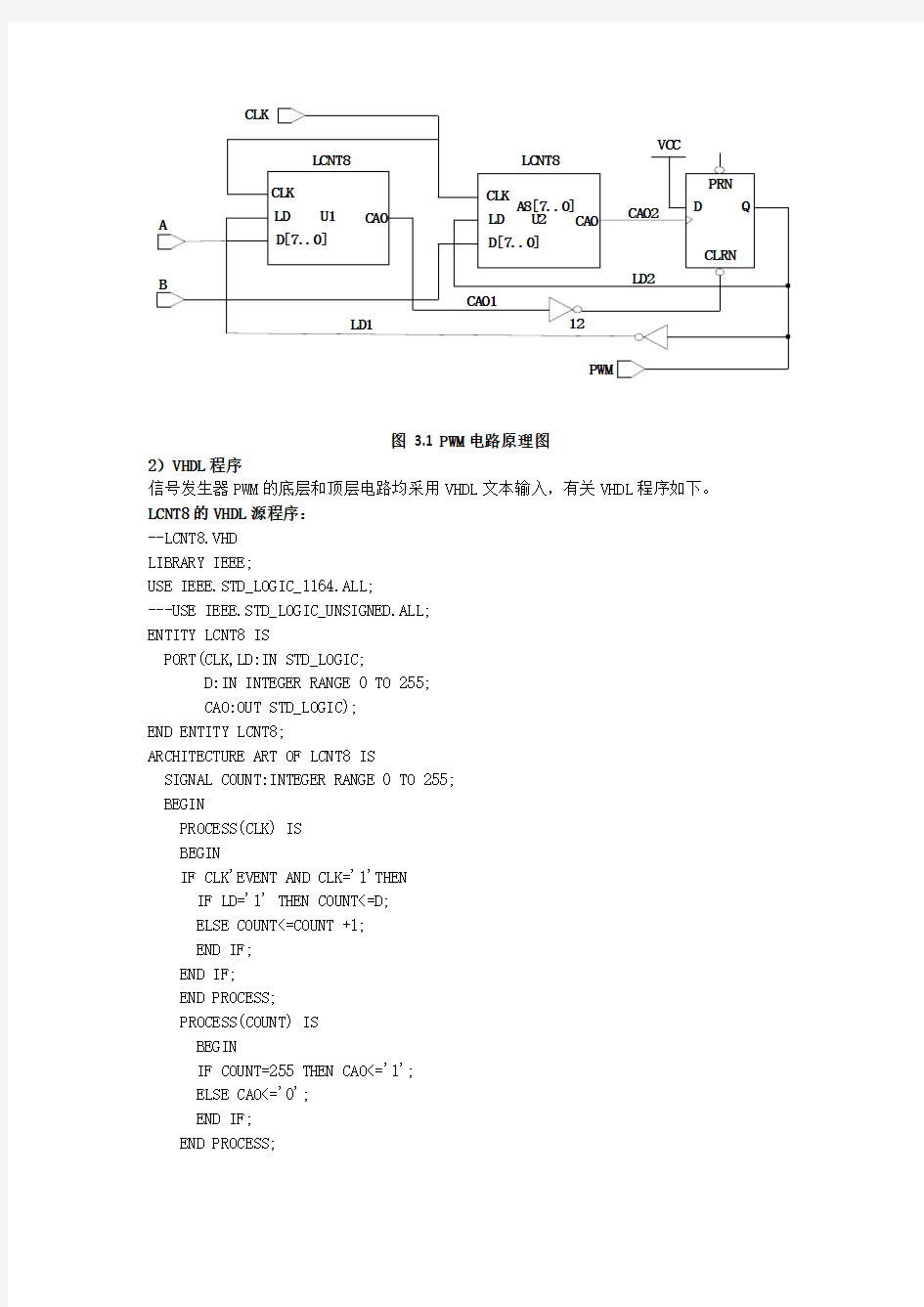

本信号发生器电路PWM的设计分为两个层次,其中底层电路包括两个完全相同的可自加载加法计数器LCNT8组成的,它的输出信号的高/低电平脉宽可分别由两组8位预置数进行控制。

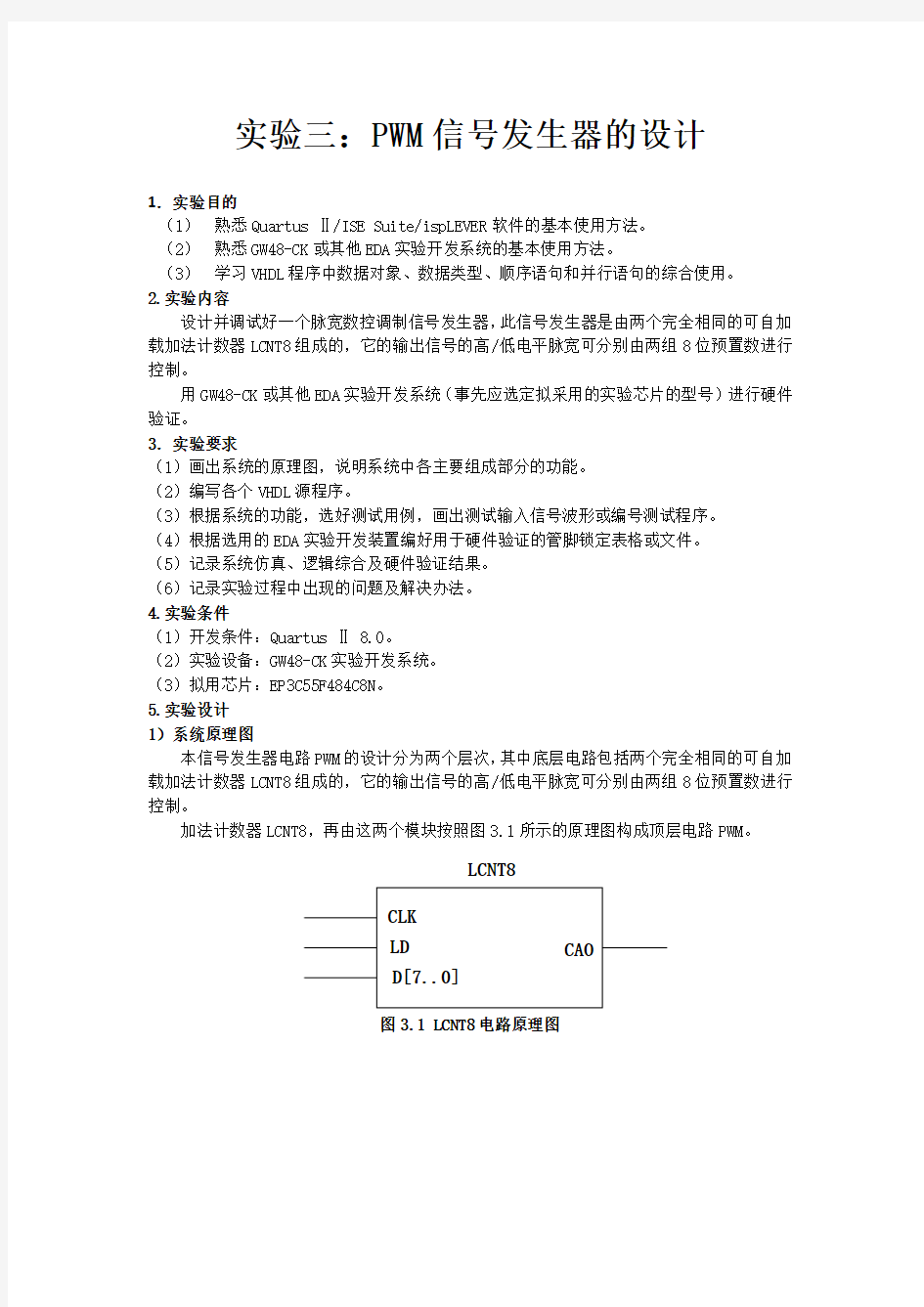

加法计数器LCNT8,再由这两个模块按照图3.1所示的原理图构成顶层电路PWM。

LCNT8

图3.1 LCNT8电路原理图

图 3.1 PWM电路原理图

2)VHDL程序

信号发生器PWM的底层和顶层电路均采用VHDL文本输入,有关VHDL程序如下。LCNT8的VHDL源程序:

--LCNT8.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

---USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY LCNT8 IS

PORT(CLK,LD:IN STD_LOGIC;

D:IN INTEGER RANGE 0 TO 255;

CAO:OUT STD_LOGIC);

END ENTITY LCNT8;

ARCHITECTURE ART OF LCNT8 IS

SIGNAL COUNT:INTEGER RANGE 0 TO 255;

BEGIN

PROCESS(CLK) IS

BEGIN

IF CLK'EVENT AND CLK='1'THEN

IF LD='1' THEN COUNT<=D;

ELSE COUNT<=COUNT +1;

END IF;

END IF;

END PROCESS;

PROCESS(COUNT) IS

BEGIN

IF COUNT=255 THEN CAO<='1';

ELSE CAO<='0';

END IF;

END PROCESS;

END ARCHITECTURE ART;

PWM的VHDL源程序:

--PWM.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

ENTITY PWM IS

PORT(CLK: IN STD_LOGIC;

A,B: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

PWM: OUT STD_LOGIC);

END ENTITY PWM;

ARCHITECTURE ART OF PWM IS

COMPONENT LCNT8 IS

PORT(CLK,LD: IN STD_LOGIC;

D: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

CAO: OUT STD_LOGIC);

END COMPONENT LCNT8;

SIGNAL CAO1,CAO2:STD_LOGIC;

SIGNAL LD1,LD2:STD_LOGIC;

SIGNAL SPWM:STD_LOGIC;

BEGIN

U1:LCNT8 PORT MAP(CLK=>CLK, LD=>LD1, D=>A, CAO=>CAO1);

U2:LCNT8 PORT MAP(CLK=>CLK, LD=>LD2, D=>B, CAO=>CAO2);

PROCESS(CAO1,CAO2) IS

BEGIN

IF CAO1='1'THEN SPWM<='0';

ELSIF CAO2'EVENT AND CAO2='1' THEN SPWM<='1';

END IF;

END PROCESS;

LD1<=NOT SPWM;

LD2<=SPWM;

PWM<=SPWM;

END ARCHITECTURE ART;

3)仿真波形设置

本设计包括两个层次,因此先进行底层的可自加载加法计数器LCNT8的仿真,再进行顶层PWM的仿真。PWM仿真输入设置及可能结果估计,图3.2为PWM仿真输入设置及可能结果估计图。

图3.2 PWM仿真输入设置及可能结果估计图

4)管脚锁定文件

根据图3.1所示的PWM电路原理图,本设计实体的输入信号CLK、A、B,输出信号PWM,据此可选择实验电路结构图NO.1,对应实验模式1。

图NO.1实验电路结构图

根据图3.5所示的实验电路结构图NO.1和图3.1确定引脚的锁定。选用EP3C55F484C8N 芯片,其引脚锁定过程如表3.1所示,其中CLK接CLOCK0,8位数控预置输入B[7..0]接PIO15~PIO8,由键4和键3控制输入,输入值分别显示在数码4、3上;另外8位数控预置输入A[7..0]接PIO7~PIO0,由键2和键1控制输入,输入值分别显示在数码2、1上;输出PWM接SPEAKER。

表3.1PWM管脚锁定过程表

6.试验结果及总结

1)系统仿真情况

PWM的时序仿真结果分别如图 3.3所示(本仿真结果是通过同时按下“CTRL+Print Screen”键抓取当前屏幕信息放入剪贴板中,再通过Windows的画图工具进行粘贴裁剪后复制,最后在Word等文档中通过粘贴的方法获得)。

图3.3 PWM的时序仿真结果

从系统仿真结果可以看出,本系统底层和顶层的程序设计完全符合设计要求。同时从系统时序仿真结果可以看出,从输入到输出有一定的延时,大约为5ns,这正是器件延时特性的反应。

2)逻辑综合结果

使用Quartus Ⅱ 8.0进行逻辑综合后,PWM的RTL视图如图3.5所示,对PWM进行逻辑综合后的资源使用情况为:Family:MAX7000S ,Device:EPM7128SLC84-10,Total macrocells:19/128(15%),Total pins:23/68(34%)。

图3.5 PWM的RTL视图

3)硬件验证情况

CLK接CLOCK0,8位数控预置输入B[7..0]接PIO15~PIO8,由键4和键3控制输入,输入值分别显示在数码4、3上;另外8位数控预置输入A[7..0]接PIO7~PIO0,由键2和键1控制输入,输入值分别显示在数码2、1上;输出PWM接SPEAKER。

4)软件下载

4)实验过程中出现的问题及解决办法

(1)刚开始由于不知道怎么管脚锁定,所以一直在徘徊,通过查阅书籍,了解到【Assignment】下的【Pins】,由于第一次打开所以找不到【Location】,没办法管脚锁定,最后通过【Pin Planner】下的【View】栏下的【Group list】及【All pins list】才打开管脚锁定窗口,通过对对应的管脚意义锁定,然后再编译一次即可。

(2)由于第一次编程下载,没有找到端口,所以结果没有办法下载在硬件里,通过单击【Hardware Steup】找到【USB Blaster【USB-0】】再添加好PWM.Sof文件,最后单击【Start】即可下载,当【Progress】进程显示100%时,编译成功,可以观察实验面板,进行硬件测试验证。