实验四(一) 串并转换实验(2学时)

湖北民族学院科技学院

信息工程学院

单片机原理实验报告

实验名称:单片机串口应用

专业班级

学号

姓名

指导教师

实验四(一)串并转换实验(2学时)

一、实验目的

⑴掌握8031串行口方式0工作方式及编程方法。

⑵掌握利用串行口扩展并行I/O通道的方法。

二、实验内容

(1)在实验箱上完成:

利用8031串行口和串行输入并行输出移位寄存器74LS164,扩展一个8位输出通道,用于驱动一个共阳极数码显示器,在数码显示器上循环显示8031串行口输出的0~9这10个数字。

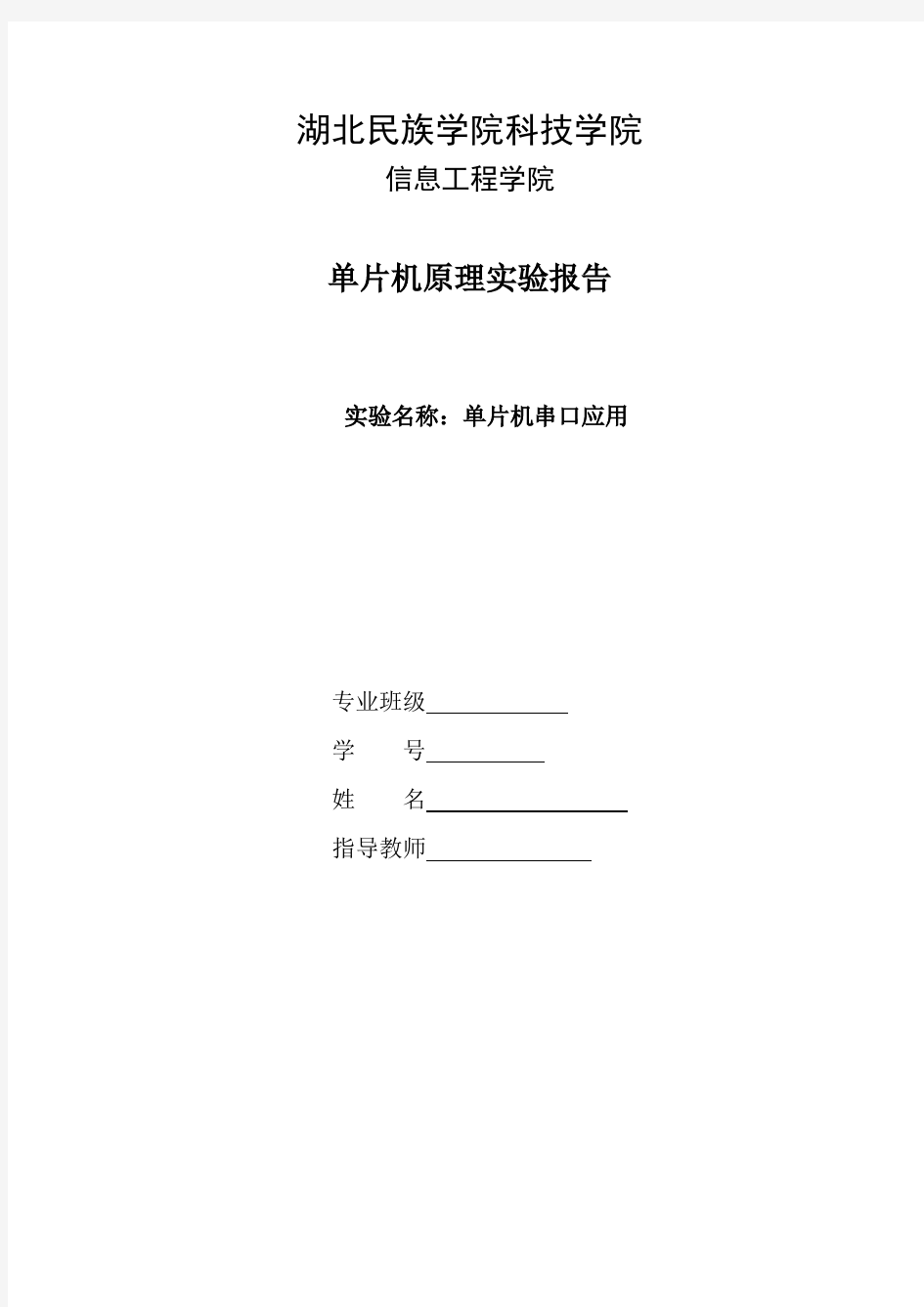

(2)用Proteus软件参照实验电路连线并仿真运行,得出与实验箱上相同的软件仿真结果。

所用元器件:单片机AT89C51、串入并出移位寄存器74LS164、数码管7SEG-COM-CAT-GREEN(BLUE) 参考仿真电路图:

三、实验说明

串行口工作在方式0时,可通过外接移位存储器实现串并行转换。在这种方式下,数据为8位,只能从RXD端输入输出,TXD端总是输出移位同步时钟信号,其波特率固定为晶振频率1/12。由软件置位串行控制寄存器(SCON)的REN后才能启动串行接收,在CPU将数据写入SBUF寄存器后,立即启动发送。待8位数据输完后,硬件将SCON寄存器的TI位置1,TI必须由软件清零。

共阳极数码管的0~9的显示码如下:0x03,0x9F,0x25,0x0D,0x99,0x49,0x41,0x1F,0x01,0x09

四、实验步骤

⑴将串并单元DATA插孔接P3.0插孔。

⑵将串并单元CLK插孔接P3.1插孔。

⑶将串并单元CLR插孔接地址线A9下方CLR插孔。上电时对164复位。

⑷执行程序

⑸在串并单元数码管上循环显示0~9这10个数字。

五、实验电路(图中粗实线)

六、程序框图

实验程序清单:

#include

#define uchar unsigned char #define uint unsigned int

uint num,i=0; //全局变量定义

uchar code Table[]={0x03,0x9F,0x25,0x0D,0x 99,

0x49,0x41,0x1F,0x01,0x09}; //共阳数码管字段 void main()

{ TMOD=0x01; //定时器T0方式1

TH0=(65536-50000)/256;//定时器赋初值,定时100ms ,(12MHz 晶振) TL0=(65536-50000)%256; EA=1; //总中断打开 ET0=1; //开定时器0中断 TR0=1; //启动定时器0 SCON=0x00;

while(1); //程序停在此处,等待下一次中断 }

void T0_() interrupt 1 //中断服务子程序 {

TH0=(65536-50000)/256; //定时器重赋初值

TL0=(65536-50000)%256; num++;

if(num==10) //定时1S 时间到 {

num=0; i++;

if(i==10) i=0; //数码管反复扫描

SBUF=~Table[i]; //取反,送数码管显示数字 } }

实验四(二)单片机与PC机串行通信实验(2学时)

一、实验目的

⑴掌握串行口工作方式的程序设计,掌握单片机通信程序编制方法。

⑵了解实现串行通信的硬环境,数据格式的协议,数据交换的协议。

⑶了解PC机通信的基本要求。

二、实验内容

(1)在实验箱上实现:

利用8031单片机串行口,实现与PC机通信。将“PC机发送程序”上的字符(0~F)显示到实验仪的数码管上。

(2)用Proteus软件参照实验电路连线并仿真运行,得出与实验箱上相同的软件仿真结果。

所用元器件:单片机AT89C51、8位锁存器74LS273或74LS373、3-8译码器74LS138、排阻或电阻RESPACK-8(RES)、或非门74LS02、共阳极六合一数码管7SEG-MPX6-CA以上是“时钟显示实验”电路。

另外增加:TTL和RS232电平转换芯片MAX232、RS232串口COMPIM、串口通信仿真器VIRTUAL TERMINAL 参考仿真电路图:(显示字符的ASCII码值)

三、实验电路及连线

实验时需将8032串行接收信号线P3.0(RXD)连到实验仪右上角RX0插孔;8031的P3.1(TXD)连到实验仪右上角TX0插孔上;使用通信电缆连接PC机与实验仪。

四、程序流程

五、实验步骤

注意:进行本实验时请把通信选择开关拨至最左面一位。

(一)PC机发送,实验仪接收

(1) 若在联机状态,请先装载程序代码至实验系统(生成HEX文件后,点击“start/stop debug session”按钮将程序装载到实验箱中);

(2) 装载完毕后,点击“start/stop debug session”按钮,此时将退出Debug环境,并结束对实验

箱串口的占用,将实验系统的通信选择开关拨至最左边(波特率2400bps)并按复位;

(3) 开始运行程序,在实验系统键盘上按下[EXEC]键(实验箱键盘右上角);

(4) 打开Dais软件工作目录(如:C:\Dais),找到并运行“PC发送程序”,选择与实验仪相连的串口

(本实验使用的是默认波特率2400bps),单击“打开串口”按钮;

(5) 从“PC发送程序”单击0~F按钮发送相关字符,相应的数字会显示在实验系统的数码管上。

(二)实验仪发送,PC机接收

(1) 若在联机状态,请先装载程序代码至实验系统(生成HEX文件后,点击“start/stop debug session”

按钮将程序装载到实验箱中);

(2) 装载完毕后,点击“start/stop debug session”按钮,此时将退出Debug环境,并结束对实验

箱串口的占用,将实验系统的通信选择开关拨至最左边(波特率2400bps)并按复位;

(3) 打开Dais软件工作目录(如:C:\Dais),找到并运行“PC接收程序”,选择与实验仪相连的串口(本实验使用的是默认波特率2400bps),单击“打开串口”按钮;

(4) 开始运行程序,在实验系统键盘上按下[EXEC]键(实验箱键盘右上角);

(5) 将预先存放在存储器中的数字0~F通过单片机串口发出,“PC接收程序”会将接收到的字符显示在PC机屏幕上。

程序清单

1.从“PC发送程序”单击0~F按钮发送相关字符,相应的数字0—15会显示在实验系统数码管上。

#include

#include

#define uint unsigned int

#define uchar unsigned char

#define ZX XBYTE[0xffdc] //字形口端口地址宏定义

#define ZW XBYTE[0xffdd] //字位口端口地址宏定义

uchar value,n;//全局变量定义

uchar buffer[6]={0,0,0,0,0,0};

uchar code table[]=

{0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0 x80,0x90,0x88,0x83,0xc0,0xa1,0x86

,0x8e}; //共阳数码管字段

uchar code table2[]={0x20,0x10,0x08,0x04,0x 02,0x01}; //数码管字位

void display(uchar n); //数码管显示子函数声明,并且带参数返回

void delay(uint); //延时子函数的声明

void main()

{

SCON=0x40; //串口方式1,未开

REN

PCON=0x80; //SMOD=1

TMOD=0x20; //T1方式2(为可重装)

TH1=243; //计数初值

TL1=243; //2400322*)25612fosc SMODN波特率

TR1=1; //打开定时器1

while(1) //一直执行

{ SCON=0x50; //开

REN

while(!RI)

display(n);

RI=0; //RI需要手动清

n=SBUF;

SCON=0x40; //关

REN

}

}

void delay(uint x) //延时子函数的定义

{

uint i,j;

for(i=x;i>0;i--)

for(j=10;j>0;j--);

}

void display(uchar n) //数码管显示子函数定义,并且带参数返回

{

buffer[0]=n/10;//0—15数位分解,送给数码管显示

buffer[1]=n%10;

ZX=table[buffer[0]]; //显示十位,先送字形ZW=table2[0]; //再送字位

delay(10); //延时一小段时间

ZX=0xff; //数码管消影

ZX=table[buffer[1]]; //显示个位

ZW=table2[1];

delay(10); //延时一小段时间

ZX=0xff; //数码管消影

}

六、思考

(1)试分别使用查询和中断2中方式实现“PC机发送,实验仪接收”的功能。(2)试完成“实验仪发送,PC机接收”部分的编程并实现该功能。

思考题源程序:#include

#include

#define uint unsigned int

#define uchar unsigned char

#define ZX XBYTE[0xffdc] //字形口端口地址宏定义

#define ZW XBYTE[0xffdd] //字位口端口地址宏定义

uchar value,n;//全局变量定义

uchar buffer[6]={0,0,0,0,0,0};

uchar code table[]=

{0xc0,0xf9,0xa4,0xb0,0x99,0x92,0x82,0xf8,0 x80,0x90,0x88,0x83,0xc0,0xa1,0x86

,0x8e}; //共阳数码管数字

uchar code table2[]={0x20,0x10,0x08,0x04,0x 02,0x01};

void display(uchar n);//数码管显示子函数的声明,并且带参数返回

void delay(uint); //延时子函数的声明

void main()

{

SCON=0x40; //串口方式1,未开

REN

PCON=0x80; //SMOD=1

TMOD=0x20; //T1方式2(8为可重装) TH1=243; //计数初值

TL1=243; //2400322*)256(12fosc SMODN波特率

TR1=1; //打开定时器1

while(1) //一直执行

{

SCON=0x50; //开

REN

while(!RI)

display(n);

RI=0; //RI需要手动清0

n=SBUF;

SCON=0x40; //关

REN

}

}

void delay(uint x) //延时子函数的定义

{

uint i,j;

for(i=x;i>0;i--)

for(j=10;j>0;j--);

}

void display(uchar n) //数码管显示子函数的定义,并且带参数返回

{ //z字母的ASCII值为127,下面数位分解

buffer[0]=n/100; //百位

buffer[1]=n%100/10; //十位

buffer[2]=n%10; //个位

ZX=table[buffer[0]]; //显示ASCII的百位,先送字形

ZW=table2[0]; //再送字位

delay(10); //延时一小段时间

ZX=0xff; //

数码管消影

ZX=table[buffer[1]]; //显示ASCII的十位ZW=table2[1];

delay(10);

ZX=0xff;

ZX=table[buffer[2]]; //显示ASCII值的个位ZW=table2[2];

delay(10);

ZX=0xff; //数码管消影

}

注意:可以显示大写字母,小写字母,0—的ASCII值

DA转换实验

实验九 D/A转换实验 一、实验目的 1、熟悉D/A转换的基本原理; 2、掌握AD7303的技术指标和常用方法; 3、熟悉DSP的SPI的应用方法; 4、掌握并熟练使用DSP和AD7303的接口及其操作。 二、实验设备 计算机,CCS 2.0版软件,DSP仿真器,EXP4实验箱,F2812CUP板,示波器。 三、实验原理 DA转换芯片采用Analog Devices公司的AD7303。该芯片是单极性、双通道、串行、8位DA转换器,操作串行时钟最快可达30M,DA转换时间1.2μs采用SPI串行接口和DSP连接。DA 输出通过放大电路,可以得到0~5V的输出范围。DA输出接口在“CPLD单元”的左上角,两个2号孔“D/A输出1、D/A输出2”分别对应AD7303的“OUTA、OUTB”。下面是AD7303的功能框图: 引脚说明: 1、VOUTA:模拟输出A 2、电源 +2.7~+5.5V 3、地 4、REF:参考电压 5、SCLK:数字接口位时钟 6、DIN:数字接口数据 7、SYNC:数字接口片选 8、VOUTB:模拟输出B 接口时序:

输入的数字量和输出电压的关系: 四、实验步骤与内容 1、开关K9拨到右边,即仿真器选择连接右边的CPU:CPU2;运行CCS软件,加载示 范程序; 2、按F5运行程序,用示波器检测“D/A转换单元的的2号孔接口“输出1”输出一个 正弦波;

3、填写实验报告。 4、样例程序实验操作说明 启动CCS 2.0,打开EXP4_09_da目录下面的工程文件“Example_281x_da.pjt”,并加载Example_281x_da.out文件,双击“Source”,可查看源程序。 5、在源文件中“SpiaRegs.SPITXBUF=curve1[p];”处设断点,点击RUN运行程序;

串转并转换器1

一、题意分析及解决方案 1、课程设计名称及内容 应用STAR ES598PCI单板开发机系列接口芯片设计一个串转并转换器,熟悉串转并转换原理,掌握使用串并转换芯片扩展I/O口的实现方法。设计编写程序,循环点亮8个指示灯瞬间只有一个灯亮。观察实验结果,验证串并转换数据的正确性。 2、题意需求分析 根据题目给定的内容与要求可得:本实验需要用到的主要是控制数据输入的芯片、实现串并转换的芯片和用于显示的发光管。 本实验的核心部分是8位移位寄存器74HC164,它可以实现数据的串行输入和并行输出,达到数据从串行转换为并行的目的。为了方便控制74HC164的输入,考虑运用可编程接口芯片8255连接CPU和74HC164,实现数据的串行输入和CP脉冲的变化。同时,为了方便观察实验结果,使用74HC164移位寄存器输出接口连接8位发光二极管,显示并行输出结果。 3、解决问题的思路与方法 (1)硬件部分 程序用到的硬件芯片有8255、74HC164、发光二极管: 使用8255作为CPU和移位寄存器之间的接口电路来控制8位串行数据的输入,其本身的接口就可以支持输出的操作。而且8255的可编程并行接口,具有传输速度快效率高等优点,不需要附加外部电路便可和大多数并行传输数据的外部设备相连,数据的各位同时传送,使用十分方便。 74HC164是8位移位寄存器,当其中一个(或二个)选通串行输入端的低电平禁止进入新数据,并把第一个触发器在下一个时钟脉冲来后复位到低电平时,门控串行输入端(A 和B) 可完全控制输入数据。一个高电平输入后就使另一个输入端赋能,这个输入就决定了第一个触发器的状态。虽然不管时钟处于高电平或低电平时,串行输入端的数据都可以被改变,但只有满足建立条件的信息才能被输入。时钟控制发生在时钟输入由低电平到高电平的跃变上。为了减小传输线效应,所有输入端均采用二极管钳位。时钟 (CP) 每次由低变高时,数据右移一位,输入到 Q0, Q0 是两个数据输入端(DSA 和 DSB)的逻辑与,它将上升时钟沿之前保持一个建立时间的长度。主复位 (MR) 输入端上的一个低电平将使其它所有输入端都无效,同时非同步地清除寄存器,强制所有的

单片机串并口转换实验定稿版

单片机串并口转换实验 HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】

我也是刚入手单片机,今天编了一段小程序,就是关于单片机串口转并口和并口转串口的一个小实验,本程序在PTOTUES中完美运行。在单片机开发试板上也是完美运行。今天贴出来供大家分享,看完本历程,有助于提高您对单片机IO口的基本操作,锁存器的用法以及串并转换的使用技能 #include

#include

void delay(ulong X) //延时函数,采用了形参传递函数{ while(X--); } /**************************************************/ void LED(); //函数声明 /**************************************************/ void main() //主函数 { while(1) { LED (); } }

实验八 串转并与并转串实验

贵州大学实验报告纸 实验八串转并与并转串实验 一、实验目的 1.掌握使用74LS164扩展输出的方法。 2.掌握使用74LS165扩展输入的方法。 二、实验内容 1、使用74LS165扩展输入数据,使用74LS164扩展输出数据。74LS165的并行口 接八位逻辑电平输出(开关),CPU使用P1.0、P1.1和P1.2串行读入开关状态;74LS164的并行口接一只数码管,CPU使用P1.3和P1.4串行输出刚读入的开关状态,使之在数码管上显示出来。 2、拨动开关,在数码管显示0~9,A~F。 三、实验要求 1、根据实验内容编写一个程序,并在实验仪上调试和验证。 四、实验说明和电路原理图 1)74LS165为8位移位寄存器,其引脚功能如下: S/L:移位/置数端,低电平有效。 P0~P7:并行数据输入端。 QH:串行数据输出端。 CLK、CKLINH:时钟信号输入端。 2)74LS164为串行输入并行输出移位寄存器,其引脚功能如下: A、B:串行输入端; Q0~Q7:并行输出端; MR:清零端,低电平有效; CLK:时钟脉冲输入端,上升沿有效。 3)用P1端口输出数据时,要编程位移数据,每操作一个数据位,对应一个移位脉冲。 4)本实验需要用到CPU模块(F3区)、八位逻辑电平输出模块(E4区)和静态数码管显示模块(B4区)。74LS165电路原理图参见图8-1,74LS164电路原理图参见图8-2。 注:74LS164集成电路芯片在主板反面。

图8-1 74LS165电路 五、实验程序 ;//**************************************************************** ;//*文件名:164165 串转并,并转串实验程序 ;功能:把开关量通过74**165串行输入到内存,并通过74**164串行输出到数; 码管上显示。 ;接线:P1.0接QH165,P1.1接CLK165,P1.2接SH_LD, ; P1.3、P1.4接静态数码显示的DIN、CLK。 ;//**************************************************************** QH165 BIT P1.0 CLK165 BIT P1.1 SH_LD BIT P1.2 DAT164 BIT P1.3 CLK164 BIT P1.4 MEMORY EQU 30H

verilog实现串并并串转换的代码和仿真结果

题目:串并互换电路的设计 系(部):*** 专业班:*** 姓名:*** 学号:*** 指导教师:*** 完成比例:** 2011年12 月

摘要 本文主要讲述用verilog实现串并互换电路,在同步时钟的控制下,四位的并行数据和串行数据相互转换,通过一位的控制信号来控制该电路为串并或并串转换,最后由串并有效位来表示串并互换成功。 关键词:串转并并转串移位寄存器

Abstract This paper deals with verilog realize string and swap circuit, in synchronous clock under the control of four parallel data and serial data transformation, through a control signals to control the circuit for the series and or and string of conversion, finally by string and effective to say a string and swap success. Key W ords:Parallel turns to serial serial turns to parallel Shift register

目录 摘要.............................................................................................................................................................................. I ABSTRACT ..................................................................................................................................................................... II 1 选题背景. (1) 1.1本课题的意义 (1) 2 方案论证 (2) 2.1串并并串选择的分析 (2) 2.2串并并串转换是否成功的标志位及表达 (2) 3、程序的具体实现及仿真结果 (3) 4、本人完成部分及对该部分的理解 (9) 5结论或总结 (9) 致谢 (10) 参考文献 (10)

串并转换

实验五串并转换实验 一、实验目的 1、掌握串并行转换的原理及采用74LS164扩展端口的方法。 2、掌握数码管显示的原理及方法。 3、学习用任意两根I/O口线进行数据传输的方法。 二、实验要求 利用实验箱的显示电路,在数码管上循环显示0-9这10个数,每个数显示1秒。完成后修改程序,仅在一个数码管上显示0-F这16个数(其它三个数码管不显示)。 三、实验原理 实验设备中数码管为共阴接法,接线确定了各段从左 至右的排列顺序为:abcdefgh。如果要显示数字1,应该 是b c段发光,所以b c段对应的位写1,其它不发光的位写0。因此1的显示码为 60H。其它显示码可按此规律得出。 实验原理图见图二,串并转换芯片74LS164的A、B端为串行数据输入端,将其接到数据线P1.0上,CLK为时钟端接到时钟线P1.1上,Q0~Q7为并行输出端接数码管。在P1.1产生的时钟脉冲的作用下,数据的显示码从74LS164输入端一位一位的输入,经164转换后,串行数据变为8位并行数据经其输出端Q0~Q7加到数码管上,数码管就能显示相应的数字。 下面是数据60H的传输及显示过程: 1、将A中数据的最低位送到串口的数据线P1.0上。 2、在时钟线P1.1上产生一个脉冲。 3、在这个脉冲的作用下,P1.0上的数据被打入164的Q0输 出端,原来Q0上的数据移到Q1,Q1的数移到Q2…, 完成一位数的传输。 4、第1步到第3步重复8次,这样一个字节的数据就输出 完毕,同时74LS164将接收到的串行数据转换成并行数据 在数码管上显示出来。 四、实验框图 实验框图见图一。 五、实验连线及步骤 1、DIN接P1.0,CLK接P1.1,打开实验箱电源,打开串并 转换数码管显示模块上的开关。 2、启动KEIL软件界面,根据框图编程。 在初始化框中有两个内容,它们分别是: * 送表指针初值---寄存器 MOV R1,#0 * 送表首地址---DPTR 图一串并转换程序框图

串转并和并转串实验

实验五串转并与并转串实验 一、实验目的 1.掌握使用74LS164 扩展输出的方法。 2.掌握使用74LS165 扩展输入的方法。 二、实验内容 使用74LS165 扩展输入数据,使用74LS164 扩展输出数据。74LS165 的并行口接八位逻辑电平输出(开关),CPU 使用P1.0、P1.1 和P1.2 串行读入开关状态;74LS164 的并行口接一只数码管,CPU 使用P1.3 和P1.4 串行输出刚读入的开关状态,使之在数码管上显示出来。 三、实验要求 根据实验内容编写一个程序,并在实验仪上调试和验证。 四、实验说明和电路原理图 1)74LS165 为8 位移位寄存器,其引脚功能如下: S/L:移位/置数端,低电平有效。 P0~P7:并行数据输入端。 QH、QH:串行数据输出端。 CLK、CKLINH:时钟信号输入端。 2)74LS164 为串行输入并行输出移位寄存器,其引脚功能如下: A、B:串行输入端; Q0~Q7:并行输出端; MR:清零端,低电平有效; CLK:时钟脉冲输入端,上升沿有效。 3)用P1 端口输出数据时,要编程位移数据,每操作一个数据位,对应一个移位脉冲。 4)本实验需要用到CPU 模块(F3 区)、八位逻辑电平输出模块(E4 区)和静态数码管显示模块(B4 区)。74LS165 电路原理图参见图5-1,74LS164 电路原理图参见图8-2。 注:74LS164 集成电路芯片在主板反面。 图5-1 74LS165 电路

图5-2 74LS164电路 五、实验步骤 1)系统各跳线器处在初始设置状态。 用导线对应连接八位逻辑电平输出模块的QH165、CLK165、SH/LD 到CPU 模块的P10、P11、P12。用导线对应连接静态数码管显示模块的DIN、CLK 到CPU 模块的P13、P14。 2)启动PC 机,打开THGMW-51 软件,输入源程序,并编译源程序。编译无误后,下载程序运行。 3)观察数码(八段码)管的亮灭与拨动开关的状态是否一致。拨动开关拨下输出为低电平,段码点亮。 QH165 BIT P1.0 ;位定义 CLK165 BIT P1.1 SH_LD BIT P1.2 DAT164 BIT P1.3 CLK164 BIT P1.4 MEMORY EQU 30H ORG 0000H AJMP START ORG 00B0H START: SETB CLK165 ;开关数据置入165 CLR SH_LD ;低电平置数 SETB SH_LD ;高电平移位 MOVR7, #8 Input: RRA MOVC, QH165 ;读数 MOV ACC.7, C ;把C送到累加器最高位 CLR CLK165 ;脉冲

LS164串进并出实验及165并串转换实验

2、165并串转换实验。 (1)74LS165芯片引脚图 管脚说明: D0 through D7 --Parallel in puts SI -- Serial in put Q7,/Q7 -- Data outputs CLK -- Clock CKIN -- Clock in hibit S/L --(高有效)Shift/Parallel-load 实验二 74LS164串进并出实验及165并串转换实验 一、 实验目的 1 、了解74LS164芯片的工作原理,以及与单片机的接口方法。 2、掌握单片机串行口的工作原理以及编程方法。 3 、了解74LS165芯片的工作原理。 4、掌握74LS165芯片在单片机系统中的应用及编程。 二、 实验内容 1、 用74LS164芯片扩展并行输出口,本实验中我们用 74LS164扩展两个8位输出口的 接口显示电路,两位数码管循环显示 00~99之间的数字。 2、 利用实验系统上的 74LS165芯片,编程实现8位数据并行输入,串行口串行接收, 并将接收的数据存放在 CPU 内部存储区50H~59H 中,共10个数据。(并行输入数据由P1 口 来送入) 三、 编程指南 1、74LS164串进并出实验。 (1) 本实验中MCS-51单片机串行口工作在方式 0 (移位寄存器方式,用于并行 I/O 口 扩展)的发送状态时,串行数据由 P3.0(RXD )送出,移位时钟由 P3.1( TXD 送出。在移位 时钟的作用下,串行口发送缓冲器的数据一位一位地移入 74LS164中。需要指出的是,由于 741S164无并行输出控制端,因而在串行输入过程中,其输出端的状态会不断变化,故在某 些应用 场合,在74LS164的输出端应加接输出三态门控制, 以便保证串行输入结束后再输出 数据。 (2) 74LS164引脚功能图 管脚说明: SIA 、SIB --- Serial in puts Q0 through Q7 ---- Data outputs CLK ---- CLOCK CLR ——Clear in put 功能表: VCC Q7 08 Q5 射 CLK CLK | K I ] nJ 17 10 * | T 7ns 16^1 □J 2 jj LsJ LzJ SIA 5IB QQ QI Q? Q3 ENJ S/L CP D4 D5 D6 DT /Q7 GND

实验四(一) 串并转换实验(2学时)

湖北民族学院科技学院 信息工程学院 单片机原理实验报告 实验名称:单片机串口应用 专业班级 学号 姓名 指导教师

实验四(一)串并转换实验(2学时) 一、实验目的 ⑴掌握8031串行口方式0工作方式及编程方法。 ⑵掌握利用串行口扩展并行I/O通道的方法。 二、实验内容 (1)在实验箱上完成: 利用8031串行口和串行输入并行输出移位寄存器74LS164,扩展一个8位输出通道,用于驱动一个共阳极数码显示器,在数码显示器上循环显示8031串行口输出的0~9这10个数字。 (2)用Proteus软件参照实验电路连线并仿真运行,得出与实验箱上相同的软件仿真结果。 所用元器件:单片机AT89C51、串入并出移位寄存器74LS164、数码管7SEG-COM-CAT-GREEN(BLUE) 参考仿真电路图: 三、实验说明 串行口工作在方式0时,可通过外接移位存储器实现串并行转换。在这种方式下,数据为8位,只能从RXD端输入输出,TXD端总是输出移位同步时钟信号,其波特率固定为晶振频率1/12。由软件置位串行控制寄存器(SCON)的REN后才能启动串行接收,在CPU将数据写入SBUF寄存器后,立即启动发送。待8位数据输完后,硬件将SCON寄存器的TI位置1,TI必须由软件清零。 共阳极数码管的0~9的显示码如下:0x03,0x9F,0x25,0x0D,0x99,0x49,0x41,0x1F,0x01,0x09 四、实验步骤 ⑴将串并单元DATA插孔接P3.0插孔。 ⑵将串并单元CLK插孔接P3.1插孔。 ⑶将串并单元CLR插孔接地址线A9下方CLR插孔。上电时对164复位。 ⑷执行程序 ⑸在串并单元数码管上循环显示0~9这10个数字。 五、实验电路(图中粗实线)

LTC1196ADC输出串并转换电路

实验二 LTC1196ADC 输出串并转换电路 一、 实验要求 利用状态机等设计将LTC1196(ADC )的串行输出数据转换成并行数据的转换电路,ADC 的时钟由转换电路提供,CS 信号由转换电路处理后提供给ADC ,以保证LTC1196的时序要求。 二、 实验原理 利用状态机的方法设计,通过资料得知LTC1196的工作频率为1MHz ,同时把系统时钟也设置为1MHz ,2个片选信号之间间隔为12个工作频率,因此将状态在内的12个状态,在初始状态st0中将所有的信号量初始化,在st1-st4中为采集模拟量时间,转换电路空操作,在st5-st12状态中将ADC 转换的串行数字量保存给中间变量。 图1 LTC1196-2B 时序图 从时序图可以知道:采样时间t SMPL 至少为2.5个f CLK ,单次转换时间不少于12个f CLK ;片选下降沿离上一CLK 上升沿至少13ns ,离下一CLK 上升沿,CS 建立时间至少26ns ;时钟频率f CLK 不高于12MHz 。转换关系为 V V DATA in 5/255?= 下图为该状态机的状态图 suCS t

下面第程序中的参数作简要的介绍: enable:转换电路使能端,由FPGA控制 start:LTC1196使能端 din:LTC1196的串行数字端 dout:并行输出端 rst:异步复位端 fclk:系统时钟接入端,1MHz busy:转换工作中,当采集模拟量的时候为高电平 adok:转换结束,可以通知FPGA取数 三、实验程序 library ieee; use ieee.std_logic_1164.all; entity adc is port (fclk,enable,din,rst:in std_logic; dout:out std_logic_vector(7 downto 0); busy,start,adok:out std_logic); end entity adc; architecture behav of adc is type states is (st0,st1,st2,st3,st4,st5,st6,st7,st8,st9,st10,st11); --12个状态 signal count: integer range 0 to 49; --50分频的常量 signal current_state:states; signal next_state:states; signal data:std_logic_vector(7 downto 0); --传输数据的中间量 signal rise:std_logic; --rise通知FPGA可以取数上升沿有效signal serok:std_logic; --LTC1196模拟量采样完毕信号 signal sample:std_logic; --模拟变换数字后的中间量

74LS164串进并出实验及165并串转换实验

74L S164串进并出实验及165并串转换实 验 -CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN

实验二 74LS164串进并出实验及165并串转换实验 一、实验目的 1、了解74LS164芯片的工作原理,以及与单片机的接口方法。 2、掌握单片机串行口的工作原理以及编程方法。 3、了解74LS165芯片的工作原理。 4、掌握74LS165芯片在单片机系统中的应用及编程。 二、实验内容 1、用74LS164芯片扩展并行输出口,本实验中我们用74LS164扩展两个8位输出口的接口显示电路,两位数码管循环显示00~99之间的数字。 2、利用实验系统上的74LS165芯片,编程实现8位数据并行输入,串行口串行接收,并将接收的数据存放在CPU内部存储区50H~59H中,共10个数据。(并行输入数据由P1口来送入) 三、编程指南 1、74LS164串进并出实验。 (1)本实验中MCS-51单片机串行口工作在方式0(移位寄存器方式,用于并行I/0口扩展)的发送状态时,串行数据由P3.0(RXD)送出,移位时钟由P3.1(TXD)送出。在移位时钟的作用下,串行口发送缓冲器的数据一位一位地移入74LS164中。需要指出的是,由于741S164无并行输出控制端,因而在串行输入过程中,其输出端的状态会不断变化,故在某些应用场合,在74LS164的输出端应加接输出三态门控制,以便保证串行输入结束后再输出数据。 (2)74LS164引脚功能图 管脚说明: SIA、SIB --- Serial inputs Q0 through Q7 ---- Data outputs CLK ---- CLOCK CLR ---- Clear input

实验四 串行AD转换实验

南昌大学实验报告 学生姓名:学号:专业班级: 实验类型:□验证□综合□√设计□创新实验日期:实验成绩: 实验四串行A/D 转换实验 一、实验目的 1.熟悉八位串行AD转换器TLC549的性能及转换过程。 2.掌握单片机和TLC549硬件联接及软件编程。 二、实验内容 使用TLC549 实现单片机模数转换。模拟信号为0~5V 电位器分压输出,单片机读取模拟信号,并在数码管上用十六进制形式显示出来。 三、实验要求 根据实验内容编写一个程序,并在实验仪上调试和验证。四、实验说明和电路原理图TLC549是一种采用8位逐次逼近式工作的A/D转换器。内部包含系统时钟、采样和保持、8 位A/D转换器、数据寄存器以及控制逻辑电路。TLC549每25uS重复一次“输入——转换——输出”。器件有两个控制输入:I/O CLOCK和片选(CS)。 内部系统时钟和I/O CLOCK可独立使用。应用电路的设计只需利用I/O时钟启动转换或读出转换结果。当CS为高电平时,DA TA OUT处于高阻态且I/O时钟被禁止。当CS变为低电平时,前次转换结果的?高有效位(MSB)开始出现在DA TA OUT端。在接下来的7个I/O CLOCK周期的下降沿输出前次转换结果的后7位,至此8位数据已经输出。然后再将第8 个时钟周期加至I/O CLOCK,此时钟周期的下跳沿变使芯片进行下一轮的AD 转换。在第8个I/O CLOCK周期之后,CS必须变为高电平,并且保持高电平直至转换结束为止(>17uS),否则CS的有效高电平至低电平的转换将引起复位(其它详细资料看芯片说明)。本实验需要用到CPU 模块(F3 区)、电位器模块(E2 区)、串行模数转换模块(D5 区)、串行静态数码显示模块(B4 区)。TLC549 串行模数转换电路原理参见下图。

并串串并转换设计

并串/串并转换电路设计 一、实验目的: 用verilog语言设计一个8:1的并串转换电路、设计一个1:8的串并转换电路。 二、实验原理: 实现8位的并行数据转换为串行的数据:并行转串行,只要把每个输入按从高到低的顺序输出即可。即每个时钟脉冲输出一个数据。 实现8位的串行数据转换为并行的数据:8位串行数据转换为并行数据,需要一个模为8的计数器,当计到8个时钟脉冲时,把之前的8个数据全部输出,然后从新接收。 三、实验内容: 用verilog实现8位的并行数据转换为串行的数据: module bingchuan(out,in,rst,clk); output out; reg out; input [7:0] in; input rst,clk; integer i=0; always@(posedge clk) begin if(rst) out<=0; else begin if(i==8) begin out<=0; end else out<=in[i]; i<=i+1; end end endmodule module textbingchuan; reg [7:0] in;

reg rst,clk; wire out; bingchuan bc(out,in,rst,clk); initial clk=1; always #5 clk=~clk; initial begin rst=1; #100 rst=0;in=8'b11101110; end endmodule 仿真后的波形: 用verilog实现8位的串行数据转换为并行的数据:module chuanbing(out,in,rst,clk); output [7:0] out; reg [7:0] out; input in,rst,clk; reg[7:0] temout; reg[2:0] cd; always@(posedge clk) begin if(rst) cd=3'b111; else begin temout[cd]<=in; cd<=cd-1'b1; if(cd==3'b111) begin out<=temout; end

单片机串并转换实验报告

实验五串并转换实验 姓名:赵新专业:通信工程(401)学号:2011412547 成绩: 一、实验目的 1、掌握8051串行口方式0工作方式及编程方法; 2、掌握利用串行口扩展I/O通道的方法; 二、实验内容 1、用Proteus画出仿真电路图。利用8051串行口和串行输入并行输出移位寄存器74LS164 可以进行I/O的扩展,要求以级联的形式用2片74LS164扩展两个8位I/O,驱动两个数码管,电路自行设计。 2、按流程图编写程序,在数码管上循环显示从8051串行口输出的0--9这10个数字。 3、编写程序,利用定时器T0产生1S的定时,通过数码管显示计时时间0~99秒,计到99 秒后再减1计时,即由99~0。 三、实验原理及步骤 1、串行口工作在方式0是时,可通过外接移位寄存器实现串并行转换。在这种方式下,数据为8位,只能从RXD端输入输出,TXD端总是输出移位同步时钟信号,其波特率固定为晶振频率的1/12。由软件置位串行控制寄存器(SCON)的REN后才能启动串行接受,在CPU将数据写入SBUF寄存器后,立即启动发送。待8位数据输入完后,硬件将SCON寄存器的TI位置1,TI必须由软件清零。 2、74LS164:8位串入并出移位寄存器,共有14个引脚。 注意:74LS164接数码管时应接限流电阻(200欧姆左右),否则无法驱动级联的另一块74LS164。 3、实验步骤:1、用proteus设计串并转换电路; 2、在Keil C51中编写控制程序,编译通过后,与Proteus联合调试; 3、连续执行程序,在扩展的数码管上循环显示0~99这10个数字; 4、修改程序,实现加减计时功能。 四、电路设计及调试 1、实验电路

串并转换实验

一、实验内容: (1)在实验箱上完成:利用8031串行口和串行输入并行输出移位寄存器74LS164,扩展一个8位输出通道,用于驱动一个共阳极数码显示器,在数码显示器上循环显示8031串行口输出的0~9这10个数字。 (2)用Proteus软件参照实验电路连线并仿真运行,得出与实验箱上相同的软件仿真结果。 所用元器件:单片机AT89C51、串入并出移位寄存器74LS164、数码管7SEG-COM-CAT-GREEN(BLUE) 二、实验电路及功能说明 串行口工作在方式0时,可通过外接移位存储器实现串并行转换。在这种方式下,数据为8位,只能从RXD端输入输出,TXD端总是输出移位同步时钟信号,其波特率固定为晶振频率1/12。由软件置位串行控制寄存器(SCON)的REN后才能启动串行接收,在CPU将数据写入SBUF寄存器后,立即启动发送。待8位数据输完后,硬件将SCON寄存器的TI位置1,TI 必须由软件清零。共阳极数码管的0~9的显示码如下:0x03,0x9F,0x25,0x0D,0x99,0x49,0x41,0x1F,0x01,0x09 三、实验程序流程图: 主程序:

子程序: 四、实验结果分析 五、心得体会 通过实验让我掌握8031串行口方式0工作方式及编程方法。同时了解和掌握了利用串行口扩展并行I/O通道的方法。 程序清单 #include

串并转换

利用状态机等设计将LTC1196(ADC)的串行输出数据转换成并行数据的转换电路,ADC 的时钟由转换电路提供,CS 信号由转换电路处理后提供给ADC ,以保证LTC1196的时序要求。 1 有限状态机 有限状态机(Finite State Machine )主要用于顺序逻辑电路的建模,在顺序逻辑电路设计中,因不同阶段具有明确的顺序状态,所以其显得非常有用。图1是一个状态机的基本结构。有限状态机的主要功能是用来实现一个数字电路设计的控制部分,其功能和CPU 的功能十分相似。在进行数字系统的电路设计时,如果考虑实现一个控制功能,通常会选择状态机或者是CPU 来实现,但是在执行耗费时间和执行时间的确定性方面,状态机要比CPU 好。 有限状态机可以有多种不同的描述方式。描述状态机的VHDL 代码必须遵守一定的规则。 (1) 至少要包括一个用来指定状态机状态的状态信号; (2) 状态转移指定和输出指定,它们对应于控制单元中与每个控制步有关的 转移条件; (3) 用来进行同步的时钟信号; (4) 复位信号。 使用枚举数据类型来定义状态机的状态,并使用多进程方式来描述状态机的内部逻辑,可以得到高效、可综合的VHDL 状态机描述。状态变量不能是接口或端口信号,而且状态变量的操作只限于等于或不等于的比较操作。在描述有限状态机的过程中常使用的描述方式有单进程方式、双进程方式和三进程方式。三进程方式就是将有限状态机的次态逻辑、状态寄存器和输出逻辑分别使用三个进程来描述。这种描述方式可以把状态机的组合逻辑部分和时序逻辑部分分开,有利于对状态机的组合逻辑部分和时序逻辑部分分别进行测试。双进程描述方式是将有限状态机的次态逻辑、状态寄存器和输出逻辑分别用两个进程来描述。同样一个单进程描述方式就是将有限状态机的次态逻辑、状态寄存器和输出逻辑使用一个进程来描述。 2.LTC1196(ADC) 状态译码器 (组合逻辑) 状态寄存器 (时序逻辑) 输出译码器 状态 图1 状态机的基本结构

单片机串并口转换实验

我也是刚入手单片机,今天编了一段小程序,就是关于单片机串口转并口和并口转串口的一个小实验,本程序在PTOTUES中完美运行。在单片机开发试板上也是完美运行。今天贴出来供大家分享,看完本历程,有助于提高您对单片机IO口的基本操作,锁存器的用法以及串并转换的使用技能 #include

#include< intrins.h > #define uchar unsigned char #define uint unsigned int #define ulong unsigned long code uint a[]={0xfe,0xfd,0xfb,0xf7,0xef,0xdf,0xbf,0x7f}; sbit SO=P1^0; //定义165的输出 sbit STCP=P1^1; sbit DS=P1^2; sbit SHCP=P1^3; sbit SHLD=P1^4; sbit CLK=P1^5; sbit cs573=P1^6; /**************************************************/ void delay(ulong X) //延时函数,采用了形参传递函数

{ while(X--); } /**************************************************/ void LED(); //函数声明 /**************************************************/ void main() //主函数 { while(1) { LED (); } } /****************************************************/

实验四 串并转换与串行通信

单片机实验报告 题目: 实验四串并转换和串行通信班级:0310405 姓名:左立刚 学号: 031040522 指导老师:高林 时间: 2013年6月8日

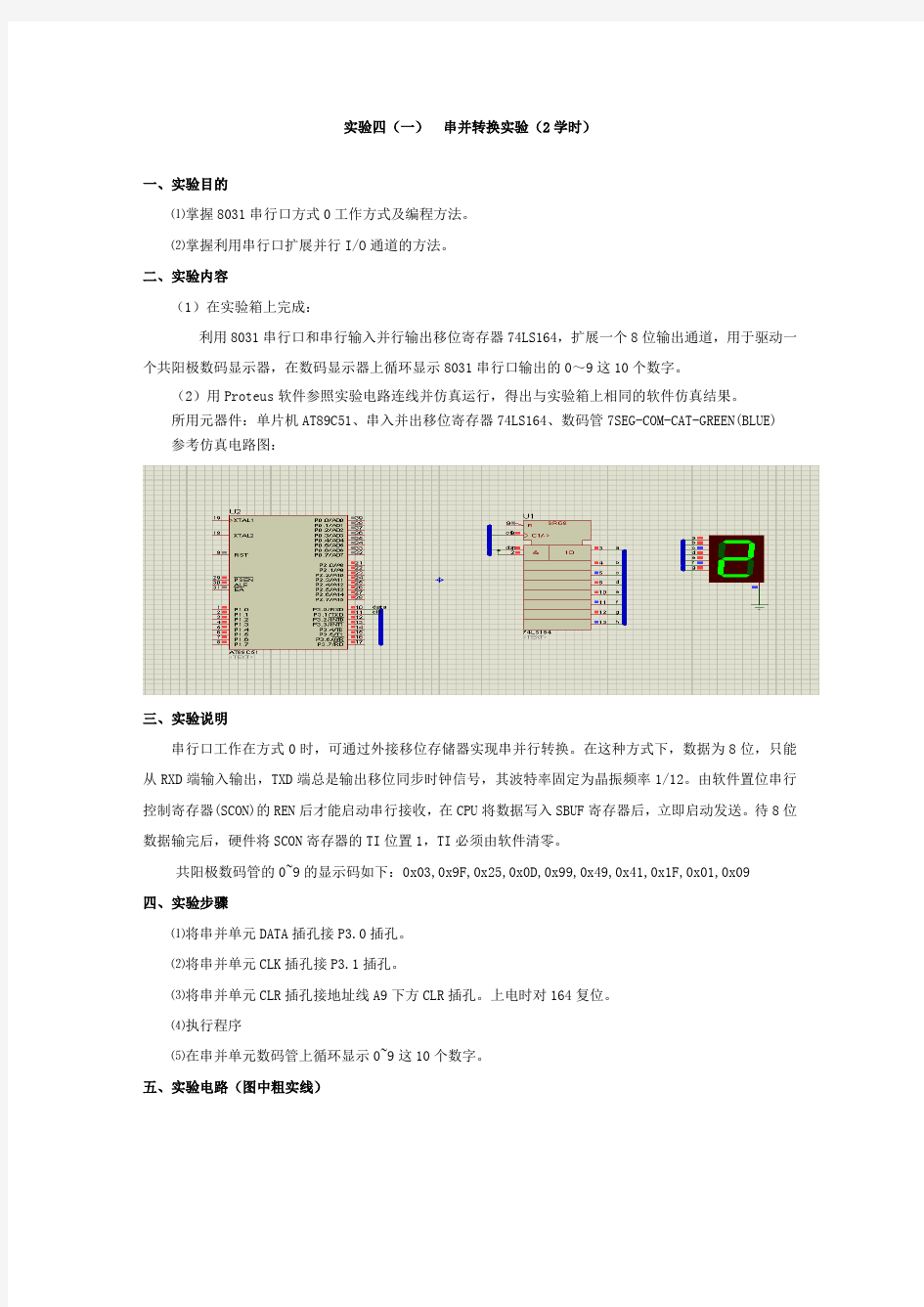

实验四(一)串并转换实验(2学时) 一、实验目的 ⑴掌握8031串行口方式0工作方式及编程方法。 ⑵掌握利用串行口扩展并行I/O通道的方法。 二、实验内容 (1)在实验箱上完成: 利用8031串行口和串行输入并行输出移位寄存器74LS164,扩展一个8位输出通道,用于驱动一个共阳极数码显示器,在数码显示器上循环显示8031串行口输出的0~9这10个数字。 (2)用Proteus软件参照实验电路连线并仿真运行,得出与实验箱上相同的软件仿真结果。 所用元器件:单片机AT89C51、串入并出移位寄存器74LS164、数码管 7SEG-COM-CAT-GREEN(BLUE) 三、实验步骤 ⑴将串并单元DATA插孔接P3.0插孔。 ⑵将串并单元CLK插孔接P3.1插孔。 ⑶将串并单元CLR插孔接地址线A9下方CLR插孔。上电时对164复位。 ⑷执行程序 ⑸在串并单元数码管上循环显示0~9这10个数字。 四、程序框图

五、proteus 仿真图 data clk clk data data a h a g b c d e f b c d e f g XTAL2 18 XTAL1 19 ALE 30EA 31 PSEN 29RST 9 P0.0/AD039P0.1/AD138P0.2/AD237P0.3/AD336P0.4/AD435P0.5/AD534P0.6/AD633P0.7/AD732P1.01P1.12P1.23P1.34P1.45P1.56P1.67P1.78 P3.0/RXD 10P3.1/TXD 11P3.2/INT012P3.3/INT113P3.4/T014P3.7/RD 17 P3.6/WR 16P3.5/T115P2.7/A1528P2.0/A821P2.1/A922P2.2/A1023P2.3/A1124P2.4/A1225P2.5/A1326P2.6/A1427U1 AT89C51 SRG8R C1/-> &1D 13 2 456108 1112913 U2 74LS164 六、程序清单: #include

串行DA转换实验

实验一串行D/A转换实验 实验目的 1、了解串行D/A TLC5615的功能与特性 2、理解串行D/A TLC5615的工作时序 3、掌握串行D/A TLC5615驱动程序编程 实验仪器 单片机开发板、万利仿真机、稳压电源、计算机 实验原理 1、TLC5615功能与特性 TLC5615为美国德州仪器公司1999年推出的产品,是具有串行接口的数模转换器,其输出为电压型,最大输出电压是基准电压值的两倍。带有上电复位功能,即把DAC寄存器复位至全零。其特点有: (1)10位CMOS电压输出; (2)5V单电源供电; (3)与CPU三线串行接口; (4)最大输出电压可达基准电压的二倍; (5)输出电压具有和基准电压相同极性; (6)建立时间12.5μs; (7)内部上电复位; (8)低功耗,最大仅1.75mW。 TLC5615内部结构图如图4-34所示。 图4-34 TLC5615内部结构图 2、TLC5615的时序 TLC5615接口时序兼容SPI、QSPI、WSPI、Microwire。如图4-35所示。

图4-35 TLC5615接口时序图 当片选信号有效时,串行接口可以输入数据。从图可知看出,当SCLK 的正脉冲锁存输入的数据。串行数模转换器TLC5615的使用有两种方式,即级联方式和非级联方式。如不使用级联方式,DIN 只需输入12位数据。DIN 输入的12位数据中,前10位为TLC5615输入的D/A 转换数据,且输入时高位在前,低位在后,后两位必须写入数值为零的低于LSB 的位,因为TLC5615的DAC 输入锁存器为12位宽。如果使用TL5615的级联功能,来自DOUT 的数据需要输入16位时钟下降沿,因此完成一次数据输入需要16个时钟周期,输入的数据也应为16位。输入的数据中,前4位为高虚拟位,中间10位为D/A 转换数据,最后2位为低于LSB 的位为零。如图4-36所示。 图4-36 TLC5615数据格式 3、 TLC5615串行D/A 电路连接 实验电路如图4-37所示。TLC5615的片选信号由 P2口经74LS138译码后给定。时钟线,数据线分别接 P1.7、P1.5。参考电源为2.048V ,这时输出电压最大值 是4.096V 。当需要级联时,只需把TLC5615的第4脚 接到第2片的数据输入,时钟端、片选端只需并联即可。 4、 TLC5615驱动程序设计 TLC5615的驱动程序主要是用软件模拟SPI 接口 (也可以用STC12C 系例单片机的SPI 接口输出)。首先 设计出一次串行输出8位的SPI 子程序,然后再按TLC5615规定的格式输出数据。流程图 图4-38 TLC5615驱动程序流程图 图4-37 TLC5615电路板