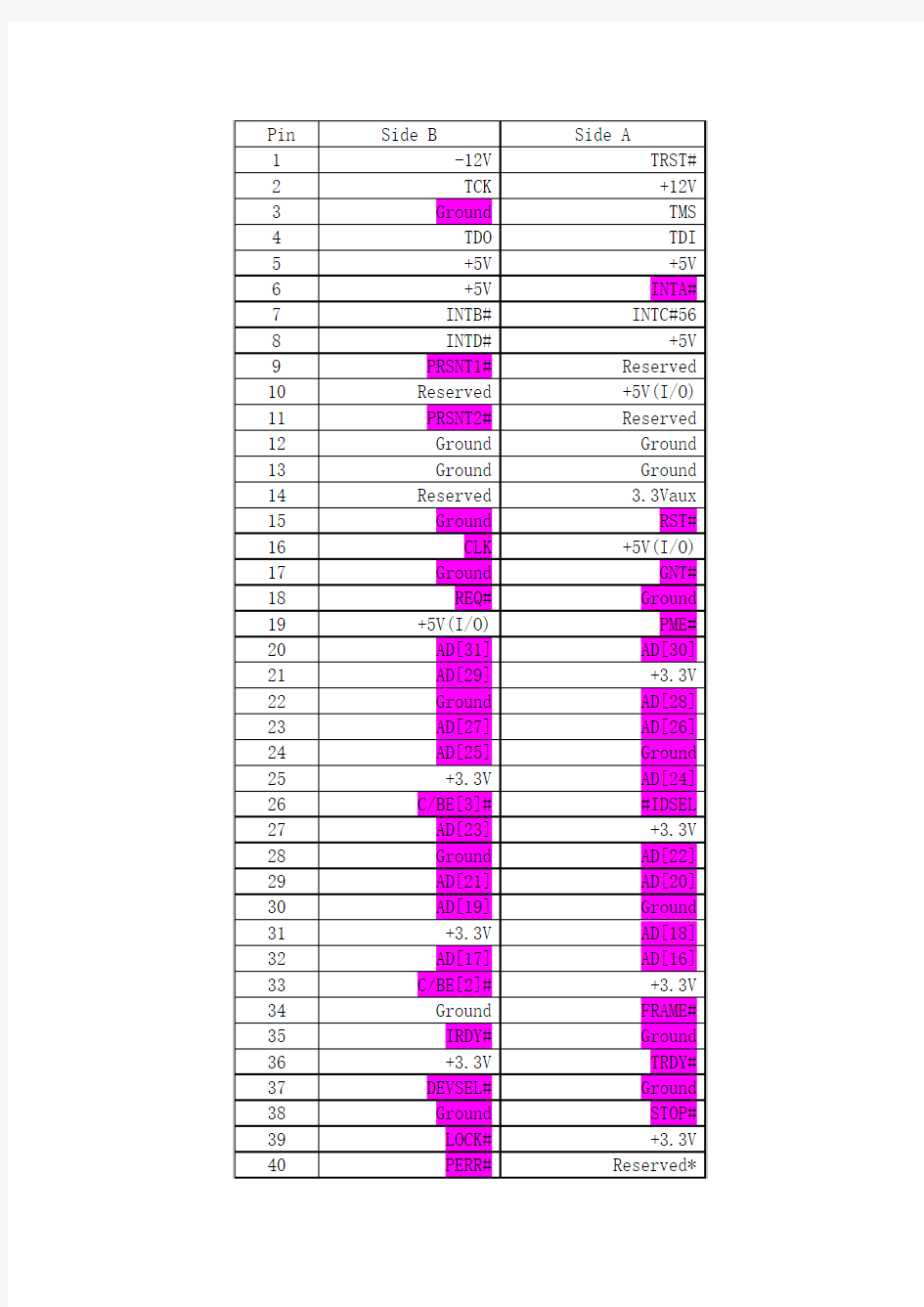

PCI总线接口引脚定义

由于M模式使用范围比较小,J模式使用起来控制比较复杂,一般使用C模式。所有模式

AD[31:0](Address and Data)地址和时钟复用,首先是一个地址段,后面跟着一个或多个数据段,支持突发模式的读写;

C/BE[3:0]#(Bus Command and Byte Enables)总线命令和数据使能复用管脚,在AD 为地址线的时候作为总线命令,在AD为数据线的时候作为数据使能;

DEVSEL#(Device Select)有效的时候表示当前设备被选中,作为输入端口;

FRAME#(Cyclone Frame)由主设备驱动,用来表示当前设备已经开始接入,总线开始传输数据。有效:传输数据。无效:完成最后一个数据的传输;

GNT#(Grant)用来表示当前接入的设备已经被接受;

IDSL(Initialization Device Select)在配置寄存器读写的时候用做片选信号;

INTA#(Interrupt A)PCI中断请求;

IRDY#(Initiator Ready)说明当前数据有效,可以并要完成传输;

LOCK#(Lock)提示有自动操作,需要消耗若干个时钟来完成操作;

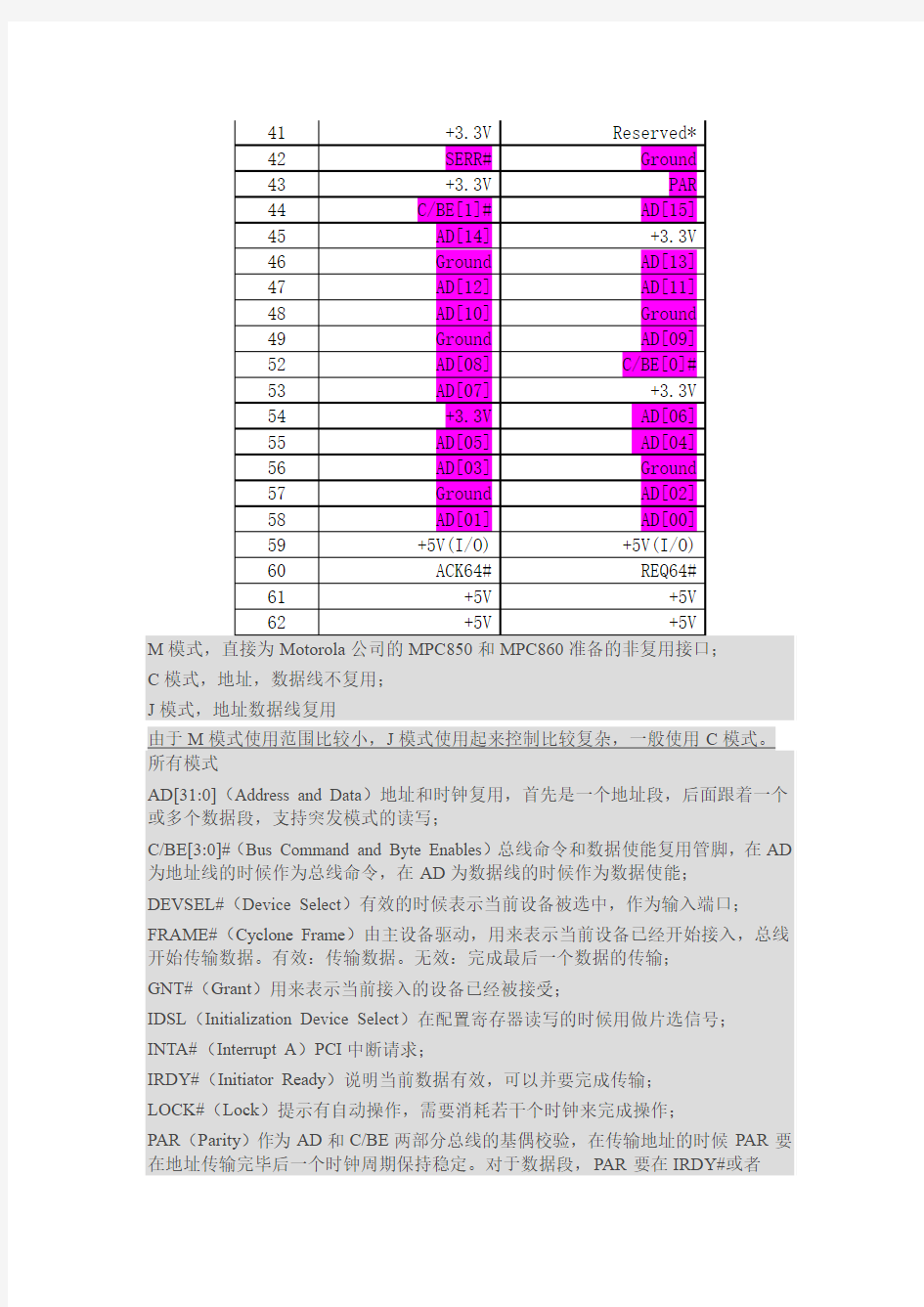

PAR(Parity)作为AD和C/BE两部分总线的基偶校验,在传输地址的时候PAR要在地址传输完毕后一个时钟周期保持稳定。对于数据段,PAR要在IRDY#或者

TRDY#有效以后一个时钟周期保持稳定。一旦PAR数据有效,将保持有效到当前数据或地址段传输结束;

PCLK(Clock)系统时钟,9054工作在33MHz;

PERR#(Parity Error)用来报告奇偶校验错误,不包括特殊周期;

PME#(Power Management Event)唤醒中断;

REQ#(Request)请求信号,通知总线判决器,当前设备必须使用总线;

RST#(Reset)系统复位;

SERR#(System Error)用来报告特殊周期的奇偶校验错误和其他系统错误;STOP#(Stop)要求主系统,停止当前设备的数据传输;

TRAY#(Target Ready)目标设备准备完毕,可以传输当前数据;

BIGEND#(Big Endian Select)

CCS#(Configuration Register Select)低有效的片选信号;

EECS(Serial EEPROM Chip Select)选择串行EEPROM;

EEDI/DDEO(Serial EEPROM Data In/ Serial EEPROM Data Out)控制串行EEPROM 读写数据;

EESK(Serial Data Clock)EEPROM读写时钟;

ENUM#(Enumeration)突发输出,用来表示一个使用PCI9054芯片的适配器刚刚从一个CPI总线通道里面加入或者移出;

LCLK(Local Processor Clock)本地时钟输入;

LEDon/LEDin LED控制;

LFRAME#(PCI Buffered FRAME# Signal)指示PCI总线的状态;

LINT#(Local Interrupt)本地总线中断。输入到9054,低有效,触发一个PCI中断。作为输出,等待到一个触发发生;

LRESETo#(Local Bus Reset Out)当PCI9054芯片被复位以后,该管脚可以用来驱动其他芯片的RESET#信号;

MDREQ#/MDPAF/EOT#

MODE[1:0](Bus Mode)11:M模式;10:J模式;01:保留;00:C模式;TEST(Test Pin)芯片检测管脚,高为检测,低为工作,平时置低;

USERi/BACK0#/LLOCKi# 复用管脚

USERo/DREQ0#/LLOCKo# 复用管脚

VDD电源

VSS地

C模式:

ADS#(Address Strobe)说明地址有效,总线有新设备接入;

BLAST#(Burst Last)该信号由本地总线控制,表示最后一个字符的传输;

BREQi(Bus Request In)本地总线控制,数据从本地总线输入;

BREQo(Bus Request Out)PCI总线控制,数据从PCI总线输出;

BTERM#(Burst Terminate)作为输入,表示当前突发操作结束,开始下一个突发地址的读写,和PCI9054内部的可编程等待状态生成器一起使用。作为输出,和READY#一起使用,中断当前突发操作,开始下一个突发操作地址周期;

DP[3:0](Data Parity)奇偶校验数据;

LA[31:2](Address Bus)地址总线;

LBE[3:0]#(Byte Enable)控制数据有效,不同的模式有不同的控制方法;

LD[31:0](Data Bus)数据总线;

LHOLD(Hold Request)发送要求使用本地总线,本地总线决定分配给当前装置以后,判决器发送LHOLDA信号反馈;

LHOLDA(Hold Request)反馈信号;

LSERR#(System Error Interrupt Output)系统错误中断;

LW/R#(Write/?Read)低电平读,高电平写;

READY#(Ready Input/Output)无论主还是从模式,表示数据准备好,有效;

WAIT#(Wait Input/Output)作为输入,控制PCI9054插入等待状态。作为输出,PCI9054处于Ready状态。