实验五 组合逻辑电路

实验五组合逻辑电路(实验报告)

一、实验目的

1.掌握组合逻辑电路的设计方法

2.熟悉常用组合逻辑器件的使用方法

3.熟悉用逻辑门电路、74LS138和74LS151进行综合性设计的方法

二、试验设备和器件

设备:数字电子技术试验箱

器件:74LS00,74LS20,74LS86,74LS138,74LS151

三、实验内容及步骤

1.实现一位全加器

(1)按照组合逻辑电路的一般设计步骤,用基本门电路(74LS00,74LS20,74LS86)实现一

位全加器;

(2)用1片74LS138和1片74LS20实现一位全加器。

2.设计一个监测信号灯工作状态的逻辑电路,每一组信号灯由红、黄、绿三盏构成,仅有红灯R亮、仅有绿灯G亮、黄灯Y和绿灯G同时亮为正常工作状态,其余为故障状态。故障状态时要发出报警信号。要求用74LS151实现。

(1)逻辑抽象。红黄绿三盏信号灯的状态为输入变量,分别用R、Y、G表示,并规定灯亮时为1,灭时为0;故障信号为输出变量,用Z表示,并规定正常工作状态下Z为0,发生故障时Z为1;

(2) 列真值表于表3-1;

(3) 根据真值表写出用最小项表示的Z的逻辑表达式。

(4) 按照逻辑表达式进行电路连接,画出电路连接图,并对电路进行测试。

四、实验结果及数据分析

1.实现一位全加器

(1)列真值表

(2)由真值表得:S=ABC-1 ,C0=

(3)根据逻辑表达式,画出逻辑电路图如下:

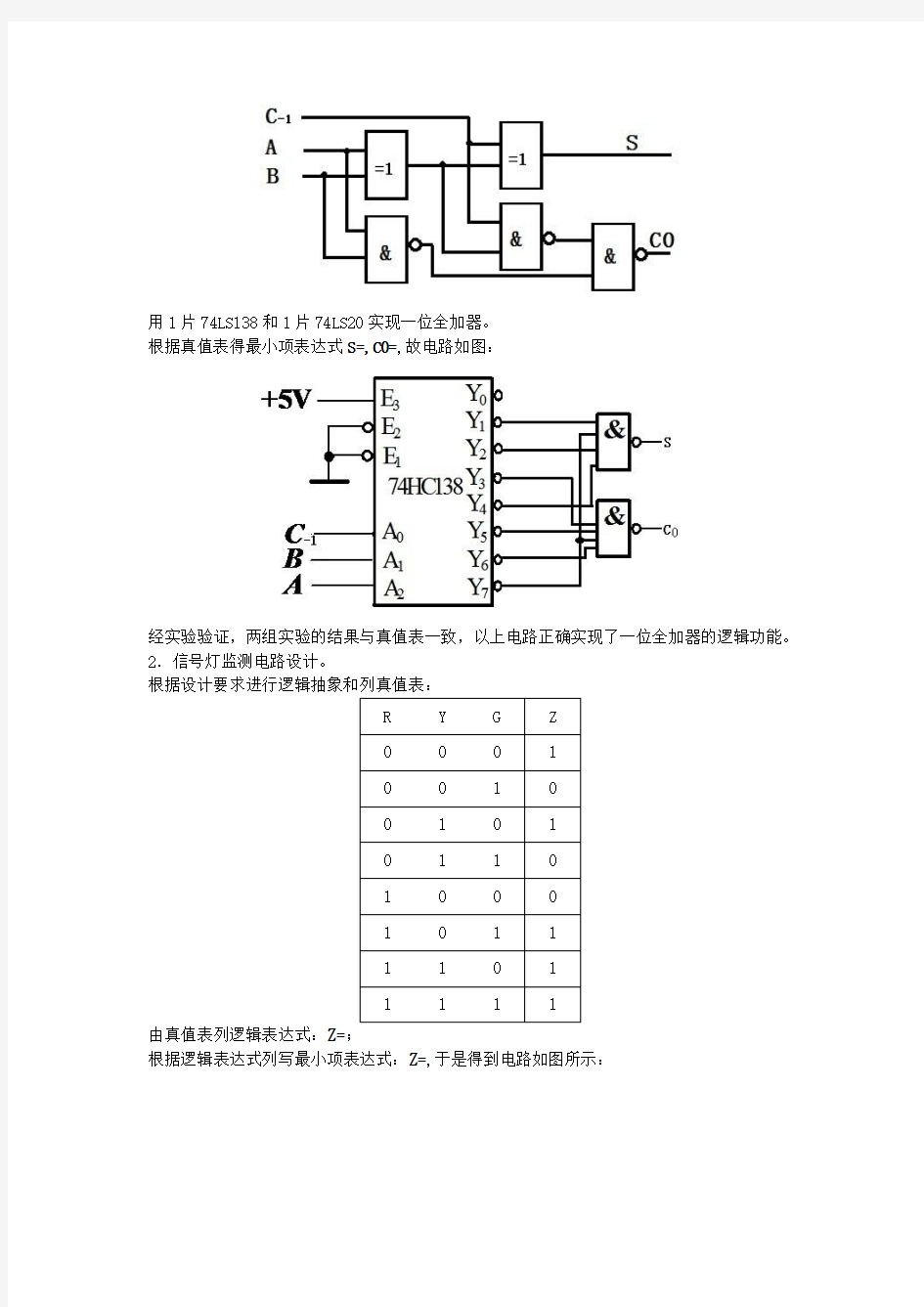

用1片74LS138和1片74LS20实现一位全加器。

根据真值表得最小项表达式S=,C0=,故电路如图:

经实验验证,两组实验的结果与真值表一致,以上电路正确实现了一位全加器的逻辑功能。2.信号灯监测电路设计。

由真值表列逻辑表达式:Z=;

根据逻辑表达式列写最小项表达式:Z=,于是得到电路如图所示:

经过实验验证,实验结果符合预期,电路实现了故障诊断的逻辑功能。

六、实验总结

本次实验比较成功,通过本实验,我基本掌握了组合逻辑电路的设计方法,熟悉了常用组合逻辑器件的使用方法,进一步学习了用逻辑门电路、74LS138和74LS151进行综合性设计的方法,而且,本实验加深了我对组合逻辑电路的理解,锻炼了我的实验能力。实验说明:对于三输入逻辑电路,都可以通过74LS138和74LS151实现,而且74LS138可以同时实现多个函数。

组合逻辑电路设计的一般步骤为:(1)明确实际问题的逻辑功能,确定输入、输出变量数计表示符号。(2)根据电路逻辑功能的要求,列出真值表。(3)由真值表写出逻辑表达式。(4)简化和变换逻辑表达式,从而画出逻辑图以及电路原理图。

第五章组合逻辑电路典型例题分析

第五章 组合逻辑电路典型例题分析 第一部分:例题剖析 例1.求以下电路的输出表达式: 解: 例2.由3线-8线译码器T4138构成的电路如图所示,请写出输出函数式. 解: Y = AC BC ABC = AC +BC + ABC = C(AB) +CAB = C (AB) T4138的功能表 & & Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 “1” T4138 A B C A 2A 1A 0Ya Yb S 1 S 2 S 30 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 1 S 1S 2S 31 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0 A 2A 1A 0Y 0Y 1Y 2Y 3Y 4Y 5Y 6Y 70 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 0

例3.分析如图电路,写出输出函数Z的表达式。CC4512为八选一数据选择器。 解: 例4.某组合逻辑电路的真值表如下,试用最少数目的反相器和与非门实现电路。(表中未出现的输入变量状态组合可作为约束项) CC4512的功能表 A ? DIS INH 2A 1A 0Y 1 ?0 1 0 0 0 00 00 00 0 0 0 0 00 0 ?????0 0 00 0 10 1 00 1 11 0 0 1 0 11 1 01 1 1 高阻态 0D 0D 1D 2D 3D 4D 5D 6D 7 Z CC4512 A 0A 1A 2 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 DIS INH D 1 D A B C D Y 0 0 0 0 1 0 0 0 1 00 0 1 0 10 0 1 1 00 1 0 0 0 CD AB 00 01 11 1000 1 0 0 101 0 1 0 1 11 × × × ×10 0 1 × × A B 第一步画卡诺图第三步画逻辑电路图

数电实验报告 实验二 组合逻辑电路的设计

实验二组合逻辑电路的设计 一、实验目的 1.掌握组合逻辑电路的设计方法及功能测试方法。 2.熟悉组合电路的特点。 二、实验仪器及材料 a) TDS-4数电实验箱、双踪示波器、数字万用表。 b) 参考元件:74LS86、74LS00。 三、预习要求及思考题 1.预习要求: 1)所用中规模集成组件的功能、外部引线排列及使用方法。 2) 组合逻辑电路的功能特点和结构特点. 3) 中规模集成组件一般分析及设计方法. 4)用multisim软件对实验进行仿真并分析实验是否成功。 2.思考题 在进行组合逻辑电路设计时,什么是最佳设计方案 四、实验原理 1.本实验所用到的集成电路的引脚功能图见附录 2.用集成电路进行组合逻辑电路设计的一般步骤是: 1)根据设计要求,定义输入逻辑变量和输出逻辑变量,然后列出真值表; 2)利用卡络图或公式法得出最简逻辑表达式,并根据设计要求所指定的门电路或选定的门电路,将最简逻辑表达式变换为与所指定门电路相应的形式; 3)画出逻辑图; 4)用逻辑门或组件构成实际电路,最后测试验证其逻辑功能。 五、实验内容 1.用四2输入异或门(74LS86)和四2输入与非门(74LS00)设计一个一位全加器。 1)列出真值表,如下表2-1。其中A i、B i、C i分别为一个加数、另一个加数、低位向本位的进位;S i、C i+1分别为本位和、本位向高位的进位。 A i B i C i S i C i+1 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 10 1 1 1 00 1 1 1 1 1 1 2)由表2-1全加器真值表写出函数表达式。

组合逻辑电路的分析

组合逻辑电路的分析(大题)一.目的 由逻辑图得出逻辑功能 二.方法(步骤) 1.列逻辑式: 由逻辑电路图列输出端逻辑表达式; (由输入至输出逐级列出) 2.化简逻辑式: 代数法、卡诺图法; (卡诺图化简步骤保留) 3.列真值表: 根据化简以后的逻辑表达式列出真值表;4.分析逻辑功能(功能说明): 分析该电路所具有的逻辑功能。 (输出与输入之间的逻辑关系); (因果关系) (描述函数为1时变量取值组合的规律) 技巧:先用文字描述真值表的规律(即叙述函数值为1时变量组合所有的取值),然后总结归纳电路实现的具体功能。

5.评价电路性能。三.思路总结: 组合逻辑 电路逻辑表达式最简表达式真值表逻辑功能化简 变换 四.注意: 关键:列逻辑表达式; 难点:逻辑功能说明 1、逻辑功能不好归纳时,用文字描述真值表的规律。(描述函数值为1时变量组合所有的取值)。 2、常用的组合逻辑电路。 (1)判奇(偶)电路; (2)一致性(不一致性)判别电路; (3)相等(不等)判别电路; (4)信号有无判别电路; (5)加法器(全加器、半加器); (6)编码器、优先编码器; (7)译码器; (8)数值比较器; (9)数据选择器; (10)数据分配器。

3、多输出组合逻辑电路判别: 1)2个输出时考虑加法器:2输入半加;3输入全加。 2)4输出时考虑编码器:4输入码型变换;编码器。 五.组合逻辑电路分析实例 例1 电路如图所示,分析电路的逻辑功能。 A B Y 解: (1)写出输出端的逻辑表达式:为了便于分析可将电路自左至右分三级逐级写出Z1、Z2、Z3和Y的逻辑表达式为:

数字电子电路与逻辑 刘可文主编 第五章 组合逻辑电路 答案

习 题5 题5-1 逻辑电路如图5-1所示,列出对应逻辑电路的真值表。 解:图5-1所示的逻辑电路,S 的逻辑表达式为:B A B A B AB A AB S +==,C 的逻辑 表达式为:AB C =。电路所对应的真值表如表5-1所示。 题5-2 分析图5-2所示逻辑电路的逻辑功能,并且列出真值表。 解:图5-2所示的逻辑电路,输出变量Y 0、Y 1的逻辑表达式为:CD ABD CD ABD Y 0+=?=,D C B D B C D C A D C B D B C D C A Y 1?++?=????=。 电路所对应的真值表如表5-2所示。 电路的功能分析,从函数表达式以及逻辑真值表,输出变量和输入变量之间没有明显的有规律的逻辑关系,由此可以看出,可以认为电路逻辑功能为两个逻辑函数的产生电路。实现CD ABD Y 0+=,D B D BC D Y 1?++?=逻辑函数的运算。 题5-3 写出如图5-3所示逻辑电路输出函数表达式,并且列出真值表。 解:图5-3所示的逻辑电路,输出变量F 的逻辑表达式为 C B A AC BC AB C B A AC BC AB F ??+++=?????=.电路所对应的真值表如表5-3 所示。 题5-4 利用与非门实现下列函数所描述逻辑功能的逻辑电路。 (1) )D C )(C A (F ++= , (2) C A AB F +=, 图5.1 图5-3

(3) )CD B (A F += , (4) B A D B AC F ++=, (5) )B A )(D B )(C A (F +++= , (6) C B CD C A F ++=, 解:利用反演定律,将各个逻辑函数转换成“与非”表达式为 (1) AD D C )D C )(C A (F 1?=+=++= , (2) C A AB C A AB F 2?=+=, (3) CD B A D B C B A )CD B (A F 3??=++=+=, (4) B A D B AC B A D B AC F 4??=++=, (5) B A D B C A B A D B C A )B A )(D B )(C (F 5???=?++=+++= , (6) C B CD C A C B CD C A F 5??=++=。 根据逻辑函数的相应“与非”表达式作出各个逻辑函数的逻辑电路图如图5-4所示。 题5-5 利用或非门实现下列函数所描述逻辑功能的逻辑电路。 (1). ABCD D ABC D C B A D BC A D C B A D C B A D C B A D C B A L +++++++= (2). )14,11,9,8,6,5,3,1()D ,C ,B ,A (L m ∑= (3). )15,14,13,12,11()9,8,6,5,2,1()D ,C ,B ,A (L d m ∑+∑= (4). )4,3()6,2,1()C ,B ,A (L d m ∑+∑= (5). C A BC B A L ++= 解:利用如图5-5(1)、(2)、(3)、(4)、(5)、(6)所示的逻辑函数“卡诺图”,将逻辑函数化简并利用反演定律,将各个逻辑函数转换成“或非”表达式为 (1). ABCD D ABC D C B A D BC A D C B A D C B A D C B A D C B A L 1+++++++= =∑m (0,1,2,4,6,10,14,15)=)C A )(D B A )(D C B (+++++ C A D B A D C B +++++++= (2). )14,11,9,8,6,5,3,1()D ,C ,B ,A (L m 2∑= )D C B )(C B A )(D C B )(D C B )(D B A (++++++++++= D C B C B A D C B D C B D B A ++++++++++++++= (3). )15,14,13,12,11()9,8,6,5,2,1()D ,C ,B ,A (L d m 3∑+∑= )C A )(D C A )(D C A (+++++=C A D C A D C A +++++++= (4). )4,3()6,2,1()C ,B ,A (L d m 4∑+∑= A )D B )(D C (++=A D B D C ++++= (5). C A BC B A L 5++=)C B )(C A (++=C B C A +++=。

(完整版)第20章习题1-门电路与组合逻辑电路

第20章习题 门电路和组合逻辑电路 S10101B 为实现图逻辑表达式的功能,请将TTL 电路多余输入端C 进行处理(只需一种处理方法),Y 1的C 端应接 ,Y 2的C 端应接 , 解:接地、悬空 S10203G 在F = AB +CD 的真值表中,F =1的状态有( )。 A. 2个 B. 4个 C. 3个 D. 7个 解:D S10203N 某与非门有A 、B 、C 三个输入变量,当B =1时,其输出为( )。 A. 0 B. 1 C. AC D. AC 解:C S10204B 在数字电路中,晶体管的工作状态为( )。 A. 饱和 B. 放大 C. 饱和或放大 D. 饱和或截止 解:D S10204I 逻辑电路如图所示,其逻辑函数式为( )。 A. B A B A + B. AB B A + C. B A B A + D. A AB + 解:C S10204N 已知F =AB +CD ,选出下列可以肯定使F = 0的情况( )。 A. A = 0,BC = 1 B. B = C = 1 C. C = 1,D = 0 D. AB = 0,CD = 0 解:D S10110B 三态门电路的三种可能的输出状态是 , , 。 解:逻辑1、逻辑0、高阻态 1 & B 1 & ≥1

逻辑图和输入A ,B 的波形如图所示,分析当输出F 为“1”的时刻应是( )。 A. t 1 B. t 2 C. t 3 解:A S10211I 图示逻辑电路的逻辑式为( )。 A. F =A B AB + B. B A AB F = C. F =()A B AB + 解:B S10212I 逻辑电路如图所示,其功能相当于一个( )。 A. 门 B. 与非门 C. 异或门 解:C S10216B 图示逻辑电路的逻辑式为( )。 A. F =A B +A B B. F =AB AB + C. F =AB +A B 解:C S10217B 逻辑图如图(a )所示,输入A 、B 的波形如图(b ),试分析在t 1瞬间输出F 为( )。 A. “1” B. “0” C. 不定 解:B S10218B 图示逻辑符号的逻辑状态表为( )。 A. B. C. 解:B A B F A B F A B F 0 0 0 0 0 0 0 0 1 0 1 0 0 1 1 0 1 1 1 0 0 1 0 1 1 0 1 1 1 1 1 1 1 1 1

实验六 组合逻辑电路的设计与测试

实验六组合逻辑电路的设计与测试 1.实验目的 (1)掌握组合逻辑电路的设计方法; (2)熟悉基本门电路的使用方法。 (3)通过实验,论证所设计的组合逻辑电路的正确性。 2.实验设备与器材 1)数字逻辑电路实验箱,2)万用表,3)集成芯片74LS00二片。 3.预习要求 (1)熟悉组合逻辑电路的设计方法; (2)根据具体实验任务,进行实验电路的设计,写出设计过程,并根据给定的标准器件画出逻辑电路图,准备实验; (3)使用器件的各管脚排列及使用方法。 4.实验原理 数字电路中,就其结构和工作原理而言可分为两大类,即组合逻辑电路和时序逻辑电路。组合逻辑电路输出状态只决定于同一时刻的各输入状态的组合,与先前状态无关,它的基本单元一般是逻辑门;时序逻辑电路输出状态不仅与输入变量的状态有关,而且还与系统原先的状态有关,它的基本单元一般是触发器。 (1)组合电路是最常用的逻辑电路,可以用一些常用的门电路来组合完成具有其他功能的门电路。设计组合逻辑电路的一般步骤是: 1)根据逻辑要求,列出真值表; 2)从真值表中写出逻辑表达式; 3)化简逻辑表达式至最简,并选用适当的器件; 4)根据选用的器件,画出逻辑电路图。 逻辑化简是组合逻辑设计的关键步骤之一。为了使电路结构简单和使用器件较少,往往要求逻辑表达式尽可能化简。由于实际使用时要考虑电路的工作速度和稳定可靠等因素,在较复杂的电路中,还要求逻辑清晰易懂,所以最简设计不一定是最佳的。但一般来说,在保证速度、稳定可靠与逻辑清楚的前提下,尽量使用最少的器件,以降低成本。 (2)与非门74LS00芯片介绍 与非门74LS00一块芯片内含有4个互相独立的与非门,每个与非门有二个输入端。其逻辑表达式为Y=AB,逻辑符号及引脚排列如图6-1(a)、(b)所示。 (a)逻辑符号(b)引脚排列 图6-1 74LS20逻辑符号及引脚排列 (3)异或运算的逻辑功能 当某种逻辑关系满足:输入相同输出为“0”,输入相异输出为“1”,这种逻辑关系称为“异或”逻辑关系。 (4)半加器的逻辑功能 在加法运算中,只考虑两个加数本身相加,不考虑由低位来的进位,这种加法器称为半加器。 5.实验内容 (1)用1片74LS00与非门芯片设计实现两输入变量异或运算的异或门电路 要求:设计逻辑电路,按设计电路连接后,接通电源,验证运算逻辑。输入端接逻辑开关输出插口,以提供“0”与“1”电平信号,开关向上,输出逻辑“1”,向下为逻辑“0”;电路的输出端接由LED发光二极管组成的0-1指示器的显示插口,LED亮红色为逻辑“1”,亮绿色为逻辑“0”。接线后检查无误,通电,用万用表直流电压20V档测量输入、输出的对地电压,并观察输出的LED颜色,填入表6-1。

数电实验报告 实验二 利用MSI设计组合逻辑电路

数电实验报告 实验二 利用MSI设计组合逻辑电路 姓名: 学号: 班级: 院系: 指导老师: 2016年 目录 实验目的:错误!未定义书签。

实验器件与仪器:错误!未定义书签。 实验原理:错误!未定义书签。 实验内容:错误!未定义书签。 实验过程:错误!未定义书签。 实验总结:错误!未定义书签。 实验: 实验目的: 熟悉编码器、译码器、数据选择器等组合逻辑功能模块的功能与使用方法。 掌握用MSI设计的组合逻辑电路的方法。 实验器件与仪器: 数字电路实验箱、数字万用表、示波器。 虚拟器件:74LS00,74LS197,74LS138,74LS151 实验原理: 中规模的器件,如译码器、数据选择器等,它们本身是为实现某种逻辑功能而设计的,但由于它们的一些特点,我们也可以用它们来实现任意逻辑函数。 用译码器实现组合逻辑电路 译码器是将每个输入的二进制代码译成对应的输出高、低电平信号。如3线-8线译码器。当附加控制门Gs的输入为高电平(S = 1)的时

候,可由逻辑图写出。 从上式可看出。-同时又是S2、S1、S0这三个变量的全部最小项的译码输出。所以这种译码器也叫最小项译码器。如果将S2、S1、S0当作逻辑函数的输入变量,则可利用附加的门电路将这些最小项适当的组合起来,便可产生任何形式的三变量组合逻辑函数。 用逻辑选择器实现组合逻辑电路 数据选择器的功能是从一组输入数据中选出某一个信号输出。或称为多路开关。如双四选一数据选择器74LS153

Y1和Y2为两个独立的输出端,和为附加控制端用于控制电路工作状态和扩展功能。A1、A0为地址输入端。D10、D11、D12、D13或D20、D21、D22、D23为数据输入端。通过选定不同的地址代码即可从4个数据输入端选出要的一个,并送到输出端Y。输出逻辑式可写成 其简化真值表如下表所示。 S1A1A0Y1 1X X0 000D10 001D11 010D12 011D13 从上述可知,如果将A1A0作为两个输入变量,同时令D10、D11、D12、D13为第三个输入变量的适当状态(包括原变量、反变量、0和1),就可以在数据选择器的输出端产生任何形式的三变量组合逻辑电路。 实验内容: 数据分配器与数据选择器功能正好相反。它是将一路信号送到地址选择信号指定的输出。如输入为D,地址信号为A、B、C,可将D按地址分配到八路输出F0、F1、F2、F3、F4、F5、F6、F7。其真值表如下

组合逻辑电路实验

实验一基本门电路的功能和特性及组合逻辑电路实验(2学时) 实验目的及要求:掌握常用的集成门电路的逻辑功能与特性;掌握各种门电路的逻辑符号;了解集成电路的外引线排列及其使用方法;学习组合逻辑电路的设计及测试方法。 实验题目:部分TTL门电路逻辑功能验证及组合逻辑电路设计之全加器或全减器。 实验二数值比较器、数据选择器(3学时) 实验目的及要求:掌握数值比较器和数据选择器的逻辑功能;学习组合逻辑电路的设计及测试方法。用7486和7400、7404搭出一位数值比较器,画出其设计逻辑电路图,并验证它的运算;用74153选择器实现多数据表决器,要求3个输入中有2个或3个为1时,输出Y为高电平,否则Y为低电平。画出电路图并简述实现原理。用7400、7404、7432实现该多数表决器。 实验题目:组合逻辑电路设计之数值比较器和数据选择器 实验三计数器的应用(3学时) 实验目的及要求:掌握集成二进制同步计数器74161的逻辑功能;掌握任意进制计数器的构成方法;学习时序逻辑电路的设计及测试方法。用74161搭建一个60进制计数器电路,并将结果输出到7段数码管显示出来,画出其设计逻辑电路图并验证它的功能。 实验题目:时序逻辑电路设计之计数器的应用 74LS00: QUAD 2-INPUT NAND GATE

74LS04: HEX INVERTER 74LS32:Quad 2-Input OR Gates

74LS74: Dual Positive-Edge-Triggered D Flip-Flops with Preset, Clear and Complementary Outputs 74LS153: Dual 4-Input Multiplexer with common select inputs and individual enable inputs 74LS161: Synchronous 4-Bit Binary Counters

数字电路第二章答案

第二章 组合逻辑电路 习题参考答案 2-1 写出图2-29所示各逻辑电路输出的逻辑表达式,列出真值表。 解:(a) BC AB Z +=1 (b) D C B A D C B A Z =+?+=2 真值表: (3) E D C B A E D C B A Z +++++++=)(3 E D C B A E D C B A +++?+++= ))((E D C B A E D C B A ++++++++=

+ + B C D ? + ] = + + E A+ ] ) A ( ) ( [ [E B C D A+ B A + + C = + + A (E )( D D ) B E B C BE C A+ A + D = + + B E D E E B C A E 真值表: 2-2分析图2-30所示的各逻辑电路,写出输出的逻辑表达式,列出真值表。

解:(a) )()(AC C B A C B A Z ?+?⊕+⊕= C B A C A B A C B A ⊕++=)( C B A C A B A C B A C B A C A B A C B A +++++=)( C B A A C B A C B A C A B A C B A +=+=+++= 真值表: (b) C B A ABC C B A C B A C B C B A C B A X +++=+⊕=⊕⊕=)()( C A BC B A Y ++= 2-3分析图2-31所示的逻辑电路,画出电路输出的波形图。 解:由逻辑图可以得到其输出表达式 C A D D BC B AD C AD D BC B AD Z +++==)( C AD D C B B D A +++++=)()( C AD D C D B D B B A +++++= C AD D B D B B A ++++=

(完整版)第五章 CMOS组合逻辑电路设计II

第五章CMOS组合逻辑电路设计II -动态CMOS电路 第一节动态逻辑门电路的基本结构、原理、特点第二节多米诺(Domino)CMOS电路 第三节改进的Domino CMOS电路 第四节时钟CMOS (C2MOS)

第一节动态逻辑门电路的基本结构、原理、特点 一、预充-求值动态CMOS的基本结构和工作原理 二、动态CMOS的特点 三、动态CMOS的问题 四、动态CMOS的级联 静态电路:靠管子稳定的导通、截止来保持输出状态除状态反转外,输出始终与VDD和GND保持通路。动态电路:靠电容来保存信息

一、预充-求值动态CMOS 的基本结构和工作原理 In 1In 2PDN In 3M e M p Clk Clk Out C L 预充-求值动态CMOS 电路的基本结构 工作过程: ?预充阶段:Clk =0,Out 被Mp 预充到VDD ,Me 截止,无论输入何值,均不存在直流通路。 此时的输出无效。 ?求值阶段:Clk =1,Mp 截止,Me 导通,Out 和GND 之间形成一条有条件的路径。具体由PDN 决定。若PDN 存在该路径,则Out 被放电,Out 为低电平,“0”。如果不存在,则预充电位保存在CL 上,Out 为高电平“1”。 ?求值阶段,只能有与GND 间的通路,无与VDD 间的,一旦放电,不可能再充电,只能等下次。 预充FET 求值FET

预充-求值动态CMOS 电路的工作原理 预充 预充 求值 输出只在此时有效 ) ,2,1(Xn X X F Y ???=当Clk =1时 Clk Out Clk =0时,输出为1,与输入无关

实验一组合逻辑电路设计

实验一 组合逻辑电路的设计 一、实验目的: 1、 掌握组合逻辑电路的设计方法。 2、 掌握组合逻辑电路的静态测试方法。 3、 加深FPGA 设计的过程,并比较原理图输入和文本输入的优劣。 4、 理解“毛刺”产生的原因及如何消除其影响。 5、 理解组合逻辑电路的特点。 二、实验的硬件要求: 1、 EDA/SOPC 实验箱。 2、 计算机。 三、实验原理 1、组合逻辑电路的定义 数字逻辑电路可分为两类:组合逻辑电路和时序逻辑电路。组合逻辑电路中不包含记忆单元(触发器、锁存器等),主要由逻辑门电路构成,电路在任何时刻的输出只和当前时刻的输入有关,而与以前的输入无关。时序电路则是指包含了记忆单元的逻辑电路,其输出不仅跟当前电路的输入有关,还和输入信号作用前电路的状态有关。 通常组合逻辑电路可以用图1.1所示结构来描述。其中,X0、X1、…、Xn 为输入信号, L0、L1、…、Lm 为输出信号。输入和输出之间的逻辑函数关系可用式1.1表示: 2、组合逻辑电路的设计方法 组合逻辑电路的设计任务是根据给定的逻辑功能,求出可实现该逻辑功能的最合理组 合电路。理解组合逻辑电路的设计概念应该分两个层次:(1)设计的电路在功能上是完整的,能够满足所有设计要求;(2)考虑到成本和设计复杂度,设计的电路应该是最简单的,设计最优化是设计人员必须努力达到的目标。 在设计组合逻辑电路时,首先需要对实际问题进行逻辑抽象,列出真值表,建立起逻辑模型;然后利用代数法或卡诺图法简化逻辑函数,找到最简或最合理的函数表达式;根据简化的逻辑函数画出逻辑图,并验证电路的功能完整性。设计过程中还应该考虑到一些实际的工程问题,如被选门电路的驱动能力、扇出系数是否足够,信号传递延时是否合乎要求等。组合电路的基本设计步骤可用图1.2来表示。 3、组合逻辑电路的特点及设计时的注意事项 ①组合逻辑电路的输出具有立即性,即输入发生变化时,输出立即变化。(实际电路中 图 1.1 组合逻辑电路框图 L0=F0(X0,X1,···Xn) · · · Lm=F0(X0,X1,···Xn) (1.1) 图 1.2 组合电路设计步骤示意图图

(整理)《数字逻辑电路》试题2.

一、选择题(每小题1.5分) 第一章: 1. 带符号位二进制数10011010的反码是( )。 A. 11100101 B. 10011010 C. 10011011 D. 11100110 2. 十进制数5对应的余3码是( )。 A. 0101 B. 1000 C. 1010 D. 1100 3. 二进制代码1011对应的格雷码是( )。 A. 1011 B. 1010 C. 1110 D. 0001 第二章: 1. 下列公式中哪一个是错误的? ( ) A. A A 0=+ B. A A A =+ C. B A )B A ('+'='+ D. )C A )(B A (BC A ++=+ 2. 下列各式中哪个是三变量A 、B 、C 的最小项? ( ) A. B A '' B. C B A +'+' C.ABC D. C B '+' 3. 下列函数中不等于A 的是( )。 A. A +1 B. A +A C. A +AB D. A (A +B ) 4. 在逻辑代数的加法运算中,1+1=( )。 A. 2 B. 1 C. 10 D. 0 5. A ⊕1=( )。 A. A B. 1 C. A ' D. 0 6. 含有A 、B 、C 、D 四个逻辑变量的函数Y=A+B+D 中所含最小项的个数是( )。 A. 3 B. 8 C. 14 D. 16 7. 下列函数中等于AB 的是( )。 A. (A +1)B B. (A +B )B C. A +AB D. A (AB ) 8. 为了将600份文件顺序编码,如果采用二进制代码,最少需要用( )位。 A. 3 B. 10 C. 1024 D. 600 9. 为了将600个运动员顺序编码,如果采用八进制代码,最少需要用( )位。 A. 3 B. 4 C. 10 D. 75 第三章:

组合逻辑电路的设计实验报告

广西大学实验报告纸 _______________________________________________________________________________ 实验内容___________________________________________指导老师 【实验名称】 组合逻辑电路的设计 【实验目的】 学习组合逻辑电路的设计与测试方法。 【设计任务】 用四-二输入与非门设计一个4人无弃权表决电路(多数赞成则提案通过)。要求:采用四-二输入与非门74LS00实现;使用的集成电路芯片种类尽可能的少。 【实验用仪器、仪表】 数字电路实验箱、万用表、74LS00。 【设计过程】 设输入为A、B、C、D,输出为L,根据要求列出真值表如下 真值表

根据真值表画卡若图如下 由卡若图得逻辑表达式 B D C

BD AC CD AB BD AC CD AB BD AC CD AB BD AC CD BD AC AB D BCD C ACD B ABD A ABC ACD BCD ABD ABC L ???=???=++=+++=?+?+?+?=+++=))(()()( 用四二输入与非门实现 A B C D L 实验逻辑电路图

Y 实验线路图

【实验步骤】 1.打开数字电路实验箱,按下总电源开关按钮。 2.观察实验箱,看本实验所用的芯片、电压接口、接地接口的位置。 3.检查芯片是否正常。芯片内的每个与非门都必须一个个地测试,以保证芯片 能正常工作。 4.检查所需导线是否正常。将单根导线一端接发光二极管,另一端接高电平。 若发光二极管亮,说明导线是正常的;若发光二极管不亮时,说明导线不导通。不导通的导线不应用于实验。 5.按实验线路图所示线路接线。 6.接好线后,按真值表的输入依次输入A、B、C、D四个信号,“1”代表输入高 电平,“0”代表输入低电平。输出端接发光二极管,若输出端发光二极管亮则说明输出高电平,对应记录输出结果为“1”;发光二极管不亮则说明输出低电平,对应记录输出结果为“0”。本实验有四个输入端则对应的组合情况有16种,将每种情况测得的实验结果记录在实验数据表格中。 测量结果见下表: 实验数据表格

组合逻辑电路设计实验报告

组合逻辑电路设计实验报告 1.实验题目 组合电路逻辑设计一: ①用卡诺图设计8421码转换为格雷码的转换电路。 ②用74LS197产生连续的8421码,并接入转换电路。 ③记录输入输出所有信号的波形。 组合电路逻辑设计二: ①用卡诺图设计BCD码转换为显示七段码的转换电路。 ②用74LS197产生连续的8421码,并接入转换电路。 ③把转换后的七段码送入共阴极数码管,记录显示的效果。 2.实验目的 (1)学习熟练运用卡诺图由真值表化简得出表达式 (2)熟悉了解74LS197元件的性质及其使用 3.程序设计 格雷码转化: 真值表如下:

卡诺图: 1 010100D D D D D D G ⊕=+= 2 121211D D D D D D G ⊕=+=

3232322D D D D D D G ⊕=+= 33D G = 电路原理图如下: 七段码显示: 真值表如下: 卡诺图:

2031020231a D D D D D D D D D D S ⊕++=+++= 10210102b D D D D D D D D S ⊕+=++= 201c D D D S ++= 2020101213d D D D D D D D D D D S ++++= 2001e D D D D S +=

2021013f D D D D D D D S +++= 2101213g D D D D D D D S +++= 01213g D D D D D S +⊕+= 电路原理图如下:

4.程序运行与测试 格雷码转化: 逻辑分析仪显示波形:

数电第二章习题教学内容

第二章 一、选择题 1.下列表达式中不存在竞争冒险的有 C D 。 A.Y =B +A B B.Y =A B +B C C.Y =A B C +A B D.Y =(A +B )A D 2.若在编码器中有50个编码对象,则要求输出二进制代码位数为B 位。 A.5 B.6 C.10 D.50 3.一个16选一的数据选择器,其地址输入(选择控制输入)端有 C 个。 A.1 B.2 C.4 D.16 4.下列各函数等式中无冒险现象的函数式有 D 。 A.B A AC C B F ++= B.B A BC C A F ++= C.B A B A BC C A F +++= D.C A B A BC B A AC C B F +++++= E.B A B A AC C B F +++= 5.函数C B AB C A F ++=,当变量的取值为 A C D 时,将出现冒险现象。 A.B =C =1 B.B =C =0 C.A =1,C =0 D.A =0,B =0 6.四选一数据选择器的数据输出Y 与数据输入X i 和地址码A i 之间的逻 辑表达式为Y = A 。 A.3X A A X A A X A A X A A 01201101001+++ B.001X A A C.101X A A D.3X A A 01 7.一个8选一数据选择器的数据输入端有 E 个。 A.1 B.2 C.3 D.4 E.8 8.在下列逻辑电路中,不是组合逻辑电路的有 D 。 A.译码器 B.编码器 C.全加器 D.寄存器 9.八路数据分配器,其地址输入端有 C 个。 A.1 B.2 C.3 D.4 E.8 10.组合逻辑电路消除竞争冒险的方法有 A B 。 A. 修改逻辑设计 B.在输出端接入滤波电容 C.后级加缓冲电路 D.屏蔽输入信号的尖峰干扰 11.101键盘的编码器输出 C 位二进制代码。 A.2 B.6 C.7 D.8 12.用三线-八线译码器74L S 138实现原码输出的8路数据分配器,应 A B C 。 A.A ST =1,B ST =D ,C ST =0 B. A ST =1,B ST =D ,C ST =D C.A ST =1,B ST =0,C ST =D D. A ST =D ,B ST =0,C ST =0 13.以下电路中,加以适当辅助门电路, A B 适于实现单输出组合逻辑电路。

组合逻辑电路-实验报告

电子通信与软件工程系2013-2014学年第2学期 《数字电路与逻辑设计实验》实验报告 --------------------------------------------------------------------------------------------------------------------- 班级:姓名:学号:成绩: 同组成员:姓名:学号: --------------------------------------------------------------------------------------------------------------------- 一、实验名称:组合逻辑电路(半加器全加器及逻辑运算) 二、实验目的:1、掌握组合逻辑电路的功能调试 2、验证半加器和全加器的逻辑功能。 3、学会二进制数的运算规律。 三、实验内容: 1.组合逻辑电路功能测试。 (1).用2片74LS00组成图所示逻辑电路。为便于接线和检查.在图中要注明芯片编号及各引脚对应的编号。 (2).图中A、B、C接电平开关,YI,Y2接发光管电平显示. (3)。按表4。1要求,改变A、B、C的状态填表并写出Y1,Y2逻辑表达式. (4).将运算结果与实验比较.

2.测试用异或门(74LS86)和与非门组成的半加器的逻辑功能.根据半加器的逻辑表达式可知.半加器Y是A、B的异或,而进位Z是A、B相与,故半加器可用一个集成异或门和二个与非门组成如图. (1).在学习机上用异或门和与门接成以上电路.接电平开关S.Y、Z接电平显示.(2).按表4.2要求改变A、B状态,填表. 3.测试全加器的逻辑功能。 (1).写出图4.3电路的逻辑表达式。 (2).根据逻辑表达式列真值表. (3).根据真值表画逻辑函数S i 、Ci的卡诺图. (4).填写表4.3各点状态 (5).按原理图选择与非门并接线进行测试,将测试结果记入表4.4,并与上表进行比较看逻辑功能是否一致.

第5章课后习题参考答案

第五章组合逻辑电路 1.写出如图所示电路的输出信号逻辑表达式,并说明其功能。 (a)(b) 解:(a)Y1ABC(判奇功能:1的个数为奇数时输出为1) Y2AB(AB)CABACBC(多数通过功能:输出与输入多数一致)(b)Y1(AB)A(AB)BABAB(同或功能:相同为1,否则为0)2.分析如图所示电路的逻辑功能 (a)(b)(c) 解:(a)Y 1ABAB(判奇电路:1的个数为奇数时输出为1) 0011 (b)Y2(((AA)A)A)(判奇电路:1的个数为奇数时输出为1) 0123 YAM 00 (c)Y 1 A M 1 (M=0时,源码输出;M=1时,反码输出) YAM 23 3.用与非门设计实现下列功能的组合逻辑电路。(1)实现4变量一致电路。 (2)四变量的多数表决电路 解:(1) 1)定变量列真值表:

ABCDYABCDY 0000110000 0001010010 0010010100 0011010110 010******* 010******* 0110011100 0111011111 2)列函数表达式:YABCDABC D ABCDABCD 3)用与非门组电路 (2)输入变量A、B、C、D,有3个或3个以上为1时输出为1,输人为其他状态时输出为0。 1)列真值表2)些表达式 3)用与非门组电路 4.有一水箱由大、小两台水泵ML和Ms供水,如图所示。水箱中设置了3个水位检测元

件A、B、C,如图(a)所示。水面低于检测元件时,检测元件给出高电平;水面高于检测元件时,检测元件给出低电平。现要求当水位超过C点时水泵停止工作;水位低于C点而高于B点时Ms单独工作;水位低于B点而高于A点时ML单独工作;水位低于A点时 ML和Ms同时工作。试用门电路设计一个控制两台水泵的逻辑电路,要求电路尽量简单。 解:(1)根据要求列真值表(b) (b)(a) (2)真值表中×对应的输入项为约束项,利用卡诺图化简(c)(d) (c)(d) (e) 得:MABC s MB L (ML、M S的1状态表示工作,0状态表示停止) (3)画逻辑图(e)

组合逻辑电路实验报告

实验名称:组合逻辑电路 一、实验目的 1、掌握组合逻辑电路的分析、设计方法与测试方法; 2、了解组合逻辑电路的冒险现象及消除方法。 二、实验器材 需要与非门CC4011×3,异或门CC4030×1,或门CC4071×1。 CC4011引脚图CC4030引脚图 CC4071引脚图 三、实验内容及实验电路 1、分析、测试用与非门CC4011组成的半加器的逻辑功能。列出真值表并画出卡诺图判断是否可以简化。 图1由与非门组成的半加器电路

A B S C 2、分析、测试用异或门CC4030与与非门CC4011组成的半加器逻辑电路。 图2由异或门和与非门组成的半加器电路 A B S C 3、分析、测试全加器的逻辑电路。写出实验电路的逻辑表达式,根据实验结果列出真值表与全加器的逻辑功能对比,并画出i S和i C的卡诺图。 图3由与非门组成的全加器电路 A B1 i C i S i C

4、设计、测试用异或门、与非门和或门组成的全加器逻辑电路。 全加和:()1 -⊕⊕=i i i i C B A S 进位:()i i i i i i B A C B A C ?+?⊕=-1将全加器的逻辑表达式,变换成由两个异或门,四个与非门,一个或门组成;画出全加器电路图,按所画的原理图选择器件并在实验板上连线;进行功能测试并自拟表格填写测试结果。电路图:A B 1-i C i S i C 5、观察冒险现象。按图4接线,当1==C B 时,A 输入矩形波(MHz f 1=以上),用示波器观察输出波形,并用添加冗余项的方法消除冒险现象。 图4观察冒险现象实验电路

四、实验预习要求 1、复习组合逻辑电路的分析方法。 2、复习组合逻辑电路的设计方法。 3、复习用与非门和异或门等构成半加器和全加器的工作原理。 4、复习组合电路冒险现象的种类、产生原因和如何防止。 5、根据试验任务要求,设计好实验时必要的实验线路。 五、实验报告 1、整理实验数据、图表,并对实验结果进行分析讨论。 2、总结组合逻辑电路的分析与测试方法。 3、对冒险现象进行讨论。

第5章 典型组合逻辑电路

I I 4 5 7 I 1 6 2 I I I 0 3 I I I 9 8 I 图 P5.7 图P5.8 第5章 组合逻辑电路应用 习题5 5.1 设计一个10线-4线编码器,输出为8421BCD 码。 5.2 试用2片8线-3线优先编码器74148,设计一个10线-4线优先编码器。连接时允许附加必要的门电路。 5.3 试分析图P5.3所示电路的功能(74148为8线-3线优先编码器)。 5.4 分析图P5.4所示电路的功能。 5.5 用2片3线-8线译码器74138,组成4线-16线译码器。 5.6 某一个8421BCD 码七段荧光数码管译码电路的e 段部分出了故障,为使数码管能正确地显示0~9十种状态,现要求单独设计一个用与非门组成的e 段译码器。已知共阳极数码管如图P5.6所示。 5.7 分析图P5.7所示电路的功能(74148为8线-3线优先编码器)。 5.8 画出用两片4线-16线译码器74154组成5线-32译码器的接线图。图P5.8是74154的符号,S A 和S B 是两个控制端(亦称片选端),译码器工作时应使S A 和S B 同时为低电平,当输入信号A 3A 2A 1A 0为0000到1111共16种状态时,输出端从Y 0到Y 15依次给出低电平输出信号。 图P5. 4 图P5.6 图P5.3

5.9 设计一个编码转换器,将三位2进制码转换为循环码。 5.10 某医院的某层有6个病房和一个大夫值班室,每个病房有一个按扭,在大夫值班室有一个优先编码器电路,该电路可以用数码管显示病房的编码。各个房间按病人病情严重程度不同分类,1号房间病人病情最重,病情按房间号依次降低,6号房间病情最轻。试设计一个呼叫装置,该装置按病人的病情严重程度呼叫大夫,若两个或两个以上的病人同时呼叫大夫,则只显示病情最重病人的呼叫。 5.11 设计一个电话机信号控制电路。电路有I 0(火警)、I 1(盗警)和I 2(日常业务)三种输入信号,通过排队电路分别从Y 0、Y 1、Y 2输出,在同一时间只能有一个信号通过。如果同时有两个以上信号出现时,应首先接通火警信号,其次为盗警信号,最后是日常业务信号。试按照上述轻重缓急设计该信号控制电路。要求用集成门电路7400(每片含4个2输入端与非门)实现。 5.12 试用一片3线-8线译码器T3138,实现下列逻辑函数(可使用必要的门电路): (1)B A L =1 (2)B A AB L +=2 (3)C B A L ⊕⊕=3 5.13 用4路数据选择器实现下列函数: (1) ∑=)5,4,2,0(),,(1m C B A L (2) ∑= )7,5,3,1(),,(2m C B A L (3)∑=)7,5,2,0(),,(3m C B A L (4)∏= )3,2,0(),,(4M C B A L 5.14 用8路数据选择器实现下列函数: (1) ∑=)15,13,10,8,7,5,2,0(),,,(1m D C B A L (2) ∑= )12,10,9,5,4,3,0(),,,(2m D C B A L (3) C B AB C B A L +=),,(3 5.15 将四选一数据选择器,扩展为16选一数据选择器。 5.16 用3线-8线译码器74138和8选1数据选择器74151和少量与非门实现组合逻辑电路。当控制变量C 2C 1C 0=000时,F=0;C 2C 1C 0=001时,F=ABC ;C 2C 1C 0=010时,F=A+B+C ;C 2C 1C 0=011时,F=ABC ;C 2C 1C 0=100时,F=C B A ++;C 2C 1C 0=101时,F=C B A ⊕⊕;C 2C 1C 0=110时,F=AB+AC+BC ;C 2C 1C 0=111时,F=1。画出电路图。 5.17 分析图P5.17所示电路的工作原理,说明电路的功能。