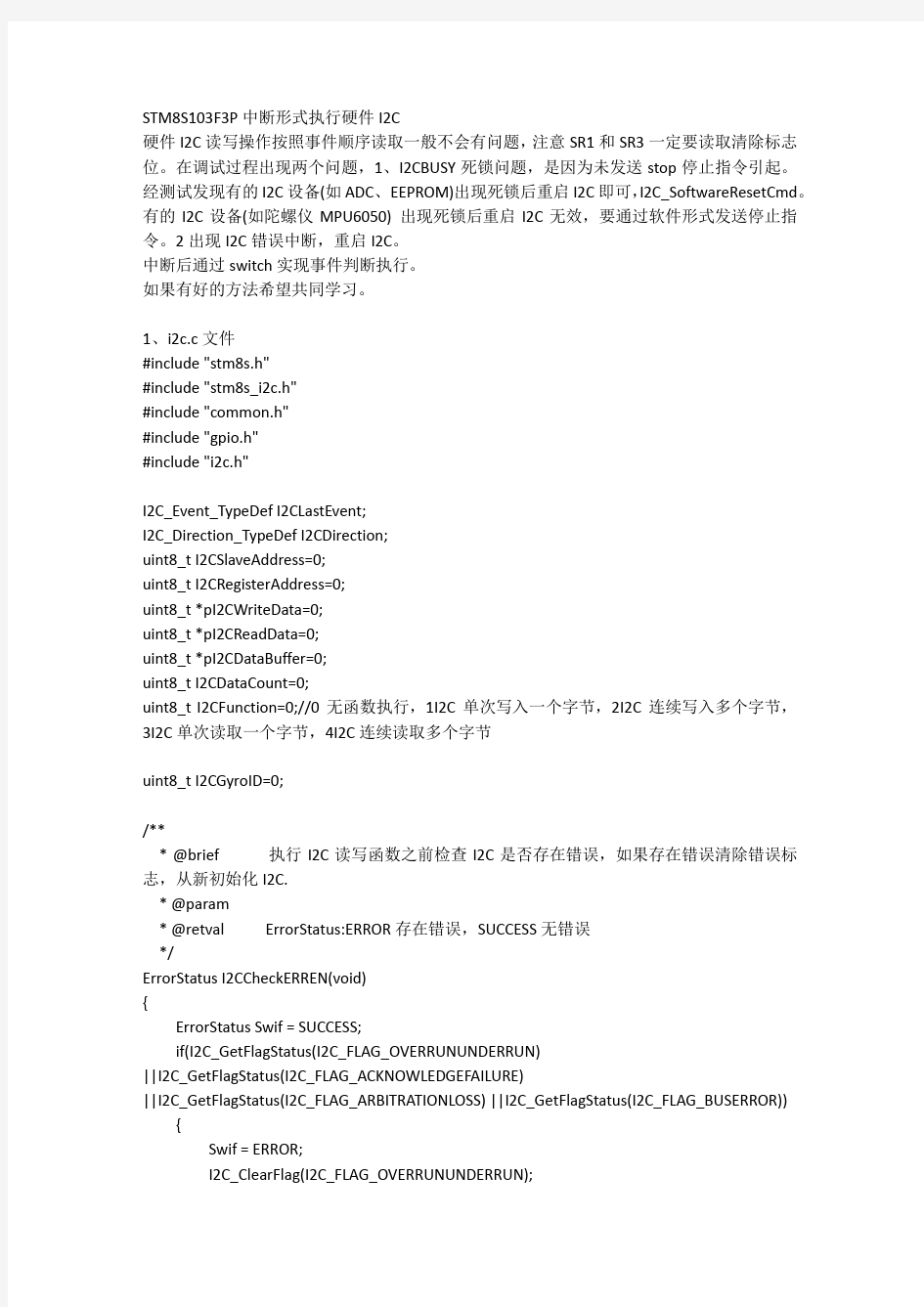

STM8S103F3P中断形式执行硬件I2C

单片机 实验2-外部中断程序设计-中断按键按下次数计数数码管显示-硬件和程序设计参考

硬件电路参考如下:

程序参考如下: #pragma sfr #pragma interrupt INTP0 LED_INTP0 /* 定义使用INTP0中断,中断函数名LED_INTP0*/ #pragma di /*禁止使用中断功能声明*/ #pragma ei /*允许使用中断功能声明*/ /*数码管编码数组*/ unsigned char LED_light[10]={0x30,0x5B,0x4F,0x66,0x6D,0x7D,0x07,0x7F,0x6F,0x3F}; unsigned char j=0; /*按键次数变量*/ void hdinit() /*硬件初始化*/ { PM1=0; /*P1口输出数码管字型码,所以设置为输出*/ PU1=0XFF; /*由于P1口直接驱动数码管显示,为增大驱动,设置为内部上拉*/ PM12.0=0; /*P12.0口线要作为中断多功能,设置为输出和内部上拉 */ PU12.0=1; PIF0=0; /*中断请求标志,没有中断请求*/ PMK0=0; /*中断屏蔽标志,允许中断*/ PPR0=1; /*中断优先级,低优先级*/ EGP.0=1; /*与EGN组合,上升沿有效*/ EGN.0=0; } void main (void) { DI(); /*首先做准备,禁止中断*/ IMS=0XCC; IXS=0X00; hdinit(); EI(); /*准备完成,允许中断*/ while(1) { /*啥也不干,就等待中断,仅是在这个实验中使用中断,实际不是这样/* } } __interrupt void LED_INTP0() /*中断函数*/ { P1= LED_light[j]; /*P1赋值,数码管显示相应数值*/ j++; /*按键次数加一*/ if(j==10) /*如果按键次数达到十次,按键计数归0*/ {j=0;} } 思考: 如果用两位数码管,从0—99循环计数又该怎样设计硬件和软件呢?

中断程序编写与硬件仿真调试经验

1,中断程序的编写 一个编程经验是,所有的中断都要尽快的运行和退出,中断服务程序越短越好,这样才不至于干扰主程序的工作和其他中断的运行。也就是,我们应该尽量把程序代码从中断服务函数里搬出来。 对于定时器的中断的工作方式,我们可以建立一个全局的标记(变量flag),在中断里置这个标记,然后就退出。在主程序里去检查这个标记,再清0 标记和处理相应的工作。检查到这个标记之后,就运行相关的程序。对于CPU 任务比较多的项目来说,这种工作方式可以获得最佳的工作效率。当然,对于非常实时的应用要求,比如时钟,还是建议在中断里做完,因为使用标记的方式时,主程序可能太忙而造成错过标记信号,就是这个标记还没有开始处理呢,下一个该中断又来了。熟练的程序员还是可以避开这些异常的情况的。(实质上是看中断发生的频率与cpu主频的相对快慢,cpu处理速度快就不会产生这种问题) 2,在没有硬件的情况下,看看程序执行的如何,使用单步执行。但到外部中断的时候就过不去了,怎么让他接着执行外部中断的服务从程序呢? 在仿真运行时,在peripheral中打开对应的IO口或UART等,找到外部中断输入的那一位,手动给中断信号就可。 3,Keil中调试技巧 <1>查看变量的值 注意,要查看变量的值,只能在程序停下来的状态下查看。在程序运行的过程中,程序不断地运行,变量也在不断地变化,一般是无法查看的。 (1)点停止程序后,在C源文件窗口程序中,将鼠标放在的变量“n”上面,可以看到旁边出现了一个小框框,上面显示了n=0x47D3,这就是变量此时的值。 (2)如果觉得这样可能会点不准确,可以选中你要看的变量,同样会显示变量的值,个人感觉这种操作更为方便。 (3)在命令行窗口下,输入的方法也可以看变量,在命令行输入n,回车,就看到结果了。 (4)在watch 窗口看变量。点watch 图标,就是那个有个眼镜的图标,打开watch 窗口。注意要看某个变量,如果这个变量是某个函数私有的(局部变量),必须是程序停止时并且PC 已经停止在了这个函数中才可以看到(这就需要在该函数中设置断点),各种看变量的情况都是这样。 注:watch框内的变量只有在当前变量作用域的才可以添加,例如全局变量。局部变量即使添加后,在下次调试时也会从watch窗口移除,改到locals窗口内显示。这个' 符号似乎是表示该变量是上次调试时定义的,好像没其他什么作用。做过测试,只要成功被记录进watch窗口的全局变量,即使该量的物理地址发生了变化,下次调试时调试器也能准确跟踪到,并在watch内刷新结果。locals窗口是查看当前函数处内部变量值得窗口。不要被误导。KEIL调试时的watch窗口是查看的全局变量值,不能看内部变量值。 如果在watch窗口看内部变量,会是错误的。会误导你的!! <2>这里再教一招,如果我想让n 现在就变成我想要的值怎么办?这也是调试常见的手段,设置一个变量的值,比如,让n =0x1234,只要在命令窗口里输入“n=0x1234”就行了,几乎所有变量都可以这样直接设置,包括IO 口,比如你输入“P1.1=0”,结果第二个灯就亮了。 <3>还有一种直接看存储器的方法,可以看到所有存储器的值,但是和变量名称就不是那么好对应起来了。点memory 窗口图标,打开memory 窗口。在实际的硬件调试方式中,如果不用看memery 窗口,就建议不用打开它。因为保持它的打开会增加仿真时通讯的时间,特别是单步运行的时间。

悠景OLED (STM8S)I2C驱动

/******************************************************* ******************** * 文件名:oled.c * 描述:SSD1306 OLED 驱动IC驱动代码 * 驱动方式:I2C * i_restart@https://www.360docs.net/doc/6915772104.html, DB.Yan * 最后修改:2013-12-03 * *硬件连接图 |----------------------------------------------------------------| | SCL---PB4 | | SDA---PB5 | | RST---PD7 | ******************************************************************************/ #include "oled.h" #include "stdlib.h" #include "font.h" //OLED的显存 //存放格式如下. //Page[0]0 1 2 3 (127) //Page[1]0 1 2 3 (127) //Page[2]0 1 2 3 (127) //Page[3]0 1 2 3 (127) //Page[4]0 1 2 3 (127) //Page[5]0 1 2 3 (127) //Page[6]0 1 2 3 (127) //Page[7]0 1 2 3 (127) uint8_t OLED_GRAM[128][8]; #define SCL PB_ODR_ODR4 #define SDA PB_ODR_ODR5 #define SDAM PB_IDR_IDR5 #define RST PD_ODR_ODR7 #define SET_SCL_OUT() {PB_DDR_DDR4=1; PB_CR1_C14 = 1; PB_CR2_C24 = 0;} #define SET_SDA_OUT() {PB_DDR_DDR5=1; PB_CR1_C15 = 1; PB_CR2_C25 = 0;} #define SET_SDA_IN() {PB_DDR_DDR5=0; PB_CR1_C15 = 0; PB_CR2_C25 = 0;} #define SET_RST_OUT() {PD_DDR_DDR7=1;PD_CR1_C17 = 1;PD_CR2_C27 = 0;} //-------------------------------------------------------------- // Prototype : void I2C_Init(void) // Calls :

实验八 IIC通信协议

实验八I2C通信协议 一、实验目的: 1、培养学生阅读资料的能力; 2、加深学生对I2C总线通信协议的理解; 3、加强学生对模块化编程的理解; 二、实验环境: 1、硬件环境:PC机一台、单片机实验板一块、母头串口交叉线、USB电源线; 2、软件环境:keil uVision2集成开发环境; STC-ISP下载上位机软件; 三、实验原理: 要学会I2C通信协议的编程,关键是要看懂并掌握其时序图,理解对I2C通信协议相关子程序的实验编写。I2C通信协议的总线时序图如下所示: I2C总线时序图 I2C相关子程序的详细介绍 1、起始信号:SCL为高电平时,SDA由高电平向低电平跳变,开始传送数据。 2、结束信号:SCL为高电平时,SDA由低电平向高电平跳变,结束传送数据。 起始信号和结束信号的时序图如下所示: 起始信号和结束信号的时序图 起始信号的流程如下:

1、SCL和SDA拉高,保持时间约为0.6us-4us; 2、拉低SDA,保持时间为约为0.6us-4us; 3、拉低时钟线 结束信号的流程如下: 1、SCL置高电平,SDA置低电平,保持时间约为0.6us-4us 2、SDA拉高,保持时间约为1.2-4us; 应答信号:接收数据的IC在接收到8bit数据后,向发送数据的IC发出特定的低电平脉冲,表示已收到数据。CPU向受控单元发出一个信号后,等待受控单元发出一个应答信号,CPU接收到应答信号后,根据实际情况作出是否继续传递信号的判断。 若未收到应答信号,由判断为受控单元出现故障。应答信号的时序图如下所示: 应答时序图 发送时的应答信号 ;**********应答信号********** ACK: SETB SDA ;数据线置高 SETB SCL ;时钟线置高 ACALL DELAY JB SDA,$ ;等待数据线变低 ACALL DELAY CLR SCL ;时钟线置低 RET 注意:这里如果数据线一直为高将进入死循环,所以一般我们都会在这做一个容错的处理。具体的程序如下: ACK: MOV R4,#00H SETB SDA SETB SCL LOP0: JNB SDA,LOP DJNZ R4,LOP0 ;循环255次 LOP: ACALL DEL CLR SCL RET 接收时的应答信号

stm8中断使用

stm8中断使用 工程应用分析 最近的一个项目中用到了stm8s,一个比较重要的知识点就是中断的使用。暂且称stm8s这边做从机,要进行双机通信。stm8s作“从机”接收数据,也可以发送数据给主机。 自定了一个通信协议,一个CLK线,一个DAT线,CLK线总是由主机边控制。类似于I2C通信,CLK为高时,DAT由高到底表示开始。CLK 位高时,DAT由低到高表示结束。CLK为高电平时,DAT线数据为保持,为低电平时允许数据跳变。实际的时序图如下: 我这边接收数据其实有很多种方法,比如: 1.可以在程序主循环while(1)中每一次周期监视检测电平的变化,来达到判断信号的目的 2.采用延时,很多常用的通信会采用,比如我们接收数据,在高电平读数据,传送16位数据,得到第一个CLK高电平之后,可以直接延时固定间隔时间读,就可以得到下一个高电平时DAT数据,以此类推 3.采用中断,不依赖于时间,完全依赖于硬件检测电平变化 4.采用中断加延时的方法 评价: 1的方法,对时间要求比较高,因为有传输速度的要求,电平变化本来比较快,应尽可能缩短主循环一次执行时间,后续添加其他功能会有影响 2的方法,对时间要求比较高,双机通信,一对一尚可,如果一对很多,不稳定,待验证 3的方法,完全依赖于自身的硬件,比较稳定 4的方法,依然存在2的缺点,情况类似 最终实现方法DAT触发条件为上升沿和下降沿,CLK触发条件为上升沿 DAT触发,检测DAT电平,只有开始和结束符合条件,所以可以用这个来判断开始位和结束位。CLK上升沿触发中断,读DAT,可以保证肯定是在高电平时读的数据。俩个中断同时开启,最终的操作还是简单的,参考代码如下:

汇编语言中断程序设计

汇编语言程序设计实验报告 学院:计算机科学与技术专业:计算机科学与技术班级:计科131

LEA DX,FNAME MOV CX,0 ;语句1 INT 21H JC EXIT MOV FNUM,AX MOV BX,AX ;语句2 MOV CX,100 MOV AH,40H LEA DX ,BUF INT 21H MOV BX,FNUM MOV AH,3EH INT 21H EXIT: MOV AH,4CH INT 21H CODE ENDS END START 使用相应的文本编辑器建立文件,内容如上所示。 2.汇编并运行此程序后,在当前目录建立的文件名是什么其内容是什么 1>汇编: C:\masm> masm lab7; 2>连接: C:\masm> link lab7; 3>运行: C:\masm> lab7 3.若将语句1 改为mov cx,1,则运行情况与前面会有什么区别 4.若将语句1 改为mov cx,2,则运行结果同上会有什么不同并简要说明此语句的作用. 5.若将语句2 改为mov bx,1,则运行结果会有什么不同简要说明则语句的作用. 实验二:编写0 号中断的处理程序,使得在除法溢出发生时,在屏幕中间显示字符串“divide error!”,然后返回到DOS。源程序下: assume cs:code code segment start: mov ax,cs mov ds,ax

mov si,offset do mov ax,0 mov es,ax mov di,200h mov cx,offset doend-offset do ;安装中断例程cld rep movsb mov word ptr es:[0],200h mov word ptr es:[2],0 ;设置中断向量表 mov dx,0ffffh mov bx,1 ;测试一下 div bx mov ax,4c00h int 21h do:jmp short dostart db 'divide error!' dostart: mov ax,0 mov ds,ax mov si,202h mov ax,0b800h mov es,ax mov di,160*12+60 mov cx,13 s: mov al,ds:[si] mov ah,15 mov es:[di],ax inc si inc di inc di loop s mov ax,4c00h int 21h doend:nop code ends end start

计算机组成原理中断实验报告

北京建筑大学 2015/2016 学年第二学期 课程设计 课程名称计算机组成原理综合实验 设计题目微程序控制器设计与实现 系别电信学院计算机系 班级计141 学生姓名艾尼瓦尔·阿布力米提 学号 完成日期二〇一六年七月八日星期五 成绩 指导教师 (签名) 计算机组成综合实验任务书

指令执行流程图; ?5、利用上端软件,把所编写的微程序控制器内容写入实验台中控制器中。 ?6、利用单拍测试控制器与编程的要求是否一致。如果有错误重新修改后再写入控制器中。 7、编写一段测试程序,测试控制器运行是否正确。 实验目的 1.融合贯通计算机组成原理课程,加深对计算机系统各模块的工作原理及相互联系(寄存器堆、运算器、存储器、控制台、微程序控制器)。 2.理解并掌握微程序控制器的设计方法和实现原理,具备初步的独立设计能力;3.掌握较复杂微程序控制器的设计、调试等基本技能;提高综合运用所学理论知识独立分析和解决问题的能力。 实验电路 1. 微指令格式与微程序控制器电路 2.微程序控制器组成 仍然使用前面的CPU组成与机器指令执行实验的电路图,但本次实验加入中断系统。这是一个简单的中断系统模型,只支持单级中断、单个中断请求,有中断屏蔽功能,旨在说明最基本的原理。

中断屏蔽控制逻辑分别集成在2片GAL22V10(TIMER1 和TIMER2)中。其ABEL语言表达式如下: INTR1 := INTR; INTR1.CLK = CLK1; IE := CLR & INTS # CLR & IE & !INTC; IE.CLK= MF; INTQ = IE & INTR1; 其中,CLK1是TIMER1产生的时钟信号,它主要是作为W1—W4的时钟脉冲,这里作为INTR1的时钟信号,INTE的时钟信号是晶振产生的MF。INTS微指令位是INTS机器指令执行过程中从控制存储器读出的,INTC微指令位是INTC机器指令执行过程中从控制存储器读出的。INTE是中断允许标志,控制台有一个指示灯IE显示其状态,它为1时,允许中断,为0 时,禁止中断。当INTS = 1时,在下一个MF的上升沿IE变1,当INTC = 1时,在下一个MF的上升沿IE变0。CLR信号实际是控制台产生的复位信号CLR#。当CLR = 0时,在下一个CLK1的上升沿IE变0。当 CLR=1 且INTS = 0 且 INTC = 0时,IE保持不变。 INTR是外部中断源,接控制台按钮INTR。按一次INTR按钮,产生一个中断请求正脉冲INTR。INTR1是INTR经时钟CLK1同步后产生的,目的是保持INTR1与实验台的时序信号同步。INTR脉冲信号的上升沿代表有外部中断请求到达中断控制器。INTQ是中断屏蔽控制逻辑传递给CPU的中断信号,接到微程序控制器上。当收到INTR脉冲信号时,若中断允许位INTE=0,则中断被屏蔽,INTQ仍然为0;若INTE =1,则INTQ =1。

简单的I2C协议理解 i2c程序(调试通过)

简单的I2C协议理解 一. 技术性能: 工作速率有100K和400K两种; 支持多机通讯; 支持多主控模块,但同一时刻只允许有一个主控; 由数据线SDA和时钟SCL构成的串行总线; 每个电路和模块都有唯一的地址; 每个器件可以使用独立电源 二. 基本工作原理: 以启动信号START来掌管总线,以停止信号STOP来释放总线; 每次通讯以START开始,以STOP结束; 启动信号START后紧接着发送一个地址字节,其中7位为被控器件的地址码,一位为读/写控制位R/W,R /W位为0表示由主控向被控器件写数据,R/W为1表示由主控向被控器件读数据; 当被控器件检测到收到的地址与自己的地址相同时,在第9个时钟期间反馈应答信号; 每个数据字节在传送时都是高位(MSB)在前; 写通讯过程: 1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线; 2. 发送一个地址字节(包括7位地址码和一位R/W); 3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信号(ACK); 4. 主控收到ACK后开始发送第一个数据字节; 5. 被控器收到数据字节后发送一个ACK表示继续传送数据,发送NACK表示传送数据结束; 6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线; 读通讯过程: 1. 主控在检测到总线空闲的状况下,首先发送一个START信号掌管总线; 2. 发送一个地址字节(包括7位地址码和一位R/W); 3. 当被控器件检测到主控发送的地址与自己的地址相同时发送一个应答信

号(ACK); 4. 主控收到ACK后释放数据总线,开始接收第一个数据字节; 5. 主控收到数据后发送ACK表示继续传送数据,发送NACK表示传送数据结束; 6. 主控发送完全部数据后,发送一个停止位STOP,结束整个通讯并且释放总线; 四. 总线信号时序分析 1. 总线空闲状态 SDA和SCL两条信号线都处于高电平,即总线上所有的器件都释放总线,两条信号线各自的上拉电阻把电平拉高; 2. 启动信号START 时钟信号SCL保持高电平,数据信号SDA的电平被拉低(即负跳变)。启动信号必须是跳变信号,而且在建立该信号前必修保证总线处于空闲状态; 3. 停止信号STOP 时钟信号SCL保持高电平,数据线被释放,使得SDA返回高电平(即正跳变),停止信号也必须是跳变信号。 4. 数据传送 SCL线呈现高电平期间,SDA线上的电平必须保持稳定,低电平表示0(此时的线电压为地电压),高电平表示1(此时的电压由元器件的VDD决定)。只有在SCL线为低电平期间,SDA上的电平允许变化。 5. 应答信号ACK I2C总线的数据都是以字节(8位)的方式传送的,发送器件每发送一个字节之后,在时钟的第9个脉冲期间释放数据总线,由接收器发送一个ACK(把数据总线的电平拉低)来表示数据成功接收。 6. 无应答信号NACK 在时钟的第9个脉冲期间发送器释放数据总线,接收器不拉低数据总线表示一个NACK,NACK有两种用途: a. 一般表示接收器未成功接收数据字节; b. 当接收器是主控器时,它收到最后一个字节后,应发送一个NACK信号,以通知被控发送器结束数据发送,并释放总线,以便主控接收器发送一个停止信号STOP。 五. 寻址约定

STM8L探索套件学习笔记-EXTI外部中断(二)

STM8L探索套件学习笔记-EXTI外部中断(二) 上节讲到GPIO 口可以作为外部中断使用,今天我们就使用探索套件上的USER 按键,翻转LED1 灯。外部中断叙述如下图所示,USER KEY 连到的是PC.1 所以使用的是EXTI1 中断线,和STM32 的中断方式比较接近。 首先我们把KEY 的GPIO 设置为输入中断使能 GPIO_Init(KEY_PORT,KEY_PIN,GPIO_Mode_In_FL_IT); 然后配置中断1 为下降沿低电平触发 EXTI_SetPinSensitivity(EXTI_Pin_1, EXTI_Trigger_Falling_Low); 设置中断的优先级 ITC_SetSoftwarePriority(EXTI1_IRQn, ITC_PriorityLevel_1); 开全局中断 enableInterrupts(); 最后我们到中断文件里面STM8L15X_it.c 设置 INTERRUPT_HANDLER(EXTI1_IRQHandler, 9) { /* In order to detect unexpected events during development, it is recommended to set a breakpoint on the following instruction. */ GPIO_ToggleBits(GPIOE, GPIO_Pin_7); Delay(0xFFFF); EXTI_ClearITPendingBit(EXTI_IT_Pin1); } tips:感谢大家的阅读,本文由我司收集整编。仅供参阅!

I2C总线协议规范 v2.1

THE I2C-BUS SPECIFICATION VERSION 2.1 JANUARY 2000

CONTENTS 1PREFACE. . . . . . . . . . . . . . . . . . . . . . . . . . .3 1.1Version 1.0 - 1992. . . . . . . . . . . . . . . . . . . . 3 1.2Version 2.0 - 198. . . . . . . . . . . . . . . . . . . . . 3 1.3Version 2.1 - 1999. . . . . . . . . . . . . . . . . . . . 3 1.4Purchase of Philips I2C-bus components . . 3 2THE I2C-BUS BENEFITS DESIGNERS AND MANUFACTURERS. . . . . . . . . . . . . . .4 2.1Designer benefits . . . . . . . . . . . . . . . . . . . . 4 2.2Manufacturer benefits. . . . . . . . . . . . . . . . . 6 3INTRODUCTION TO THE I2C-BUS SPECIFICATION . . . . . . . . . . . . . . . . . . . . .6 4THE I2C-BUS CONCEPT . . . . . . . . . . . . . . .6 5GENERAL CHARACTERISTICS . . . . . . . . .8 6BIT TRANSFER . . . . . . . . . . . . . . . . . . . . . .8 6.1Data validity . . . . . . . . . . . . . . . . . . . . . . . . 8 6.2START and STOP conditions. . . . . . . . . . . 9 7TRANSFERRING DATA. . . . . . . . . . . . . . .10 7.1Byte format . . . . . . . . . . . . . . . . . . . . . . . . 10 7.2Acknowledge. . . . . . . . . . . . . . . . . . . . . . . 10 8ARBITRATION AND CLOCK GENERATION . . . . . . . . . . . . . . . . . . . . . .11 8.1Synchronization . . . . . . . . . . . . . . . . . . . . 11 8.2Arbitration . . . . . . . . . . . . . . . . . . . . . . . . . 12 8.3Use of the clock synchronizing mechanism as a handshake. . . . . . . . . . . 13 9FORMATS WITH 7-BIT ADDRESSES. . . .13 107-BIT ADDRESSING . . . . . . . . . . . . . . . . .15 10.1Definition of bits in the first byte . . . . . . . . 15 10.1.1General call address. . . . . . . . . . . . . . . . . 16 10.1.2START byte . . . . . . . . . . . . . . . . . . . . . . . 17 10.1.3CBUS compatibility. . . . . . . . . . . . . . . . . . 18 11EXTENSIONS TO THE STANDARD- MODE I2C-BUS SPECIFICATION . . . . . . .19 12FAST-MODE. . . . . . . . . . . . . . . . . . . . . . . .19 13Hs-MODE . . . . . . . . . . . . . . . . . . . . . . . . . .20 13.1High speed transfer. . . . . . . . . . . . . . . . . . 20 13.2Serial data transfer format in Hs-mode. . . 21 13.3Switching from F/S- to Hs-mode and back . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2313.4Hs-mode devices at lower speed modes. . 24 13.5Mixed speed modes on one serial bus system. . . . . . . . . . . . . . . . . . . . . . . . . . . . 24 13.5.1F/S-mode transfer in a mixed-speed bus system. . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 13.5.2Hs-mode transfer in a mixed-speed bus system. . . . . . . . . . . . . . . . . . . . . . . . . . . . 25 13.5.3Timing requirements for the bridge in a mixed-speed bus system. . . . . . . . . . . . . . 27 1410-BIT ADDRESSING. . . . . . . . . . . . . . . . 27 14.1Definition of bits in the first two bytes. . . . . 27 14.2Formats with 10-bit addresses. . . . . . . . . . 27 14.3General call address and start byte with 10-bit addressing. . . . . . . . . . . . . . . . . . . . 30 15ELECTRICAL SPECIFICATIONS AND TIMING FOR I/O STAGES AND BUS LINES. . . . . . . . . . . . . . . . . . . . 30 15.1Standard- and Fast-mode devices. . . . . . . 30 15.2Hs-mode devices. . . . . . . . . . . . . . . . . . . . 34 16ELECTRICAL CONNECTIONS OF I2C-BUS DEVICES TO THE BUS LINES . 37 16.1Maximum and minimum values of resistors R p and R s for Standard-mode I2C-bus devices . . . . . . . . . . . . . . . . . . . . . 39 17APPLICATION INFORMATION. . . . . . . . . 41 17.1Slope-controlled output stages of Fast-mode I2C-bus devices. . . . . . . . . . . . 41 17.2Switched pull-up circuit for Fast-mode I2C-bus devices . . . . . . . . . . . . . . . . . . . . . 41 17.3Wiring pattern of the bus lines. . . . . . . . . . 42 17.4Maximum and minimum values of resistors R p and R s for Fast-mode I2C-bus devices . . . . . . . . . . . . . . . . . . . . . 42 17.5Maximum and minimum values of resistors R p and R s for Hs-mode I2C-bus devices . . . . . . . . . . . . . . . . . . . . . 42 18BI-DIRECTIONAL LEVEL SHIFTER FOR F/S-MODE I2C-BUS SYSTEMS . . . . 42 18.1Connecting devices with different logic levels. . . . . . . . . . . . . . . . . . . . . . . . . 43 18.1.1Operation of the level shifter . . . . . . . . . . . 44 19DEVELOPMENT TOOLS AVAILABLE FROM PHILIPS. . . . . . . . . . . . . . . . . . . . . 45 20SUPPORT LITERATURE . . . . . . . . . . . . . 46

基于STM8的外部中断实验

例程四按键中断 其实在上个例程就说那个中断的,但不是重点说,例程四就重点说下这个中断的设置,主要是针对外部中断,对于其他的中断,到时在相应的模块里面会说的。在STM8S207RB这个芯片里面有很多IO口都可以触发中断的。主要是GPIO_A,GPIO_B,GPIO_C,GPIO_D,GPIO_E,这五组IO口都可以触发外部中断,所以大家以后要设计电路的话,必须先要查看先对应的文档来看下,了解清楚芯片的资料才好设置。其实大家学会调用库里面的函数的话,这些初始化相当来说就很容易的了。 以上外部中断的设置来自“STM8寄存器.pdf”文档第74页 下面看下电路图先吧,只要当你清楚电路具体的链接,才能完成相对应的初始化。

用到内部的资源 "stm8s_clk.h" "stm8s_exti.h" "stm8s_gpio.h" "stm8s_uart1.h" "stm8s_clk.c" "stm8s_exti.c" "stm8s_gpio.c" "stm8s_uart1.c" 看完了电路图,照样是先看主函数

在主函数里面最重要的是Buttom_Init();的初始化,其他的初始话上前几个例程已经有介绍过,相信大家也很清楚了。下面重点讲下Buttom_Init()。 函数原型: 第一条语句是设置Buttom1和Buttom2相对应的IO为上拉输入; 第二条语句是设置GPIOD,也即是按键,为下降沿触发中断。 __enable_interrupt();这条语句是开总中断,在上一个例程里面说过了,以后凡是有触发中断的都要用上这条语句,所以说这条语句很重要的。 下面讲下外部中断常用的几个函数,这些函数都是库有的,可以直接调用的。

内部中断、外部中断、硬件中断和软件中断分析

软件中断、硬件中断、外部中断、内部中断 2010-01-30 16:35:05| 分类:电子爱好者|字号订阅 8086/8088把中断分为内部中断和外部中断两大类。为了支持多任务和虚拟存储器等功能,80386把外部中断称为“中断”,把内部中断称为“异常”。与8086/8088一样,80386通常在两条指令之间响应中断或异常。80386最多处理256种中断或异常。 1.中断 对80386而言,中断是由异步的外部事件引起的。外部事件及中断响应与正执行的指令没有关系。通常,中断用于指示I/O设备的一次操作已完成。与8086/8088一样,80386有两根引脚INTR和NMI接受外部中断请求信号。INTR接受可屏蔽中断请求。NMI接受不可屏蔽中断请求。在80386中,标志寄存器EFLAGS中的IF标志决定是否屏蔽可屏蔽中断请求。 外部硬件在通过INTR发出中断请求信号的同时,还要向处理器给出一个8位的中断向量。处理器在响应可屏蔽中断请求时,读取这个由外部硬件给出的中断向量号。处理器对这个中断向量号并没有规定。但在具体的微机系统中,系统必须通过软件和硬件的配合设置,使得给出的这个中断向量号不仅与外部中断源对应,而且要避免中断向量号使用冲突情况的出现。可编程中断控制器芯片8259A可配合80386工作,能够根据设置向处理器提供上述中断向量号,还能处理中断请求的优先级。每个8259A芯片可以支持8路中断请求信号,如果使用9个8259A芯片(一个主片,8个从片),就可使80386在单个引脚INTR上接受多达64个中断源的中断请求信号。 处理器不屏蔽来自NMI的中断请求。处理器在响应NMI中断时,不从外部硬件接收中断向量号。与8086/8088一样,在80386中,不可屏蔽中断所对应的中断向量号固定为2。为了不可屏蔽中断的嵌套,每当接受一个NMI中断,处理器就在内部屏蔽了再次响应NMI,这一屏蔽过程直到执行中断返回指令IRET后才结束。所以,NMI处理程序应以IRET指令结束。 2.异常 异常是80386在执行指令期间检测到不正常的或非法的条件所引起的。异常与正执行的指令有直接的联系。例如,执行除法指令时,除数等于0。再如,执行指令时发现特权级不正确。当发生这些情况时,指令就不能成功完成。软中断指令“INT n”和“INTO”也归类于异常而不称为中断,这是因为执行这些指令产生异常事件。 80386识别多种不同类别的异常,并赋予每一种类别以不同的中断向量号。异常发生后,处理器就象响应中断那样处理异常。即根据中断向量号,转相应的中断处理程序。把这种中断处理程序称为异常处理程序可能更合适。 根据引起异常的程序是否可被恢复和恢复点不同,把异常进一步分类为故障(Fault)、陷阱(Trap)和中止(Abort)。我们把对应的异常处理程序分别称为故障处理程序、陷阱处理程序和中止处理程序。 故障是在引起异常的指令之前,把异常情况通知给系统的一种异常。80386认为故障是可排除的。当控制转移到故障处理程序时,所保存的断点CS及EIP的值指向引起故障的指令。这样,在故障处理程序把故障排除后,执行IRET返回到引起故障的程序继续执行时,刚才引起故障的指令可重新得到执行。这种重新执行,不需要操作系统软件的额外参与。故障的发现可能在指令开始执行之前,也可能在指令执行期间。如果在指令执行期间检测到故障,那么中止故障指令,并把指令的操作数恢复为指令开始执行之前的值。这可保证故障指令的重新执行得到正确的结果。例如,在一条指令的执行期间,如果发现段不存在,那么停止该指令的执行,并通知系统产生段故障,对应的段故障处理程序可通过加载该段的方法来排除故障,之后,原指令就可成功执行,至少不再发生段不存在的故障。

关于IIC的通信协议程序

#define uchar unsigned char #define uint unsigned int #define ulong unsigned long #define _BV(bit) (1 << (bit)) #ifndef cbi #define cbi(reg,bit) reg &= ~_BV(bit) #endif #ifndef sbi #define sbi(reg,bit) reg |= _BV(bit) #endif extern uchar dog; /* void delay_1ms(uchar xtal) { uchar i; for(i=0;i<(uint)(143*xtal-2);i++) {;} } //2 延时nms void delay_ms(uchar m, uchar fosc) { uchar i; i=0; while(i DSP/BIOS软件中断(SWI) 一、SWI模块概述 在DSP/BIOS内核中,系统管理并运行的线程分为四个等级:硬件中断服务程序、软件中断服务程序、任务和后台空闲函数,优先级依次降低。每个软件中断服务程序都对应一个函数,当然,每个软件中断也可以单独设置优先级。高优先级的软件中断会抢占正在执行的低优先级的软件中断 所有软件中断都是通过DSP/BIOS内核的API调用来启动。一旦启动了一个SWI 对象,此时,系统将为该SWI对象中的函数创建一个运行时间表。因此,当一个软件中断被启动后,其对象函数不一定会立即执行,而是会按照时间表在执行队列中根据优先级排队等候运行。DSP/BIOS根据软件中断优先级来判断是否要暂停当前运行的线程。 中断线程(包括硬件中断和软件中断)都是使用相同的堆栈来执行的。当中断发生时,新的线程就会添加到栈顶,系统会执行一次任务切换(Context Switch)。由于高优先级软件中断会打断低优先级的软件中断的运行,所以SWI模块在运行高优先级软件中断前会自动保存寄存器中的内容。在高优先级软件中断运行完成后,寄存器会恢复原来的内容,以便继续运行原来的低优先级中断。如果没有启动其他高优先级的软件中断,低优先级的软件中断就会运行。DSP/BIOS内核虽然具有抢占的特点,但如果没有导致任务切换的API 函数调用,系统则不会主动切换道其他线程去执行的。(理解这点在实际应用中很重要,即如果现在运行的是低优先级软中断对应的函数,如果你不在函数中调用如SWI_post()启动更高优先级的软件中断或启动了比自身低的优先级中断,则当前软中断就不会被打断,执行直到退出)。 个人经验:尽量不要在一个软中断对应的函数中去启动另一个比其本身优先级高的软件中断,因为根据抢占原则,其本身将被打断,从而CPU转去执行高优先级软中断对应的函数,低优先级的实时性将得不到保证,当有多级优先级及系统复杂情况下甚至引起系统瘫痪。也不要设置很多的优先级。当然这也不是绝对的,如果系统规划的好,利用好软中断的基于优先级抢占式的特点会大大简化你的设计。 二、SWI的执行 通过调用SWI_andn,SWI_sec,SWI_inc,SWI_or,SWI_post可以使软件中断被调度执行。这些函数本身可以在程序的任何地方调用------中断服务程序ISR中,周期函数中,空闲函数中或其他软件中断函数中。 当一个SWI对象被触发时,SWI管理器将该软件中断添加到一个被触发软件中断的列表中等待,然后SWI管理器检查软件中断当前是否被使能。如果使能,SWI管理器将该SWI对象的优先级和当前运行线程的优先级进行比较。若当前运行线程是后台空闲循环IDL或是一个更低优先级的SWI,那么SWI管理器将这个SWI对象从被触发SWI对象列表中移除,并将CPU控制权从当前线程交给SWI对象,开始执行SWI函数。 Note:1.当一个SWI开始执行后,必须无阻塞地运行到结束; 2.当在HWI中调用时,调用任何会触发软件中断的SWI函数的代码必须包装在一个HWI_enter/HWI_exit宏调用中,或者由HWI调度程序调用; 3.如果一个软件中断在SWI管理器将其从被触发SWI对象列表中移除之前,被触发多次,其SWI函数只会执行一次。这个类似硬件中断的特征:即在CPU清除中断标志寄存器中相应的中断标志为之前,如果该硬件中断触发多次,对应的HWI只会执行一次。DSPBIOS软件中断(SWI)