PCB堆叠设计规范总则

PCB设计规范总则CHECKLIST

自检人:________________

检查人:________________

检查日期:_____年_____月_____日

审查内容:____________________________________________________________________

审查结果:通过□不通过□

说明:____________________________________________________________________

修改内容

序号

总 则 条 款

执行情况

说明

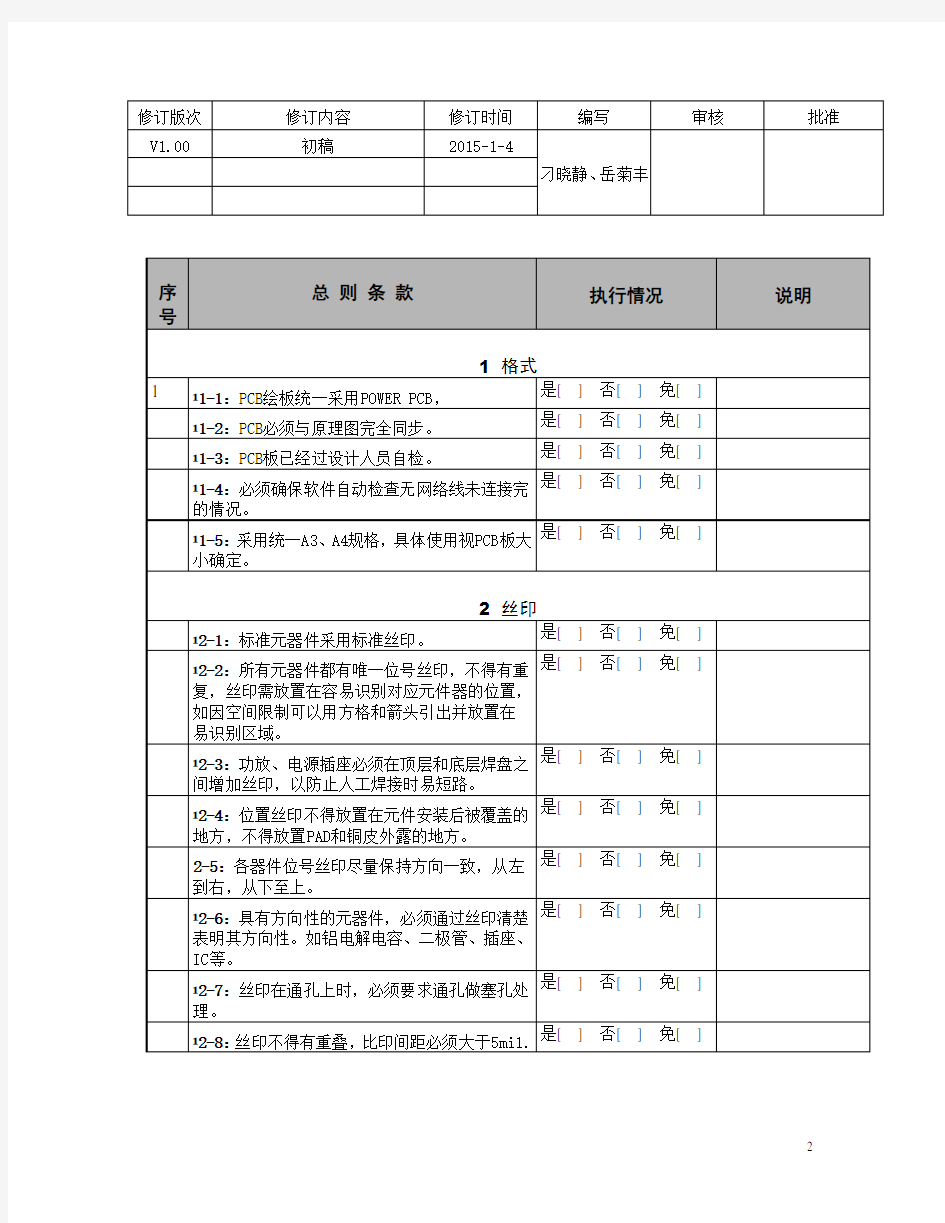

1 格式

1 11-1:PCB 绘板统一采用POWER PCB , 是[ ] 否[ ] 免[ ] 11-2:PCB 必须与原理图完全同步。 是[ ] 否[ ] 免[ ] 11-3:PCB 板已经过设计人员自检。

是[ ] 否[ ] 免[ ] 11-4:必须确保软件自动检查无网络线未连接完的情况。

是[ ] 否[ ] 免[ ]

11-5:采用统一A3、A4规格,具体使用视PCB 板大小确定。

是[ ] 否[ ] 免[ ]

2 丝印

12-1:标准元器件采用标准丝印。

是[ ] 否[ ] 免[ ]

12-2:所有元器件都有唯一位号丝印,不得有重复,丝印需放置在容易识别对应元件器的位置,如因空间限制可以用方格和箭头引出并放置在易识别区域。

是[ ] 否[ ] 免[ ]

12-3:功放、电源插座必须在顶层和底层焊盘之间增加丝印,以防止人工焊接时易短路。

是[ ] 否[ ] 免[ ]

12-4:位置丝印不得放置在元件安装后被覆盖的地方,不得放置PAD 和铜皮外露的地方。

是[ ] 否[ ] 免[ ]

2-5:各器件位号丝印尽量保持方向一致,从左到右,从下至上。

是[ ] 否[ ] 免[ ]

12-6:具有方向性的元器件,必须通过丝印清楚表明其方向性。如铝电解电容、二极管、插座、IC 等。

是[ ] 否[ ] 免[ ]

12-7:丝印在通孔上时,必须要求通孔做塞孔处理。

是[ ] 否[ ] 免[ ]

12-8:丝印不得有重叠,比印间距必须大于5mil.

是[ ] 否[ ] 免[ ]

修订版次 修订内容 修订时间 编写 审核 批准 V1.00 初稿 2015-1-4

刁晓静、岳菊丰

序

总则条款执行情况说明号

是[ ] 否[ ] 免[ ] 12-9:PCB板名、日期、版本号等制板信息丝印位

置必须放置在明显无元器件的较大面处。

是[ ] 否[ ] 免[ ] 2-10:元件名称丝印要清楚可直接目视且尽可能

直接标在元件近旁

是[ ] 否[ ] 免[ ] 12-11:必须要求PCB制造厂将其公司识别标识丝

印上去。

是[ ] 否[ ] 免[ ] 12-12:PCB板的丝印GERBER文件必须单独输出并

经CAM检查没有问题。

是[ ] 否[ ] 免[ ] 12-13:为了方便制成板的安装,所有螺丝孔都要

做出白油丝印标识。

是[ ] 否[ ] 免[ ] 12-14:所有连接器必须用3角形标注第1脚的位

置。

是[ ] 否[ ] 免[ ] 12-15:所有跳线电阻在短接时,需用铜皮短接,

不允许使用2D线

是[ ] 否[ ] 免[ ] 12-16:所有IC必须用1mm直径圆标注第1脚,圆点

位置必须在后装IC后不会被盖住。

是[ ] 否[ ] 免[ ]12-17:为了保证锡道连续性,要求开窗的地方无

丝印;为了便于器件插装和维修,器件位号不应

被安装后器件所遮挡,丝印不能压在导通孔、焊

盘上。

3 走线

是[ ] 否[ ] 免[ ] 13-1:供电电源(+12V)与地的走线建议满足以

下要求:

1电源走线与地线之间的间隔尽量小,最大间距

0.5mm,电源和地线线宽尽量宽,最小2mm(引到

IC或其他无法达到2mm宽度的元器件除外),电

源线上阻值尽量小,最大为0.5欧。

13-2:IC退耦电容尽量放置靠近IC的PIN脚。是[ ] 否[ ] 免[ ]

序

总则条款执行情况说明号

是[ ] 否[ ] 免[ ] 13-3:当电源和地区分为数字和模拟时,退耦电

容不得跨接,数字电源和模拟电源不得重叠:

1

是[ ] 否[ ] 免[ ] 13-4:独立的电源或地之间不得在隔开处采用电

容或走线跨接:

1

是[ ] 否[ ] 免[ ] 13-5:同一位置采用并联电容退耦时,电容之间

采用不同数量级的容值,如10nF和100nF.

是[ ] 否[ ] 免[ ] 13-6:晶振必须放置在离IC最近的旁边,晶振时钟

信号走线最长1cm,两晶振时钟走线之间间距尽

量小,最大间距0.5mm.

是[ ] 否[ ] 免[ ]13-7:晶振时钟信号走线尽量不要打孔,保持同

层走线。

是[ ] 否[ ] 免[ ] 13-7:晶振走线周围地需要用地包围起来,其中的

地应与其他电源供电地和信号地分开。

1

1

是[ ] 否[ ] 免[ ] 13-8:匹配电阻要靠近信号的驱动端,对于I2C

如果驱动多个I2C元器,匹配电阻尽量放置在被

驱动的终端。

序

总则条款执行情况说明号

13-9:功放输出走线最小宽度为40MIL。是[ ] 否[ ] 免[ ]

是[ ] 否[ ] 免[ ] 13-10:走线不得有一端浮空的情况,

1

是[ ] 否[ ] 免[ ] 13-11:对于重要高频信号,其布线长度不得与其

波长成整数倍关系。

13-12:走线不得采用锐角和直角。是[ ] 否[ ] 免[ ]

是[ ] 否[ ] 免[ ] 13-13:走线应从焊盘端中心位置引出。

1

是[ ] 否[ ] 免[ ] 13-14:走线不得偏移焊盘:

1

是[ ] 否[ ] 免[ ] 13-15:当和焊盘连接的走线比焊盘宽时,走线不

能覆盖焊盘,应从焊盘末端引线:

1

序

总则条款执行情况说明号

是[ ] 否[ ] 免[ ] 13-16:密间距的SMT焊盘引脚需要连接时,应从

焊盘外部连接,不容许在焊脚间直接连接:

1

是[ ] 否[ ] 免[ ] 13-17: IC或连接器相邻PIN脚为相同网络时,不

得整体铺铜:

1

13-18:要求所有的走线及铜箔距离板边:V—CUT

边大于0.75mm,铣槽边大于0.35mm,布线离板边

距离要求≥0.5mm。

13-19:USB,走差分,信号线有完整的地平面参考,

90 Ohm差分阻抗。

13-20:CVBS,R,G,B AUDIO的R,L走12MIL,包地。

13-21:CLK走12MIL,走线短,包地,SD CARD走线

尽量短

13-22:GPS天线要做50 Ohm阻抗。

13-23:收音天线 75 Ohm阻抗。

3-24:DDR 50 Ohm阻抗,地址、数据等同组线

等长误差不超过50MIL。在有主芯片

Layout guide的情况下,必须满足Layout guide

要求。

序

总则条款执行情况说明号

13-25:BGA过孔到焊盘连接的走线需使狗骨头方

式,如图所示.

1

4 过孔

4-1:定位孔、螺丝孔内不得沉铜。是[ ] 否[ ] 免[ ]

是[ ] 否[ ] 免[ ] 4-2:元器件焊盘内不得有过孔,过孔离PAD最

边沿应大于0.3mm.

4-3:小于0.5mm的过孔必须做塞孔处理。是[ ] 否[ ] 免[ ]

是[ ] 否[ ] 免[ ] 4-4:元件有引线的下面不能有过孔,以防止短

路,如功放和类似封装的电源IC。

4-5:元件面贴有板的安装件,如导航核心板、

是[ ] 否[ ] 免[ ]

蓝牙模块,其下面尽量不走过孔,并且模块所贴

位置必须全部丝印盖住。

5 测试点

是[ ] 否[ ] 免[ ] 5-1:<2MM间距的插座需有测试点,其测试点尺

寸:¢08.0+0.1mm。。

是[ ] 否[ ] 免[ ] 5-2:测试点统一放置在BOTTOM层,对双面都有

元件的测试点放置在元器件少的那一面。

是[ ] 否[ ] 免[ ] 5-3:测试点的位置要尽量分散,均匀放置在PCB,

以防止PCB变形。测试点的密度不能大于每平方厘

米4-5 个

是[ ] 否[ ] 免[ ] 5-4:测试点与焊接面上的元件的间距应大于

2.54mm。

是[ ] 否[ ] 免[ ] 5-5:测试点相邻两点的边距大于等于1.8mm.

是[ ] 否[ ] 免[ ] 5-6:测试点到PCB 板边缘的距离应大于2.0mm。

是[ ] 否[ ] 免[ ] 5-7:测试点到定位孔的距离应该大于0.5mm,为

定位柱提供一定净空间。

是[ ] 否[ ] 免[ ] 5-8:供电电源正、负极测试点最小为2mm.

序

总则条款执行情况说明

号

是[ ] 否[ ] 免[ ] 5-9:测试点不得做在过孔上。

是[ ] 否[ ] 免[ ] 5-10:测试点必须固化位置,量产后PCB变更不

得变动测试点位置,除非得到工程确认可以移动

位置。

6 MARK点及工艺边

6-1:PCB板的MARK点不要放在工艺边上,要放

在板的对角线上,且不对称,便于过炉区分方向

6-2:需要拼板的单板,每块单元板上尽量保证

有MARK点,若由于空间原因单元板上无法布下

MARK点时,则单元板上可以不布MARK点,但应

保证拼板工艺边上有MARK点。

6-3:MARK点标准尺寸:¢1.0±0.1mm。周围3MM

范围内不设任何线路或元件

6-4:MARK和板边距离要保证在3MM以上,防

止PCB的MARK点被机器链条轨道或定位时被

边夹夹住无法识别;MARK与测试点距离中心距

≥5mm;

6-5:BGA、QFN以及小于0.4MM 脚间距的元器件

需加MARK点,其尺寸:¢0.5±0.05mm,如下图:

6-6:板边必须放置在拼板后较长边上。是[ ] 否[ ] 免[ ]

是[ ] 否[ ] 免[ ] 6-7:双面贴片元件PCB板不得与单面贴片拼在

一起。

6-8:如无元器件超出板边,固定板边宽度为3mm,

是[ ] 否[ ] 免[ ] 对于安装元器件后超出板边的,以最长器件外

边,一般是连接器最外边计算,边板宽度超出其

3mm.

6-9:板边必须两头有MARK点。工艺边上需标注

是[ ] 否[ ] 免[ ] 过炉方向。

7 拼板

序

总则条款执行情况说明号

是[ ] 否[ ] 免[ ] 7-1:拼板时必须完全对整齐,不能有偏差.有元

件外露在PCB板外的,拼板时需考虑外露器件不

影响相邻板对应元件的安装。

是[ ] 否[ ] 免[ ] 7-2:条型小板拼板注意避免开长槽,中间连接

小于50X50的必须拼版,工艺边加在拼版后的长

边,工艺边的宽度为5MM,有超过工艺边5MM的零

件工艺边应根据实际大小再增加

是[ ] 否[ ] 免[ ] 7-3:不规则形状的PCB 而使制成板加工有难

度的PCB,应在过板方向两侧加工艺边,对于

不规则的PCB需要用邮票孔连接时,建议邮票

孔外径向PCB内陷0.2~0.3mm

是[ ] 否[ ] 免[ ] 7-4:在同一位置当正反两面都有结构要求放置

元件时,要注意开槽、定位孔、插件脚与SMT焊

盘有无互相干涉(如SD卡座与USB两面同时安

装)。

是[ ] 否[ ] 免[ ] 7-5:邮票孔不允许金属化,要求孔径0.5mm,孔间

距0.5mm,每组3-5个邮票孔.对于长度小于20mm

小板,采用0.5mm孔径邮票孔,孔边间距0.25mm.

7-6:邮票孔间距0.5mm,即中心间距为1.0mm是[ ] 否[ ] 免[ ]

是[ ] 否[ ] 免[ ] 7-7:拼板用邮票孔连接时,要考虑分板后残留

的板边对组装时的影响.邮票孔的圆心向板内内

陷0.4mm。

是[ ] 否[ ] 免[ ] 17-8:邮票孔与其他孔(尤其插件孔)边沿间距

需大于0.8mm

是[ ] 否[ ] 免[ ] 17-9:邮票孔需要避开安装孔5mm以上,避开走线

2mm以上

是[ ] 否[ ] 免[ ] 17-10:螺丝孔封装的非沉铜孔让开铜皮的距离为

0.3mm

是[ ] 否[ ] 免[ ] 17-11:安装孔、螺钉孔以中心为准在半径3mm内

是禁布区

是[ ] 否[ ] 免[ ] 17-12:对于拼板的尺寸范围限制在宽(100mm~

250mm)×长(200mm~300mm)内,

是[ ] 否[ ] 免[ ] 17-13:拼板的间隙面积大于4cm2且间隙的宽度大

于10mm 时,要把间隙补上(否则SMT检测不到

板)。

是[ ] 否[ ] 免[ ] 17-14:当板边有缺口,或板内有大于35mm×35mm

的空缺时,建议在缺口增加辅助块。如果辅助块

大于100×50,最少要添加2组邮票孔,如果辅助

块大于150×50,最少要添加3组邮票孔

序

总则条款执行情况说明号

是[ ] 否[ ] 免[ ] 17-15:屏蔽框(盖)与其它元件之间焊盘间距≧

0.5mm

是[ ] 否[ ] 免[ ] 17-16:对于规则工艺边采用V-CUT划槽,V形槽的

角度要求30度,两侧深度各为PCB厚度的1/3。

是[ ] 否[ ] 免[ ] 17-17:不规则拼板需要采用铣槽加 V-cut 方式

时,铣槽间距应大于1.2mm

8 螺钉孔的禁布区范围