ARM中断实现串口通信

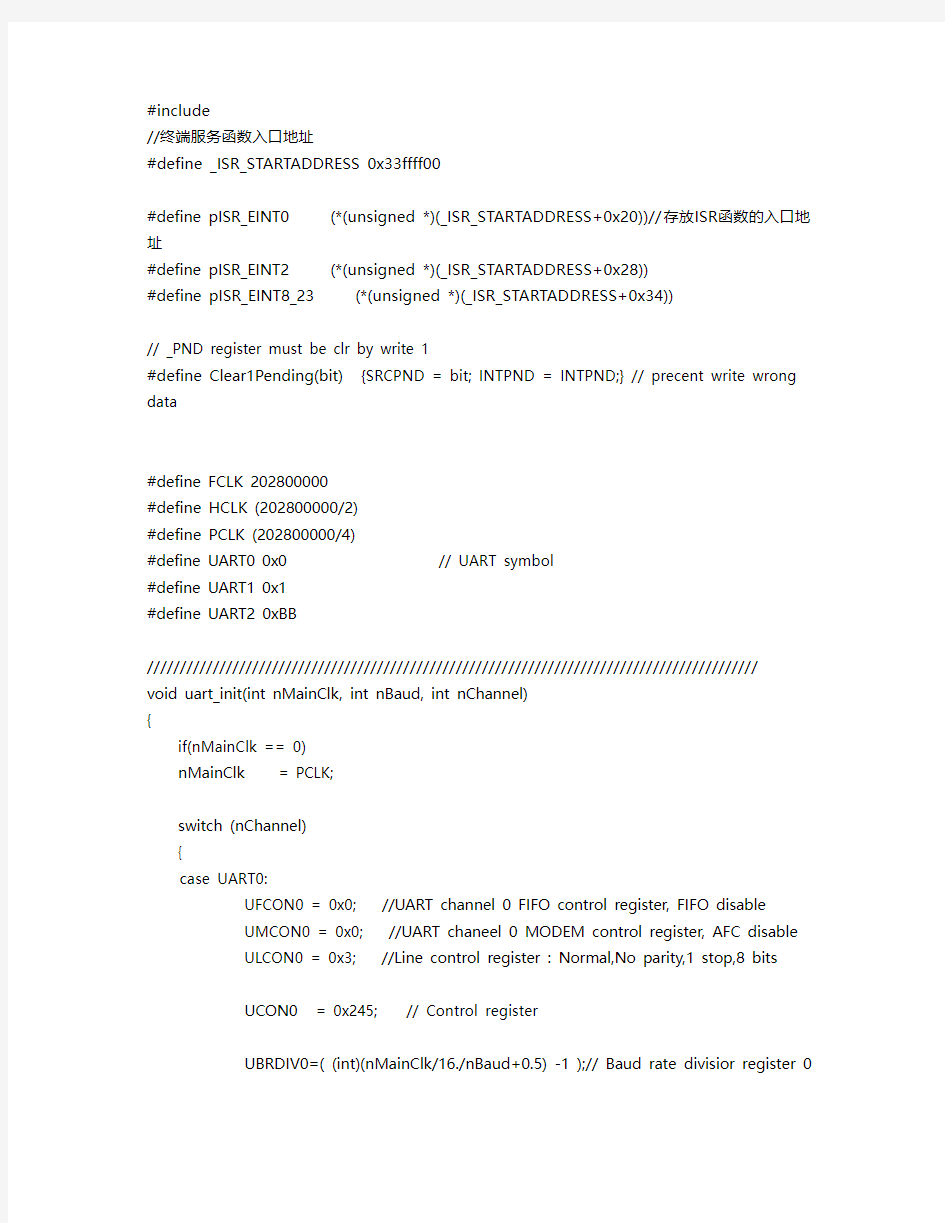

#include

//终端服务函数入口地址

#define _ISR_STARTADDRESS 0x33ffff00

#define pISR_EINT0 (*(unsigned *)(_ISR_STARTADDRESS+0x20))//存放ISR函数的入口地址

#define pISR_EINT2 (*(unsigned *)(_ISR_STARTADDRESS+0x28))

#define pISR_EINT8_23 (*(unsigned *)(_ISR_STARTADDRESS+0x34))

// _PND register must be clr by write 1

#define Clear1Pending(bit) {SRCPND = bit; INTPND = INTPND;} // precent write wrong data

#define FCLK 202800000

#define HCLK (202800000/2)

#define PCLK (202800000/4)

#define UART0 0x0 // UART symbol

#define UART1 0x1

#define UART2 0xBB

/////////////////////////////////////////////////////////////////////////////////////////////

void uart_init(int nMainClk, int nBaud, int nChannel)

{

if(nMainClk == 0)

nMainClk = PCLK;

switch (nChannel)

{

c ase UART0:

UFCON0 = 0x0; //UART channel 0 FIFO control register, FIFO disable

UMCON0 = 0x0; //UART chaneel 0 MODEM control register, AFC disable

ULCON0 = 0x3; //Line control register : Normal,No parity,1 stop,8 bits

UCON0 = 0x245; // Control register

UBRDIV0=( (int)(nMainClk/16./nBaud+0.5) -1 );// Baud rate divisior register 0

break;

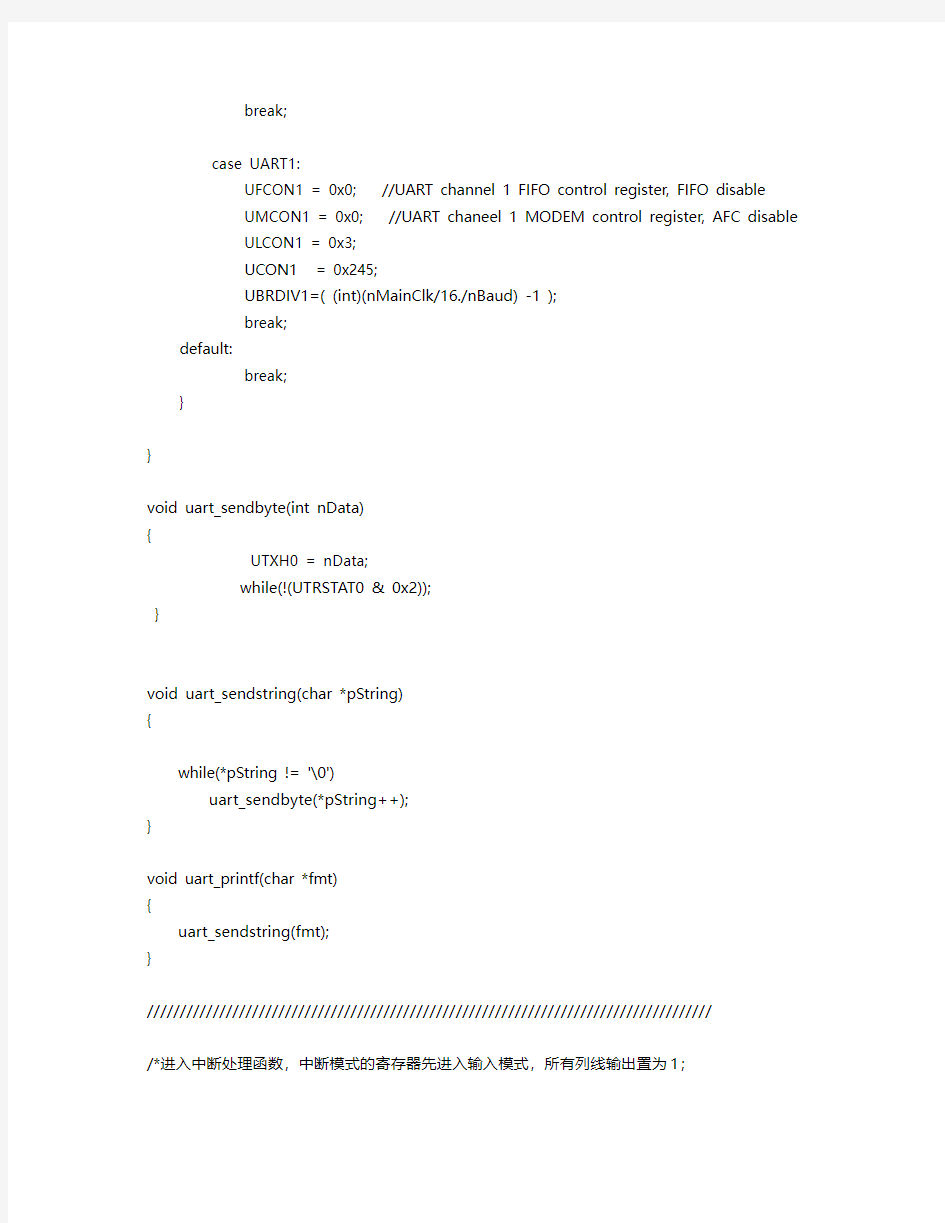

case UART1:

UFCON1 = 0x0; //UART channel 1 FIFO control register, FIFO disable

UMCON1 = 0x0; //UART chaneel 1 MODEM control register, AFC disable

ULCON1 = 0x3;

UCON1 = 0x245;

UBRDIV1=( (int)(nMainClk/16./nBaud) -1 );

break;

default:

break;

}

}

void uart_sendbyte(int nData)

{

UTXH0 = nData;

while(!(UTRSTAT0 & 0x2));

}

void uart_sendstring(char *pString)

{

while(*pString != '\0')

uart_sendbyte(*pString++);

}

void uart_printf(char *fmt)

{

uart_sendstring(fmt);

}

//////////////////////////////////////////////////////////////////////////////////////

/*进入中断处理函数,中断模式的寄存器先进入输入模式,所有列线输出置为1;

依次把列线拉低,检测输入端口,EINT的值,如果为低点平,说明该列被拉低;

这样行列坐标就确定了。

处理完成,返回中断模式,IO口重新设定为输出低电平,使能下降沿触发中断;*/

void __irq int0_int(void)

{

// 10 11 12 16

// enter input_mod ,kscan0-kscan3 output 1

GPGDAT &= ~(1<<11);// 0

GPEDAT |= (1<<13); // 1

GPGDAT |= ((1<<2)|(1<<6));//output 1

GPFCON &= ~(0x3<<0);//EINT_mod to input_mod

if(((GPFDAT>>0)&1)==0) uart_printf("key10\n");

GPEDAT |= (1<<11);//set pre_bit

GPGDAT &= ~(1<<6); // clr exam_bit

if(((GPFDAT>>0)&1)==0) uart_printf("key11\n");

GPGDAT |= (1<<6); //set pre_bit

GPEDAT &= ~(1<<13); //clr exam_bit

if(((GPFDAT>>0)&1)==0) uart_printf("key12\n");

GPEDAT |= (1<<13); //set pre_bit

GPGDAT &= ~(1<<2); //clr exam_bit

if(((GPFDAT>>0)&1)==0) uart_printf("key16\n");

//enter eint_mod , ouput_mod 0

GPFCON |= (0x2<<0); //EINT0 mod

GPEDAT &= ~((1<<11)|(1<<13));//output 0

GPGDAT &= ~((1<<2)|(1<<6)); //output 0

// clr _pend bit is essential after E_int

Clear1Pending(0x1);

}

void __irq int2_int(void)

{

// 7 8 9 15

GPGDAT &= ~(1<<11);// 0

GPEDAT |= (1<<13); // 1

GPGDAT |= ((1<<2)|(1<<6));//output 1

GPFCON &= ~(0x3<<4);// input_mod

if(((GPFDAT>>2)&1)==0) uart_printf("key7");

GPEDAT |= (1<<11);

GPGDAT &= ~(1<<6);

if(((GPFDAT>>2)&1)==0) uart_printf("key8\n");

GPGDAT |= (1<<6);

GPEDAT &= ~(1<<13);

if(((GPFDAT>>2)&1)==0) uart_printf("key9\n");

GPEDAT |= (1<<13);

GPGDAT &= ~(1<<2);

if(((GPFDAT>>2)&1)==0) uart_printf("key15\n");

GPFCON |= (0x2<<4); // EINT2 mod

GPEDAT &= ~((1<<11)|(1<<13));

GPGDAT &= ~((1<<2)|(1<<6));

// uart_printf(" EINT2 interrupt occurred.\n");

Clear1Pending(0x1<<2);

}

void __irq int11_int(void)

{

//4 5 6 14

if(((EINTPEND>>11)&1)==1)

{

GPGDAT &= ~(1<<11);// 0

GPEDAT |= (1<<13); // 1

GPGDAT |= ((1<<2)|(1<<6));//output 1

GPGCON &= ~(0x3<<6);// input mod

if(((GPGDAT>>3)&1)==0) uart_printf("key4\n");

GPEDAT |= (1<<11);

GPGDAT &= ~(1<<6);

if(((GPGDAT>>3)&1)==0) uart_printf("key5\n");

GPGDAT |= (1<<6);

GPEDAT &= ~(1<<13);

if(((GPGDAT>>3)&1)==0) uart_printf("key6\n");

GPEDAT |= (1<<13);

GPGDAT &= ~(1<<2);

if(((GPGDAT>>3)&1)==0) uart_printf("key14\n");

GPGCON |= (0x2<<6);//EINT 11 mod

GPEDAT &= ~((1<<11)|(1<<13));

GPGDAT &= ~((1<<2)|(1<<6));

EINTPEND=(1<<11);

// uart_printf(" EINT11 interrupt occurred.\n");

}

else

{ // 1 2 3 13

GPGDAT &= ~(1<<11);// 0

GPEDAT |= (1<<13); // 1

GPGDAT |= ((1<<2)|(1<<6));//output 1

GPGCON &= ~(0x3<<22);// input mod

if(((GPGDAT>>11)&1)==0) uart_printf("key1\n");

GPEDAT |= (1<<11);

GPGDAT &= ~(1<<6);

if(((GPGDAT>>11)&1)==0) uart_printf("key2\n");

GPGDAT |= (1<<6);

GPEDAT &= ~(1<<13);

if(((GPGDAT>>11)&1)==0) uart_printf("key3\n");

GPEDAT |= (1<<13);

GPGDAT &= ~(1<<2);

if(((GPGDAT>>11)&1)==0) uart_printf("key13\n");

GPGCON |= (0x2<<22);//EINT19 mod

GPEDAT &= ~((1<<11)|(1<<13));

GPGDAT &= ~((1<<2)|(1<<6));

EINTPEND=(1<<19);//sub_pend_clr

}

Clear1Pending(0x1<<5); // pnd_clr

}

/////////////////////////////////////////////////////////////////////////////

void int_init(void)

{

SRCPND = SRCPND;// clear all interrupt

INTPND = INTPND;// clear all interrupt

EINTPEND = 0xffffff;

GPFCON=(GPFCON & 0)|(0x2<<0)|(0x2<<4) ;//EINT0 EINT2

GPGCON=(GPGCON & 0)|(0x2<<6)|(0x2<<22)|(0x1<<12)|(0x1<<4);//EINT11 EINT19 GPGDAT=(GPGDAT & ~((0x1<<2)|(0x1<<6)));// GPG6,GPG2 output 0

//中断处理函数的绑定

pISR_EINT0 = (unsigned int)int0_int;//isrEINT0;

pISR_EINT2 = (unsigned int)int2_int;

pISR_EINT8_23 = (unsigned int)int11_int; // isrEINT11_19;

GPECON=(GPECON & 0)|(0x1<<22)|(0x1<<26);//GPE11 GPE13 output 0

GPEDAT=(GPEDAT & ~((0x1<<11)|(0x1<<13)));

// write 1 to bits to clr

EINTPEND = 0xffffff;

EXTINT0 = (EXTINT0 & 0) | (0x2<<0)|(0x2<<8); //EINT0=falling edge triggered

EXTINT1 = (EXTINT1 & 0) | (0x2<<12);//EINT11=falling edge triggered

EXTINT2 = (EXTINT2 & 0) | (0x2<<12); //EINT19=falling edge triggered

EINTMASK &= ~((1<<11)|(1<<19)); // enable eint0,eint2

INTMSK &= ~((0x1)|(0x1<<5)|(0x1<<2)); // enable eint11,eint19

}

void int_test(void)

{

int_init();

uart_printf("\n External Interrupt Test Example\n");

}

/********************************************************************************************* */

int main()

{

WTCON = 0; //close watchdog

CLKDIVN = (1<<1) | 1; //设置1:2:4

MPLLCON = (0xa1<<12) | (0x3<<4) | 0x1; // Fin=12MHz FCLK=202.8MHz

// concerning setting for uart

GPHCON = 0x2afaaa;

GPHUP = 0x7ff;

uart_init(PCLK, 115200, UART0);

uart_printf ("boot success...");

// call init_

int_test();

while(1);

}

;/*****************************************************************************/

;/* S3C2410A.S: Startup file for Samsung S3C410A */ ;/*****************************************************************************/

;/* <<< Use Configuration Wizard in Context Menu >>> */ ;/*****************************************************************************/

;/* This file is part of the uVision/ARM development tools. */

;/* Copyright (c) 2005-2006 Keil Software. All rights reserved. */

;/* This software may only be used under the terms of a valid, current, */

;/* end user licence from KEIL for a compatible version of KEIL software */

;/* development tools. Nothing else gives you the right to use this software. */

;/*****************************************************************************/

; *** Startup Code (executed after Reset) ***

; Standard definitions of Mode bits and Interrupt (I & F) flags in PSRs

Mode_USR EQU 0x10

Mode_FIQ EQU 0x11

Mode_IRQ EQU 0x12

Mode_SVC EQU 0x13

Mode_ABT EQU 0x17

Mode_UND EQU 0x1B

Mode_SYS EQU 0x1F

I_Bit EQU 0x80 ; when I bit is set, IRQ is disabled

F_Bit EQU 0x40 ; when F bit is set, FIQ is disabled

;//

;//

;//

;//

;//

;//

;//

;//

UND_Stack_Size EQU 0x00000000

SVC_Stack_Size EQU 0x00000008

ABT_Stack_Size EQU 0x00000000

FIQ_Stack_Size EQU 0x00000000

IRQ_Stack_Size EQU 0x00000080

USR_Stack_Size EQU 0x00000400

Stack_Size EQU (UND_Stack_Size + SVC_Stack_Size + ABT_Stack_Size + \

FIQ_Stack_Size + IRQ_Stack_Size + USR_Stack_Size)

AREA STACK, NOINIT, READWRITE, ALIGN=3

Stack_Mem SPACE Stack_Size

Stack_Top EQU Stack_Mem + Stack_Size

;//

;//

;//

Heap_Size EQU 0x00000000

AREA HEAP, NOINIT, READWRITE, ALIGN=3

Heap_Mem SPACE Heap_Size

; Clock Management definitions

CLK_BASE EQU 0x4C000000 ; Clock Base Address LOCKTIME_OFS EQU 0x00 ; LOCKTIME Offset MPLLCON_OFS EQU 0x04 ; MPLLCON Offset UPLLCON_OFS EQU 0X08 ; UPLLCON Offset CLKCON_OFS EQU 0x0C ; CLKCON Offset CLKSLOW_OFS EQU 0x10 ; CLKSLOW Offset CLKDIVN_OFS EQU 0X14 ; CLDKIVN Offset CAMDIVN_OFS EQU 0X18 ; CAMDIVN Offset

;//

;//

;// Mpll = (m * Fin) / (p * 2^s)

;//

;// m = MDIV + 8

;//

;// p = PDIV + 2

;//

;// s = SDIV

;//

;//

;// Upll = ( m * Fin) / (p * 2^s),Uclk must be 48MHZ to USB device ;//

;// m = MDIV + 8,if Fin=12MHZ MDIV could be 0x38 ;//

;// p = PDIV + 2,if Fin=12MHZ PDIV could be 0x2

;//

;// s = SDIV ,if Fin=12MHZ SDIV could be 0x2

;//

;//

;//

;//

;//

;//

;// PLL Clock: FCLK = FMPLL

;// Slow Clock: FCLK = Fin / (2 * SLOW_VAL), SLOW_VAL > 0

;// Slow Clock: FCLK = Fin, SLOW_VAL = 0

;//

;// 0: UCLK ON(UPLL is also turned on) 1: UCLK OFF (UPLL is also turned off)

;//

;// 0: Turn on PLL.After PLL stabilization time (minimum 300us), SLOW_BIT can be cleared to 0. 1: Turn off PLL. PLL is turned off only when SLOW_BIT is 1. ;//

;//

;//

;//

;//

;// 0: HCLK = FCLK/1, 01 : HCLK = FCLK/2

;//

;// 0: PCLK has the clock same as the HCLK/1,1: PCLK has the clock same as the HCLK/2

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

;//

CLK_SETUP EQU 1

MPLLCON_Val EQU 0x0005C080

UPLLCON_Val EQU 0x00028080

CLKCON_Val EQU 0x0007FFF0

CLKSLOW_Val EQU 0x00000004

LOCKTIME_Val EQU 0x00FFFFFF

CLKDIVN_Val EQU 0X00000000

;Interrupt definitions

INTOFFSET EQU 0X4A000014 ;Address of Interrupt offset Register

;//

;//

;// You could define Interuupt Vctor Table address.

;// The Interrupt Vector Table address must be word aligned adress. ;//

IntVT_SETUP EQU 1

IntVTAddress EQU 0x33FFFF20

; Watchdog Timer definitions

WT_BASE EQU 0x53000000 ; WT Base Address

WTCON_OFS EQU 0x00 ; WTCON Offset

WTDAT_OFS EQU 0x04 ; WTDAT Offset

WTCNT_OFS EQU 0x08 ; WTCNT Offset

;//

;//

;//

;//

;//

;// <0=> 1/16 <1=> 1/32 <2=> 1/64 <3=> 1/128

;// Clock Division Factor

;//

;//

;//

WT_SETUP EQU 1

WTCON_Val EQU 0x00008021

WTDAT_Val EQU 0x00008000

; Memory Controller definitions

MC_BASE EQU 0x48000000 ; Memory Controller Base Address

;//

MC_SETUP EQU 1

;//

;//

;// <0=> 1 Data <1=> 4 Data <2=> 8 Data <3=> 16 Data ;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> 6 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks <3=> 4 clks

;// <4=> 6 clk <5=> 8 clks <6=> 10 clks <7=> 14 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;//

;//

;//

;// <0=> 8-bit <1=> 16-bit <2=> 32-bit <3=> Rsrvd

;//

;// <0=> WAIT Disable

;// <1=> WAIT Enable

;//

;// <0=> Not using UB/LB

;// <1=> Using UB/LB

;//

;// <0=> 1 Data <1=> 4 Data <2=> 8 Data <3=> 16 Data ;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> 6 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks <3=> 4 clks

;// <4=> 6 clk <5=> 8 clks <6=> 10 clks <7=> 14 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;//

;//

;//

;// <0=> 8-bit <1=> 16-bit <2=> 32-bit <3=> Rsrvd

;//

;// <0=> WAIT Disable

;// <1=> WAIT Enable

;//

;// <0=> Not using UB/LB

;// <1=> Using UB/LB

;//

;// <0=> 1 Data <1=> 4 Data <2=> 8 Data <3=> 16 Data

;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> 6 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks <3=> 4 clks

;// <4=> 6 clk <5=> 8 clks <6=> 10 clks <7=> 14 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;//

;//

;//

;// <0=> 8-bit <1=> 16-bit <2=> 32-bit <3=> Rsrvd

;//

;// <0=> WAIT Disable

;// <1=> WAIT Enable

;//

;// <0=> Not using UB/LB

;// <1=> Using UB/LB

;//

;// <0=> 1 Data <1=> 4 Data <2=> 8 Data <3=> 16 Data ;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> 6 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks <3=> 4 clks

;// <4=> 6 clk <5=> 8 clks <6=> 10 clks <7=> 14 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;//

;//

;//

;// <0=> 8-bit <1=> 16-bit <2=> 32-bit <3=> Rsrvd

;//

;// <0=> WAIT Disable

;// <1=> WAIT Enable

;//

;// <0=> Not using UB/LB

;// <1=> Using UB/LB

;//

;// <0=> 1 Data <1=> 4 Data <2=> 8 Data <3=> 16 Data ;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> 6 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks <3=> 4 clks

;// <4=> 6 clk <5=> 8 clks <6=> 10 clks <7=> 14 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;//

;//

;//

;// <0=> 8-bit <1=> 16-bit <2=> 32-bit <3=> Rsrvd

;//

;// <0=> WAIT Disable

;// <1=> WAIT Enable

;//

;// <0=> Not using UB/LB

;// <1=> Using UB/LB

;//

;// <0=> 1 Data <1=> 4 Data <2=> 8 Data <3=> 16 Data

;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> 6 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks <3=> 4 clks

;// <4=> 6 clk <5=> 8 clks <6=> 10 clks <7=> 14 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;//

;//

;//

;// <0=> 32M <1=> 64M <2=> 128M <4=> 2M <5=> 4M <6=> 8M <7=> 16M

;//

;// <0=> 8-bit <1=> 16-bit <2=> 32-bit <3=> Rsrvd

;//

;// <0=> WAIT Disable

;// <1=> WAIT Enable

;//

;// <0=> Not using UB/LB

;// <1=> Using UB/LB

;//

;// <0=> ROM or SRAM

;// <3=> SDRAM

;//

;//

;// <0=> 1 Data <1=> 4 Data <2=> 8 Data <3=> 16 Data

;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> 6 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks ;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks ;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks <3=> 4 clks ;// <4=> 6 clk <5=> 8 clks <6=> 10 clks <7=> 14 clks ;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks ;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks ;//

;//

;//

;// <0=> 8-bit <1=> 9-bit <2=> 10-bit <3=> Rsrvd ;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> Rsrvd ;//

;// <0=> Normal

;// <1=> Reduced Power

;//

;// <0=> DISABLE

;// <1=> ENABLE

;//

;// <0=> DISABLE

;// <1=> ENABLE

;//

;// <0=> 1

;//

;// <0=> Sequential

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks

;//

;// <0=> Mode Register Set

;//

;// <0=> 0

;//

;//

;//

;//

;//

;// <0=> 32M <1=> 64M <2=> 128M <4=> 2M <5=> 4M <6=> 8M <7=> 16M

;//

;// <0=> 8-bit <1=> 16-bit <2=> 32-bit <3=> Rsrvd

;//

;// <0=> WAIT Disable

;// <1=> WAIT Enable

;//

;// <0=> Not using UB/LB

;// <1=> Using UB/LB

;//

;// <0=> ROM or SRAM

;// <3=> SDRAM

;//

;//

;// <0=> 1 Data <1=> 4 Data <2=> 8 Data <3=> 16 Data

;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> 6 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks <3=> 4 clks

;// <4=> 6 clk <5=> 8 clks <6=> 10 clks <7=> 14 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;// <0=> 0 clk <1=> 1 clk <2=> 2 clks <3=> 4 clks

;//

;//

;//

;// <0=> 8-bit <1=> 9-bit <2=> 10-bit <3=> Rsrvd ;//

;// <0=> 2 clks <1=> 3 clks <2=> 4 clks <3=> Rsrvd ;//

;// <0=> Normal

;// <1=> Reduced Power

;//

;// <0=> DISABLE

;// <1=> ENABLE

;//

;// <0=> DISABLE

;// <1=> ENABLE

;//

;// <0=> 1

;//

;// <0=> Sequential

;//

;// <0=> 1 clk <1=> 2 clks <2=> 3 clks

;//

;// <0=> Mode Register Set

;//

;// <0=> 0

;//

;//

;//

;//

;//

;// <0=> Disable <1=> Enable

;//

;// <0=> CBR/Auto Refresh

;// <1=> Self Refresh

;//

;// <0=> 2 clks

;// <1=> 3 clks

;// <2=> 4 clks

;// <3=> Rsrvd

嵌入式系统实验报告-串行通信实验

《嵌入式系统实验报告》 串行通信实验 南昌航空大学自动化学院050822XX 张某某 一、实验目的: 掌握μC/OS-II操作系统的信号量的概念。 二、实验设备: 硬件:PC机1台;MagicARM2410教学实验开发平台台。 软件:Windows 98/2000/XP操作系统;ADS 1.2集成开发环境。 三、实验内容: 实验通过信号量控制2个任务共享串口0打印字符串。为了使每个任务的字符串信息(句子)不被打断,因此必须引入互斥信号量的概念,即每个任务输出时必须独占串口0,直到完整输出字符串信息才释放串口0。 四、实验步骤: (1)为ADS1.2增加DeviceARM2410专用工程模板(若已增加过,此步省略)。 (2)连接EasyJTAG-H仿真器和MagicARM2410实验箱,然后安装EasyJTAG-H仿真器(若已经安装过,此步省略),短接蜂鸣器跳线JP9。 (3)启动ADS 1.2,使用ARM Executable Image for DeviceARM2410(uCOSII)工程模板建立一个工程UART0_uCOSII。(本范例在ADS文件夹中操作) (4)在ADS文件夹中新建arm、Arm_Pc、SOURCE文件夹。将μC/OS 2.52源代码添加到SOURCE文件夹,将移植代码添加到arm文件夹,将移植的PC服务代码添加到Arm_Pc文件夹。 (5)在src组中的main.c中编写主程序代码。 (6)选用DebugRel生成目标,然后编译链接工程。 (7)将MagicARM2410实验箱上的UART0连接跳线JP1短接,使用串口延长线把MagicARM2410实验箱的CZ11与PC机的COM1连接。 注意:CZ11安装在MagicARM2410实验箱的机箱右侧。 (8)PC机上运行“超级终端”程序(在Windows操作系统的【开始】->【程序】->【附件】->【通讯】->【超级终端】),新建一个连接,设置串口波持率为115200,具体设置参考图3.5,确定后即进入通信状态。 (9)选择【Project】->【Debug】,启动AXD进行JTAG仿真调试。 (10)全速运行程序,程序将会在main.c的主函数中停止(因为main函数起始处默认设置有断点)。 (11)可以单步运行程序,可以设置/取消断点,或者全速运行程序,停止程序运行,在超级终端上观察任务0和任务1的打印结果。 五、实验结论与思考题(手写,打印无效): 1、如果任务0删除语句“OSSemPost(UART0_Sem);”,那么程序还能完全正常无误运行么?如果发生异常会出现什么现象?

串口中断服务函数集

串口中断服务函数集 https://www.360docs.net/doc/6d11254883.html, 2003-4-22 电子工程师网站 //本函数集来自“51单片机世界”,作者斑竹丁丁(聂小猛)。 //主页地址https://www.360docs.net/doc/6d11254883.html, //串口中断服务程序,仅需做简单调用即可完成串口输入输出的处理 //出入均设有缓冲区,大小可任意设置。 //可供使用的函数名: //char getbyte(void);从接收缓冲区取一个byte,如不想等待则在调用前检测inbufsign是否为1。 //getline(char idata *line, unsigned char n); 获取一行数据回车结束,必须定义最大输入字符数 //putbyte(char c);放入一个字节到发送缓冲区 //putbytes(unsigned char *outplace,j);放一串数据到发送缓冲区,自定义长度//putstring(unsigned char code *puts);发送一个定义在程序存储区的字符串到串口 //puthex(unsigned char c);发送一个字节的hex码,分成两个字节发。 //putchar(uchar c,uchar j);输出一个无符号字符数的十进制表示,必须标示小数点的位置,自动删除前面无用的零 //putint(uint ui,uchar j);输出一个无符号整型数的十进制表示,必须标示小数点的位置,自动删除前面无用的零 //delay(unsigned char d); 延时n x 100ns //putinbuf(uchar c);人工输入一个字符到输入缓冲区 //CR;发送一个回车换行 //********************************************************************** *** #include

ARM中的中断要点

一、S5PV210中中断的特点 1、特点 ? Supports 93 vectored IRQ interrupts ? Fixed hardware interrupts priority levels ? Programmable interrupt priority levels ? Supports Hardware interrupt priority level masking ? Programmable interrupt priority level masking ? Generates IRQ and FIQ ? Generates Software interrupt 2、FIQ与IRQ的区别 1)FIQ和IRQ并不是中断源,而是中断的类型,我们可以将一个中断源设置成FIQ也可以设置成IRQ。2)FIQ是快速中断,IRQ是一般中断,FIQ的响应时间比IRQ短。 3)FIQ的优先级高于IRQ。 4)FIQ的分组寄存器(R8~R14)比IRQ(R13~R14)多。当在FIQ产生的时候,R8~R14不需要保存,响应的速度会快。 3、S5PV210的中断源

二、原理图分析

三、如何以中断的方式来检测按键:GPH2_2(EINT18) 、GPH2_3(EINT19) 按键的检测:轮询:将GPIO配置成输入……. 中断:将GPIO配置成外部中断……. 1、GPIO的配置,将一个GPIO配置成外部中断 2、外部中断的触发方式 (高电平、低电平、上升沿、下降沿)

3、外部中断的开关寄存器 0 = Enables Interrupt 打开中断 1 = Masked 关闭中断 4、外部中断判断寄存器 0 = Not occur 外部中断没有发生 1 = Occur interrupt 触发了中断

嵌入式_USART 串口通讯

USART 串口通讯-存储池方式 【实验目的】 学习USART的特性及功能 学习USART 串口通讯的使用 【实验原理】 1. USART介绍 通用同步异步收发器(USART)提供了一种灵活的方法与使用工业标准NRZ异步串行 数据格式的外部设备之间进行全双工数据交换。USART利用分数波特率发生器提供宽范围的波特率选择。它支持同步单向通信和半双工单线通信,也支持LIN(局部互连网),智能卡协议和IrDA(红外数据组织)SIR ENDEC规范,以及调制解调器(CTS/RTS)操作。它还允许多处理器通信。使用多缓冲器配置的DMA方式,可以实现高速数据通信。 2. USART特性 全双工的,异步通信 标准格式 分数波特率发生器系统 ─发送和接收共用的可编程波特率,最高达 4.5Mbits/s 可编程数据字长度(8位或9位) 可配置的停止位-支持1或2个停止位 LIN主发送同步断开符的能力以及LIN从检测断开符的能力 ─当USART硬件配置成LIN时,生成13位断开符;检测10/11位断开符发送方为同步传输提供时钟 编码器解码器 ─在正常模式下支持3/16位的持续时间 智能卡模拟功能 ─智能卡接口支持ISO7816-3标准里定义的异步智能卡协议 ─智能卡用到的0.5和 1.5个停止位 单线半双工通信 可配置的使用DMA的多缓冲器通信 ─在SRAM里利用集中式DMA缓冲接收/发送字节 单独的发送器和接收器使能位 检测标志 ─接收缓冲器满 ─发送缓冲器空 ─传输结束标志 校验控制 ─发送校验位 ─对接收数据进行校验 四个错误检测标志 ─溢出错误通用同步异步收发器(USART) ─噪音错误 ─帧错误

51单片机外部中断与定时器的实用

中断使能寄存器 通过设置中断使能寄存器 IE 的 EA 位 使能所有中断 每个中断源都有单独的使能位 可通过软件设置 IE 中相应的使能位在任何时候使能或禁能中断 中断使能寄存器 IE 的各 位如下所示 中断使能寄存器IE 位地址 0AFH 0AEH 0ADH 0ACH 0ABH 0AAH 0A9H 0A8H 位符号 EA / ET2 ES ET1 EX1 ET0 EX0 EA 使能标志位 置位则所有中断使能 复位则禁止所有中断保留 ET2 定时器2 中断使能 ES 串行通信中断使能 ET1 定时器 1 中断使能 EX1 外部中断 1 使能 ET0 定时器0 中断使能 EX0 外部中断 0使能 8051 支持两个中断优先级 有标准的中断机制, 低优先级的中断只能被高优先级的中断所中断 ,而高优先级的中断不能被中断。 中断优先级寄存器 每个中断源都可通过设置中断优先级寄存器IP 来单独设置中断优先级 如果每个中断源的相应位被置位 则该中断源的优先级为高,如果相应的位被复位, 则该中断源的优先级为低, 如果你觉得两个中断源不够用 ,别急以后我会教你如何增加中断优先级 表 A-5 示出了 IP 寄存器的各位 此寄存器可位寻址 IP 寄存器 位地址 0BFH 0BEH 0BDH 0BCH 0BBH 0BAH 0B9H 0B8H 位符号 / / / PS PT1 PX1 PT0 PX0 编号 中断源 中断向量 上电复位 0000H 0 外部中断0 0003H 1 定时器0溢出 000BH 2 外部中断1 0013H 3 定时器1溢出 001BH 4 串行口中断 0023H 5 定时器2溢出 002BH PT2 定时器 2中断优先级 PS 串行通信中断优先级 PT1 定时器 1中断优先级 PX1 外部中断1 优先级 PT0 定时器0中断优先级 PX0 外部中断0 优先级

2020年嵌入式串口通信设计参照模板

***************** 实践教学 ******************* 兰州理工大学 计算机与通信学院 2013年春季学期 嵌入式系统开发技术课程设计 题目:嵌入式串口通信设计 专业班级:通信工程四班 姓名: 学号: 指导教师: 成绩:

嵌入式是以应用为中心,以计算机技术为基础,软件硬件可剪裁,适应应用系统对功能、可靠性、成本、体积、功耗严格要求的专用计算机系统。随着嵌入式系统的发展和大规模应用,为了提升系统的整体性能,必须实现PC机和嵌入式计算机之间的通信。在实际开发应用中,串口通信是不可缺少的部分。 目前嵌入式系统与PC机之间一种非常重要而且普遍应用的通信方式。本文通过基于2410F 的嵌入式串口通信的实现,按照嵌入式系统的软、硬件结构组成,较为详细地介绍了串口通信的硬件电路和软件实现方法。通过与计算机串口间的接,实现在ARM 平台上,传输速率115200bps,接收来自串口(通过超级终端)的字符并将接收到的字符发送到超级终端,实现监测。与外部设备通信的基本功能。 关键字:嵌入式系统,串口通信,Linux系统

前言 ------------------------------------------------------------------------------------------- - 4 - 一、串口通信概述--------------------------------------------------------------------------- - 5 - 1.1 串口通信的原理 ------------------------------------------------------------------ - 5 - 1.2 串口通信的开发工具 ------------------------------------------------------------ - 5 - 1.2.1 2410F硬件平台简介---------------------------------------------------------- - 5 - 1.3 串口通信的基本任务 ------------------------------------------------------------ - 8 - 二、系统分析--------------------------------------------------------------------------------- - 9 - 三、串口驱动程序设计 ------------------------------------------------------------------- - 17 - 3.1 串口操作需要的头文件 -------------------------------------------------------- - 17 - 3.2 打开串口 -------------------------------------------------------------------------- - 17 - 3.3 串口设置 -------------------------------------------------------------------------- - 18 - 3.4 串口读写 -------------------------------------------------------------------------- - 20 - 3.5 关闭串口 -------------------------------------------------------------------------- - 22 - 四、总结-------------------------------------------------------------------------------------- - 23 - 参考文献-------------------------------------------------------------------------------------- - 24 - 附录----------------------------------------------------------------------------------------- - 25 -

基于linux的嵌入式串口通信

天津电子信息职业技术学院 嵌入式软件编程》课程报告 课程名称:基于linux 的嵌入式串口通信 课程代码:115229 姓名:甘琦 学号:48 专业:物联网应用技术 班级:物联S14-1 完成时间:2016 年10 月28 日

目录 摘要 (1) 前言 (2) 一、嵌入式串口通信概述 (2) 1.1嵌入式串口通信的原理 (2) 1.2嵌入式串口通信的开发工具 (2) 1.2.1 ............................................................. CC2530 功耗 2 1.2.2........................................................... ARM 简介 3 1.2.3................................................................ L inux 系统简介 3 1.3嵌入式串口通信的基本任务 (4) 1.4嵌入式串口通信协议及实现 (4) 二、RS-232C 标准 (5) 2.1引脚定义 (5) 2.2字符(帧)格式 (6) 2.3握手协议 (8) 2.4双机互连方式 (9) 2.4.1无硬件握手情况 (9) 2.4.2 .................................................................. DTR 和DSR握手情况9 三、嵌入式串口驱动程序设计 (10) 3.1嵌入式串口操作需要的头文件 (10) 3.2打开串口 (10) 3.3串口设置 (11) 3.4串口读写 (13) 3.5关闭串口 (14) 四、源程流程图 (15) 五、源程序代码 (15) 总结 (19)

利用中断实现UART串口

中断方式下进行串口通讯的正确方法 一般普遍的把串口通讯分为查询方式和中断方式。查询方式比较容易理解,各种书籍上都介绍的比较清楚。但中断方式,没有几本书讲得好的,甚至有些例程根本无法实际应用。 问题有: 1,半中断法。只使用接收中断,不使用发送中断,发送时还是依靠查询中断标志的办法;如下: ES = 0;//若是接收使用中断方式,某些单片机需要关中断。但C51不一定需要。这里只是示例。 SBUF = needsendchar; While (!TI); TI = 0; ES = 1; 这里的问题是:发送数据时需要等待数据发完才能继续其他工作,程序效率降低;发送时需要关中断,影响数据接收。 2,接收中断的处理方法错误。如下: 中断程序: void ser() interrupt 4 { RI = 0; temp = SBUF; //读走数据,放入缓存(全局的)变量 rx_flag = 1; //设置接收标志 } 主程序: void main(){ …;//初始化 While (1) { If (rx_flag ==1){//查询接收标志 rx_flag = 0; //清楚接收标志 x = temp; //从暂存变量读取数据 …;//接收处理 } …; //其它操作 } } 这里的问题是:如果串口接收数据的间隔时间小于“接收处理”和“其它操作”所用的时间时,接收数据会丢失一部分。 正确使用中断方式处理串口收发应达到以下目的: 1,完全使用中断控制接收和发送,以达到最快的收发速度。 2,接收和发送互不影响,达到全双工通讯效果。 3,应用程序不发生等待,以达到最高运行效率。

正确的中断发送方法如下: 1,建立一个足够大小的环形发送缓冲区,建立一个信号量(用于指示发送的数据量),建立一个发送标志位(用于指示发送状态)。 2,应用程序将数据写入环形发送缓冲区,查询发送接收标志,若不在发送状态,手动触发中断。 3,产生发送中断时,查询信号量,以判别发送缓冲区内是否有数据;若有,置发送标志位,从缓冲区读取数据发送,累减信号量;若无,清除发送标志位。 C51的例程如下: //变量定义 #define BUF_SIZE 0x10//环形收发缓冲区长度 //发送参数 char tx_circbuf[BUF_SIZE];//环形发送缓冲区 uint8 tx_sem;//信号量 bool tx_run;//发送标志位 uint8 tx_circin;//进环形缓冲区的位置指示 uint8 tx_circout;//出环形缓冲区的位置指示 //发送初始化程序 void tx_init(void){ //硬件初始化略 //发送参数初始化 tx_sem = 0; tx_run = False; tx_circin = 0; tx_circout = 0; } //中断程序 void tx_int(void) interrupt 4 { if (TI){ TI = 0; if (tx_sem){ SBUF = tx_circbuf [tx_circout]; // 发送缓冲区中的字符 if (++tx_circout >= BUF_SIZE) tx_circout = 0; tx_sem--;//累减信号量 tx_run = True;//置发送标志位 } else tx_run = False;//清除发送标志位 } } //发送处理程序,由应用程序调用 //输入:发送数据指针,发送数据长度

实验5 ARM中断编程

实验五 ARM中断编程 一、实验目的 1.学习键盘驱动原理。 2.掌握中断的使用方法。 二、实验内容 通过ARM的外部中断进行键盘的扫描,利用中断服务程序编写键盘的驱动,在超级终端上显示相应的键值。UART接收中断,以中断方式(而不是查询方式)实现串口数据的接收 三、预备知识 1.掌握在ADS1.2集成开发环境中编写和调试程序的基本过程。 2.会使用UltraEdit编辑C语言源程序。 3.了解ARM中断服务程序的框架结构。 4.了解编译后的映象文件的下载方法。 四、键盘驱动程序的原理 1.简单键盘扫描 通常在一个键盘中使用了一个瞬时接触开关,并且用如图1所示的简单电路,微处理器可以容易地检测到闭合。当开关打开时,通过处理器的I/O口的一个上拉电阻提供逻辑1;当开关闭合时,处理器的I/O口的输入将被拉低得到逻辑0。可遗憾的是,开关并不完善,因为当它们被按下或者被释放时,并不能够产生一个明确的1或者0。尽管触点可能看起来稳定而且很快地闭合,但与微处理器快速的运行速度相比,这种动作是比较慢的。当触点闭合时,其弹起就像一个球。弹起效果将产生如图2所示的好几个脉冲。弹起的持续时间通常将维持在5ms~30ms之间。如果需要多个键,则可以将每个开关连接到微处理器上它自己的输入端口。然而,当开关的数目增加时,这种方法将很快使用完所有的输入端口。为此我将用到矩阵键盘。 图1 简单键盘电路

图2 键盘抖动 2. 复杂矩阵键盘扫描 键盘上陈列这些开关最有效的方法(当需要5个以上的键时)就形成了一个如图3所示的二维矩阵。当行和列的数目一样多时,也就是方型的矩阵,将产生一个最优化的布列方式(I/O 端被连接的时候)。一个瞬时接触开关(按钮)放置在每一行与线一列的交叉点。矩阵所需的键的数目显然根据应用程序而不同。每一行由一个输出端口的一位驱动,而每一列由一个电阻器上拉且供给输入端口一位。 图3 矩阵键盘 键盘扫描过程就是让微处理器按有规律的时间间隔查看键盘矩阵,以确定是否有键被按下。一旦处理器判定有一个键按下,键盘扫描软件将过滤掉抖动并且判定哪个键被按下。每个键被分配一个称为扫描码的唯一标识符。应用程序利用该扫描码,根据按下的键来判定应该采取什么行动。换句话说,扫描码将告诉应用程序按下哪个键。

用定时器计数器设计一个简单的秒表

目录 摘要................................................................................................ 错误!未定义书签。 1 Proteus简介错误!未定义书签。 2 主要相关硬件介绍错误!未定义书签。 AT89C52简介错误!未定义书签。 四位数码管错误!未定义书签。 74LS139芯片介绍错误!未定义书签。 3 设计原理错误!未定义书签。 4 电路设计错误!未定义书签。 电路框图设计错误!未定义书签。 电路模块介绍错误!未定义书签。 控制电路错误!未定义书签。 译码电路错误!未定义书签。 数码管显示电路错误!未定义书签。 仿真电路图错误!未定义书签。 5 设计代码错误!未定义书签。 6 仿真图错误!未定义书签。 7 仿真结果分析错误!未定义书签。 8 实物图错误!未定义书签。 9 心得体会错误!未定义书签。 参考文献错误!未定义书签。

摘要 现在单片机的运用越来越宽泛,大到导弹的导航装置、飞机上各种仪表的控制、计算机的网络通讯与数据传输、工业自动化过程的实时控制和数据处理,小到广泛使用的各种智能IC卡、各种计时和计数器等等。本次课设我们要设计一个能显示计时状态和结果的秒表,它是基于定时器/计数器设计一个简单的秒表。 本次设计的数字电子秒表系统采用AT89C51单片机为中心器件,利用其定时器/计数器定时和记数的原理,结合显示电路、LED数码管以及外部中断电路来设计计时器。将软、硬件有机地结合起来,使得系统能够实现四位LED显示,显示时间为0~秒,计时精度为秒,能正确地进行计时,并显示计时状态和结果。其中软件系统采用汇编或者C语言编写程序,包括显示程序,定时中断服务,外部中断服务程序,延时程序等,并在keil中调试运行,硬件系统利用PROTEUS强大的功能来实现,简单切易于观察,在仿真中就可以观察到实际的工作状态。 关键词:秒表,AT89C51,proteus,C语言

基于linux的嵌入式串口通信

天津电子信息职业技术学院《嵌入式软件编程》课程报告 课程名称:基于linux的嵌入式串口通信 课程代码:115229 姓名:甘琦 学号:48 专业:物联网应用技术 班级:物联S14-1 完成时间:2016 年10 月28日

目录 摘要 (1) 前言 (2) 一、嵌入式串口通信概述 (2) 1.1 嵌入式串口通信的原理 (2) 1.2 嵌入式串口通信的开发工具 (2) 1.2.1 CC2530功耗 (2) 1.2.2 ARM简介 (3) 1.2.3 Linux系统简介 (3) 1.3 嵌入式串口通信的基本任务 (4) 1.4嵌入式串口通信协议及实现 (4) 二、 RS-232C标准 (5) 2.1引脚定义 (5) 2.2 字符(帧)格式 (6) 2.3握手协议 (8) 2.4 双机互连方式 (9) 2.4.1无硬件握手情况 (9) 2.4.2 DTR和DSR握手情况 (9) 三、嵌入式串口驱动程序设计 (10) 3.1 嵌入式串口操作需要的头文件 (10) 3.2 打开串口 (10) 3.3 串口设置 (11) 3.4 串口读写 (13) 3.5 关闭串口 (14) 四、源程流程图 (15) 五、源程序代码 (15) 总结 (19)

摘要 随着Internet的发展和后PC时代的到来,嵌入式系统以其可靠性强、体积小、专用性、成本低等特性得到日益广泛的应用。目前嵌入式系统技术已经成为了最热门的技术之一。与此同时,一个独立的嵌入式系统的功能缺陷也逐渐暴露出来。新一代嵌入计算系统的功能集成和应用模式使之迅速向网络化嵌入计算的方向发展,标准和统一的TCP/IP通信协议是独立于任何厂家的硬件的,因此嵌入环境下的实时网络通信成为嵌入计算技术研究的重点和热点。本文通过基于2410F 的嵌入式串口通信的实现,按照嵌入式系统的软、硬件结构组成,较为详细地介绍了串口通信的硬件电路和软件实现方法。 关键词:嵌入式串口通信 2410F

STM32串口中断接收方式详细比较

本例程通过PC机的串口调试助手将数据发送至STM32,接收数据后将所接收的数据又发送至PC机,具体下面详谈。。。 实例一: void USART1_IRQHandler(u8 GetData) { u8 BackData; if(USART_GetITStatus(USART1, USART_IT_RXNE) != RESET) //中断产生 { USART_ClearITPendingBit(USART1,USART_IT_RXNE); //清除中断标志. GetData = UART1_GetByte(BackData); //也行GetData=USART1->DR; USART1_SendByte(GetData); //发送数据 GPIO_SetBits(GPIOE, GPIO_Pin_8 ); //LED闪烁,接收成功发送完成 delay(1000); GPIO_ResetBits(GPIOE, GPIO_Pin_8 ); } } 这是最基本的,将数据接收完成后又发送出去,接收和发送在中断函数里执行,main函数里无其他要处理的。 优点:简单,适合很少量数据传输。 缺点:无缓存区,并且对数据的正确性没有判断,数据量稍大可能导致数据丢失。 实例二: void USART2_IRQHandler() { if(USART_GetITStatus(USART2,USART_IT_RXNE) != RESET) //中断产生 { USART_ClearITPendingBit(USART2,USART_IT_RXNE); //清除中断标志 Uart2_Buffer[Uart2_Rx_Num] = USART_ReceiveData(USART2); Uart2_Rx_Num++; } if((Uart2_Buffer[0] == 0x5A)&&(Uart2_Buffer[Uart2_Rx_Num-1] == 0xA5)) //判断最后接收的数据是否为设定值,确定数据正确性 Uart2_Sta=1; if(USART_GetFlagStatus(USART2,USART_FLAG_ORE) == SET) //溢出 { USART_ClearFlag(USART2,USART_FLAG_ORE); //读SR USART_ReceiveData(USART2); //读DR } } if( Uart2_Sta ) { for(Uart2_Tx_Num=0;Uart2_Tx_Num < Uart2_Rx_Num;Uart2_Tx_Num++)

ARM异常中断机制.

ARM9(以S3C2410为例)中断机制 一、ARM异常机制介绍 ARM9处理器有7种工作模式。分别是(除了用户模式其他都是异常模式 用户模式(usr:ARM处理器正常的程序执行状态。 快速中断模式(fiq:用于高速数据传输或通道处理。 外部中断模式(irq:用于通用的中断处理。 管理模式(svc:操作系统使用的保护模式。 数据访问终止模式(abt:当数据或指令预取终止时进入该模式。 系统模式(sys:运行具有特权的操作系统任务。 未定义指令中止模式(und:当未定义的指令执行时进入该模式。 每种模式通过5位二进制编码进行标示: 用户模式10000 快速中断模式10001 外部中断模式10010 管理模式10011 数据访问终止模式10111 未定义指令中止模式11011 系统模式11111 模式编码存放在CPSR(程序当前状态寄存器,记录当前工作模式的编码的值)中的[4:0]。

快速中断模式、外部中断模式、数据访问终止模式、未定义指令中止模式、管理模式称为异常模式。 异常类型具体含义 复位当处理器的复位电平有效时,产生复位异常,程序跳转到复位异常处理程序处执行。 未定义指令遇到不能处理的指令时,产生未定义指令异常。 软件中断该异常由执行SWI指令产生,可用于用户模式下的程序调用特权操作指令。可使用该异常机制实现系统功能调用。 指令预取中止若处理器预取指令的地址不存在,或该地址不允许当前指令访问,存储器会向处理器发出中止信号,但当预取的指令被执行时,才会产生指令预取中止异常。 数据中止若处理器数据访问指令的地址不存在,或该地址不允许当前指令访问时,产生数据中止异常。 IRQ(外部中断请求)当处理器的外部中断请求引脚有效,且CPSR中的I 位为0时,产生IRQ异常。系统的外设可通过该异常请求中断服务。 FIQ(快速中断请求)当处理器的快速中断请求引脚有效,且CPSR中的F 位为0时,产生FIQ异常。 当多个异常发生时,处理器根据优先级进行处理。优先级

定时器中断程序设计实验

实验一定时器/中断程序设计实验 一、实验目的 1、掌握定时器/中断的工作原理。 2、学习单片机定时器/中断的应用设计和调试 二、实验仪器和设备 1、普中科技单片机开发板 HC6800-EM3V3.0; 2、Keil uVision4 程序开发平台; 3、PZ-ISP 普中自动下载软件。 三、实验原理 805l 单片机内部有两个 16 位可编程定时/计数器,记为 T0 和 Tl。8052 单片机内除了 T0 和 T1 之外,还有第三个16位的定时器/计数器,记为T2。它们的工作方式可以由指令编程来设定,或作定时器用,或作外部脉冲计数器用。定时器T0由特殊功能寄存器TL0和TH0组成,定时器Tl由特殊功能寄存器TLl和TH1组成。定时器的工作方式由特殊功能寄存器TMOD编程决定,定时器的运行控制由特殊功能寄存器TCON编程控制。T0、T1在作为定时器时,规定的定时时间到达,即产生一个定时器中断,CPU转向中断处理程序,从而完成某种定时控制功能。T0、T1用作计数器使用时也可以申请中断。作定时器使用时,时钟由单片机内部系统时钟提供;作计数器使用时,外部计数脉冲由P3口的P3.4(或P3.5)即T0(或T1)引脚输入。 方式控制寄存器TMOD的控制字格式如下: 低4位为T0的控制字,高4位为T1的控制字。GATE为门控位,对定时器/计数器的启动起辅助控制作用。GATE=l时,定时器/计数器的计数受外部引脚输入电平的控制。由由运行控制位TRX(X=0,1)=1和外中断引脚(0INT或1INT)上的高电平共同来启动定时器/计数器运行;GATE=0时。定时器/计数器的运行不受外部输入引脚的控制,仅由TRX(X=0,1)=1来启动定时器/计数器运行。 C/-T 为方式选择位。C/-T=0 为定时器方式,采用单片机内部振荡脉冲的12 分频信号作为时钟计时脉冲,若采用12MHz的振荡器,则定时器的计数频率为1MHZ,从定时器的计数值便可求得定时的时间。C/-T=1为计数器方式。采用外部引脚(T0为P3.4,Tl为P3.5)的输入脉冲作为计数脉冲,当T0(或T1)输入信号发生从高到低的负跳变时,计数器加1。最高计数频率为单片机时钟频率的1/24。M1、M0二位的状态确定了定时器的工作方式,详见表。

嵌入式课程设计--_串口通信

摘要 (2) 1、绪论 (2) 1.1目的和意义 (2) 1.2设计内容 (2) 2、设计方案 (3) 2.1方案选择 (3) 2.1.1S3C2410X 串行通讯(UART)单元 (3) 2.1.2 波特率的产生 (3) 2.1.3 UART 通信操作 (4) 2.1.4 UART 控制寄存器 (4) 2.1.5 RS232 接口电路 (5) 3、硬件设计 (6) 3.1Embest EduKit-III 实验平台 (6) 3.2ULINK2 仿真器套件,PC 机 (6) 4、软件设计 (6) 4.2程序流程图设计 (7) 4.3调试运行结果 (7) 5、总结与体会 (8) 参考文献 (9)

摘要 为了掌握嵌入式技术,就应该学习以ARM 微处理器为核心的嵌入式开发环境和开发平台。本设计采用ARM原理和C语言程序设计的,设置S3C2410X 处理器 UART 相关控制寄存器和ARM 处理器系统硬件电路中 UART 接口,利用Embest EduKit-III 实验平台实现S3C2410X处理器和PC机的结合。 关键字: Embest EduKit-III 实验平台;S3C2410X 串行通讯(UART)单元;UART 控制寄存器;串口通信

1、绪论 1.1目的和意义 串口通信是目前单片机和 DSP 等嵌入式系统之间,以及嵌入式系统与 PC 机或无线模块之间的一种非常重要且普遍使用的通信方式。在嵌入式系统的硬件结构中,通常只有一个8位或 16位的 CPU, 不仅要完成主流程的工作, 同时还要处理随时发生的各种中断, 因而嵌入式系统中的串口通信程序设计与 PC 机有很大的不同。为了顺应当今世界技术革新的潮流,了解、学习和掌握嵌入式技术,就必然要学习和掌握以ARM 微处理器为核心的嵌入式开发环境和开发平台。 1.2设计内容 本设计采用Embest EduKit-III 实验平台实现,通过EmbestIDE Pro for ARM 软件编写程序,仿真调试。实现实验平台与PC的串口通信。通过PC的超级终端显示接受的结果。

串口中断程序

//串口中断服务程序,仅需做简单调用即可完成串口输入输出的处理 //出入均设有缓冲区,大小可任意设置。 //可供使用的函数名: //char getbyte(void);从接收缓冲区取一个byte,如不想等待则在调用前检测inbufsign是否为1。 //getline(char idata *line, unsigned char n); 获取一行数据回车结束,必须定义最 大输入字符数 //putbyte(char c);放入一个字节到发送缓冲区 //putbytes(unsigned char *outplace,j);放一串数据到发送缓冲区,自定义长度 //putstring(unsigned char code *puts);发送一个定义在程序存储区的字符串到串口 //puthex(unsigned char c);发送一个字节的hex码,分成两个字节发。 //putchar(uchar c,uchar j);输出一个无符号字符数的十进制表示,必须标示小数点的位置,自动删除前面无用的零 //putint(uint ui,uchar j);输出一个无符号整型数的十进制表示,必须标示小数点的位置,自动删除前面无用的零 //delay(unsigned char d); 延时n x 100ns //putinbuf(uchar c);人工输入一个字符到输入缓冲区 //cr;发送一个回车换行 //************************************************************************* #include

ARM的中断原理

ARM的中断原理(转) 1.中断概述 CPU与外设的数据传输方式通常有以下3种方式:查询方式、中断方式、DMA方式。 所谓查询方式是指,CPU不到查询外设的状态,如果外设准备就绪则开始进行数据传输;如果外设还没有准备好,CPU将进入循环等待状态。很显然这样浪费了大量的CPU时间,降低了CPU的利用率。 所谓中断方式是指,当外设准备好与CPU进行数据传输时,外设首先向CPU发出中断请求,CPU 接收到中断请求并在一定条件下,暂时停止原来的程序并执行中断服务处理程序,执行完毕以后再返回原来的程序继续执行。由此可见,采用中断方式避免了CPU把大量的时间花费在查询外设状态的操作上,从而大大提高了CPU的执行效率。 1.中断概述 CPU与外设的数据传输方式通常有以下3种方式:查询方式、中断方式、DMA方式。 所谓查询方式是指,CPU不到查询外设的状态,如果外设准备就绪则开始进行数据传输;如果外设还没有准备好,CPU将进入循环等待状态。很显然这样浪费了大量的CPU时间,降低了CPU的利用率。 所谓中断方式是指,当外设准备好与CPU进行数据传输时,外设首先向CPU发出中断请求,CPU 接收到中断请求并在一定条件下,暂时停止原来的程序并执行中断服务处理程序,执行完毕以后再返回原来的程序继续执行。由此可见,采用中断方式避免了CPU把大量的时间花费在查询外设状态的操作上,从而大大提高了CPU的执行效率。 ARM系统包括两类中断:一类是IRQ中断,另一类是FIQ中断。IRQ是普通中断,FIQ是快速中断,在进行大批量的复制、数据传输等工作时,常使用FIQ中断。FIQ的优先级高于IRQ。 在ARM系统中,支持7类异常,包括:复位、未定义指令、软中断、预取中止、数据中止、IRQ和FIQ,每种异常对应于不同的处理器模式。一旦发生异常,首先要进行模式切换,然后程序将转到该异常对应的固定存储地址执行。这个固定的地址称为异常向量。异常向量中保存的通常为异常处理程序的地址。ARM的异常向量如下: 异常模式正常地址高向量地址 复位管理 0x00000000 0xFFFF0000 未定义指令未定义 0x00000004 0xFFFF 0004 软中断管理 0x00000008 0xFFFF 0008 预取指中止中止0x0000000C 0xFFFF 000C 数据中止中止0x00000010 0xFFFF0010 IRQ IRQ 0x00000018 0xFFFF0018

51单片机C语言程序 定时 计数器 中断

51单片机C语言程序定时计数器中断51单片机C语言程序定时计数器 中断 程序一 利用定时/计数器T0从P1.0输出周期为1s的方波,让发光二极管以1HZ闪烁, #include reg52.h//52单片机头文件 #include intrins.h//包含有左右循环移位子函数的库 #define uint unsigned int//宏定义 #define uchar unsigned char//宏定义 sbit P1_0=P1^0; uchar tt; void main()//主函数 { TMOD=0x01;//设置定时器0为工作方式1 TH0=(65536-50000)/256; TL0=(65536-50000)%256; EA=1;//开总中断 ET0=1;//开定时器0中断 TR0=1;//启动定时器0 while(1);//等待中断产生 } void timer0()interrupt 1 { TH0=(65536-50000)/256; TL0=(65536-50000)%256; tt++;

if(tt==20) { tt=0; P1_0=~P1_0; } } 程序二 利用定时/计数器T1产生定时时钟, 由P1口控制8个发光二极管, 使8个指示灯依次一个一个闪动, 闪动频率为10次/秒(8个灯依次亮一遍为一个周期),循环。 #include reg52.h//52单片机头文件 #include intrins.h//包含有左右循环移位子函数的库 #define uint unsigned int//宏定义 #define uchar unsigned char//宏定义 sbit P1_0=P1^0; uchar tt,a; void main()//主函数 { TMOD=0x01;//设置定时器0为工作方式1 TH0=(65536-50000)/256; TL0=(65536-50000)%256; EA=1;//开总中断 ET0=1;//开定时器0中断 TR0=1;//启动定时器0 a=0xfe; while(1);//等待中断产生 } void timer0()interrupt 1